## STM32L4 - Flash

内蔵Flashメモリ

Revision 1

Dec- 2015

STM32L4のFlashメモリのプレゼンテーションへようこそ。

本プレゼンテーションでは、Flashメモリの全ての機能について説明します。

- STM32L4は最大1MBのデュアルバンクのFlashメモリを内蔵しています。

- Flashインターフェースは全てのアクセス(読み出し、プログラム、消去)、メモリ保護、および、オプションバイトのプログラミングを管理します。

## アプリケーションの利点

- 高性能で低消費電力

- 書き込み中の読み出しに対応

- 小さい消去単位

- 短いプログラム時間

- デュアルバンクブートに対応

STM32L4は最大1MBのデュアルバンクのFlashメモリを内蔵しています。

Flash・インターフェースは全てのアクセス(読み出し、プログラム、消去)、メモリ保護、および、オプションバイトのプログラミングを管理します。

Flash・インターフェースを使用するアプリケーションでは、高性能で低消費電力のアクセスが可能です。

本Flashメモリは書き込み中の読み出しに対応しており、また、小さい消去単位、短いプログラム時間、デュアルバンクブートに対応しています。

## 主な特長

3

- 最大1MBのデュアルバンク・Flashメモリ、および、書き込み中の読み出しに対応

- 高速消去(22ms)と高速プログラム時間(ダブルワードで82μs)

- ART accelerator™ (命令キヤッシュ、データキヤッシュ、および、プリフェッчバッファ)により、動作周波数に対して線形的なパフォーマンスを実現

- エラーコード訂正(ECC)に対応: 64bitのダブルワードに対して8bit

- 1つのエラー検出および訂正

- 2つのエラー検出

STM32L4のFlashメモリには様々な特徴的な機能があります。最大1MBのデュアルバンク・Flashメモリ、および、書き込み中の読み出しに対応しているため、1つのバンクに書き込み、または、消去処理をしている間に、もう一方のバンクのコードを実行することができます。

消去単位はページサイズに従うため、たったの2KBです。ページ、バンク、または、全消去に要する時間はたったの22msで、ダブルワードのプログラミングに要する時間は立ったの82usです。

命令キヤッシュ、データキヤッシュ、および、プリフェッチバッファを搭載した適応型リアルタイム・メモリ・アクセラレータは、動作周波数に対して線形的なパフォーマンスを実現できます。

本Flashメモリは、エラーコード訂正(ECC)に対応しており、各64bitのダブルワードに対して8bit長が割り当てられています。本機能を使用して、1bitのエラー検出、および、訂正が可能ですが、また、2bitのエラー検出も可能ですが、訂正には対応し

ておりません。

# Flashメモリ構成

4

Flashメモリは2つのバンクに分けることができます。それぞれのバンクは以下の様に構成されています:

- メインメモリブロックはブロックあたり、2KBのページを256ページ含んでいます。各ページは、256バイトの行が8行で構成されています。

- インフォメーションブロックは以下を含みます:

- ST用途のために予約されているシステムメモリおよびブートローダ

- ユーザデータ用の1KB(128ダブルワード)のOTP(1度だけプログラム可能)エリア(バンク1のみ)。OTPエリアのデータは消去できず、書き込みは1度のみとなります。1つのbitだけが”0”に設定された場合、以降、そのbitを含むダブルワードの全てのbitに対して、”0”の値でも書き込めなくなります。

- ユーザ設定用のオプションバイト

Flashメモリは2つのバンクに分けることができ、それぞれのバンクは2KBのページを256ページ含むメインメモリブロックを持っています。

各ページは、256バイトの行が8行で構成されています。

各メインメモリブロックは、3つの部分で構成されるインフォメーションブロックを持っています。

1つ目の部分はシステムメモリで、STマイクロエレクトロニクスの用途で使用する予約領域とブートローダを含みます。これが選択されると、デバイスはシステムメモリにてブートを行い、ブートローダを実行します。

2つ目の部分は1KBの1度だけプログラム可能なエリアです。このエリアはバンク1のみに配置されています。OTPエリアは消去できず、1度だけ書き込むことができます。1つのbitが”0”的場合、以降、そのbitを含むダブルワードの全てのbitに対して、”0”的値でも書き込めなくなります。

3つ目の部分はユーザ設定用のオプションバイトを含みます。

# Flashメモリ構成

5

| Flash領域        |       | Flash・メモリ・アドレス            | サイズ   | 名前       |

|----------------|-------|---------------------------|-------|----------|

| メインメモリ         | バンク 1 | 0x0800 0000 – 0x0800 07FF | 2 KB  | ページ 0    |

|                |       | ...                       | 2 KB  |          |

|                |       | 0x0807 F800 – 0x0807 FFFF | 2 KB  | ページ 255  |

|                | バンク 2 | 0x0808 0000 – 0x0808 07FF | 2 KB  | ページ 256  |

|                |       | ...                       | 2 KB  |          |

|                |       | 0x0808 F800 – 0x0808 FFFF | 2 KB  | ページ 511  |

| インフォメーション・ブロック | バンク 1 | 0x1FFF 0000 – 0x1FFF 6FFF | 28 KB | システムメモリ  |

|                | バンク 2 | 0x1FFF 8000 – 0x1FFF EFFF | 28 KB |          |

|                | バンク 1 | 0x1FFF 7000 – 0x1FFF 73FF | 1 KB  | OTP エリア  |

|                | バンク 1 | 0x1FFF 7800 – 0x1FFF 780F | 16 B  | オプションバイト |

|                | バンク 2 | 0x1FFF F800 – 0x1FFF F80F | 16 B  |          |

本スライドはFlashメモリマップを示します。バンク1にはページ0から始まる256ページ、バンク2にはページ256から始まる256ページがあります。

ページ番号のMSBはバンク番号に相当します。

ページ番号はページ消去時のソフトウェアプロセスの中で使用されます。

# Flash・デュアルバンク

6

## 書き込み中読み出しとデュアルバンク・ブートが可能

- 書き込み中読み出しに対応した、256KB、512KB、または、1MB の デュアルバンク Flashメモリ

- ユーザ・オプション・バイトの **BFB2** オプション

- $BFB2 = 1$  の場合、デバイスは有効なバンクに応じてバンク 2、または、バンク 1からブートします

- $BFB2 = 0$  の場合、デバイスはバンク 1からのみブートします

- ユーザ・オプション・バイトの**DUALBANK** オプションにより、256KB、および、512KBの型番のデュアルバンク機能を選択します

| Flash領域                     |       | Flash・メモリ・アドレス            | サイズ  | 名前      |

|-----------------------------|-------|---------------------------|------|---------|

| メインメモリ<br>512 KB<br>デュアルバンク | バンク 1 | 0x0800 0000 – 0x0800 07FF | 2 KB | ページ 0   |

|                             |       | ...                       | 2 KB |         |

|                             |       | 0x0803 F800 – 0x0803 FFFF | 2 KB | ページ 127 |

|                             | バンク 2 | 0x0804 0000 – 0x0804 07FF | 2 KB | ページ 256 |

|                             |       | ...                       | 2 KB |         |

|                             |       | 0x0807 F800 – 0x0807 FFFF | 2 KB | ページ 511 |

Flashメモリはデュアルバンク・メモリで、書き込み中読み出し、および、デュアルバンク・ブートの機能に対応している為、バンク1、または、バンク2からのブートが可能です。

ユーザ・オプションバイトのBFB2オプションにより、デュアルバンク・ブート・モードを選択できます。

BFB2オプションがセットされている場合、デバイスは有効なバンクに応じてバンク2、または、バンク1からブートします。

BFB2オプションがクリアされている場合、デバイスは常にバンク1からブートします。

また、DUALBANKオプションにより、256KB、および、512KBの型番をシングルバンクとして使用するかデュアルバンクとして使用するか選択します。

例えば、512KB品に対して、DUALBANKを選択すると、バンク1に128ページ、バンク2に128ページ割り当てられます。

ページ名のMSBがバンク番号を表す為、バンク2の最初のページ名は、デバイスのメモリサイズによらず常に「ページ256」となります。

# デュアルバンク・Flashメモリ

7

- 書き込み中読み出し

- デュアルバンク構成により、1つのバンクにプログラム／消去中に別のバンクを読み出すことがあります。=> Flashメモリをプログラム中、コード実行が停止することはありません。

- 同じバンクへのデータのプログラム／消去時：BUSY中はAHBはストールします

- SYSCFG\_MEMRMPレジスタの**FB\_MODE**bitの設定で、メモリバンクを入れ替えることができます

|           | バンク1                               | バンク2                               |

|-----------|------------------------------------|------------------------------------|

| FB_MODE=0 | @0x0800 0000<br>エイリアス @0x0000 0000 | @0x0808 0000<br>エイリアス @0x0008 0000 |

| FB_MODE=1 | @0x0808 0000<br>エイリアス @0x0008 0000 | @0x0800 0000<br>エイリアス @0x0000 0000 |

デュアルバンク・メモリでは、1つのバンクにプログラム/消去中に別のバンクを読み出す事が出来ます。

Flashメモリをプログラム中、コード実行が停止しすることはありません。

同じバンクへのデータのプログラム/消去時、Flashメモリコントローラがビジー状態である間、AHBはストールします。

SYSCFG\_MEMRMPレジスタの**FB\_MODE**bitにより、2つのFlashバンクアドレスを入れ替える事ができます。

このbitがクリアされると、バンク1は0x0800 0000に、エイリアスは0に割り当てられます。

このbitがセットされると、バンク2は0x0800 0000に、エイリアスは0に割り当てられるため、デバイスのバンク2からのブートが可能となります。

# デュアルバンク・ブート

8

デュアルバンク・ブート機能により安全なファームウェアのアップグレードが可能

Boot 0 = 0 (ブートモード = Flash)

MJM

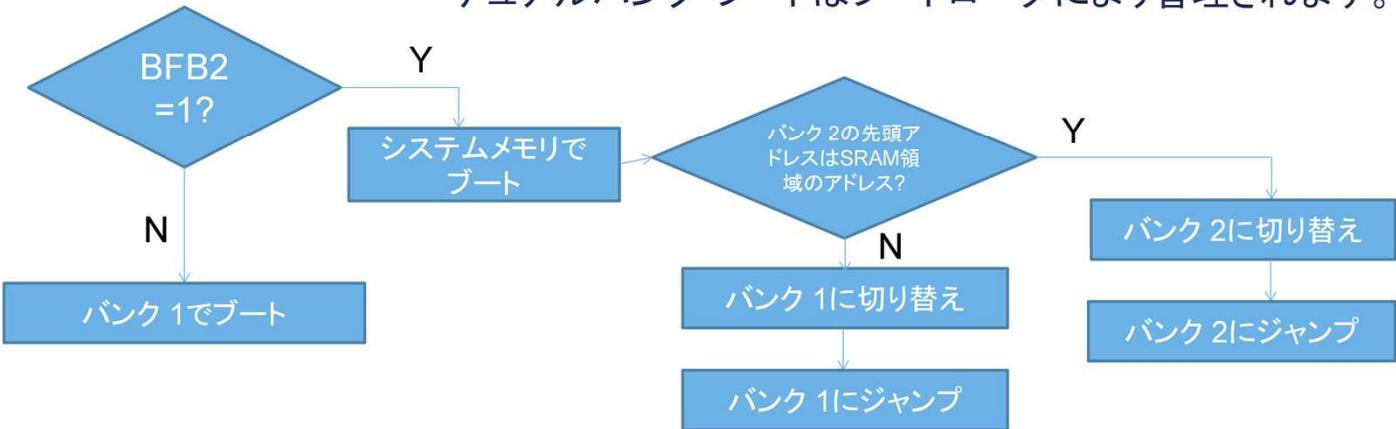

デュアルバンク・ブートはブートローダにより管理されます。

SRAM1の 0x2000 0000 - 0x2000 1000の領域はブートローダで使用されます。

デュアルバンク・ブートは、他のメモリバンクに前のバージョンのファームウェアを残した状態での安全なファームウェアの更新を可能にします。

デュアルバンク・ブートは、ブートローダにより管理されます。Flash・オプションバイトのBFB2オプションbitの設定により、デバイスをバンク2からブートさせる事ができます。

Flashメモリのブート設定は、ブートピン、および、ブートオプションによって行なわれます。

BFB2オプションbitがクリアされている場合、デバイスはFlash・バンク1でブートされます。

BFB2オプションbitがセットされている場合、デバイスはシステムメモリでブートされます。

ブートローダは、バンクの先頭アドレスをチェックし、そこにあるスタックポインタを必ず確認する必要があります。

バンク2の先頭アドレスが有効なSRAMアドレスの場合、ブートローダはバンク2がアドレス0になるように切り替え、バンク2にジャンプします。

バンク2の先頭アドレスが有効なSRAMアドレスでない場合、ブートローダはバンク1がアドレス0になるように切り替え、バンク1にジャンプします。

ブートローダはSRAM1のアドレス0x2000 0000 から 0x2000 1000の領域を使用するため、BFB2オプションbitがセットされている場合、

SRAMのこの領域はアプリケーションで使用しないように注意してください。

## Slide 8

---

**MJM1** Is this correct?? Boot 0 is NOT mentionned in the document.

Mike MILLER, 2015/07/08

# Flashの特長

9

## 堅牢なメモリの実装と安全性

- **ECC (エラーコード訂正)**: 64bitワードに対して8bit長

- 1つのエラー訂正: FLASH\_ECCRレジスタのECCC bitをセットすることで、オプションで割り込み生成が可能

- 2つのエラー検出: FLASH\_ECCRレジスタのECCD bitをセット=>NMI

- **FLASH\_ECCR**レジスタに、問題発生のアドレスとバンクが保存されます。

- プログラム最小単位は64bit(実際は8bitのECCを含め72bit)

- 2つのプログラミングモード:

- 標準(メインメモリ、および、OTP向け)

- 高速(メインメモリのみ)。Flash領域をベリファイせず32のダブルワードを書き込み

Flashメモリは、エラーコード訂正機能を搭載しており、堅牢なメモリの実装と安全性を実現しています。

ECCは64bitワードに対して8bit長です。1つのエラーの場合、訂正することが可能です。FLASH\_ECCRレジスタのECCCbitがセットされ、割り込みが有効の場合、割り込みを発生させることができます。

2つのエラーの場合、検出することが可能ですが、訂正はできません。FLASH\_ECCRレジスタのECCDbitがセットされ、ノンマスカブル割り込みが生成されます。

ECCエラーが検出されると、問題発生のアドレスと、関連するバンクはFLASH\_ECCRレジスタに保存されます。

プログラムの最小単位は64bitですが、実際はECC分の8bitを含め72bitとなります。

本Flashメモリには、2つのプログラミングモードがあります。メインメモリとOTPに使用可能な標準モードとメインメモリのみに使用可能な高速モードです。

標準モードでは、Flashメモリはプログラムする前に対象のダ

ブルワードが消去されているかどうかチェックします。

高速モードでは、Flash領域をベリファイせずに32のダブル

ワードを書き込みます。

# プログラム／消去時間

10

短いプログラム／消去時間と小さいページサイズ

=> データEEPROMエミュレーションに便利

| パラメータ               | 標準値                              |

|---------------------|----------------------------------|

| 64bit プログラム時間       | 82 $\mu$ s                       |

| ページ(2KB)消去時間        | 22 ms                            |

| 1行(32ダブルワード)プログラム時間 | 標準モード: 2.6 ms<br>高速モード: 1.9 ms   |

| 1ページ(2KB)プログラム時間    | 標準モード: 20.9 ms<br>高速モード: 15.3 ms |

| 1バンク(512KB)プログラム時間  | 標準モード: 5.35 s<br>高速モード: 3.9 s    |

| 全消去時間(1または2バンク)     | 22 ms                            |

Flashのプログラム時間は64bitダブルワードあたり、たったの82usです。

1ページ(2KB)のプログラムは、標準モードの場合20.9ms、高速モードの場合15.3msかかります。

バンク全体の場合、高速モードで3.9sかかります。

ページ消去時間は22msです。また、1つか両バンクの消去には22msしかかりません。これは、両バンクの消去処理が同時に実行されるからです。

短いプログラム/消去時間と小さいページサイズにより、データEEPROMのエミュレーションが実現しやすくなります。

## 行 (32 ダブルワード) 高速プログラミング

11

- メインメモリのみ高速プログラミングに対応しています

- Flash領域はプログラミングの前にハードウェアによりベリファイされません

- 32ダブルワードは連続的に書き込む必要があります。

- プログラミング中は常に、Flashメモリに高い電圧がかけられます

- 2つのダブルワードの書き込み要求間の最大時間はプログラム時間(約20us)です => 割り込みは無効である必要があります

- CPUのクロック周波数(HCLK)は 最低でも8 MHz以上である必要があります。

高速プログラミングモードにより、32ダブルワードを標準プログラミングモードよりも高速にプログラムすることが可能です。メインメモリのみ、高速プログラミングモードでプログラムすることができます。

Flashアドレス領域の内容は高速モードでプログラミングする前にハードウェアによりベリファイされません。

32ダブルワードは連続的に書き込む必要があります。

プログラミング中は常に、Flashメモリに高い電圧がかけられます。

2つのダブルワードの書き込み要求間の最大時間はプログラム時間、すなわち、約20usになります。

従って、割り込みは無効にして、2つのワード書き込み要求間の20usを越えないようにする必要があります。

高速プログラミングモードでは、クロック周波数は最低でも8MHz以上にする必要があります。

## 標準 対 高速プログラミングモード

12

|                | プログラミングモード      |                                                               |

|----------------|-----------------|---------------------------------------------------------------|

|                | 標準              | 高速                                                            |

| 対象             | メインメモリ + OTP 領域 | メインメモリのみ                                                      |

| 最小単位           | 8 バイト           | 256 バイト                                                       |

| 制限事項           | なし              | アドレス領域のチェックなし<br>CPUクロック周波数 $\geq 8 \text{ MHz}$<br>割り込みの使用禁止 |

| 256バイトのプログラム時間 | 2.6 ms          | 1.9 ms                                                        |

本スライドでは、標準と高速のプログラミングモードを比較しています。

標準モードはメインメモリおよびOTP領域のプログラミングに使用できる一方、高速モードはOTPのプログラミングに使用できません。

標準モードでは、64bitダブルワード、または、8バイトのプログラミングができますが、高速モードでは、32bitダブルワード、または、256バイトのプログラミングのみできます。

高速モードでは、プログラミングの前にアドレス領域の内容はチェックされません。また、CPUクロック周波数は8MHz以上である必要があり、割り込みの使用も禁止されます。

256バイトのプログラミング時間は標準モードでは2.6ms、高速モードでは1.9msとなります。

|            |                                                                                                                                                          |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 書き換え回数     | 最低1万回 @ -40°C ~ +105°C                                                                                                                                   |

| データ保持年数    | 30年 (1万回書き換え後に55°Cで)<br>15年 (1万回書き換え後に85°Cで)<br>10年 (1万回書き換え後に105°Cで)<br><br>30年 (1000回書き換え後に85°Cで)<br>15年 (1000回書き換え後に105°Cで)<br>7年 (1000回書き換え後に125°Cで) |

| 書き換えサイクル耐性 | 1 ppm                                                                                                                                                    |

Flashメモリは、最低1万回の書き換えサイクルを最大105°Cで保証します。

データ保持年数は、1万回書き換え後に55°Cで30年、85°Cで15年、105°Cで10年です。

また、1000回書き換え後の場合、85°Cで30年、105°Cで15年、125°Cで7年です。

# Flash読み出しアクセス

14

80 MHz で100 DMIPS

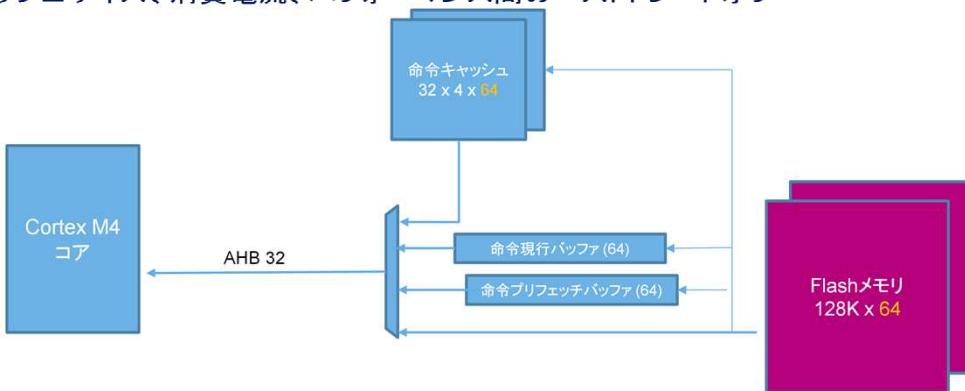

適応型リアルタイムメモリアクセラレータ(ART Accelerator™)は、Flashメモリへのアクセス時間によらず周波数に対して線形的なパフォーマンスを実現します。

| ウェイットステート<br>(WS)<br>(遅延) | HCLK (MHz)       |                  |

|---------------------------|------------------|------------------|

|                           | $V_{CORE}$ レンジ 1 | $V_{CORE}$ レンジ 2 |

| 0 WS                      | ≤ 16             | ≤ 6              |

| 1 WS                      | ≤ 32             | ≤ 12             |

| 2 WS                      | ≤ 48             | ≤ 18             |

| 3 WS                      | ≤ 64             | ≤ 26             |

| 4 WS                      | ≤ 80             |                  |

Flashメモリを読み出す為には、クロック周波数に応じて読み出しアクセスに挿入するウェイットステート数を設定する必要があります。

ウェイットステート数は電圧スケーリングレンジにも依存します。レンジ1では、4ウェイットステートでFlashメモリに最大80MHzでアクセスできます。

0ウェイットステートの場合、最大16MHzまでのアクセスが可能です。

レンジ2では、3ウェイットステートで最大26MHzまでのアクセスが可能です。

適応型リアルタイムメモリアクセラレータ(ARTアクセラレータ)により、クロック周波数によらずプログラムを0ウェイットステートで実行することができます。

これにより、周波数に対してほぼ線形的なパフォーマンスを実現しています。また、80MHzで100Dhrystone MIPSを実現しています。

# 適応型リアルタイムメモリアクセラレータ (ART Accelerator™)

15

## 優れたパフォーマンスと低消費電力

- 命令キャッシュ = 命令用に 4ダブルワードが 32 ライン × 64bit (1 KB)

- データキャッシュ = リテラルプール用に 4ダブルワードが 8 ライン × 64bit (256 バイト)

- プリフェッチバッファ

- キャッシュサイズ、消費電流、パフォーマンス間のベストトレードオフ

ARTアクセラレータは、優れたパフォーマンスと動的消費電力の削減に貢献します。

本機能は、1KBの命令キャッシュ、256バイトのデータキャッシュおよびプリフェッチバッファで構成されています。

命令キャッシュは4ダブルワードを32ライン、データキャッシュは4ダブルワードを8ライン含みます。

一度、全ての命令キャッシュメモリラインが満たされると、命令メモリキャッシュ内の置き換えられるラインを決める際、LRU(使われてから最も長い時間が経ったもの)の手法が使用されます。

この機能は、コードがループを含む場合に特に便利です。

このアーキテクチャは、キャッシュサイズ、消費電力、パフォーマンス間のベストトレードオフを提供する為に選ばれています。

キャッシュミスが発生する度に、キャッシュは要求されたダブルワードでのみ更新されます。そうすることにより、Flashアク

セスを制限し消費電力を抑える事ができます。

ライン内の4ダブルワードの全てが有効ではない場合があります。

キャッシュミスが発生した場合、Cortex-M4のコードはFlashメモリから命令を直接取得します。

並行して、64bitラインが現行バッファと有効な場合命令キャッシュにコピーされます。

従って、次の連続するアクセスは現行バッファから直接行なわれます。

プリフェッチが有効な場合、さらに64 bitのFlashアクセスが行なわれ、プリフェッチバッファは次のデータで満たされます。

データが現行バッファにある場合、CPUは現行バッファを読み出します。

その次の読み出しはプリフェッチバッファにて行なわれ、同時に現行バッファにコピーされるため、次のデータを格納する為のスペースが確保できます。

データが現行バッファにない場合、プリフェッチバッファにあればそこから読み出されます。プリフェッチバッファになければ、(キャッシュヒットしていれば)命令キャッシュから読み出されます。そうでない場合、Flashアクセスが行なわれます。

# ART の基礎

16

消費電力とパフォーマンスはアプリケーションコードに依存します

ほとんどの場合、キャッシュ有効 & プリフェッチ OFF の設定が最適なエネルギー効率

- プリフェッチが **ON**: ART の命令キャッシュは分岐キャッシュのように動作します:

- キャッシュは処理フロー内で分岐／ジャンプが発生するたびに更新されます

- 一連のアクセスは現行命令バッファ＋プリフェッチバッファにより発行されますプリフェッチバッファがヒットするたびに、内容が現行命令バッファに転送され、プリフェッチバッファにデータを入れるための新しいFlashアクセスが行なわれます。

=>キャッシュの内容は変わりません

- プリフェッチが **OFF(リセット値)**: ART のキャッシュは普通のキャッシュのように動作します:

- プリフェッチバッファは無効なので、一連のアクセスでもキャッシュの内容を変更します

命令キャッシュは、プリフェッチバッファが有効か無効かによって動作が異なります。

プリフェッチバッファが有効な場合、ARTの命令キャッシュは分岐キャッシュのように動作します。

キャッシュは処理フロー内で、分岐、または、ジャンプが発生するたびに変更されます。

一連のアクセスは現行命令バッファ、および、プリフェッチバッファにより発行されます。

プリフェッチバッファがヒットするたびに、その内容は現行命令バッファに転送され、プリフェッチバッファにデータを入れるための新しいFlashアクセスが行なわれます。

この場合、キャッシュの内容は変わりません。

プリフェッチバッファが無効な場合、ARTの命令キャッシュは普通のキャッシュのように動作します。

プリフェッチバッファは無効なので、一連のアクセスでもキャッシュの内容を変更します。

消費電力とパフォーマンスのトレードオフは、アプリケーションごとに評価し、プリフェッчバッファを有効にした方がいいか、無効にした方がいいかを判断する必要があります。

ほとんどのアプリケーションでは、プリフェッчバッファを有効にすることでパフォーマンスを若干向上しますが消費電力が増えます。

ほとんどの場合、最適なエネルギー効率は、キャッシュを有効およびプリフェッчバッファを無効に設定し、Flashへのアクセス回数を減らす事で得られます。

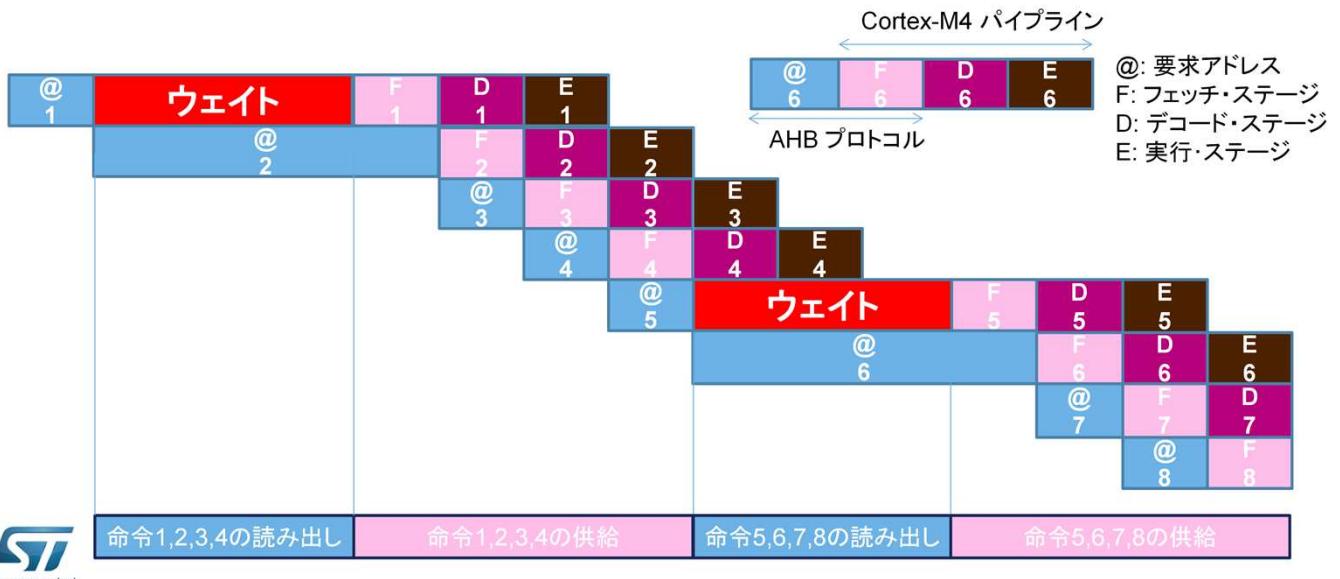

# 一連の16bit命令実行 (3WS) プリフェッチ無効

17

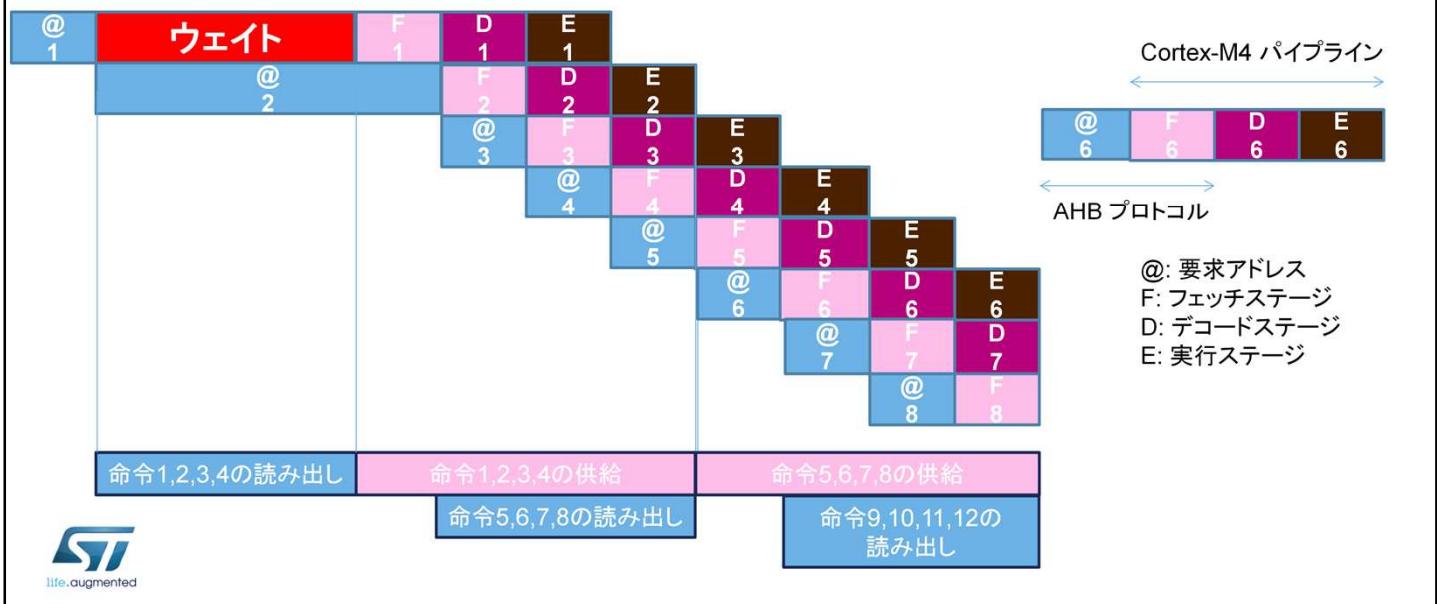

本スライドは、Flashメモリへのアクセスに3ウェイツステート必要な場合で、プリフェッチ無効時に一連の16bit命令の実行に必要なサイクル数を示しています。

各Flashアクセスにより64bitまたは4命令取得できます。また、各Flashアクセスにおいて、4命令ごとに3ウェイツステート挿入されます。

# 一連の16bit命令実行 (3WS) プリフェッч有効

18

本スライドは、Flashメモリへのアクセスに3ウェイターステート必要な場合で、プリフェッч有効時に一連の16bit命令の実行に必要なサイクル数を示しています。

各Flashアクセス後に、次のFlashアクセスを行ないプリフェッчバッファを満たすことができます。

従って、現行バッファから全ての命令がフェッчされた後、次の一連の命令はプリフェッчバッファより読み出され、命令フローが連続的である限り、

ウェイターステートは挿入されません。

# Flashメモリの保護

19

## アプリケーションでの必要性に応じた柔軟なFlash保護機能

### ・ 読出し保護 (RDP)

メモリ保護のトレーニング資料を参照

デバッグインターフェース (JTAG/SWD)、SRAM1からのブート時、または、ブートローダ選択時の Flash/SRAM2/バックアップレジスタへのアクセスを禁止します。

### ・ 独自仕様コード読出し保護 (PCROP)

- 64bit単位でバンク当たり1領域

- 特定のコード領域への読み出し/書き込みアクセスを保護します。コード実行のみ可能。

### ・ 書込み保護 (WRP)

- 2KB単位でバンク当たり2領域

- 特定のコード領域への不要な書き込みアクセスを保護に使用します。

様々なFlashメモリ保護機能がオプションバイトにて設定できます。

読み出し保護はRDPのオプションバイトを使用して設定されます。

読み出し保護はFlashメモリ、SRAM2、および、バックアップレジ

スタへのデバッグインターフェース、SRAM1からのブート時、ま

たは、ブートローダ選択時のアクセスを禁止します。

独自仕様コード読み出し保護はPCROPのオプションバイトを使

用して設定されます。

このオプションは特定のコード領域への読み出し、または、書き

込みアクセスを保護し、コード実行のみ可能となります。

保護対象領域は、64bit単位でバンクあたり1領域指定するこ

とができます。

書き込み保護はWRPのオプションバイトを使用して設定されま

す。

このオプションは特定のコード領域への不要な書き込みアクセスを保護します。

書き込み保護対象領域は、2KB単位で指定することができます。

保護オプションの詳細に関してはシステム保護のトレーニング資料を参照してください。

## ユーザ・オプション・バイト

20

ユーザ・オプション・バイトは次の場合にロードされます:

- パワーリセット後(BOR または STANBY/SHUTDOWNモードからの復帰)

- Flash制御レジスタ(FLASH\_CR)のOBL\_LAUNCHbitがセットされた時

| オプション                                     | 説明                                                                    |

|-------------------------------------------|-----------------------------------------------------------------------|

| BOR_LEV[2:0]                              | ブラウンアウトリセットの閾値レベル                                                     |

| nRST_STOP; nRST_STDBY;<br>nRST_SHDW       | STOP/STANBY/SHUTDOWNモードから復帰する際のリセット発行                                 |

| WWDG_SW; IDWG_SW<br>IWDG_STOP; IWDG_STDBY | ウィンドウ型／独立型ウォッチドッグのハードウェア／ソフトウェア設定<br>STOP/STANBYモードの独立型ウォッチドッグのカウント凍結 |

| BFB2<br>DUAL-BANK                         | デュアルバンク・ブート設定<br>512KB、または、256KBのFlashメモリ品のデュアルバンク設定                  |

| nBOOT1                                    | ブート設定                                                                 |

| SRAM2_RST<br>SRAM2_PE                     | システムリセット時のSRAM2消去<br>SRAM2パリティチェック                                    |

Flashメモリには、デバイスの特定の機能を設定するための様々なオプションバイトが用意されています。

ユーザ・オプション・バイトは、パワーリセットまたはブラウンアウトリセット時、STANDBYモードまたはSHUTDOWNモードからの復帰時、または、Flash制御レジスタ(FLASH\_CR)のOBL\_LAUNCHbitがセットされた時にロードされます。

ブラウンアウトリセットの閾値レベルの設定には3つのオプションbitが使用されます。

3つのオプションにより、STOP、STANDBY、SHUTDOWNの低消費電力モードから復帰する際のリセット発行の有無を設定可能です。

4つのオプションにより、ウォッチドッグの有効化をハードウェアで行なうかソフトウェアで行なうかの設定、および、独立型ウォッチドッグをSTOPモードおよびSTANDBYモードにて停止させるか否かを設定することができます。

2つのオプションにより、デュアルバンクブートの設定と、512KBまたは256KBのFlashメモリ品でデュアルバンク設定を

行なうかどうかを選択できます。

nBOOT1オプションは、ブートに使用するメモリを設定するために、BOOT0ピンと共に使用されます。

2つのオプションにより、SRAM2がシステムリセットによる消去の有無、SRAM2のパリティチェックの有効化の設定が可能です。

# ユーザ・オプション・バイト

21

| オプション                                                                                                                                            | 説明                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDP[7:0]                                                                                                                                         | 読み出し保護レベル                                                                                                                                                                                                                                                    |

| PCROP1_STRT[15:0]<br>PCROP1_END[15:0]<br>PCROP2_STRT[15:0]<br>PCROP2_END[15:0]                                                                   | バンク 1 PCROP 領域 開始オフセットアドレス<br>バンク 1 PCROP 領域 終了オフセットアドレス<br>バンク 2 PCROP 領域 開始オフセットアドレス<br>バンク 2 PCROP 領域 終了オフセットアドレス                                                                                                                                         |

| PCROP_RDP                                                                                                                                        | RDPレベルが下がった場合、PCROP 領域は保持されます                                                                                                                                                                                                                                |

| WRP1A_STRT[7:0]<br>WRP1A_END[7:0]<br>WRP1B_STRT[7:0]<br>WRP1B_END[7:0]<br>WRP2A_STRT[7:0]<br>WRP2A_END[7:0]<br>WRP2B_STRT[7:0]<br>WRP2B_END[7:0] | バンク 1 書込み保護エリア A 開始オフセットアドレス<br>バンク 1 書込み保護エリア A 終了オフセットアドレス<br>バンク 1 書込み保護エリア B 開始オフセットアドレス<br>バンク 1 書込み保護エリア B 終了オフセットアドレス<br>バンク 2 書込み保護エリア A 開始オフセットアドレス<br>バンク 2 書込み保護エリア A 終了オフセットアドレス<br>バンク 2 書込み保護エリア B 開始オフセットアドレス<br>バンク 2 書込み保護エリア B 終了オフセットアドレス |

メモリ保護オプションには、様々なオプションバイトが使用されます。

読み出し保護にはRDP、各バンクの開始アドレスと終了アドレスにはPCROP、各バンクの各2領域の開始アドレスと終了アドレスにはWRPが使用されます。

PCROP\_RDPbitは、読み出し保護を解除する際、レベル1からレベル0に変更される時に、PCROP領域を維持するか消去するかを設定するのに使用されます。

# 割り込み

22

| 割り込みイベント                 | 説明                                                             |

|--------------------------|----------------------------------------------------------------|

| <b>割り込み</b>              |                                                                |

| 操作終了                     | 1つ以上のFlashメモリ操作(プログラム／消去)が正常に完了するとハードウェアでセットされます。              |

| 操作エラー                    | Flashメモリ操作(プログラム／消去)に失敗するとハードウェアでセットされます。                      |

| 読み出しエラー                  | D-バスから読み出されるアドレスがFlashの読み出し保護領域(PCROP保護)内にある場合、ハードウェアでセットされます。 |

| ECC 訂正                   | 1つのECCエラーが検出され訂正されるとハードウェアでセットされます。                            |

| <b>ノンマスカラブル割り込み(NMI)</b> |                                                                |

| ECC 検出                   | 2つのECCエラーが検出されるとハードウェアでセットされます。                                |

Flashメモリで4つの割り込みを生成可能です。

操作終了割り込みは、1つ以上のFlashへのプログラムまたは消去操作が正常に完了した場合に生成されます。

操作エラー割り込みは、Flashメモリのプログラムまたは消去操作が失敗した場合にトリガれます。

読み出しエラー割り込みは、コアのデータバスから読み出されるアドレスがPCROPオプションによりFlash保護された領域内にある場合、トリガれます。

ECC割り込みは、1つのECCエラーが検出され訂正された場合にトリガれます。

2つのECCエラーが検出された場合、ノンマスカラブル割り込みが生成されます。

## SRAM実行時の消費電力の最適化

- RUN/低電力RUN、SLEEP/低電力SLEEPモード時、Flashへのクロック供給をゲーティングすることができます。

- Flashクロックはリセットおよびクロック制御(RCC)にて設定します

- Flashクロックはデフォルトで有効です

- SLEEP/低電力SLEEPモード時、Flashをパワーダウンモードに設定することができます。

- RUN/低電力RUNモード時、Flashをパワーダウンモードに設定することができます。

コードがFlash上で実行されていない場合、Flashメモリの消費電力を下げる事ができます。

FlashクロックはRUN/低電力RUNモード時にゲーティングすることができます。

また、SLEEP/低電力SLEEPモード時にも、Flashクロックをゲーティングすることができます。

Flashクロックはリセットおよびクロック制御(RCC)にて設定します。Flashクロックはデフォルトで有効です。

Flashメモリは、SLEEP/低電力SLEEPモード時にパワーダウンモードに設定可能です。

また、コードがSRAM上で実行されている場合、RUN/低電力RUNモード時にもFlashメモリをパワーダウンモードに設定可能です。

クロックのゲーティングおよびFlashメモリをパワーダウンモードに設定することで、大幅な消費電力の低減が可能です。

# 低電力モード

24

| モード      | 説明                                                                                                                 |

|----------|--------------------------------------------------------------------------------------------------------------------|

| RUN      | 有効。コードがSRAM上で実行されていて、Flashメモリがパワーダウンモードの場合、Flashクロックを無効にすることができます。                                                 |

| SLEEP    | 有効。ペリフェラル割り込みにより、デバイスをSLEEPモードから復帰できます。<br>SLEEPモードでは、Flashクロックを無効にすることができます。Flashメモリをパワーダウンモードに設定することができます。       |

| 低電力RUN   | 有効。コードがSRAM上で実行されていて、Flashメモリがパワーダウンモードの場合、Flashクロックを無効にすることができます。                                                 |

| 低電力SLEEP | 有効。ペリフェラル割り込みにより、デバイスを低電力SLEEPモードから復帰できます。<br>低電力SLEEPモードでは、Flashクロックを無効にすることができます。Flashメモリをパワーダウンモードに設定することができます。 |

| STOP 1   | Flashクロックは停止。ペリフェラルレジスタの内容は保持されます。                                                                                 |

| STOP 2   | Flashクロックは停止。ペリフェラルレジスタの内容は保持されます。                                                                                 |

| STANDBY  | パワーダウン。STANBYモードから復帰後、Flashインターフェースは再初期化が必要です。                                                                     |

| SHUTDOWN | パワーダウン。SHUTDOWNモードから復帰後、Flashインターフェースは再初期化が必要です。                                                                   |

RUNおよび低電力RUNモードでは、Flashメモリは有効です。

コードがSRAM上で実行されていて、Flashメモリがパワーダウンモードの場合、Flashクロックを無効にすることができます。

SLEEPおよび低電力SLEEPモードでは、Flashクロックを無効にすることができます。また、Flashメモリをパワーダウンモードに設定することができます。

STOP1およびSTOP2モードでは、Flashクロックは停止します。

Flashインターフェースレジスタの内容は保持されます。

STANDBYおよびSHUTDOWNモードでは、Flashインターフェースレジスタの内容は失われるため、モードから復帰後に再初期化が必要になります。

# Flash・パフォーマンス

25

## 3.35 Coremark / MHz

ARTアクセラレータにより、Flashパフォーマンスは周波数に対しほぼ線形的に変化します。

**3.35 CoreMark / MHz (キャッシュ ON、プリフェッチ OFF時)**

=> 268 CoreMark (80 MHz時)

|                                       |                        | ARTアクセラレータ ON<br>(キャッシュ On, プリフェッチ Off) | ARTアクセラレータ OFF |

|---------------------------------------|------------------------|-----------------------------------------|----------------|

| レンジ 1 @<br>80 MHz<br>(4 ウエイト<br>ステート) | 消費電流 (mA/MHz)          | 0.136                                   | 0.117          |

|                                       | パフォーマンス (CoreMark/MHz) | 3.32                                    | 1.55           |

|                                       | エネルギー効率 (CoreMark/mA)  | <b>24.4</b>                             | 13.2           |

| レンジ 2 @<br>26 MHz<br>(3 ウエイト<br>ステート) | 消費電流 (mA/MHz)          | 0.117                                   | 0.111          |

|                                       | パフォーマンス (CoreMark/MHz) | 3.35                                    | 1.85           |

|                                       | エネルギー効率 (CoreMark/mA)  | <b>28.6</b>                             | 16.6           |

ARTアクセラレータにより、Flashメモリのパフォーマンスは、周波数に対してほぼ線形的に変化します。

命令およびデータキャッシュが有効、プリフェッチバッファが無効の場合、80MHz時、CoreMarkのスコアは268となり、これは3.35 CoreMark/MHzに相当します。

命令およびデータキャッシュが有効、プリフェッチバッファが無効の場合、レンジ1で80MHz時、パフォーマンスは3.32CoreMark/MHzになります。

ARTアクセラレータが無効の場合、パフォーマンスはたったの1.55 CoreMark/MHzになります。

エネルギー効率に関しては、キャッシュを有効にした場合、ARTアクセラレータが有効時は24.4CoreMark/mAであるのに対し、ARTアクセラレータが無効時は13.2CoreMark/mAと大変興味深い比較となっています。

レンジ2では、エネルギー効率は26MHz時に最大28.6CoreMark/mAまで向上します。

## 関連ペリフェラル

26

- 本ペリフェラルに関するペリフェラルに関しては以下トレーニング資料を参照して下さい

- システム設定コントローラ (SYSCFG)

- システム保護

- リセットおよびクロック制御 (RCC)

- 電源コントローラ (PWR)

- 割り込み (NVIC および EXTI)

Flashメモリに関するペリフェラルのリストです。より詳細な情報が必要な場合、これらのペリフェラルのトレーニング資料を参照して下さい。

- 詳細は以下の資料をご参照下さい

- AN2606: STM32マイクロコントローラ・システム・メモリ・ブートモード(アプリケーションノート)

詳細情報に関しては、AN2606(STM32マイクロコントローラ・システム・メモリ・ブートモード)のアプリケーション・ノートをご参照下さい。