# STM32L4 - FSMC

フレキシブル・スタティック・メモリ・コントローラ

Revision 1

Dec- 2015

STM32L4のフレキシブル・スタティック・メモリ・コントローラのプレゼンテーションへようこそ。

本プレゼンテーションでは、NOR Flash、NAND Flash、SRAMおよびPSRAMといった外部メモリとの接続に使用するこのインターフェースの全ての機能について説明します。

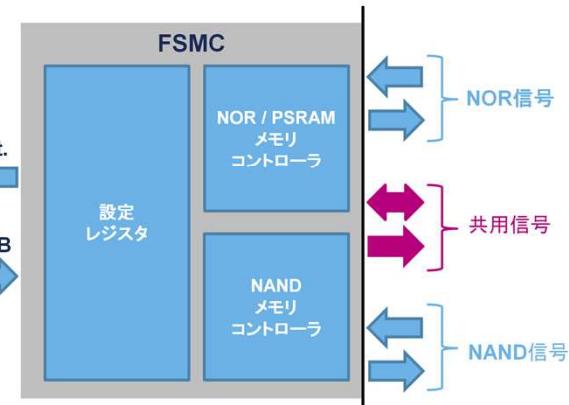

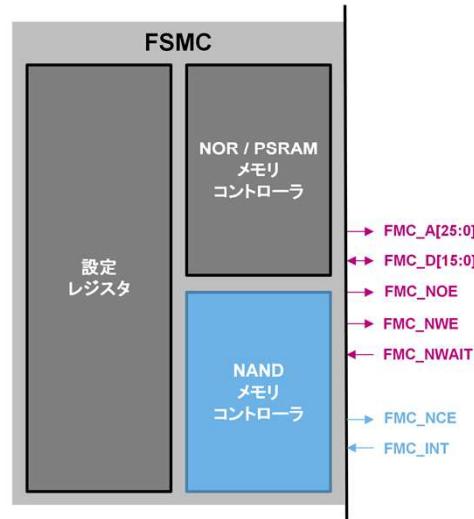

- FSMCは以下のコントローラを介して外部メモリに対応します

- NOR Flash／PSRAMコントローラ

- NANDメモリコントローラ

### アプリケーションの利点

- RAMの拡張

- Flashメモリの拡張

- パラレルインタフェース（インテル8080／モトローラ6800）

STM32L4製品に搭載されているFSMCコントローラは、NOR Flash/PSRAMコントローラとNANDメモリコントローラの2つのメモリコントローラを介して外部メモリに対応します。

これにより、CPUがNORおよびNAND Flashメモリ、PSRAM、SRAMを含む外部メモリと通信することを可能にします。

このインターフェースは自由に設定可能で、外部メモリ、または、他のパラレルインターフェースとの接続が容易です。

FSMCコントローラの利点は、RAMやFlashメモリ領域の拡張だけではなく、インテル8080、および、モトローラ6800モードに対応したほとんどのLCDコントローラと

シームレスにインターフェースが可能である点が挙げられます。

このLCDパラレルインターフェース機能により、コントローラ搭載のLCDを使用したコスト重視のグラフィックアプリケーションや、専用外部コントローラを使用した高パフォーマンスのソリューションの構築を容易にします。

- 完全に独立したバンク

- 分離されている外部メモリに対応する為の2つのバンク

- 各メモリバンク毎に独立したチップセレクト

- 各メモリバンク毎に独立した設定

- 柔軟な設定

- FSMC の外部アクセス周波数は最大HCLK/2

- 広範なデバイスに対応させる為のプログラム可能なタイミング

- 8または16bitのデータバス

- 外部非同期ウェイトコントロール

- 拡張モード(読み出しタイミング、および、書き込みタイミングと異なるプロトコル)

- 同期デバイス(NOR FlashおよびPSRAM)ではバーストモードアクセスに対応

FSMCコントローラは、分離されている外部メモリに対応するため

に2つの独立したバンクが設けられています。

それぞれのバンクは、独立したチップセレクトと設定を持っていま

す。

各バンクは、プログラム可能なタイミング、設定可能な8bitまたは

16bitのデータバス、および、非同期モード、または、NOR Flashや

PSRAMなどの

同期メモリに対してバーストモードでのアクセスが可能です。

同期メモリへは、最大HCLKの2分周の周波数でアクセス可能です。

# 対応するデバイス

4

## 広範なインターフェースやメモリと互換性があります

- スタティック・メモリマップ・デバイスは以下を含みます

- スタティック・ランダム・アクセス・メモリ(SRAM)

- 読み出し専用メモリ(ROM)

- NOR / OneNAND Flashメモリ

- PSRAM

- NAND Flashメモリ

- ECCのハードウェアにより最大8KBのデータ読み出し／書き込みのチェックが可能

- 3つの割り込みソース(レベル、立ち上がりエッジおよび立ち下がりエッジ)

- パラレルLCDモジュール

- インテル8080 およびモトローラ6800

FSMCは広範なデバイスおよびメモリに対応しています。

FSMCは以下のスタティック・メモリマップデバイスとインターフェースします。

- スタティック・ランダム・アクセス・メモリ (SRAM)

- 読み出し専用メモリ (ROM)

- NOR / OneNAND Flashメモリ

- PSRAM

FSMCは、また、NAND Flashメモリとのインターフェースにも対応し、最大8KBのデータ読み出しありは書き込みに対して誤りコード訂正(ECC)が可能です。

3つの割り込みソースの設定が可能で、NAND Flashのレディ/ビギー信号の立ち上がりエッジ、立ち下がりエッジまたはハイレベルの検出により割り込みを生成することができます。

更に、FSMCはパラレルLCDモジュールとのインターフェースにも対応し、インテル8080およびモトローラ6800モードに対応する事が可能で、様々なLCDインターフェースに適用するのに充分な柔軟性を備えています。

# バンクのメモリマッピング

5

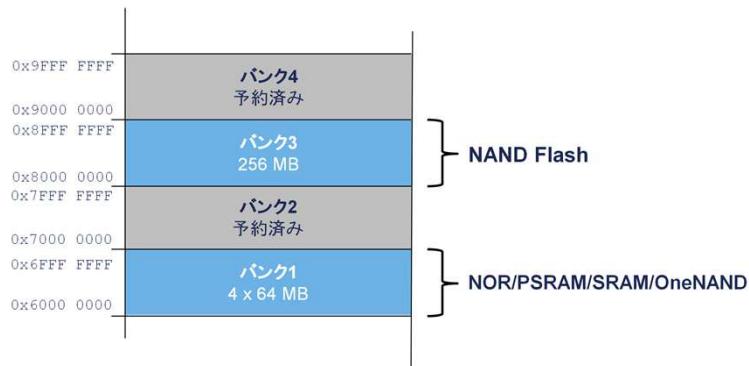

- 外部メモリは4つの固定サイズのバンクに分割されます

- バンク1 (4 x 64 MB) NOR Flash、OneNAND、SRAM または PSRAM専用

- バンク3 (256 MB) NAND Flash専用

- バンク2と4は予約済み

外部メモリ空間は、それぞれが256MBの固定サイズのバンクに分割されています。

2つの外部メモリバンクはFSMC専用です。

バンク1はNOR/PSRAMコントローラに接続されています。

バンク3はNANDコントローラに接続されています。

バンク2とバンク4は予約済みです。

# NOR/PSRAMのアドレスマッピング

6

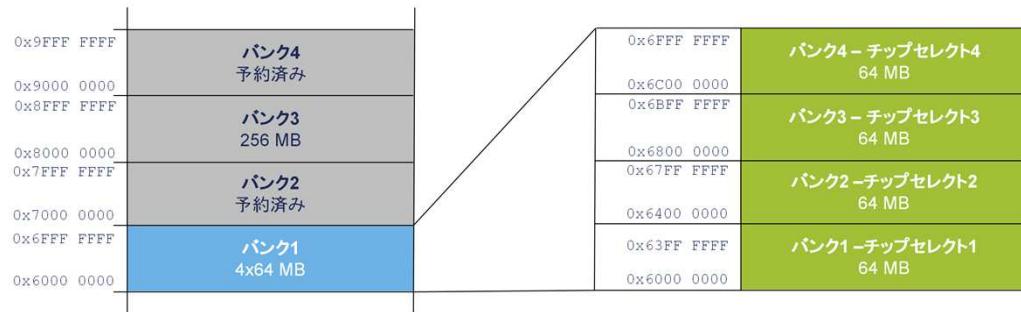

- ・ バンク1は4つの外部NOR/PSRAMメモリ(4つのチップセレクト)とインターフェースする為に、バンク当り64MBの4つのバンクに分割されており、以下に対応します

- ・ NOR Flash: 8/16bit同期/非同期、マルチプレックスまたは非マルチプレックス

- ・ SRAM/ROM: 8/16bit

- ・ CRAM/PSRAM: 8/16bit同期/非同期

バンク1は最大4つのNOR FlashメモリまたはPSRAMデバイスと接続するために使用されます。

このバンクは4つのNORまたはPSRAMの64MBサブバンクに分割され、4つの専用チップセレクトにより以下とのインターフェースに対応します。

- ・ 8または16bit 同期または非同期NOR Flash、マルチプレックスまたはノンマルチプレックスモード

- ・ 8または16bit 非同期SRAM および ROM.

- ・ 8または16bit 同期または非同期PSRAMメモリ

# NOR／PSRAMインターフェースの信号

7

- FSMCは駆動に適した信号を生成します

- 非同期SRAMおよびROM

- 8bit

- 16bit

- PSRAM (CellularRAMおよびCosmoRAM)

- 非同期モード

- バーストモード

- マルチプレックスまたはノンマルチプレックス

- NOR Flash

- 非同期モード

- バーストモード

- マルチプレックスまたはノンマルチプレックス

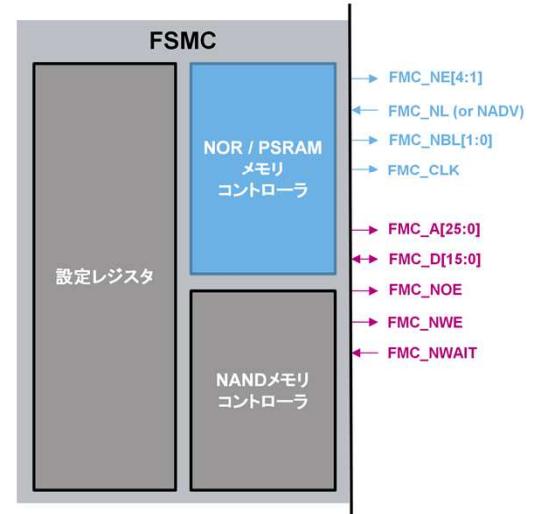

FSMCは固有のチップセレクト信号を各々のバンクへ出力し、一度に1つの外部デバイスに対してアクセスを実施します。外部メモリは、NOR/PSRAMコントローラまたはNANDコントローラのいずれかに接続され、アドレス、データおよび制御信号を共有します。

# NOR／PSRAMのタイミング設定

8

## 柔軟なタイミングの設定

- FSMCのNOR／PSRAMコントローラはバンクに接続されているメモリのタイミングを設定する為に使用されます

- アドレス・セットアップ・フェーズ時間

- アドレス・ホールド・フェーズ時間

- データ・セットアップ・フェーズ時間

- バス・ターンアラウンド・フェーズ時間

- クロック分周比

- データ遅延(同期バーストNOR Flash用)

- アクセスモード

NOR/PSRAMコントローラでは、対応するメモリの様々なタイミングパラメータを設定できます

- アドレスセットアップフェーズ: 最初のアクセスフェーズの時間

- アドレスホールドフェーズ: アクセスサイクルの中間フェーズの時間

- データセットアップフェーズ: 2番目のアクセスフェーズの時間

- バスターンアラウンドフェーズ: バスターンアラウンドフェーズの時間

- クロック分周比: 1メモリクロックサイクル(CLK)当りのAHBクロックサイクル(HCLK)数

- データ遅延: 最初のデータ転送前にメモリへ発行されるクロックサイクル数

- アクセスモード

# NANDのアドレスマッピング

9

- ・ バンク3は2つのメモリ空間を使ってNAND Flashメモリに対応する為に使用されます

- ・ コモンメモリ空間

- ・ 属性メモリ空間

- ・ 各メモリ空間は3つのサブセクションに分割されています

- ・ データセクション (64 KB): データの読み出しありは書き込みに使用

- ・ コマンドセクション (64 KB): NAND Flashメモリへのコマンド送信に使用

- ・ アドレスセクション (128 KB): NAND Flashメモリのアドレス特定に使用

バンク3はNAND Flashメモリとインターフェースするために使用され、コモンメモリ空間と属性メモリ空間の2つのメモリ空間に分割されています。

両空間は類似しています。コモンメモリ空間は全てのNAND Flashの読み出しありは書き込みアクセスのためにあります。

ただし、最後のアドレスバイトをNAND Flashデバイスに書き込む場合、CPUは属性メモリ空間へ書き込む必要があります。

これにより、最後のアドレスバイトを異なるタイミングで書き込むことで、一部のNAND Flashメモリにて必要なプリウェイト機能の実装が可能となります。

各メモリ空間は更に3つのセクションに分割されています：

- ・ データセクション (64 KB): NAND Flashメモリのデータの読み出しありは書き込みに使用

- ・ コマンドセクション (64 KB): NAND Flashメモリへのコマンド送信に使用

- ・ アドレスセクション (128 KB): NAND Flashメモリのアドレス特定に使用

# NANDインターフェースの信号

10

- FSMCはNANDメモリの駆動に適した信号を生成します

- NAND Flash

- 8bit

- 16bit

FSMCはNANDメモリの駆動に適した信号を生成します。

アドレス、データおよび制御信号はNOR/PSRAMコントローラと共用されます。

NAND Flashメモリデバイスのコマンドラッティネーブル(CLE)およびアドレスラッティネーブル(ALE)信号は、

それぞれアドレスライン16および17に接続されているFSMCコントローラからのアドレス信号で駆動されます。

アドレスセクションへの書き込み時にはALEはアクティブになります。

コマンドセクションへの書き込み時にはCLEはアクティブになります。

- FSMCのNANDメモリコントローラは以下の機能に対応しています

- 256Bから8192Bの範囲で読み出しおよび書き込み処理向けECCハードウェアアクセラレータ

- NANDバンク用に3つの割り込みソース

- 立ち上がりエッジ

- 立ち下がりエッジ

- 外部メモリのReady/nBusy出力ピンのレベル

- ウェイト機能の管理

- コントローラは、新しいアクセスを開始する前に、NAND Flashメモリがレディ状態(Ready/nBusy信号がハイ)になるのを待ちます。

FSMCのNANDメモリコントローラは以下の機能に対応しています。

- エラーコード訂正:ECCのアルゴリズムは、256から8192バイトの範囲内のNAND Flashメモリの読み出しありは書き込みごとに、1bitエラーの訂正と2bitエラーの検出を行ないます。本アルゴリズムはハミング符号化アルゴリズムに基いています。

- 3つの割り込みソースを有効化し、立ち上がりエッジ、立ち下がりエッジ、NAND FlashメモリからのReady/Busy信号の出力ピンレベルを検出することができます。

- ウェイト機能の管理:コントローラは、新しいアクセスを開始する前に、NAND Flashメモリがレディ状態になるのを待ちます。

# NANDのタイミング設定

12

- 各メモリ空間に対してパラメータを設定することができます

- セットアップ時間: コマンドがアサートされる前にアドレスをセットアップする時間

- ウェイト時間: コマンドをアサートする時間

- ホールド時間: コマンドをデアサート後にアドレスをホールドする時間

- データバス・ハイインピーダンス時間: アドレスが有効になりデータバスが駆動されるまでの時間

各メモリ空間において、コモンおよび属性をNAND Flashのコマンドアクセス、アドレス書き込みアクセスおよびデータ読み出し/書き込みアクセスに応じて異なるタイミングで設定することができます。

属性メモリ空間は、Ready/Busy管理でタイミングが前のアクセスと異なる必要がある場合、最後のアドレスの書き込みアクセスに使用されます。

それ以外の場合は、コモン空間のみ必要となります。

あらゆるNAND Flashアクセスの異なるフェーズのためのHCLKサイクル数を定義するために、4つのパラメータが使用されます。

- セットアップ時間

- 書き込み時間

- ホールド時間

- データバスハイインピーダンス時間

| 割り込みイベント | 説明                     |

|----------|------------------------|

| 立ち上がりエッジ | FMC_INTピンにて立ち上がりエッジを検出 |

| 立ち下がりエッジ | FMC_INTピンにて立ち下がりエッジを検出 |

| ハイレベル    | FMC_INTピンにてハイレベルを検出    |

NANDコントローラは、NAND FlashメモリからのReady/Busy信号に接続されたFMC\_INTピンの立ち上がりエッジ、立ち下がりエッジ、および、ハイレベルの検出の3つの割り込みソースを提供します

-

# 低電力モード

14

| モード      | 説明                                        |

|----------|-------------------------------------------|

| RUN      | 有効。                                       |

| SLEEP    | 有効。ペリフェラルの割り込みによりデバイスをSLEEPモードから復帰。       |

| 低電力RUN   | 有効。                                       |

| 低電力SLEEP | 有効。ペリフェラルの割り込みによりデバイスを低電力SLEEPモードから復帰。    |

| STOP1    | 停止。ペリフェラルレジスタの内容は保持されます。                  |

| STOP2    | 停止。ペリフェラルレジスタの内容は保持されます。                  |

| STANDBY  | パワーダウン。STANDBYモードから復帰後、ペリフェラルは再初期化が必要です。  |

| SHUTDOWN | パワーダウン。SHUTDOWNモードから復帰後、ペリフェラルは再初期化が必要です。 |

FSMCはRUN、SLEEP、低電力RUN、低電力SLEEPモード時に有効です。

A FSMC割り込みにより、デバイスをSLEEP、または、低電力SLEEPモードより復帰できます。

STANDBYまたはSHUTDOWNモードでは、FMCはパワーダウンの状態となり、復帰後に再初期化が必要になります。

# アプリケーション例

15

- ・コネクティビティとユーザ・インターフェースを含むウェアラブルアプリケーション:

- ・外部メモリは、ユーザ・インターフェースで必要となるオーディオやグラフィック（アイコン、フォント等）のデータを格納しておくことができます

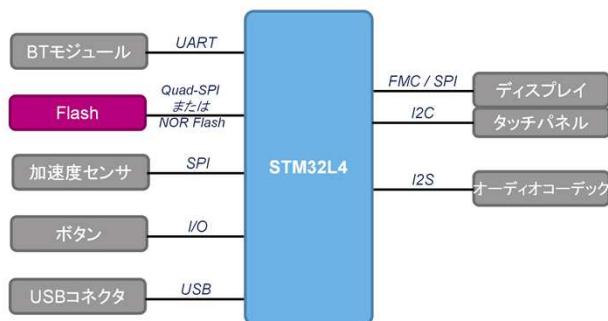

ウェアラブルアプリケーションでは低電力管理機能に加え高品質のユーザインターフェースが要求されます。

これらの要件は、STM32L4のFSMCを使って、LCDモジュールにインターフェースする為の柔軟で広範にプログラム可能なパラメータを設定することにより対応することができます。

さらに、FSMCまたはQuad-SPIインターフェースを使用して背景画像、高解像度アイコン、多言語対応のフォントなどの全てのグラフィックコンテンツを含む外部Flashメモリへのアクセスに使用できます。

さらに、着信音のオーディオデータを外部Flashメモリで提供される広い空間に保存しておくことができます。