# STM32L4 – タイマ(Timers)

高度な制御、汎用および基本的なタイマ

Revision 1

Jan - 2016

こんにちは、STM32L4のタイマについてのプレゼンテーションによこそ。これは、任意のタイミング関連のイベントを処理し、波形を生成および入力信号のタイミング特性を測定するために有用である、それらの主な特徴を説明しています。

- タイミングリソースを提供する複数のタイマユニット

- 内部 (トリガ、タイムベース)

- 外部、出力または入力:

- 波形生成 (PWM)

- 信号モニタまたは測定 (周波数 または タイミング)

### アプリケーションの利点

- 多目的動作モードは、CPUの負荷低減とインターフェース回路の必要性の最小化

- すべてのタイマ・インスタンスの単一のアーキテクチャは、拡張性と使いやすさを提供

- モータ制御とデジタル電力変換のアプリケーションのための十分な機能

STM32は、ソフトウェアやハードウェアタスクにタイミングソースを提供する複数のタイマが組み込まれています。ソフトウェアタスクは、主にタイムベース、タイムアウトイベント生成およびタイムトリガを提供するように構成されています。ハードウェアのタスクは、I/Oに関連しています。タイマは、その出力に波形を生成し、受信信号のパラメータを測定し、さらに、その入力の外部イベントに反応することができます。STM32のタイマは、非常に汎用性があり、インターフェース回路の必要性を最小限に抑えながら、反復的でタイムクリティカルなタスクからCPUの負荷低減をするための複数の動作モードを提供します。すべてのSTM32のタイマ(低電力タイマの唯一の例外を除いて)は、同じスケーラブルなアーキテクチャに基づいています。一度タイマの動作原理を知ると、それらは、いずれかのタイマのために有効です。このアーキテクチャは、相互接続の機能が含まれており、いくつかのタイマが大規模な構成に組み合わせることができます。最後に、タイマの一部は、照明やデジタルスイッチモード電源などのような電気モータ制御およびデジタル電力変換のための特定の機能を備えています。

## 主な特長

3

- すべてのタイマは、同じアーキテクチャに基づいており、以下の点でスケーラブル

- 入力/出力の数 (1 から 9)

- 分解能 (16 または 32bit)

- 機能 (PWM モード、DMA、同期、アップ/ダウンカウント)

- 複数のタイマは、リンクし同期することが可能。

- 各タイマのチャネルは、入力または出力として独立に構成することが可能。

- 他のペリフェラルとの複数の相互接続は、モニタやトリガの目的のために利用可能。

こちらは、STM32タイマの主な特長です。すべてのタイマは、同じアーキテクチャに基づいており、このプレゼンテーションの後半に記載されているいくつかの派生形で使用できます。タイマは、I/Oのない純粋なタイムベースから9つのI/Oを持つ高度な制御版まであり、それらが持っている入力と出力の数が主に異なります。タイマのほとんどは、16bitカウンタを備えて、いくつかは、32bitのカウンタを持っています。一部の機能は、(例えば、DMA、同期、アップ/ダウンカウントモードの場合)最小の機能のタイマには存在しない場合があります。

タイマのほとんどは、より大きな数の同期波形を持つか、または複雑なタイミングと波形を処理するより大きいタイムベースタイマを構築するためにリンクおよび同期することができます。

タイマ内では、すべてのチャンネル々々が独立して、入力(通常はキャプチャ用)として、または出力(通常はPWM用)として設定することができます。

タイマは、例えば、ADC変換を開始するため、あるいは内部クロックを監視するために、相互接続マトリクスにより他のペリフェラルのためのトリガとして働くことができます。

# ブロック図 (TIM15)

4

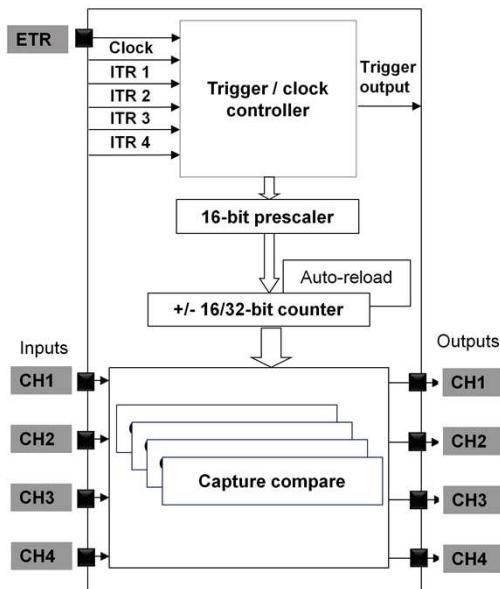

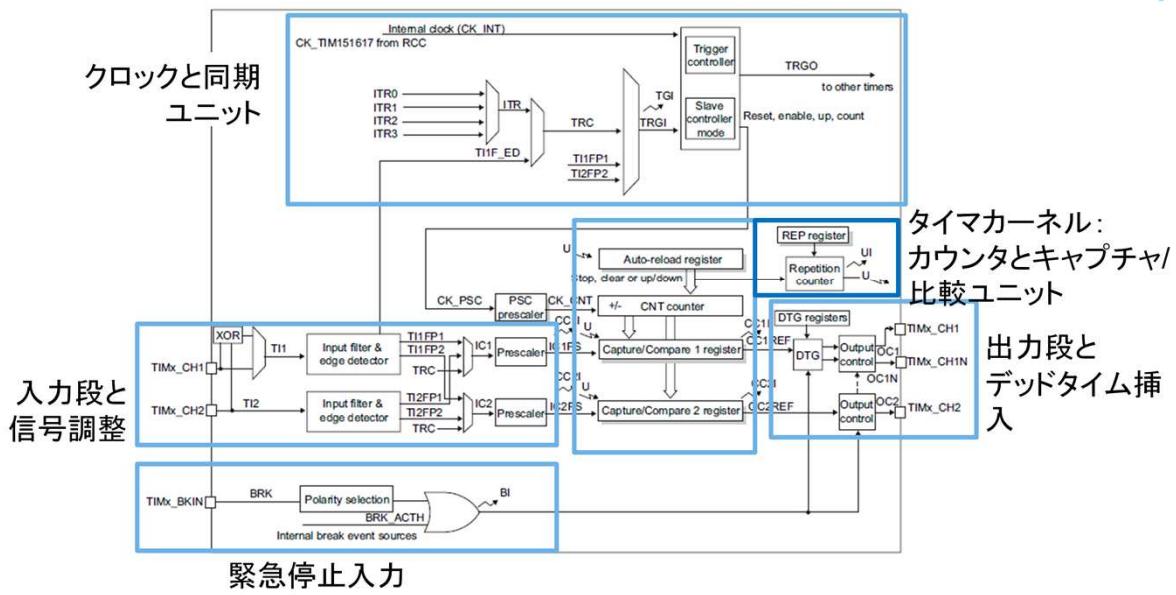

このスライドは、中間的な機能を備えたTIM15タイマのブロック図を示します。タイマカーネルは、カウント周期とカウンタロールオーバー割込みレートを調整するために、繰り返しカウンタをプログラムするためのオート再ロードレジスタが結合された16bitアップカウンタで構成されています。2つのタイマチャネルは、2つのキャプチャコンペアレジスタによって制御されます。カウンタは、タイマチェーンにも応答可能なクロックとトリガコントローラによって供給されます。

左側に示されているのは入力段と入力調整回路で、右側に出力段を持っています。これは、ハーフブリッジ電力段に適した相補的なPWM出力を提供するためのデッドタイムの挿入を含みます。TIMxCH1とTIMxCH2は、入力と出力が両方可能であることを示すために両側に現れていることに注意してください。最後に、TIMxBKIN入力は、PWM緊急停止のために使用することができます。

、

# タイマ・クロッキング方式

5

## 内部または外部の複数のクロックオプション

- APBドメインからのデフォルトのクロック

- タイマは、低消費電力の最適化のため、APB1とAPB2ドメインに分割されています。

- 可能な外部クロック：

- 他のオンチップタイマ(ITRx入力)

- 入力ピン1と2(TI1, TI2)

- デジタルフィルタとプログラマブルエッジ感度

- 多目的外部トリガ入力(ETR)

- デジタルフィルタ、プログラマブルエッジ感度と基本的なプリスケーラ(/2, /4, /8)

- エンコーダからの直交信号

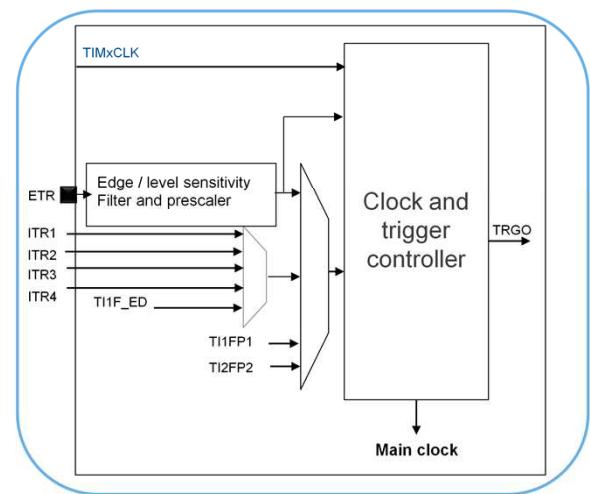

タイマは、複数のクロックオプションを備えています。

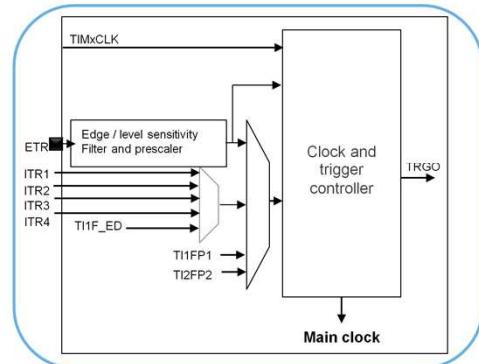

タイマチェーンにも応答可能なクロックとトリガコントローラは、カウンタのクロックを処理します。

デフォルトのクロックは、APBクロックドメインの1つにリンクされたリセットおよびクロックコントローラから来ています。各種タイマは、(タイマを含むペリフェラルによって引き出される電流を制限するために、一般的に1つの高速APBと1つの低速APB)低消費電力方式を実装するために、2つのAPBドメイン上で共有されています。

外部タイマクロックは、外部イベントのカウントや外部からのカウント周期の調整を可能にします。クロックソースは、4つの内部トリガ入力(ITR1 ... ITR4)のいずれかを使用して、他のオンチップタイマによって提供することができます。入力ピン1と2はまた、誤ったイベントを削除するためのデジタルフィルタを含むオプションを使用して、外部クロックとして使用することができます。

外部トリガ入力ETRは、デジタルフィルタ、プログラマブルエッジ感度、および必要に応じて入力信号の周波数を低減するための初めの基本プリスケーラ段を用いて、外部クロックとして構成す

ることができます。

最後に、このプレゼンテーションで後述するように、エンコーダからの直交信号は、クロックとカウント方向を提供するように処理することが可能です。

# カウント周期管理

6

## 優れた正確な周期設定

- 各タイマは、16bitのリニアプリスケーラが組み込まれています(1,2,3...65536)。

- オートリロードレジスタは、カウント期間を定義します。

- 更新イベント(割込みまたはDMA)は、オーバーフロー/アンダーフローで発行されます。

- プリロードからアクティブ(プリスケーラ、期間、比較)へのレジスタの内容の転送をトリガー

- 正確な周期変化(プリスケーラは、オーバーフローでのみ更新されます)

- コンペアレジスタが更新されているときのグリッチレス操作

- 更新割込み発行レートは、繰り返しカウンタで調整されています。

このスライドは、タイマカウント周期の調整の方法について説明しています。各タイマは、1から65536の間の任意の整数によってクロックを分割することを可能にするリニアクロックプリスケーラが組み込まれています。これは、カウント速度を正確に調整することができます。APBクロックが80MHzのとき、例えば、80による除算は、正確な1 MHzのカウントレートが得られます。自動再ロードレジスタは、カウント期間を定義します。ダウンカウントモードでは、カウンタは、アンダーフロー時に自動的に周期の値が再ロードされます。アップカウントモードでは、カウンタはロールオーバーし、オートリロード値を超えたときにリセットされます。カウンタのアンダーフロー やオーバーフローしたときに更新イベントが発行され、新しい周期が開始します。これは、リアルタイム制御のために有用であり、その期間に同期してタイマパラメータを調整するために使用される割込みまたはDMAリクエストをトリガします。

この更新イベントは、複数パラメータ、特にクロックプリスケーラ、自動再ロード値、比較レジスタとPWMモードのためのプリロードからアクティブレジスタへの転送をトリガします。

8bitプログラマブル繰り返しカウンタを使用すると、割込み発行レートをカウント期間から分離し、例えば、1つの割込みを1、2、3そして256までの PWM周期で持つことができます。これは、高いPWM周波数を扱う場合に特に有用です。

# カウントモード

7

## インクリメンタル/直交エンコーダおよびモータ駆動アプリケーションのサポート

- ・アップとダウンカウントモードのサポート

- TIM1/8 および TIM2/3/4/5

- ・センターラインPWM発生

- オーバフローとアンダーフローでの方向変更

- 電気モーター内の音響ノイズの低減

- ・直交エンコーダの内蔵サポート

- ロータリーエンコーダ/デジタルポテンショメータ

- ポジションセンサー

- タイマで直接角度の読み取りを可能にします

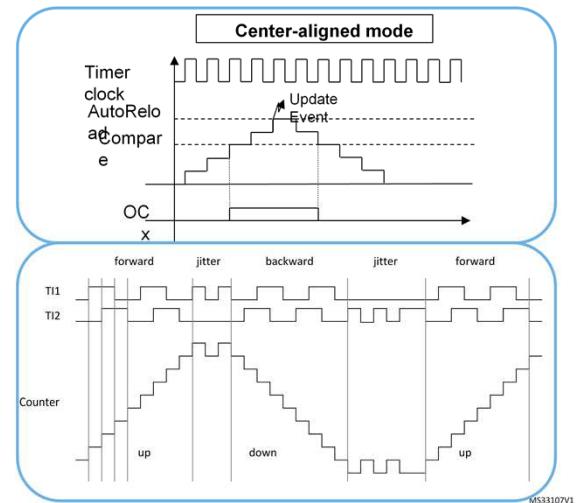

STM32のタイマの中には、アップ・ダウンカウントモードを備えています。高度制御タイマ1、8そして汎用タイマ2、3、4、5。カウント方向は、ソフトウェアでプログラムされるか、または自動的にセンターラインPWMモード時のタイマによって管理することができます。このモードでは、カウント方向は、カウンタオーバーフローとアンダーフローで自動的に変化します。任意のPWMスイッチング周波数で、このモードは、効果的な電流リップル周波数を2倍にすることにより音響ノイズを低減し、パワ一段のスイッチング損失やノイズ間の最適なトレードオフを提供しています。タイマがエンコーダモードにあるとき、カウント方向も自動的に処理することができます。直交エンコーダは、一般的には電気モーターで高精度なロータ位置検出のためか、デジタルポテンショメータのために使用されます。直交エンコーダセンサ(また、インクリメンタルエンコーダと呼ばれる)の2つの出力から、タイマは、それぞれのクロックとすべてのアクティブエッジを抽出し、2つの入力信号間の相対位相シフトに応じてカウント方向を調整します。タイマカウンタは、このように直接モータやポテンショメータの角度位置を保持しています。

# 内部タイミングリソースとしてのタイマ

8

## ソフトウェアとハードウェアのタイムベース

- タイマは、基本的なタイムベースとして使用されます。

- ソフトウェア制御用

- 他のペリフェラルへの周期的なトリガを提供

- ADC / DAC または 他のタイマ

- 更新イベント(カウンタのオーバフロー)は、割込みをトリガするために使用できます。

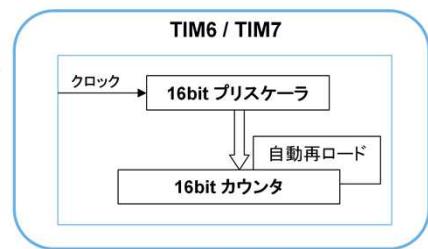

- TIM6とTIM7基本タイマ(出力なし)を使用しての最も簡単なオプション

- 汎用タイマを使用しての他の手段

- 比較イベントの使用

- 周期毎に複数のイベントを持つことが可能

- タイマのトリガ出力の使用

タイマの最も簡単な使い方は、内部のタイムベースを提供することです。これは、周期的な割込みまたはシングルショットタイマアウト保護のいずれかを提供するソフトウェアルーチンによって一般的に使用されます。タイマは、ADC、DACおよび他のタイマなどの他のオンチップペリフェラルに周期的なトリガを提供することも可能です。タイマからの更新イベント(通常、カウンタのオーバフロー)は、ソフトウェアのタイムベース割込みを持つためか、周期的なイベントをトリガするための一般的な手段です。基本的なタイマTIM6とTIM7は、入力/出力チャネルが無い最も単純なタイマ派生形であるので、そのようなタスクに最適です。それは、イベントを使用して比較し、または任意の他のタイマにトリガ出力を使用して、他のタイマを使用して内部タイミングを生成することも可能です。これは、他のタイマや比較イベントまたは他のタイマ上でトリガ出力を使い、内部タイミングの発生も可能です。複数のタイミングイベントの発生は、複数の比較チャネルを使用したシングルタイマで可能です。

# 入力キャプチャ

9

CPUオーバーヘッドを減少させる信号プリコンディショニングを含む

- 各チャンネルは、次の機能を入力キャプチャとして個別に設定することができます:

- 入力再マッピング(1つの入力を2つのキャプチャチャネルにマッピングすることが可能)

- プログラマブルエッジ感度(立ち上がり/立ち下がり/両方)

- イベントプリスケーラ(1/2/4/8イベント毎にキャプチャ)

- デジタルフィルタ(デバウンスおよびノイズ除去用)

- キャプチャイベントは、キャプチャレジスタに転送されるカウンタ値を発生し、割込みやDMA要求をトリガします。

- キャプチャレジスタがリードされずに上書きされている場合、オーバキャプチャフラグが設定されます。

このスライドは、インプットキャプチャ機能について説明します。各チャネルは、いくつかの信号コンディショニングオプションのあるインプットキャプチャとして、個別に構成することができます。入力は、2つのキャプチャチャネル(通常は、立ち下がりエッジのキャプチャから、立ち上がりエッジを区別するため)にマッピングすることができます。エッジ感度は、プログラム可能であり、立ち上がりエッジ、立ち下がりエッジまたは両エッジすることができます。イベントプリスケーラは、2、4または8イベント毎のキャプチャを可能にします。これは、高周波信号を処理する場合、CPUの負担を減少させ、複数の入力信号の周期にわたって行われるので、測定をより正確にすることができます。

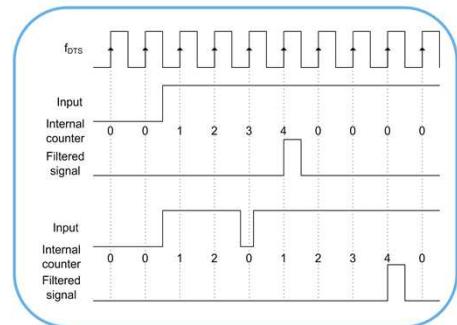

ノイズまたはバウンスによるスプリアス遷移イベントは、プログラム可能なデジタルフィルタを用いて除去することができます。図は、フィルタアクセプタンス4に設定されているときの信号をフィルタリングする方法を示しています。上のケースでは、きれいな立ち上がりエッジのキャプチャは、内部カウンタの値を見て通知することができるよう、立ち上がりエッジ後に4サンプリング周期トリガされます。下のケースでは、グリッチは、フィルタカウンタをリ

セットさせ、ハイレベルで4連続したサンプルがカウントされた後にキャプチャが行われます。

キャプチャトリガが発行されると、タイマのカウンタは、キャプチャレジスタに転送され、割込みやDMAリクエストを発行することができます。以前のものが読み込まれる前に新しいキャプチャが発生した場合は、キャプチャレジスタが上書きされ、オーバキャプチャフラグは、必要に応じて、この状態を管理するソフトウェアのために設定されます。

# 高度なキャプチャオプション

10

## ソフトウェアオーバーヘッド無しで直接測定

### ・クリアオン・キャプチャモード

- このモードでは、キャプチャがトリガされた後、カウンタは、直ぐにリセットすることができます。

### ・PWM入力モード

- タイマは、2つのキャプチャレジスタで信号のパルス幅と周期を直接キャプチャします。

### ・XOR機能付きクリアオン・キャプチャモード

- 最大3入力のエッジ間の間隔のキャプチャを可能にします。

→通常、電気モーターのホールセンサに使用されます。

このスライドは、いくつかのより高度なキャプチャ関連の機能を紹介します。

クリアオンキャプチャモードは、キャプチャがトリガされた後、直ぐに、カウンタリセットを発生させます。伝統的なフリーランニングカウンタが、トリガー後の期間を得るために追加の計算を必要とする一方で、これは、期間の直接測定を可能にします。

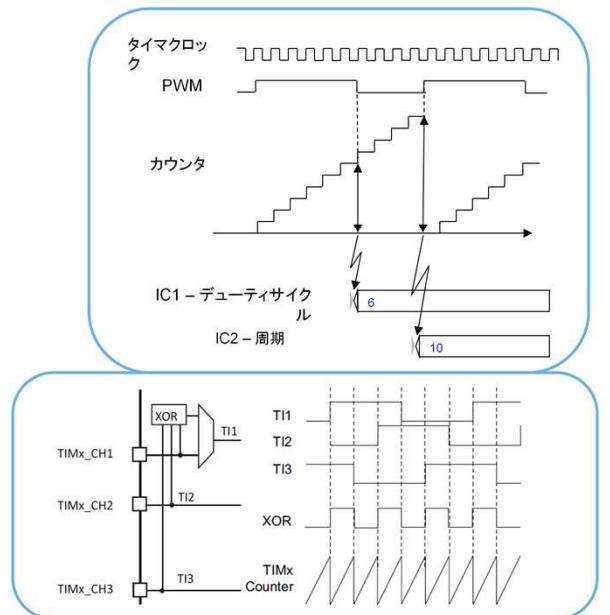

PWM入力モードでは、タイマは、入力PWM信号の周期とデューティサイクルの両方を取り込むことができます。入力信号は、内部で2つのキャプチャチャネルにルーティングされます。信号の立ち上がりエッジは、クリアオンキャプチャモードで周期の値を提供するために、インプットキャプチャ2上でキャプチャされます。立ち下がりエッジは、パルス長の継続時間を提供するキャプチャ1チャネルによってキャプチャされます。デューティサイクルは、単にインプットキャプチャ1とインプットキャプチャ2の比率に相当します。

タイマは、XORロジックで3つの入力チャンネルをまとめるXOR機能を有しています。これは、一般的には、電気モータのホールセンサからの3つの $120^\circ$ 位相シフトされた信号を処理するため

に使用されます。これは、三つの信号のそれぞれのすべてのエッジでの明確なキャプチャの発生と速度調節のために直接使用できるキャプチャ値を持つことが可能です。

# 出力コンペア

11

## 単純な出力波形や経過期間を示す

- カウンタがコンペアレジスタの値と一致した場合

- 対応する出力ピンは、次のようにプログラムすることができます

- セット

- リセット

- トグル

- 変化なし

- 割込みステータスレジスタにフラグを設定

- 対応するイネーブルビットが設定されている場合は、最終的に割込みやDMA要求を発生

- コンペアレジスタは、プリロードレジスタありまたはなしでプログラムすることができます。

- プログラムされた出力モードは、プリロードすることができます。

- 1つのモードから他のモードへグリッチの無い移行が可能

(通常、PWMからの連続オンまたはオフ状態へ)

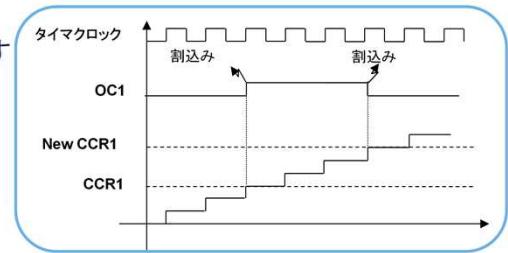

このスライドは、出力コンペア機能を紹介します。

カウンタがコンペアレジスタの値と一致したときに、比較イベントが発生します。このイベントは、割込みやDMA要求をトリガすることができます。出力セット、出力リセットまたは出力トグルにより対応する出力端子に反映させることができます。

比較レジスタは、プリロードすることができます。カウント期間中に複数の比較値が書き込まれなければならない場合、プリロードはディセーブルにする必要があります。逆に、プリロードモードは、次の値で比較レジスタを更新するソフトウェアのためのより高い時間的余裕を与えることから、リアルタイム制約のあるアプリケーションのために好まれるでしょう。カウンタがオーバフローまたはアンダフローしたとき、プリロードからアクティブ値への転送は、更新イベントによってトリガされます。出力比較モードは、例えば、強制オンまたはオフ状態にPWMモードからグリッチレスの移行を可能にするために、プリロードすることができます。

# ワンパルスモード

12

## 外部同期波形発生について

- カウンタは刺激に応答し、パルスを生成するために開始することができます

- プログラム可能な長さで

- プログラマブルな遅延の後

- 2つのソフトウェア・プログラマブル波形

- シングルパルス

- 繰り返しパルス

- 再トリガ可能オプション

- パルス幅は、新しいトリガにより拡張

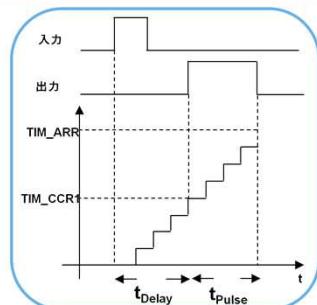

ワンパルスモードでは、外部イベントに応答してプログラム可能な長さのパルスを生成するために使用されます。入力トリガが来るかプログラマブル遅延の後直ぐに、パルスは開始することができます。オートリロードレジスタ(ARR)の値は、パルスの終了を定義し、コンペア1レジスタ(CCR1)の値は、パルスの開始時間を定義します。有効なパルス幅は、そのときARRおよびCCR1レジスタの値の差として定義されます。波形は、トリガによって生成された単一パルスを有するように、または单一のトリガによって開始された連続的なパルス列を有するようにプログラムすることができます。ワンパルスモードにも再トリガ可能なオプションを提供しています。この場合、パルスの終了前に届く新しいトリガは、カウンタをリセットし、パルス幅は、それに応じて拡張されます。

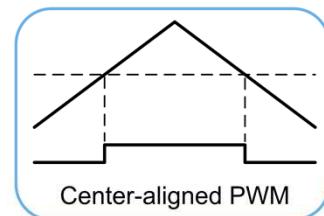

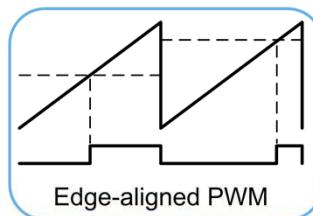

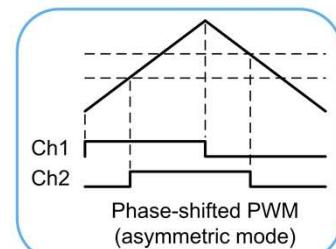

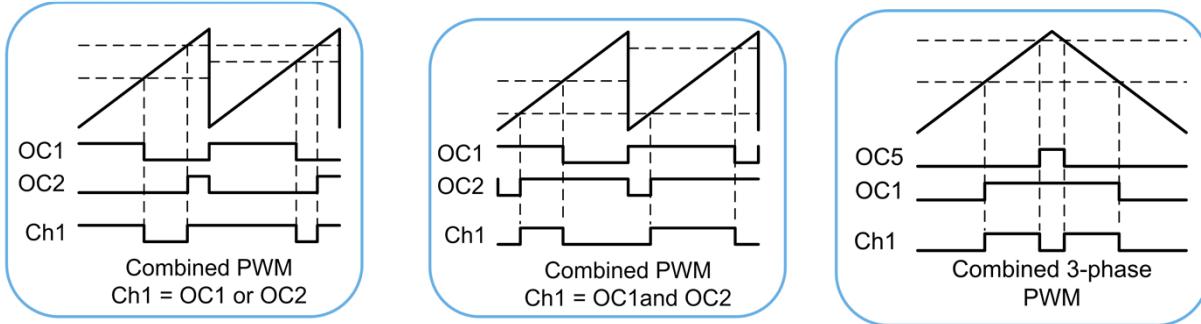

## 複数のアプリケーションに対処するための様々なPWMモード

- 基本的なPWM、エッジまたはセンターアライン

- 非対称センターアラインPWM

このスライドは、いくつかのPWMモードを紹介します。カウンタがアップまたはダウンのみのカウントモードで、標準のエッジアラインPWMモードは、周期を定義するオート再ロードレジスタとデューティサイクルを定義するコンペアレジスタでプログラムされます。シングルタイマは、独立したデューティサイクルと同一の周波数で4つのPWM信号まで生成することができます。複数のPWM波形が同じタイマにより生成されると、すべての立ち下がりエッジは同時に発生します。したがって、エッジアラインです。反対に、センターアラインのPWMの立ち上がりエッジと立ち下がりエッジは、スイッチング時間がデューティサイクル値で変化するため、カウンタロールオーバーと同期していません。これは、アップダウンモードでカウンタをプログラムすることによって達成されます。それは複数のPWMが、同じタイマで生成されたとき、スイッチングノイズを拡散させるこのモードは、興味深いです。これは、与えられたスイッチング周波数の電流リップルの周波数を2倍にすることができるので、電気モータをドライブする三相PWM生成のための重要な特長です。例えば、10 kHzのPWMは、聞こえない20 kHzの電流リップルを発生します。これは、サイレントPWM

動作を保証しながら、PWM周波数によるスイッチング損失を最小限に抑えることができます。センターアラインモードの異形は、非対称PWMモードです、ここで2つのコンペアレジスタは、PWM信号のターンオン、オフを定義します。これは、ターンオンおよびターンオフ時間が個別に定義されているので、パルス幅の設定のために、より高い分解能を提供します。また、フルブリッジ位相シフトされたトポロジに基づいてDC/ DCコンバータを駆動するのに必要な位相シフトPWM信号の生成を可能にします。この場合、タイマは同じ周波数、50%のデューティサイクル、および0~180°まで変化する位相シフトを有する2つのPWM信号を提供します。

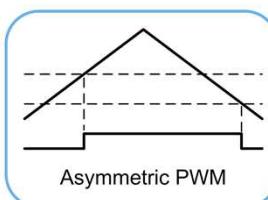

# より多くのPWMモード

14

PWM機能を拡張し、外部グルーロジックを回避

- コンバインPWMモード

- より複雑な波形のためにORまたはAND関数で2つのチャネルを結合

- コンバイン3相モード

- ゼロベクトルの挿入のために第4のPWMと通常の3相PWMとを組み合わせることが可能

このスライドは、コンバインPWMモードについて説明します。

このモードでは、2つのPWM信号の論理の組み合わせが隣接チャネルによって生成されることを可能にします（出力コンペア1と2、または、出力コンペア3と4）。PWMは、複雑な波形を生成するためにORやAND処理することができます。通常、これは、任意のパルス幅と任意の位相関係の値で生成される2つの周期的なパルスを持つことができます。

コンバイン3相モードは、具体的には3相モータ制御アプリケーションをターゲットとしています。この場合、タイマのチャネル5は、センターパターンPWM信号の中央にロー状態を挿入するために、3つのチャネル（1、2および3）のいずれかと組み合わせることができます。このモードでは、通常ゼロベクトル挿入と呼ばれる技術を使用して、3相モータの制御のための低成本電流検出技術の実装をとても簡素化します。

# 高度なPWMモード

15

## 外部制御を必要とするPWM信号

- 可変周波数PWM

- 外部信号によりドライブ

- サイクルバイサイクル制御デューティサイクル

- コンパレータまたは外部ピンによってドライブされる電流ループ

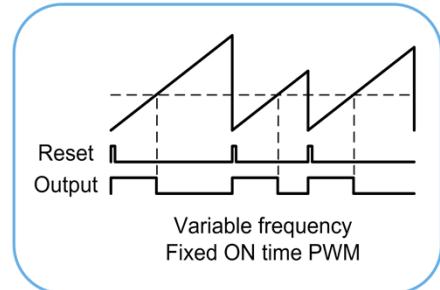

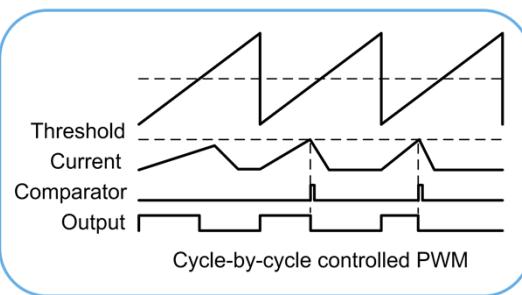

このスライドは、周波数またはデューティサイクルのいずれかが外部信号によって駆動することができる、いくつかのより具体的なPWMモードについて説明します。タイマは、ETRやチャネル1や2の入力のいずれかに接続された外部のリセット信号を使って、可変周波数信号を提供可能です。この信号の目的は、ハードウェアによって制御され連続的に調整された周波数と固定のOn-Off時間をもつ信号を提供することです。このタイマは、コンペアレジスタを使って、On(またはOff)時間の制御を提供します。それに対して、オート再ロードレジスタは、外部リセットがなくなった場合に、PWMが止まらないようにすることを保証し、境界条件で安全な制御を提供します。この技術は、主電源供給アプリケーションや電流制御デジタルLED照明のための遷移モードPFC(効率コントローラ)などの多様な目的に使用されます。タイマのための別のモードは、オンチップコンパレータまたはオフチップ信号のいずれかで、ハードウェアによって制御されるデューティーサイクルを持つためにあります。PWMは、固定の周波数で動作し、最大のデューティーサイクルは、サイクルバイサイクルで制御される実際の値とコンペアレジスタによって設定されます。これは、一

一般的には、DCモータまたはソレノイドをドライブするために、電流制御PWMを必要とするアプリケーションに使用されます。この場合、コンパレータは、負荷へのピーク電流値をモニタします。

電流がプログラムされたスレッショルドを超えると、コンパレータは、そのとき次のPWMの周期で自動的に再スタートされるPWM出力をリセットし、そして制御されたピーク電流値を提供します。

# カスケードタイマ 1/2

16

## 高柔軟性のためのスケーラブルな設計

- トリガコントローラは、マスタ/スレーブ設定で複数のタイマをカスケードする能力を提供します。

- スレーブ: トリガコントローラは、TRGI上の入力を収集

- 外部トリガピン(ETR)から

- ITRx上の他のオンチップリソースから

- 通常、他のタイマのTRGO出力

- マスタ: 内部タイマ信号は、TRGOに送信

- 指定されたタイマは、カスケード構成のスレーブとマスター mode で、同時に動作することができます。

このスライドは、タイマの同期機能について説明します。トリガコントローラは、マスタ/スレーブ設定で、複数のタイマをカスケードすることができます。タイマは、マスタとして1つまたはより多くのタイマをコントロールでき、または、スレーブとして他のタイマにより制御することができます。クロックとトリガコントローラは、タイマ間のリンクとして機能します。マスター mode では、オンチップTRGOトリガ出力への複数の内部制御信号を、タイマの外にリダイレクトできます。スレーブモードでは、外部トリガ端子(ETR)または他のTRGO出力に接続されたITR1からITR4の4つの内部トリガ入力の1つから来るTRGI上の複数の入力(メイントリガ入力)を収集します。また、入力キャプチャ1と2のピンは、内部のトリガーとして使用することができます(一般的にカウンタをリセットします)。スレーブとマスター mode は、独立にプログラムすることができます。指定されたタイマは、出力トリガを提供しながら入力トリガーを受け付けるカスケード構成とスレーブとマスター mode で、このように同時に動作することができます。

# カスケードタイマ 2/2

17

複数の信号がタイマ間で共有可能

- マスター モード: タイマは、TRGO出力の内部信号を伝えます。

- カウンタリセット、カウンタイネーブル、更新イベントまたはOC1比較一致

- OC1～OC4で生成された波形のいずれも

- スレーブ モード: タイマは、そのTRGI入力で制御されます。

- トリガモード: カウンタの開始が制御されます。

- リセットモード: TRGIの立ち上がりエッジは、カウンタを再初期化します。

- コンバインリセット & トリガモード (再トリガ可能ワンパルスモード向け)

- ゲートモード: カウンタのスタートとストップの両方が制御されます。

- その他のクロックに関するモード:

- 3つのエンコーダモード

- 外部クロック

このスライドは、いろいろな動作モードとタイマ間でやり取りされる信号を示します。

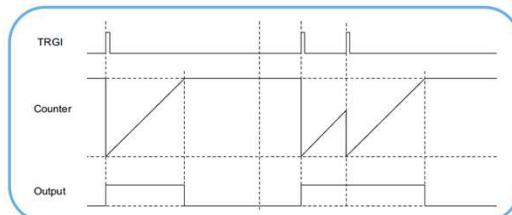

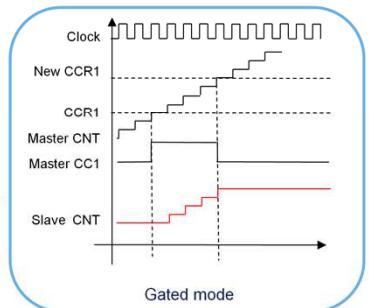

マスター モードでは、TRGO出力に送られるトリガ選択のために8つのオプションが与えられています。出力は、カウンタスタート、更新イベントまたはコンペア1一致イベントに対応するカウンタイネーブル、カウンタリセット時に発行されたシングル同期パルスとすることができます。あるいは、TRGO出力は、他のタイマモジュールに、PWM信号を含む生成された4波形のいずれかを送信することができます。スレーブ モードでは、タイマの動作モードがTRGI入力によって制御されます。トリガモードでは、カウンタのスタートは、外部から制御されます。このモードは、同時に複数のタイマを開始するために使用されます。リセットモードでは、カウンタは、通常、可変周波数PWM動作のために、TRGI入力の立ち上がりエッジでリセットされます。

リセットとトリガを含むコンバインモードは、再トリガ可能ワンパルスモード生成のために使用することができます。図に示すゲートモードでは、カウンタは、入力信号のレベルが高い間だけ有効です。

この信号は、入力または波形発生モードの別のタイマから来ています。この場合、リセット、イネーブル、更新、比較一致時に発行された同期パルスは、使用することはできません。最後に、スレーブモードの選択は、直交エンコーダのデコードまたは以前のプレゼンテーションで述べた外部クロックモードのようなクロック関連のモードを含んでいます。

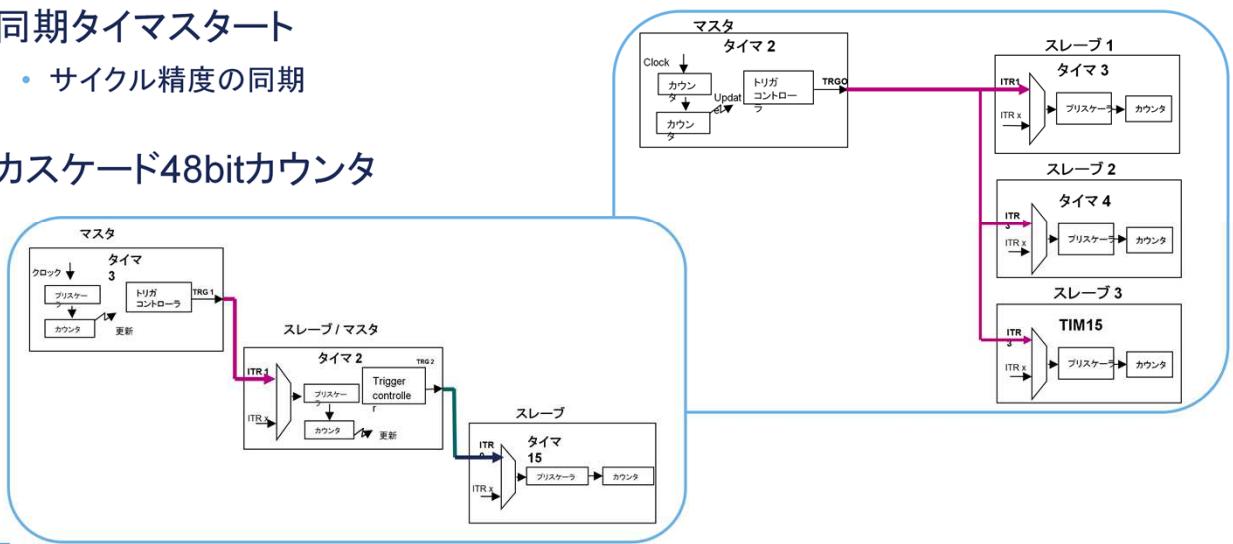

# 同期動作のサンプル

18

数個のタイマがより高い柔軟性で組合せ可能

- 同期タイマスタート

- サイクル精度の同期

- カスケード48bitカウンタ

このスライドは、同期動作の2つの例を示します。最初のサンプルは、4つのタイマを同時にスタートする方法について示します。メカニズムは、マスタータイマが、マスター/スレーブリンク遅延を補償するために、わずかに遅延してスタートし、サイクル精度で同期したすべてのタイマを持つことを可能にします。

第2のサンプルは、3つのタイマをカスケード接続することにより、48bitタイマを作成する方法を示します。

ここで、カウンタロールオーバーで生成された更新イベントは、次のスレーブタイマのために、入力クロックとして使われます。その結果、タイマ3のカウンタは最下位の16bitを保持し、タイマ2のカウンタは中間ビット(16~31ビット)を保持し、タイマ15は32~47ビットまでの上位ビットを保持します。

# モータ制御機能

19

STM32のタイマは、モータ駆動のすべての側面をカバー

- PWM 生成

- センターアラインとコンバイン3相モード

- デッドタイム挿入

- 6ステップモード

- 保護 (デュアルブレーキ緊急停止機構)

- スピード & 位置センシング

- エンコーダ、ホールセンサ、タコメータジェネレータのための専用モード

- ADC トリガ

このスライドは、タイマの4つの主要な電気モータ制御機能をまとめたものです。タイマは、電源スイッチを制御するための特定のPWMモードを含みます。先に述べられたセンターアラインとコンバイン3相PWMに加えて、タイマは、ブラシレスDCモータをドライブする6ステップモードと相補PWM生成のためのデッドタイム挿入を提供しています。これは、故障の場合にハードウェアでPWM出力を無効にするためのデュアルレベル緊急停止機構付パワー段保護回路を内蔵しています。それは、モータ制御システムに見られる最も一般的なセンサを扱うことができます。直交エンコーダおよびホールセンサは、粗密位置フィードバックのために使用され、タコメータジェネレータは、コスト効率の良い速度フィードバックと単に必要とされるクリアオンキャプチャモードのために使用されます。

最後に、タイマは、適切に電圧と電流センシングを管理することとパワー段でのスイッチングノイズの取り込み問題を回避することに必要な同期ADCトリガオプションを含みます。

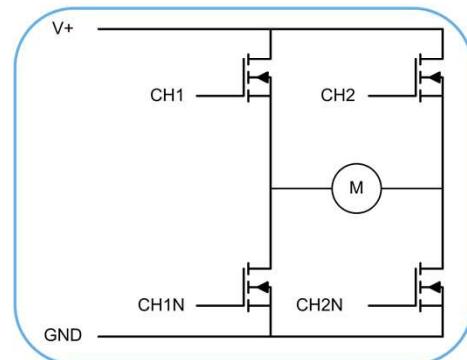

# デッドタイム挿入

20

## タイマあたり最大3つのハーフブリッジコンバータのダイレクトドライブ

- ハードウェアデッドタイムユニットは、非重複相補PWM信号を生成します

- 機能安全のためにデッドタイムレジスタ(読み取り専用)をロックする機能

- ハーフブリッジおよびフルブリッジ・コンバータでのクロスコンダクションの防止

- DC/DCコンバータ、DCモータ、3相ブラシレスモータ

フルブリッジ DCモータ ドライブ

このスライドは、デッドタイム挿入機能について説明します。ハードウェアデッドタイム発生器は、リファレンスPWM信号から非重複相補PWMを提供します。STM32タイマは、OC1、OC2とOC3チャネルの向けの最大3つのデッドタイム発生器を含んでいます。デッドタイムの期間は、8bitの値でプログラムされます。この値は、実行時に破損されることからこの重要な値を保護するために、ユーザーによってロックすることができます。これは、次のMCUのリセットまで読み取り専用モードにデッドタイムレジスタを切り替えるライトワンスロックビットをセットすることによって行われます。

デッドタイム挿入は、2つの電源レールとの間に直列に接続されている一対のトランジスタであるハーフブリッジを駆動する際に必要です。

この場合、アカウントの物理的なスイッチング特性を考慮して、もう一方の側をオフに切り替えることを可能にするために、一方をスイッチオンする前にある程度の時間を挿入する必要があります。

ハーフブリッジは、ここで示されているフルブリッジトポロジーまた

は3つのPWMペアの3相インバータのために使われるDCまたはステップモータ駆動のためのDC/ DCコンバータで通常見られます。

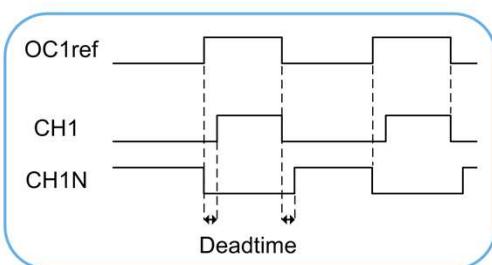

# 6ステップ / ブロックコミュニケーション

21

## BLDCモータドライブのためのCPUの負荷軽減

- 1つのタイマは、ホールセンサフィードバックを処理し、同期PWM生成のための高度なタイマをトリガすることができます。

このスライドは、6ステップドライブ(ブロックコミュニケーションとも呼ばれる)がSTM32タイマで管理されている方法を示しています。それは、他の1つが6つの連続したステップを生成しロータ角度の位置に同期したPWM生成を管理している間、1つが3つのホールセンサ信号を処理している、2つのタイマ回路で構成されています。

最初のタイマは、3つの入力によってトリガされるクリアオンキャプチャモードで動作します。コンペアレジスタ(ここではコンペア2)は、生の角度位置とコミュニケーション時間の間にプログラム可能な遅延を追加する責任があります。キャプチャレジスタ1は、連続したホールセンサのエッジ間のタイミング間隔を保持し、速度制御ループのために必要です。コンペア2マッチイベントは、TRGO出力を通してスレーブタイマに伝わります。これらのイベントは、コミュニケーションイベントおよびPWM生成のためのトリガの変化として機能します。シーケンスの6つのステップのそれぞれについて、6つの出力の状態は、アクティブまたは非アクティブに強制されるか、またはPWM信号を生成するかのいずれかに、定義されています。1つのステップから他への移行が、コミュニケーション割

込みルーチンで、ソフトウェアによってプリロードされ、そして、次のコミュニケーションが来たときの出力動作モードを再プログラムするためのハードウェアによって自動的に転送されます。右の図は、モータ位相のいずれかの電流とともに、完全な6ステップのシーケンスが二つ連続する6つのPWM信号を示しています。

# ブレーク機能 1/2

22

## ベストインクラスの保護機構

- ブレークイベントは、PWM出力をディセーブルします

- ハードウェアにより (最小の待ち時間)

- 非同期 (クロックレス動作、クロック関連の遅延なし)

- プログラマブルセーフステート (ハイ / ロー または Hi-Z)

- 相補出力でタイマ上で利用可能

- タイマ 1、8、15、16 と 17

- 2つのブレークチャネル (TIM1 と TIM8 のみ)

- デュアルレベルの保護機構が可能

- すべてがOFF出力または一部の出力が強制的にオンとオフ

- デッドタイムの挿入は、シートスルーのリスクのないことを保証

このスライドは、ブレーク機能について示します。ブレークイベントは、PWM出力を自動的にディセーブルするハードウェア保護機構をトリガし、そして、それらをローまたはハイでローインピーダンス、またはハイインピーダンスのいずれかのユーザ設定可能な状態に強制します。そのロジック回路は、クロック無しで非同期で動作します。これは、システムクロックに障害が発生した場合の機能性を保証し、さらに保護を遅延させる傾向があるクロックに関連する伝搬時間を回避します。

この機能は、電力変換タスクを実行することができる相補PWM出力を有するすべてのタイマで提供されています。(タイマ1、8、15、16、17)

タイマ1と8は、分離した2つのブレークチャネルを持ちます。これは、例えば、全てのスイッチのオフで低優先の保護は、ローサイドスイッチのアクティブで高い優先保護により上書きできるデュアルレベル保護機構を提供します。また、デッドタイム遅延は、電力段を安全に無効にするため、故障モードに入る直前に、挿入することができます。これは、潜在的なシートスルー状態を防ぎます。例えば、ハイサイドPWMがONのときに故障が発生し、そ

して安全状態がハイサイドスイッチがOFFでローサイドスイッチがONになるようにプログラムされるのを考えてみましょう。故障発生時、システムは最初にハイサイドPWMを無効にし、そしてローサイドのスイッチONの前にデッドタイムを挿入します。

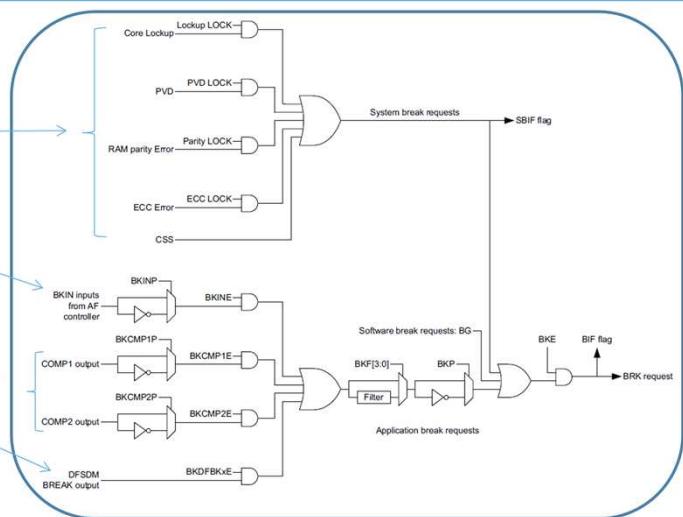

# ブレーク機能 2/2

23

## ワイドレンジ緊急停止入力

- 複数のソースの集約が可能:

- SoC レベルエラー

- ブレーク入力

- オンチップペリフェラル

- コンパレータ

- DFSDM

- デジタルフィルタ

- プログラム可能な極性

このスライドは、ブレーク機能の制御方法について示しています。複数のブレークソースは、ブレークイベントをトリガるためにまとめられています。次の5つのシステムレベルソースが選択可能です。コア・ロックアップ Cortex-M4 内部エラー、PVD(プログラマブル電圧検出器)低電圧エラー、SRAMパリティエラー、フラッシュメモリECCエラー、外部クロック障害を示すクロックセキュリティシステム(CSS)。ブレーク入力は、MCUピン配置上に、オルタネートファンクションコントローラで選択することができます。最後に、それらが範囲外の信号を検出したとき、2つの比較器とデジタルフィルタ(DFSDM)は、緊急停止ソースとして使用することもできます。外部ソースまたはオンチップコンパレータ信号は、ブレーク検出ユニットに入る前に調整することができます。これは、デジタルフィルタを用いて適切な極性とスプリアスグリッチの除去を選択することができます。

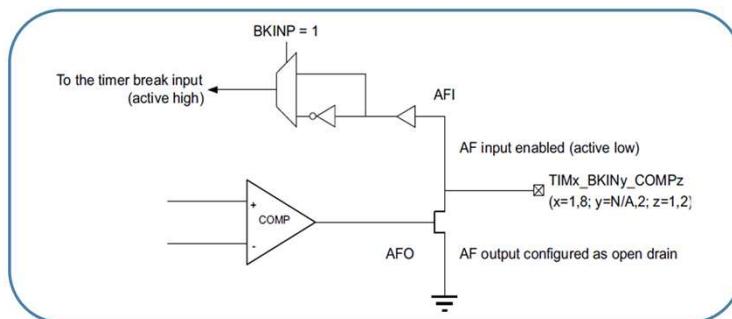

# 双方向ブレーク入力

24

## 最小のピン数で外部ICとの接続が可能

- 双方向ブレーク入力モードは、単一のピンがブレーク入力とコンパレータ出力の両方で動作させることができ、以下を提供します：

- 外部チップに内部の故障信号をエクスポートするオプション

- 単一ピンに内部と外部のブレーク信号をマージするオプション

(オープンドレイン出力で複数の比較器を使用して)

コンパレータからの定期的なデジタルブレーク入力と内部のブレークイベントの他に、図に示すように、タイマ1および8は、2つのソースを組み合わせた双方向ブレーク入力/出力を備えています。これらのピンは、タイマのブレーク入力とオープンドレインとして設定されたコンパレータ出力を兼ね備えています。単一のピンで、それらは、広域ブレーク情報が入力をシャットダウンする外部のMCUまたは外部ゲートドライバが利用できることを可能にします。これは、内部コンパレータと複数の外部オープンドレインコンパレータ出力が一緒にOR演算され、いくつかの内部および外部ブレーク入力をマージする必要がある場合に、ブレークイベントをトリガするためのオプションも用意されています。

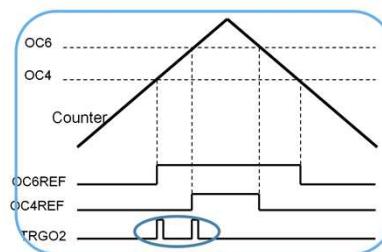

## ADCトリガの複数オプション

- ADCトリガ生成は、次を使用して管理できます：

- コンペアイベント

- TRGO 出力

- タイマ1と8は、ADC専用の追加 TRGO2出力を持っています。

- 16個の可能なトリガソース

- PWM周期毎にデュアルADCトリガが可能

- TRGOは同期目的のためにフリーです。

| Name | Source           |

|------|------------------|

| EXT0 | TIM1_CC1 event   |

| EXT1 | TIM1_CC2 event   |

| EXT2 | TIM1_CC3 event   |

| EXT3 | TIM2_CC2 event   |

| EXT4 | TIM3_TRGO event  |

| EXT5 | TIM4_CC4 event   |

| EXT6 | EXTI line 11     |

| EXT7 | TIM8_TRGO event  |

| EXT8 | TIM8_TRGO2 event |

このスライドは、タイマに関するADCトリガオプションについて示します。ADCは、3つのオプションで、STM32のタイマの大部分でトリガすることができます。これは、コンペアイベントを使用して行うことができます。ADC変換は、与えられた比較一致でスタートします。

サポートされたコンペアイベントのリストは、テーブル上に示すように、1つのタイマからその他へと変化します。

TRGOイベントは、特定のタイマで使用することができます。これは、TRGOが、レジスタ更新、カウンタリセットまたはトリガ入力としてコンペアイベントまたはタイマ内部制御信号のいずれかとすることができるので、特別な柔軟性を提供します。一方、これは、同期目的で使用されることからTRGOを防ぎます。このため、タイマ1と8はまた、追加のTRGO2出力を持ち、完全にADCトリガーに専念しています。TRGO2は、コンペアイベント4と6のイベントを組み合わせることにより、PWM周期ごとにデュアルトリガを持つ可能性と6つのコンペアイベントを含む16の可能性を提供しています。これは、複数のタイマ同期方式のためにTRGOの自由度も残します。

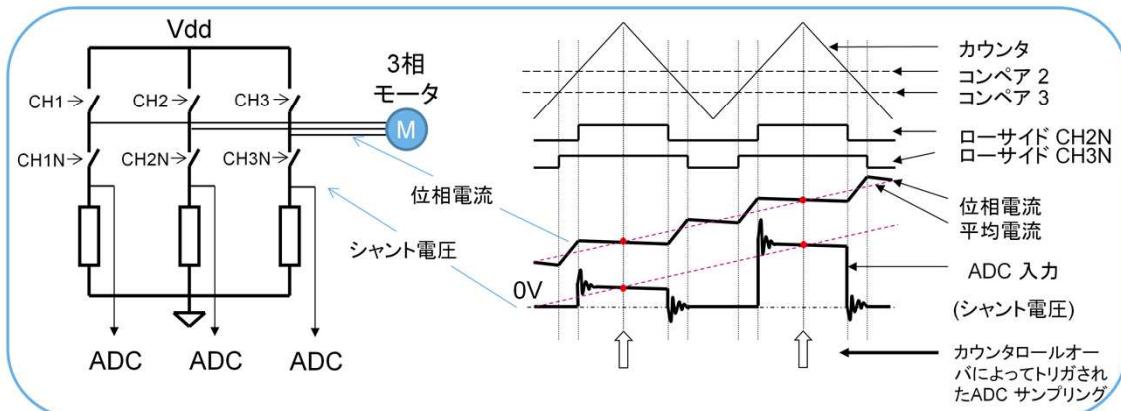

# ADC同期のサンプル

26

## ADC測定値のPWMに起因するノイズの回避

- 3相モータ制御アプリケーションでは、カウンタオーバーフローのADCトリガを使用すると、平均電流値を得ることができ、ノイズの多いADC変換を回避可能

このスライドは、PWM同期ADCトリガの例を示します。3相モータの制御のためには、電力段を制御するために生成されたPWMで同期されたADC測定値を持つことが必須です。これは、電流波形のリップルから平均値の抽出を可能にし、ADCの読み取りが、電源スイッチに起因するリングングから適切な距離で行われるのを確実にします。

ここで、左側に示されているのは、3相モータインバータです。6つのスイッチは、モータ巻線内の電流が、3つのハーフブリッジのボトム側に配置されたシャント抵抗を使用して測定されている間に挿入されたデッドタイムで3つの相補PWM対によって制御されています。右側には、タイマのカウンタ、コンペア1とコンペア2の値とCH1NとCH2Nによって制御されるローサイドスイッチに対応するPWM出力を示しています。下の2つの波形は、モータ位相の電流とシャント抵抗で得られる電流のイメージが示されています。この低成本の接続形態で、電圧はローサイドスイッチがONのときのみ測定でき、ADC入力で得られる矩形波状の信号を説明しています。これは、読み取りは期間の途中で正確に行われ、かなりのリップルがある信号の平均値を取得することができます。

加えて、PWM同期ADCトリガを使用すると、ADC変換がシャント電圧に存在するリングングノイズから離れて行われることを保証します。

# 割込みとDMA

27

| イベント                                                         | 割込み | DMA | 説明                                                                             |

|--------------------------------------------------------------|-----|-----|--------------------------------------------------------------------------------|

| アップデート                                                       | Yes | Yes | 強制的ソフトウェア更新要求の場合やカウンタがオーバーフローまたはアンダーフロー時に発行                                    |

| キャプチャ/コンペア 1<br>キャプチャ/コンペア 2<br>キャプチャ/コンペア 3<br>キャプチャ/コンペア 4 | Yes | Yes | 比較一致やキャプチャがトリガされたときに発行。各キャプチャ / コンペアチャネルは、それら自身の割込みと DMA のイネーブルビットとフラグを持っています。 |

| トリガ                                                          | Yes | Yes | トリガイベントについて発行 (内部トリガ入力ITRx、TI1 エッジ検出器、フィルタされたTI1/TI2または外部トリガ入力ピン)              |

| コム(Com)                                                      | Yes | Yes |                                                                                |

| ブレーク                                                         | Yes | No  | タイマ1、8、15、16、17のみ                                                              |

このスライドは、割込みやDMAリクエストソースについて示しています。ほとんどのイベントは、2つ同時に、割込みやDMAリクエストのいずれかを発生させることができます。カウンタがオーバーフローまたはアンダーフローしたときにアップデートが発行されます。これは主に、PWM周期の開始時にタイマの実行時の設定を更新し、次のレジスタの更新前の間隔を最大化するために使用されます。繰り返しカウンタを使用すると、いくつかのPWM周期をスキップして、高いPWM周波数での割込みやDMAリクエストの数を減らすことができます。4つのキャプチャ/コンペアイベントの各々はそれら自身の割込みとDMAを持っています。TRGI入力のトリガイベントは、割込みまたはDMAリクエストをトリガすることも可能です。最後に、割込みやDMAリクエストの追加のソースは、コミュニケーションとタイマ1、8、15、16、17のブレークイベントのみです。ブレークイベントは、DMAリクエストを生成しないことに注意してください。

# DMA バーストモード

28

## タイマの動的再コンフィギュレーション

- シングルDMAイベントで複数のレジスタの更新

- DMAの効率的な使用(シングルストリームが必要)

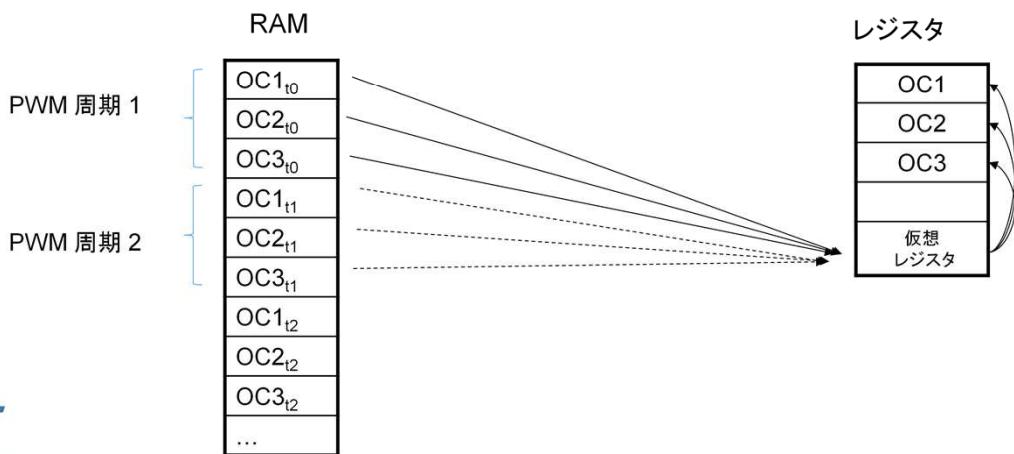

タイマは、シングルDMAストリームで複数のレジスタを再プログラムするためのDMAバーストモードが含まれています。これは、コンフィギュレーションレジスタに書き込むことによって動的にタイマの設定を変更するか、または同時に複数の実行時パラメータ変更(例えば、複数のチャネルのデューティサイクルと周波数)が可能です。

サンプルでは、3つの比較値を含むテーブルが、新しいPWM周期が始まるときに、シングルDMAストリームでコンペアレジスタに転送できる方法を示しています。

DMAは、タイマのユニークな場所(仮想レジスタTIMx\_DMAR)を指し示すペリフェラルモードのためのメモリにプログラムされる必要があります。アップデートイベントが発生すると、タイマがプログラマされたバースト長に相当するDMAリクエストの数を送信します。それぞれの値は、自動的に仮想レジスタからターゲットのアクティブルジスタにリダイレクトされます。次回のアップデートイベントでは、3つの新しい比較値が再度転送されます。この例では、このメカニズムは、更新スキームに通常必要となる2つのDMAストリームを節約します。

## ローパワー・モード

29

| モード                            | 説明                                           |

|--------------------------------|----------------------------------------------|

| ラン(Run)                        | アクティブ。                                       |

| スリープ(Sleep)                    | アクティブ。ペリフェラルの割込みは、デバイスをスリープモードから復帰させます。      |

| ローパワー・ラン<br>(Low-power run)    | アクティブ。                                       |

| ローパワースリープ<br>(Low-power sleep) | アクティブ。ペリフェラルの割込みは、デバイスをローパワースリープモードから復帰させます。 |

| ストップ1(Stop 1)                  | フリーズ。ペリフェラルレジスタの内容は、保持されます。                  |

| ストップ2(Stop 2)                  | フリーズ。ペリフェラルレジスタの内容は、保持されます。                  |

| スタンバイ(Standby)                 | パワーダウン。ペリフェラルは、スタンバイモード終了後、再初期化する必要があります。    |

| シャットダウン(Shutdown)              | パワーダウン。ペリフェラルは、シャットダウンモード終了後、再初期化する必要があります。  |

タイマは、ランとスリープモードのいずれかでアクティブで、ストップモード中でフリーズされます。タイマ状態とレジスタの内容は保存され、MCUはウェイクアップされたとき、タイマは直接動作を再開します。

スタンバイおよびシャットダウンモードでは、タイマはパワーダウンされ、これらのモードからの復帰時に完全に再初期化する必要があります。

## 電力変換アプリケーションの安全なデバッグが可能

- 各タイマについて、DBGMCUモジュールのDBG\_TIMx\_STOPコンフィギュレーションビットは、マイクロコントローラがデバッグモード(Cortex®-M4コア休止)に入ったとき、タイマがどのように動作するかを設定できます。

- $\text{DBG\_TIMx\_STOP} = 0$

- TIMxカウンタ動作は、維持されます。

- $\text{DBG\_TIMx\_STOP} = 1$

- コアが休止したとき、カウンタのクロックは、停止しています。

- 相補出力を持つタイマの場合、出力は無効になります。

デバッグモード時のタイマの状態は、タイマ毎にコンフィギュレーションビットを設定することができます。デバッグビットがリセットされると、タイマクロックは、ブレーキポイントの間、維持されます。デバッグビットがセットされると、タイマのカウンタは、コアが休止されると直ぐに停止されます。さらに、相補出力を持つタイマの出力が無効になり、非アクティブな状態に強制されます。この機能は、タイマが電源スイッチまたは電気モーターを制御しているアプリケーションのために極めて有用です。これは、過剰な電流、または、モーターがブレーキポイントにヒットしたときに制御されていない状態で放置されることによる損傷から電力段を保護します。

# 便利な数式 1/2

31

## • PWM周波数設定

- オート再ロード(TIMx\_ARRのARR)とクロックプリスケーラ(TIMx\_PSCのPSC)で定義:

$$f_{PWM} = \frac{f_{TIM}}{(ARR + 1) \times (PSC + 1)}$$

- 実際には、一つはPSC =0で始まる必要あり(プリスケーラなし):

$$ARR = \frac{f_{TIM}}{f_{PWM} \times (PSC + 1)} - 1 \rightarrow ARR = \frac{f_{TIM}}{f_{PWM}} - 1$$

- 16bit(または32bit)の範囲を超える値の場合、PSCはARRに合うまで増加させる必要あり:

$$ARR = \frac{f_{TIM}/2}{f_{PWM}} - 1 \rightarrow ARR = \frac{f_{TIM}/3}{f_{PWM}} - 1 \rightarrow ARR = \frac{f_{TIM}/4}{f_{PWM}} - 1 \rightarrow \dots$$

このスライドは、タイマのPWM周波数の設定方法について説明しています。このパラメータは、TIMx\_ARRレジスタにプログラムされた自動再ロード値とTIMx\_PSCレジスタにプログラムされたクロックプリスケーラを使って、定義されています。PWM周波数は、タイマ動作周波数 $f_{TIM}$ が $ARR+1$ とクロックプリスケーラ+1を掛け合わせたものによって割られることにより与えられます。

具体的には、両方のレジスタの値を見つけることは、反復プロセスで、1つは、PSC=0からスタートする必要があり、すなわちクロック分周なしです。これは、PWMが可能な限り細かい分解能をもつことが保証されます。

この場合、ARRの値は、タイマクロック周波数とPWM周波数間の単純な比率マイナス1です。

この式は、タイマのARRの範囲を超えるARR値が得られた場合は、16bitまたは32bitのいずれかの選択されたタイマに応じて、計算は次の順序で、高いプリスケーラ値で再実行する必要があります。

ARR値がPWM周波数分のタイマクロック周波数/2マイナス1に

等しい、そして、ARR値がPWM周波数分のタイマクロック周波数/3マイナス1に等しい、というようにARR値がプログラム可能な範囲内に収まるポイントまで。

## 便利な数式 2/2

32

- デューティサイクル設定

- オート再ロード(TIMx\_ARRのARR)とコンペア(TIMx\_CCRxのPSC)値で定義:

$$Duty\ Cycle = \frac{CCRx + 1}{ARR + 1} \rightarrow CCRx = (Duty\ Cycle \times (ARR + 1)) - 1$$

- PWM 分解能

- 分解能は、可能なデューティサイクル値の数を与え、PWM信号を詳細に制御する方法を示します:

$$Res_{(steps)} = \frac{f_{TIM}}{f_{PWM}}$$

- DAC変換器出力の分解能を与えるビットで表現する別 の方法:

$$Res_{(bits)} = \log_2\left(\frac{f_{TIM}}{f_{PWM}}\right)$$

このスライドは、与えられたPWM周波数のデューティサイクルをプログラムする方法について説明します。

このパラメータは、TIMx\_ARRレジスタにプログラムされた自動再ロード値(ARR)とTIMx\_CCRxレジスタにプログラムされた比較値を使用して定義されています。

デューティサイクルは、PWM周波数に依存せず、自動再ロード値+1以上の比較値+1で与えられます。

別の有用な指標は、PWM分解能です。これは、可能なデューティサイクル値の数を与え、PWM信号の詳細に制御する方法を示します。デューティサイクルのステップ数で表現される分解能は、タイマクロック周波数とPWM周波数との間の比率(-1)に単に等しいです。DAC変換器出力の分解能を与えるビットで表現する別 の方法では、解像度は、タイマクロック周波数とPWM周波数との間の比率(-1)の2を底とする対数です。

# アプリケーションのサンプル: LEDの調光

33

- これは、定格出力電流を超えない電流の範囲で、PWM出力を直接使って行われます。

- PWM 周波数: 1 kHz

- 周波数:  $ARR = \frac{f_{TIM}}{f_{PWM}} - 1 = \frac{80MHz}{1kHz} - 1 = 79999$

- ARRは、最大16bitの値以上

→ プリスケーラは、1に設定する必要があります

- $ARR = \frac{f_{TIM}/2}{f_{PWM}} - 1 \rightarrow ARR = \frac{80MHz/2}{1kHz} - 1 = 39999$

- 開始時のデューティサイクル = 20%

- $Duty\ Cycle = \frac{CCRx+1}{ARR+1} \rightarrow CCRx = ((ARR + 1) \times Duty\ Cycle) - 1 = ((40001) \times 0.2) - 1 \cong 7999$

- 調光の分解能

- $40000\ steps\ or\ log_2(40000) = 15.3\ bits$

このスライドは、低消費電力LEDの調光のためのPWM使用の簡単な具体例を示しています。これは、定格出力電流を超えない電流の範囲で、PWM出力を直接使って行われます。第1ステップは、1 kHzに設定される、周波数をプログラムすることです。

プリスケーラ無しと80MHzのタイマ動作周波数でARR値の計算を行う場合、得られた値は、タイマ1で使用することができる16bitの範囲を超える79999です。

タイマプリスケーラは、40MHzのタイマ動作周波数を持つために1に設定する必要があり、そしてARRレジスタにとって有効な値39999になります。

第2ステップは、20%のデューティサイクルを持つようにコンペアレジスタ値を計算することからなっています。これは、7999の値が得られます。

最後に、調光の分解能は、前のスライドに示した式から計算することができます。タイマは、40 MHzで動作し、1 kHzのPWMは、15.3ビットと同等の分解能に対応する40000の調光ステップを提供します。

## アプリケーションのヒント

34

- タイマ全体が設定され、カウンタが開始され、PWMモードがイネーブルにされ、同様に対応する出力も、しかし、ピンは何も動いていない....

→ MOEビットを設定することを検討しましたか？

- デッドタイム生成器を装備したタイマ(タイマ1、8、15、16、17)では、TIMx\_BDTRレジスタのメイン出力イネーブル(MOE)ビットは、すべての出力をコントロールし、ブレーク入力上の障害検出のサーキットブレーカとして動作します(すべてのPWM出力の広範なディセーブル)

→ MOEビットは、出力をイネーブルにするために設定する必要があります。

→ これはタイマがデッドタイム挿入なしに使用した場合であっても有効です。

このスライドは、全体のタイマが設定され、カウンタが開始され、PWMモードがイネーブルにされ、同様に対応する出力も、それでもピンは何の動きが無いといった一般的なサポートケースについて説明します。通常、これは、MOEビットが設定されていないことによります。デッドタイム発生器を装備するタイマ(タイマ1、8、15、16、17)については、TIMx\_BDTRレジスタのメイン出力イネーブル(MOE)ビットは、全ての出力をコントロールしブレーク入力上の障害検出のサーキットブレーカとして動作します。(すべてのPWM出力の広範なディセーブル) MOEビットは、出力をイネーブルにするために設定する必要があります。これは、タイマがデッドタイム挿入なしに使用した場合であっても有効で、タイマは、一般目的のアプリケーションに使用されます。

## 関連ペリフェラル

35

- タイマにリンクされている以下のペリフェラルのためのトレーニング資料を参照してください:

- ADC

- タイマは、インジェクテッドと通常変換をトリガします。

- PWMは、アナログウォッチドッグにより停止させることが可能

- DAC

- タイマは、変換をトリガします。

- COMP

- コンパレータは、PWM信号をシャットダウンするためのブレークソースとして機能します。

- DFSDM

- DFSDMは、PWM信号をシャットダウンするためのブレークソースとして機能します。

タイマは、複数のオンチップペリフェラルにリンクされています。ADCやDACのトリガソースとして動作します。それは、PWM信号をシャットダウンするために使われるADCのアナログウォッチドッグ、コンパレータまたはDFSDMフィルタからの信号も受信します。

# STM32L4 タイマの特徴

36

|                         | カウンタ分解能 | カウンタタイプ | PWMモード           | デッドタイムとブレーク入力 | DMA | キャプチャコンペアチャネル | 同期  |      |

|-------------------------|---------|---------|------------------|---------------|-----|---------------|-----|------|

|                         |         |         |                  |               |     |               | マスタ | スレーブ |

| 高度な制御<br>TIM1 and TIM8  | 16bit   | アップ/ダウン | スタンダード+コンバイン+非対称 | Yes           | Yes | 6             | Yes | Yes  |

| 一般用途<br>TIM2 and TIM5   | 32bit   | アップ/ダウン | スタンダード+コンバイン+非対称 | No            | Yes | 4             | Yes | Yes  |

| 一般用途<br>TIM3 and TIM4   | 16bit   | アップ/ダウン | スタンダード+コンバイン+非対称 | No            | Yes | 4             | Yes | Yes  |

| 一般用途<br>TIM15           | 16bit   | アップ     | スタンダード+コンバイン     | Yes           | No  | 2             | Yes | Yes  |

| 一般用途<br>TIM16 and TIM17 | 16bit   | アップ     | スタンダード           | Yes           | No  | 1             | Yes | No   |

| 基本<br>TIM6 and TIM7     | 16bit   | アップ     | スタンダード           | No            | Yes | 0             | No  | No   |

このスライドは、STM32L4に存在するタイマの実例を示しています。

タイマ1と8は、全てのPWMオプションと3相PWM信号と2つの独立したADCトリガを同時に生成することを可能にする6つのコンペアチャネルを含み、モータコントロールの能力のある、フル機能のタイマです。タイマ2、3、4と5は、全てのPWMモード、アップ・ダウンカウント能力と4チャネルを含む一般用途のタイマです。タイマ2、5は、さらに32bitのカウントレンジを提供します。タイマ15、16と17は、標準のPWMのみのサポート、1と2チャネルとアップカウントモードのみのライトタイマです。追加の独立したタイムベースが必要な時はいつでも、それらは他のタイマを補完します。また、デッドタイム挿入と1つのPWMペアだけでシンプルな電源システムを駆動するためのブレーク入力を持っています。

最後に、タイマ6と7は、主にDAC変換器をトリガするかまたはソフトウェアのタイムベースを提供することを目的とした、出力のない純粹なタイムベースです。

- 詳細については、以下の資料を参照してください:

- AN2592

- STM32F10xとSTM32L15xマイクロコントローラのリンクシステムを使用して32bitタイマの分解能を実現する方法 (ソフトウェア: STSW-STM32009)

- AN4013

- STM32F0, STM32F1, STM32F2, STM32F4, STM32L1 シリーズ, STM32F30x, STM32F3x8, STM32F373 ラインのタイマの概要

- AN4507

- STM32の高度な構成、汎用およびライトタイマのためのディザリング技術によるPWMの分解能向上 (ソフトウェア: STSW-STM32151)

AN2592は、二つの同期16bitタイマで作られた32bitタイマの実用的な実装を提供し、より全体的なタイマ同期メカニズムを理解するのに有用です。これは、ソフトウェアサンプルのダウンロードも可能です。AN4013は、すべてのタイマ機能と利用可能なファームウェアのサンプルについてより詳細な概要を提供します。AN4507は、ディザリング技術によるPWMの分解能向上の実装を提供します。これは、ソフトウェアサンプルのダウンロードも可能です。