# STM32L4 - SDMMC

SD/SDIO/MMCホスト・インターフェース

Revision 1

Jan - 2016

こんにちは、そして、[CLICK 1] STM32 SDMMCコントローラ・モジュールのこのプレゼンテーションへようこそ。

CPUをSDカードやMMCカード、またはSDIOデバイスに接続するのに用いられるコントローラの主要な特徴を説明します。

# 概要

2

- マルチメディアカード(MMC)、セキュアデジタル(SD)メモリカードとSD I/Oデバイス(SDIO)の通信インターフェースを提供

- 完全に設定が可変

- SD (2.0)、SDIO (2.0)、MMC (4.2)仕様に準拠

## アプリケーションの利点

- デフォルト速度(<25MHz)と高速カードとデバイス(最高50MHz)に適用

- 必要なピンは数本のみ

- データストレージを簡単に拡張可能

STM32製品[CLICK 1]に搭載されているSDMMCコントローラは、マイクロコントローラをマルチメディアカード、SDメモリカードとSDIOデバイスとの通信インターフェースを提供します。このインターフェースは完全に可変です。そして、外部メモリへ容易に接続できます。そして、より多くのストレージ(メモリ)が必要であるとき、大量の記憶容量を広げることができます。

メモリカードでインターフェースに必要とされるピン数を少なくできることは、アプリケーションにとって大きな利点です。

[CLICK 2]。

SDMMCインターフェースのおかげで、アプリケーションは外部Flashメモリで高速読み込み及び書き込み動作を容易に管理することができます。

## 主な特徴

3

- SDMMCホスト特徴

- 1-bit, 4-bit と8bit データバスモードに適用

- DMA経由の読み出し/書き込みをサポート(CPUは無負荷)

- クロック発生器で最大50MHzを設定可能

- 節電機能サポート

- SDIOはマルチバイト、読み出し待ち、サスPEND/再開機能のような操作に適用可

STM32に搭載されたSDMMCコントローラは、強化されたデータ処理能力のための1ビットモード(デフォルト)、4ビットモード、および8ビットモードのデータ・バス幅をサポートします。

SDMMCインターフェースは、データ読み出し/書き込みの期間にCPUに負荷をかけないために、DMAと相互接続されています。.. [Click 1]

SDMMCクロック・ジェネレータは、初期設定フェーズのための最高400kHz、および高速なモードをサポートしているカードのための最高50MHzの信号を生成できます。

電力消費量を改善するために、SDMMCコマンドとデータ・バスがアイドルな時には、SDMMCクロックは止めることができます。.. [Click 2]

SDMMCコントローラは、SD I/Oモジュールとインターフェースをとることができます、高機能としては、読み出し待ちやサス

ペンド/再開操作、標準機能としてはマルチバイト転送や1と4ビットモードの割込み信号です。

## ブロック図

4

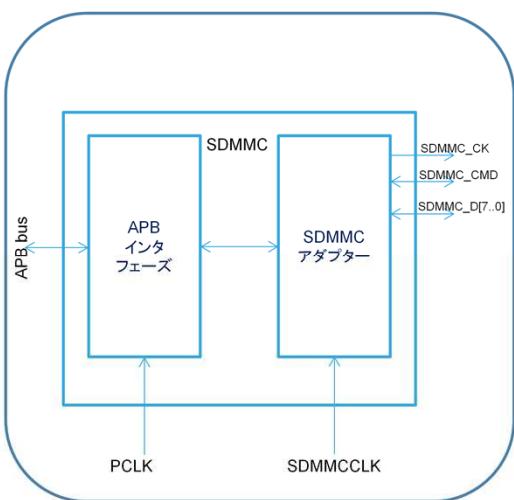

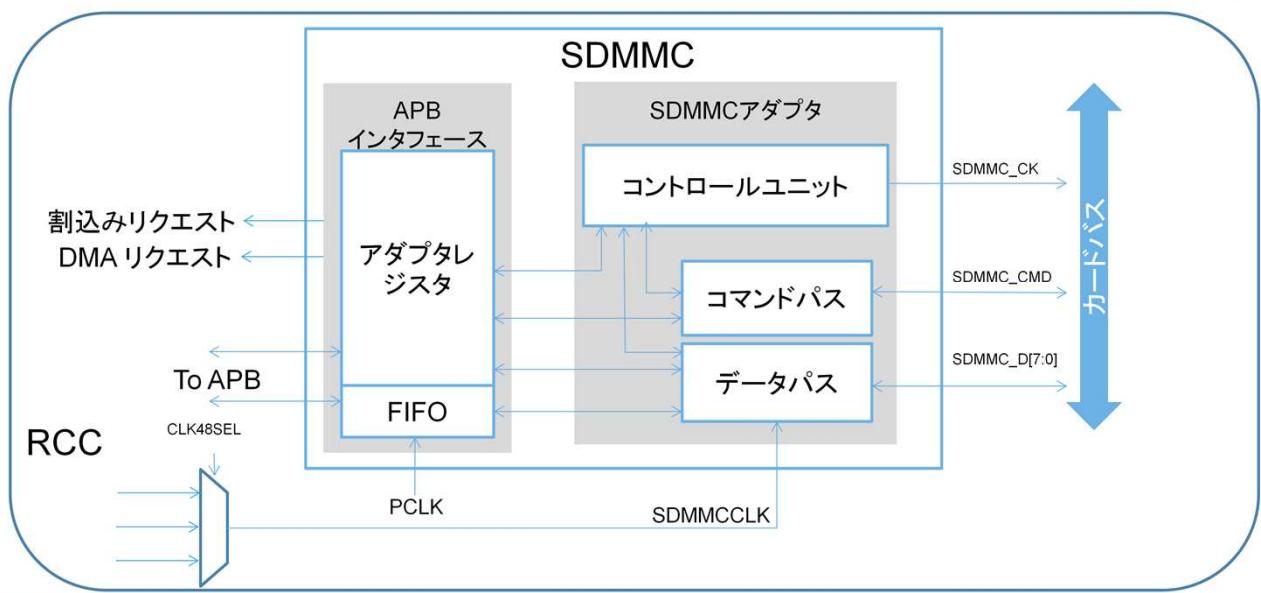

SDMMCコントローラは、カードでインターフェースに必要なすべてのSD/SDIOとMMC機能を提供するSD/MMCバス・マスターです。[クリック1]

それは、「SDMMCアダプター」とおよび「APBインターフェース」から構成されます。[クリック2]

DMAと割込み要求信号と同様に、「SDMMCアダプター」が「APBインターフェース」がコントロールとステータスレジスターと FIFOバッファを管理する間に、クロック生成、コマンド、データ転送のような機能を提供します。[クリック3]

2つのクロックがSDMMCコントローラで利用可能です。「APBインターフェース」のためのAPBクロック(PCLK)と「SDMMCアダプター」のためのSDMMCクロック(SDMMCCLK)です。

## コントロールユニット

5

- SDMMC\_CKクロック(最大50 MHz)はクロックコントロールモジュールで管理されます

- SDMMC\_CKは8bit プリスケーラ、または、クロックバイパスモードを使用できます(カードはSDMMCCCLKで直接クロックされます)

- 節電モード: SDMMC\_CKクロック出力はバスがアイドル状態のときに無効化が可能です。

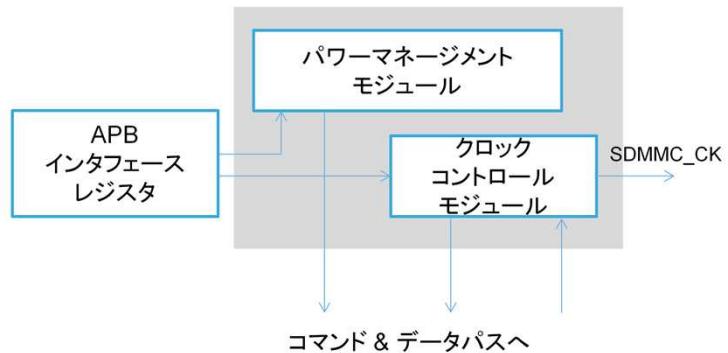

SDMMCアダプタはコントロールユニットを持っています。

[Click 1] その中には、パワーマネージメント機能用のモジュールとカードクロック(SDMMC\_CK)用のクロック分周期付きのクロックコントローラを含みます。

クロックコントロールモジュールはSDMMC\_CKクロック生成用の8bit のプリスケーラ(1/2SDMMCCCLKも生成可能)を提供します。

それはまた、最大50MHz通信用のバイパスモードも提供します。

コントロールユニットはバスがアイドル状態の時に、SDMMC\_CK 生成を無効にできます。

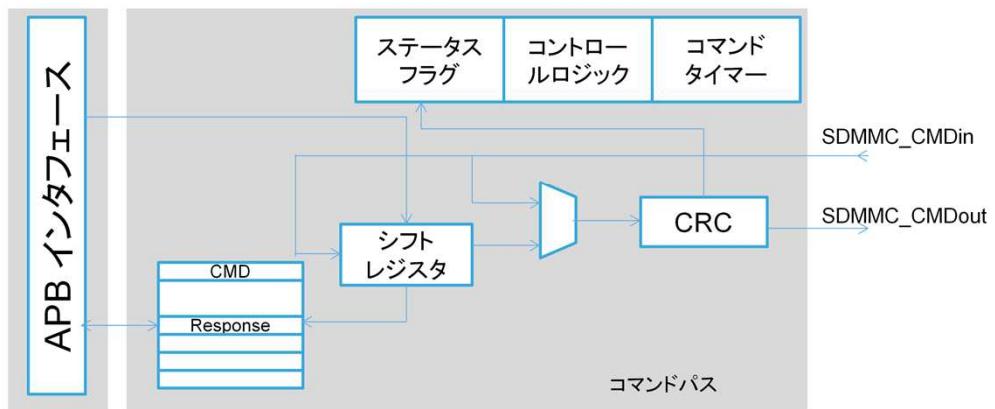

コマンドパス回路は、コマンド／レスポンスシーケンスのプログラムを作るために使用されます。

可能な場合には、コマンドパスはSDMMC\_CMDピンからコマンドインデックスとアーギュメントをシフトアウトします。

最後のペイロードビットが送られた後、終わりのビットを生成する前に、バスにはCRC7が計算されて、送られます。

反応が予期される時には、コマンドパスはSDMMC\_CMDinに設定されて、デバイスの反応を待つ。

# コマンドパスステートマシン

7

## ステートと遷移条件

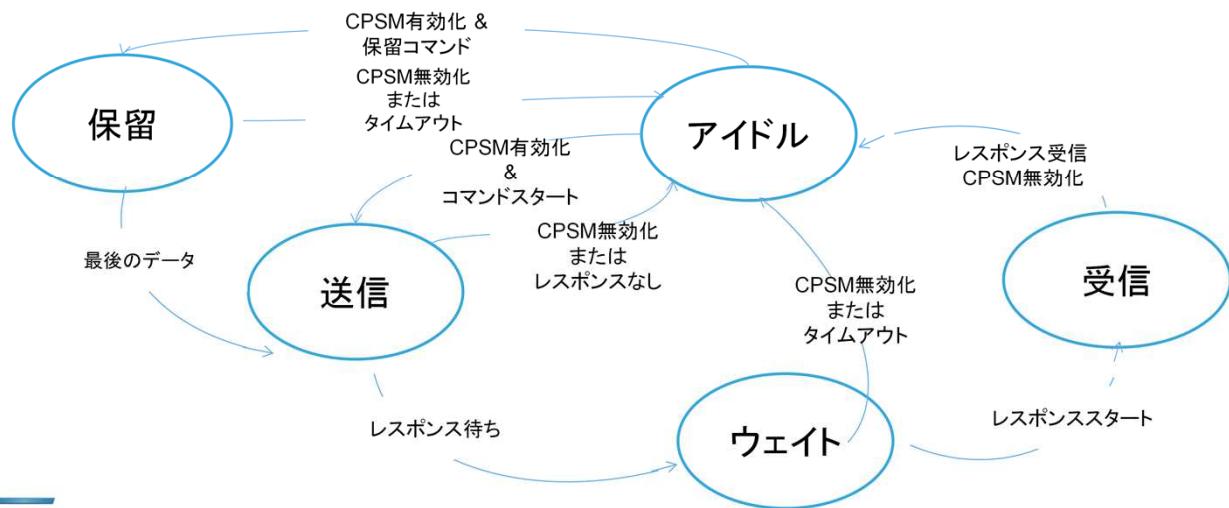

コマンドのトランスマッショントレセプションは、コマンドパスステートマシン(CPSM)によりコントロールされます。[Click 1] コマンドまたはレスポンスが全く進行していない時には、コマンドパスはアイドル状態にあります。.. [Click 2]

CPSMがコマンドを送ることが可能になると、コマンドパスは、コマンドの最後のビットが送られるまで、そして、期待されたレスポンスかどうかによって、送信状態に移行します。[Click 3]

どのレスポンスも、期待された[Click 4]ものではない時には、CPSMはアイドル状態に戻るか、またはコマンドピンのスタートビットのためにウェイト状態、および待ちに移行できます(レスポンストラニスマッショントの開始)。[Click 5]

割り当てられた時間期間以内にレスポンススタートビットが検出された時には、CPSMは、受信状態に移行します。.. [Click 6]

レスポンスの最後のビットを受け取った後に、CPSMは、受信したCRCを使ってレスポンスの完全性を確認し、それから、

アイドル状態に戻ります。[Click 7]

もしレスポンススタートが検出されないならば、CPSMは、タイムアウトの後にアイドル状態に戻ります。[Click 8]

CPSMは、最終データ転送と同期したコマンドを送るように設定できます。この機能が可能な時には、CPSMは保留の状態に移行し、MMCストリーム転送の終わりを待ちます。[Click 9]

最後のデータ信号がデータバスによりトリガされる時には、CPSMは、送信状態に移行します。

# サポートされているコマンド

8

どのようなカードとでも互換性有り

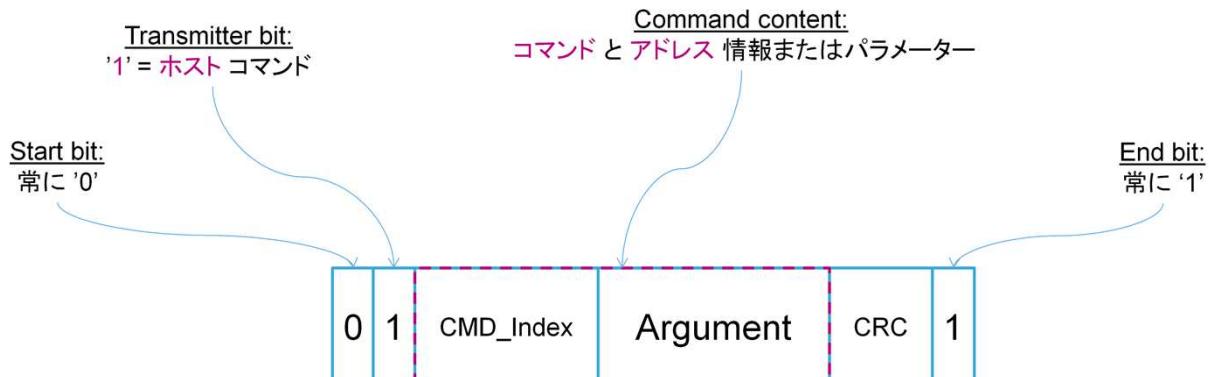

SDMMCコントローラは、コマンドインデックスとアーギュメントを設定するための高い柔軟性を提供します。

アーギュメントを設定するための柔軟な32ビットレジスタ、およびコマンドインデックスのための独立した6ビットフィールドによって、このアーキテクチャは、ファームウェアがどのようなタイプのカードにでもアドレスすることを保証します。

コマンドパスステートマシンは、コマンドインデックスとアーギュメントのいかなる制限もなく、すべてのコマンドトークンを生成することができます。

さらに、スタートビット、トランスマッタービット、CRC、および最終ビットフィールドは、バスにおいて自動的に生成されて、送られます。

# サポートされているレスポンス

9

## 短および長レスポンスタイプと互換

### 短レスポンス (全長 = 48bit)

ミラードコマンド

Example : R3

### 長レスポンス (全長 = 136bit)

R2レスポンス

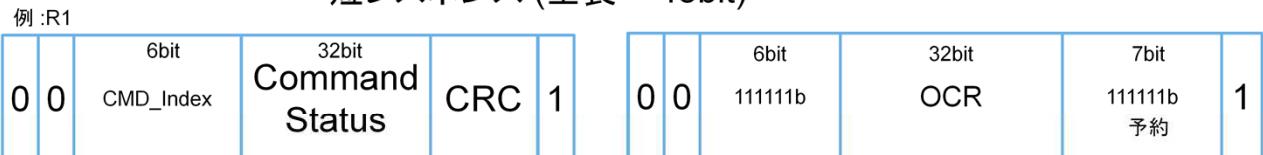

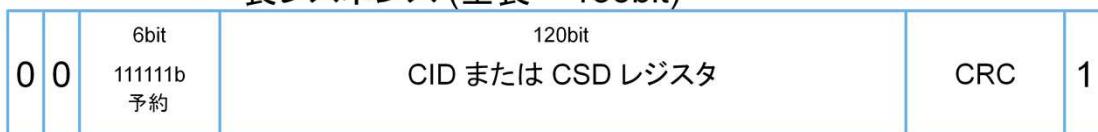

レスポンスは、前のコマンドへの返答としてカードから送られるトーケンです。

2タイプのレスポンスがあります：短と長。

4つの32bitレスポンスレジスターとレスポンス制約なしでは、SDMMCインターフェースは、それとのカードと通信を正しく初期設定するために、長と短レスポンスをサポートします。

[Click 1]

短レスポンスは全長48ビットを持ち、ミラードコマンドインデックス、32bitコマンドステータス、スタートビット、ストップビット、およびCRC7チェックサムにより構成されています。

短レスポンスが受け取られる時には、コマンドステータスは SDMMC\_RESP1レジスターに保存されて、ミラードコマンドインデックスは、入手可能な時に、SDMMC\_RESPCMDレジスターにコピーされます。[Click 2]

長レスポンスは全長136bitを持ち、スタートビット、ストップビット、およびCRC7チェックサムを含む120bit CID/CSDレジスターにより構成されています。

受信時には、CID/CSDカードレジスターは4つのSDMMC\_RESPxレジスターのうちの1つにコピーされます。SDMMCインターフェースは、スタートビット、コマンドインデックス抽出、32または128ビットレスポンス抽出、および自動CRC7ベリファイの自動的な検出を特徴とします。

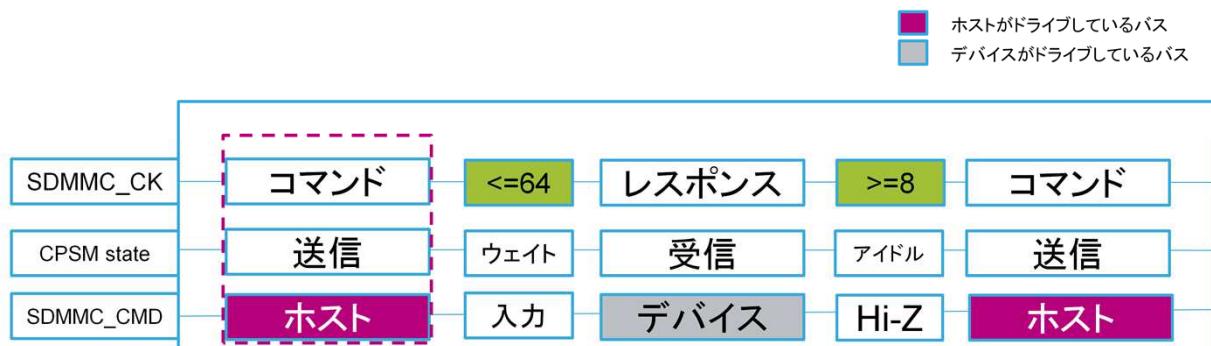

# SDMMCコマンド処理

10

## CPSMは標準のタイミングの制約と合う

一旦、SDMMC\_ARGとSDMMC\_CMDレジスタが

CMDINDEX、WAITRESP=『01』または『11』とCPSMEN =

1にプログラムされたら、CPSMは、送信状態からアイドル状

態に移行し、ホストは、コマンドをカードに送るために、

SDMMC\_CMDラインをドライブし始める。

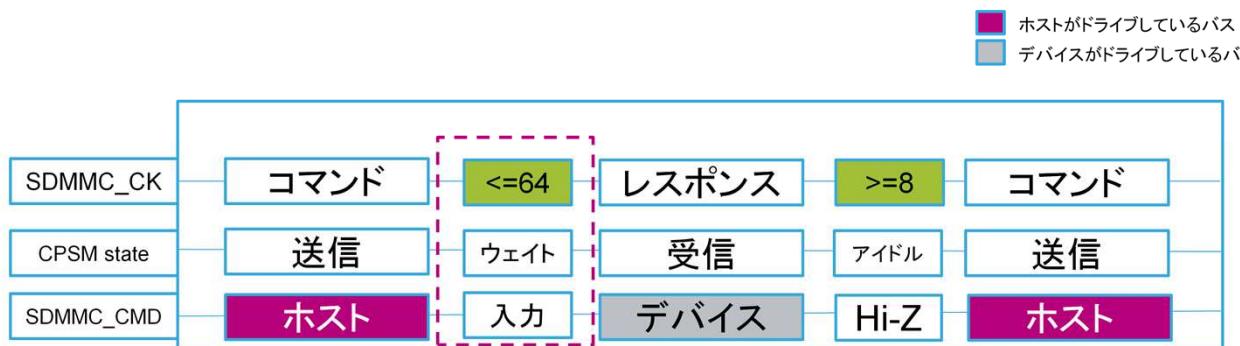

# SDMMCコマンド処理

11

## CPSMは標準のタイミングの制約と合う

もし、CPSMがレスポンス(WAITRESP=『01』または『11』)を待つようにプログラムされるならば、それは待ち状態に入り、コマンドタイマが動き始めます。

もし最長のNCR時間以内にカードが反応しないならば、タイムアウトフラグがセットされ、CPSMはアイドル状態に戻ります。

# SDMMCコマンド処理

12

## CPSMは標準のタイミングの制約と合う

■ ホストがドライブしているバス

■ デバイスがドライブしているバス

一旦、スタートビットがデバイスによりドライブされたら、それはコマンドラインにおいて検出されて、CPSMは、受信状態に移行します。

レスポンスが全部受け取られる時には、受信したCRCコードと内部で生成されたチェックサムコードが比較されて、適切なステータスフラグはSDMMCインターフェースステータスレジスターにセットされる。

CRCなしのレスポンスのために、例えばR3レスポンスフォーマットで、SDMMCコントローラが、コマンドレスポンスが受け取られたが、CRCチェックはフェイルしたことを意味しているCCRCFAILフラグを生成することに注意してください。

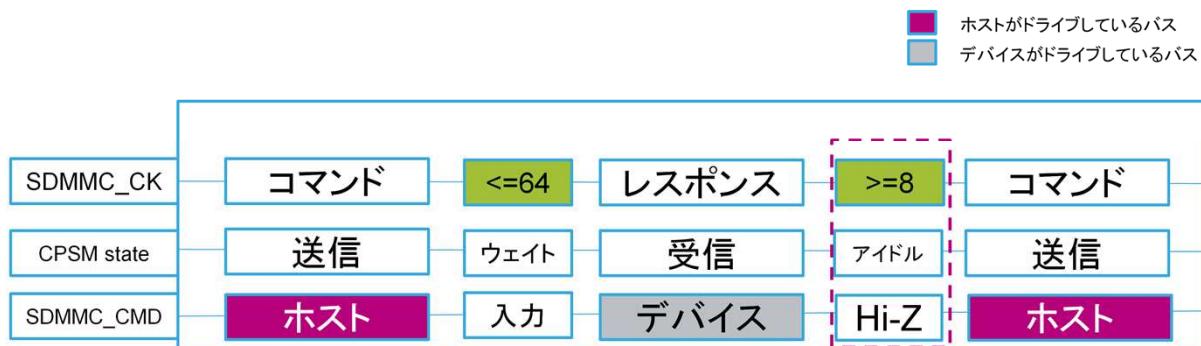

# SDMMCコマンド処理

13

## CPSMは標準のタイミングの制約と合う

レスポンス付きの完全なコマンドが受け取られた後に、

CPSMは、コマンド-コマンドタイミング(NCC)と反応-コマンド

(NRC)タイミングの制約と合わせるために、少なくとも

8SDMMC\_CKクロック期間の間アイドル状態にとどまります。

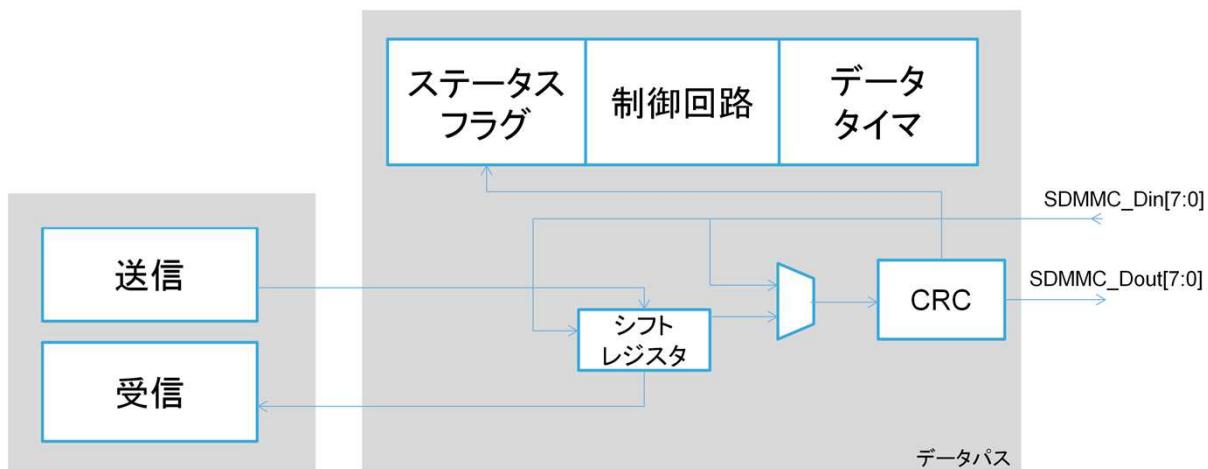

## データパス

14

データパスは、データをSD/SDIOまたはMMCカードへ/から、移します。

個々のSDMMC\_CKクロックサイクルにおいて、データパスは、1、4、または8ビットを、バス幅設定に合わせて送ることができます。

転送ロジックはSDMMCCCLKクロックと同期して動作します。それは、2つのサブユニットに分けられていて、ひとつはデータ送信、もうひとつはデータ受信用で、どちらも専門のコントロールビットとステータスフラグ付きです。

データバッファはデータパスの一部ではありません。送受信IFOロジックはAPBドメインにマップされています。異なるサブユニットからのすべての信号は再同期化されます。

CRC計算機能はカードとホストの間のデータの完全性を保証します。

データパケットの終わりに、CRCは自動的に計算されます。

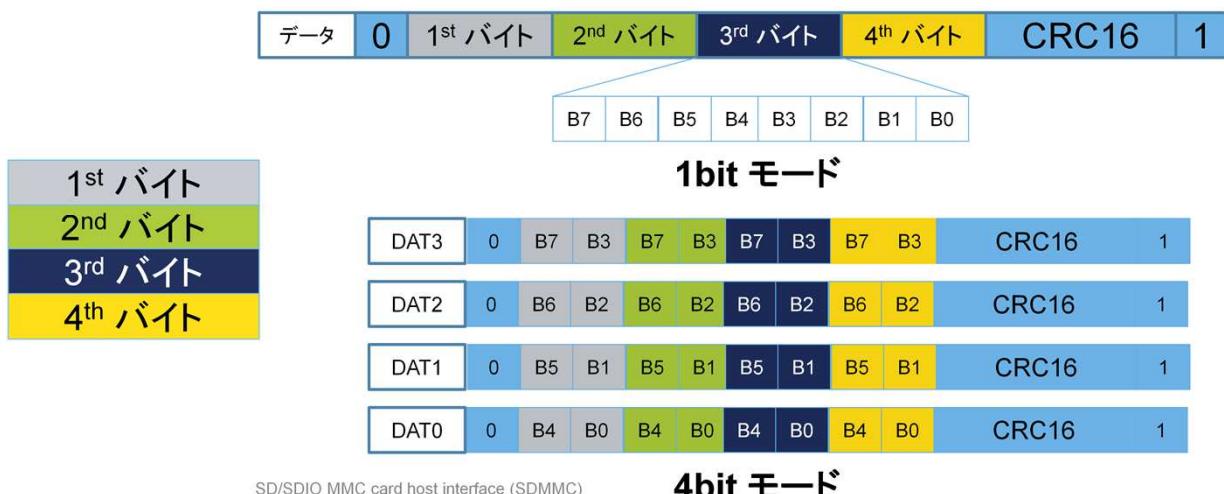

# データパケットフォーマット

15

## データバス幅をサポート

SD/SDIO MMC card host interface (SDMMC)

設定されたデータバス幅に合わせて、データバスは、1 (SDMMC\_D0)、4 (SDMMC\_D0 to SDMMC\_D3)、または 8(SDMMC\_D0 to SDMMC\_D7)のデータブロックを送ります。最初に、スタートビットがバス上に生成され、シーケンス(例の中の4番目のバイト)の最初のバイトから最後のバイトが続きます。

そして、CRC16と終わりのビットは、バスラインにおいてデータパケットに付加されます。

4ビットデータ幅設定では、個々のラインは、それ自身のスタートビット、終わりのビット、およびCRC16チェックサムを持っていきます。

# データパケットフォーマット

16

## データバス幅をサポート

1<sup>st</sup> バイト

2<sup>nd</sup> バイト

3<sup>rd</sup> バイト

4<sup>th</sup> バイト

|      |   |    |    |    |    |       |   |

|------|---|----|----|----|----|-------|---|

| DAT7 | 0 | B7 | B7 | B7 | B7 | CRC16 | 1 |

| DAT6 | 0 | B6 | B6 | B6 | B6 | CRC16 | 1 |

| DAT5 | 0 | B5 | B5 | B5 | B5 | CRC16 | 1 |

| DAT4 | 0 | B4 | B4 | B4 | B4 | CRC16 | 1 |

| DAT3 | 0 | B3 | B3 | B3 | B3 | CRC16 | 1 |

| DAT2 | 0 | B2 | B2 | B2 | B2 | CRC16 | 1 |

| DAT1 | 0 | B1 | B1 | B1 | B1 | CRC16 | 1 |

| DAT0 | 0 | B0 | B0 | B0 | B0 | CRC16 | 1 |

8bit モード

SD/SDIO MMC card host interface (SDMMC)

この例では、4バイトは8ビットモードのSDMMCバスの上に送られる。

SDMMC\_CKクロックサイクル毎に、1バイトは、スタートビット、最終ビット、およびCRC16チェックサムを各々のデータラインにシフトアウトされる。

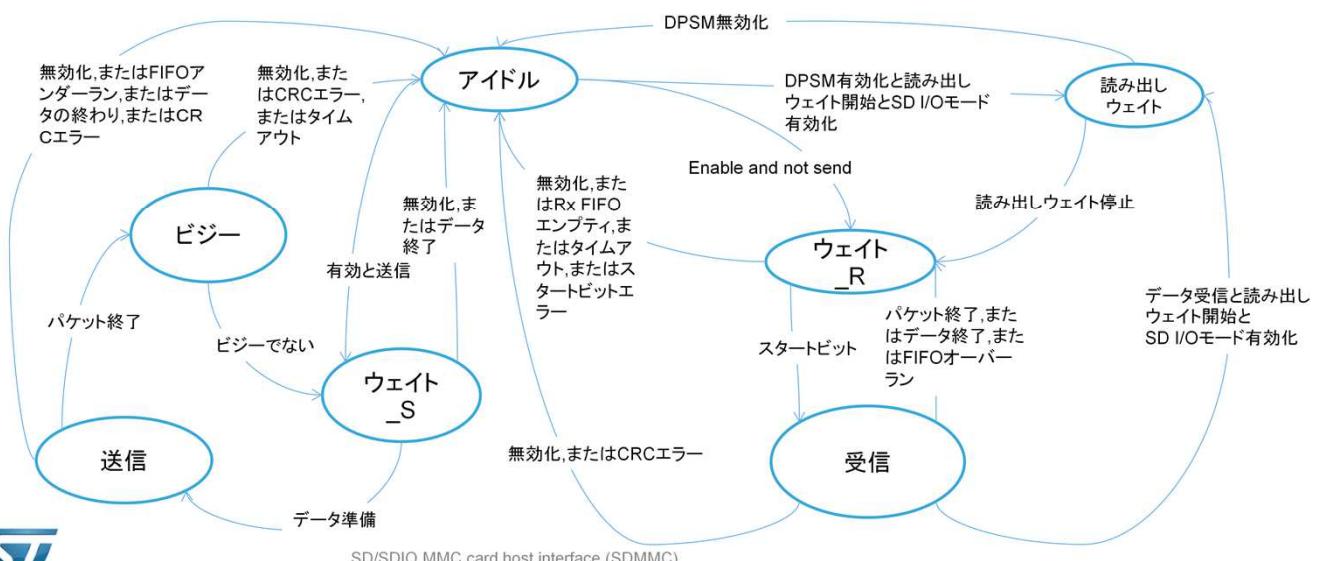

# データパスステートマシン

17

## ステートと遷移条件

データパスステートマシン(DPSM)はすべてのデータ遷移と受信を制御しますコントロールする。DPSMがアイドル状態で、DPSM有効化ビットと転送方向が設定される時に、最初の送信が引き起こされます。

[CLICK 1]

データ通信のために、可能な時に、DPSMがアイドルからウェイト\_Sに移行し、それから、送信状態に移ります。ウェイト\_Sステートの間、DPSMは、データFFIFOエンプティフラグがデアサート(ネゲート)されるまで待ちます。[CLICK 2]

FIFOバッファの中のデータが入手可能な時に、DPSMは送信ステートに移行します。

送信ステートにおいて、DPSMは、コントロールレジスターに設定されているバス幅に従ったデータをカードに送り始める。

. [CLICK 3]

データパケット終了の時に、DPSMは、内部で生成された

CRCコードと最終ビットを送り、ビジーステートに移行する。ビジーステートにおいて、DPSMIはCRCステータスフラグを待ちます。それがポジティブなCRCステータスを受信した場合、もしSDMMC\_D0ピンが「Lowレベル」ならば、それはウェイト\_Sステートに移行します（カードがビジーでないことを意味します）。[CLICK 4]

ウェイト\_Sステートから、新しいパケットトランスマッショーンは始まることができます、または、すべてのデータが送信される時には、DPSMIはアイドル状態に戻ることができます。[CLICK 5]

カードまたはFIFOのアンダーランエラーからのネガティブなCRCステータスは、DPSMIに強制的にアイドルステートに戻すことができます。[CLICK 6]

データ受信のために、DPSMIはアイドルステートからウェイト\_Rステートに移行する。バスにおいてスタートビットが検出される時には、DPSMIは受信ステートに移行する。そして、完全なパケットが受け取られるまでそこに留まります。

データ転送終了フラグとエラーが検出されない限り、DPSMIはウェイト\_Rと受信ステートの間で切り替え続ける。

もしエラーまたはデータ転送終了フラグが検出されたならば、DPSMIは、アイドルステートに戻る。. [CLICK 7]

読み出しウェイトステートは、他のコマンドまたは内部操作を実行するために、転送をストールするSDIOスペックの操作です。

それにはトランスマッショーンが進行中の間の受信ステートまたはアイドルステートから達することができます。

ファームウェアが、読み出し停止操作を要求するとき、DPSMIはウェイト\_Rステートに移行し、SDIOデバイスからスタートビットを待ちます。

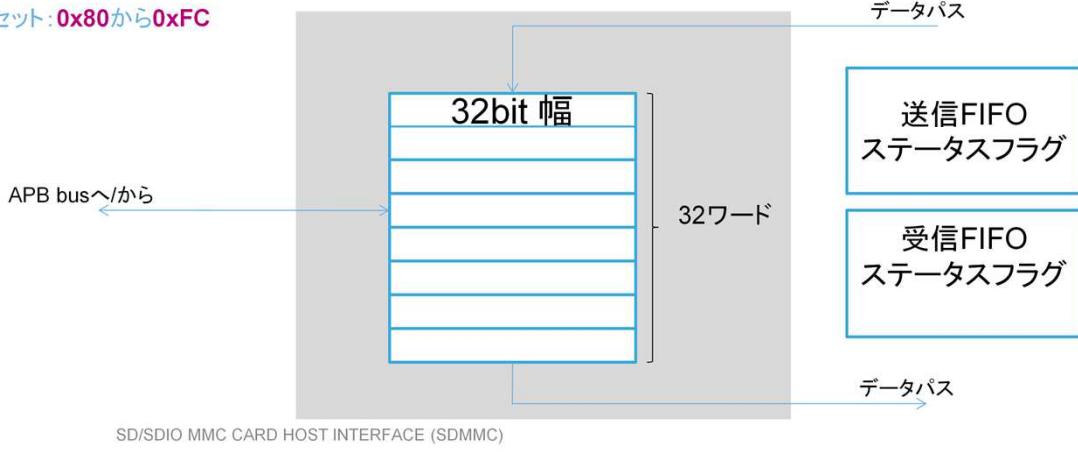

## データバッファとアクセスタイプ

- 32ワードFIFOデータバッファメモリはCPUバーストアクセス用に割り当てられている(LDM/STM instruction):

- オフセット: 0x80から0xFC

FIFOは、APBドメインにマッピングされ、32ビット幅、32ワードのデータバッファです。

データFIFOパケットはデータパス送信と受信パケットのためのデータソースです。

DPSMステータスによって、データパスFIFOは無効にできません、または送信有効か、受信有効化が可能です。

専用の受信/送信FIFOステータスフラグは、ファームウェア実行を容易にしています。

データパスが無効化にされる時には、すべてのFIFOフラグがデアサート(ネゲート)されます。

# ハードウェアフローコントロール

19

## FIFOアクセスが延期される時には有益

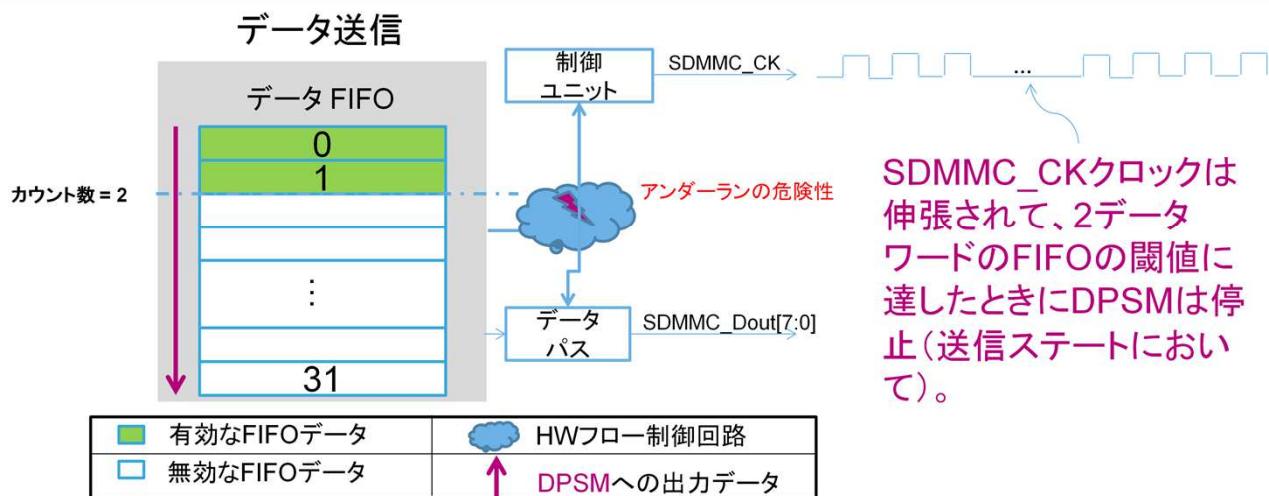

ハードウェアフロー制御機能は、FIFOアンダーラン(DPSMがTXモードである時)およびオーバーラン(DPSMがRXモードにある時)エラーを避けるために用いられます。

ハードウェアフロー制御ロジックはSDMMC\_CKピン信号を止めて、アンダラン／オーバーランのリスクが検出される時には、DPSMを凍結します。

送信ステートにおいて、SDMMC\_CKピンクロック信号は伸張されて、2データワードのFIFOの閾値に達したときにDPSMは凍結されます(送信ステートにおいて)。

# ハードウェアフローコントロール

20

FIFOアクセスが延期される時には有益

データ受信

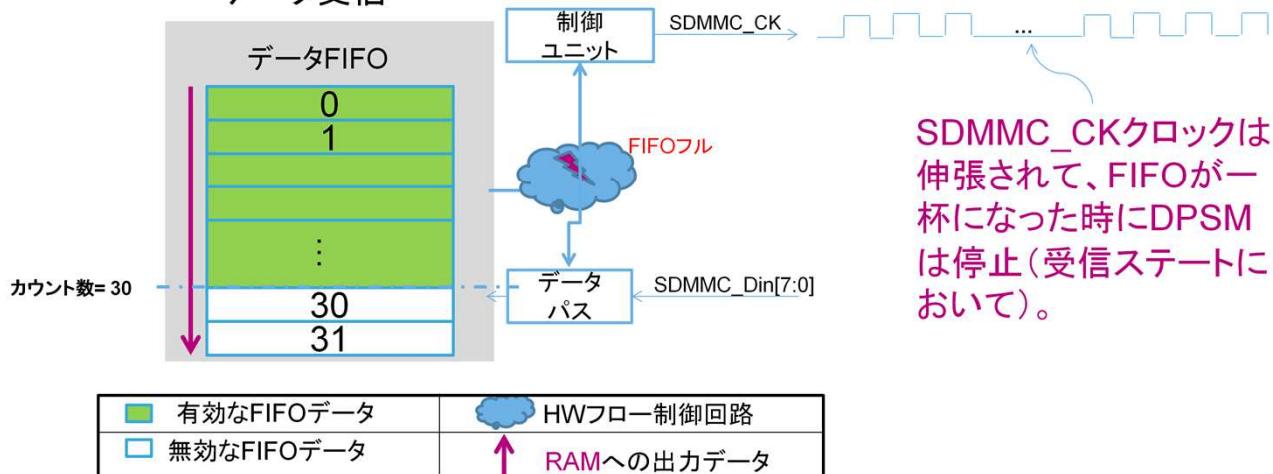

SDMMC\_CKクロックは伸張されて、FIFOが一杯になった時にDPSMは停止(受信ステートにおいて)。

受信ステートにおいて、SDMMC\_CKクロックは伸張されて、FIFOが一杯の間、DPSMは受信ステートにおいて凍結される(閾値は30ワード)。

FIFOフルフラグがデアサー(ネゲート)される時には、クロックとDPSMが再スタートします。

# SDIO読み出しウェイト

21

- SDMMCホストは、2つの読み出しウェイトモードに適用：

- SDMMC\_CKのサポート

- SDMMC\_D2使用

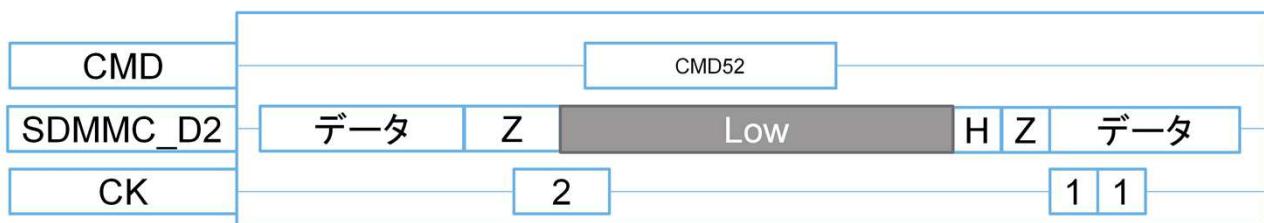

概念：読み出しウェイト操作は、SDIOの特別な操作である。そのデータバッファを空にする間、またはSDIOデバイスの他の機能にコマンドをおくる間に、一時的にホストがデータ転送をストールすることを可能にします

SDMMCコントローラは、2つの読み出しウェイトモードをサポートする：SDMMC\_CKを止めること、またはSDMMC\_D2信号を使うことによって行います。

SDMMC\_D2信号の有利な点は、読み出しウェイトモードの間でさえも、カードと通信することができます。

# SDIO サスPEND/再開

22

## ソフトウェア手続

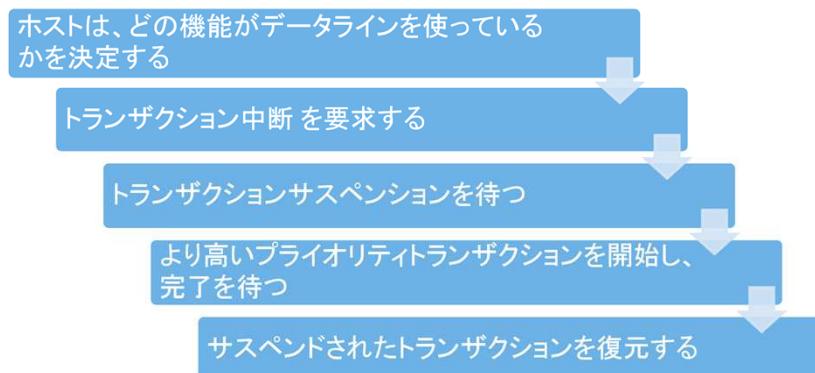

概念: マルチファンクションカードで、SDバスへのアクセスを共有する複数のデバイスがあります。

機能が、サスPEND／再開 [「サスPENDし、再開しなさい」] をサポートする時には、ホストは、他の内部の操作を実行するか、または他のデバイスと通信し、それから、サスPENDされたトランザクションを再開するために、一時的に、データ転送を停止できます。. [CLICK 1]

もしカードがサスPEND／再開機能をサポートするならば、ホストは、違う機能またはメモリーへの高いプライオリティ転送のためのバスを解放するために、一時的に、1つの機能またはメモリーへのデータ転送操作を停止できます。

SDMMC\_CMDビットが『11』に設定される時には、CPSMは、現在のコマンドがサスPENDコマンドであると知っています。もしサスPEND要求が受け入れられるならば、DPSMは、機能が完全なパケットを送り、アイドルステートに行く前に、アプリケーションが受信FIFOを空にするまで待ちます。

その時だけ、カードの高いプライオリティ部分を持つファーム

ウェアは通信を開始できます。

サスPENDされたトランザクションを再開するために、ファームウェアは、機能再開を要求する前に残されたデータを読むために、DPSMを再設定する必要があります。

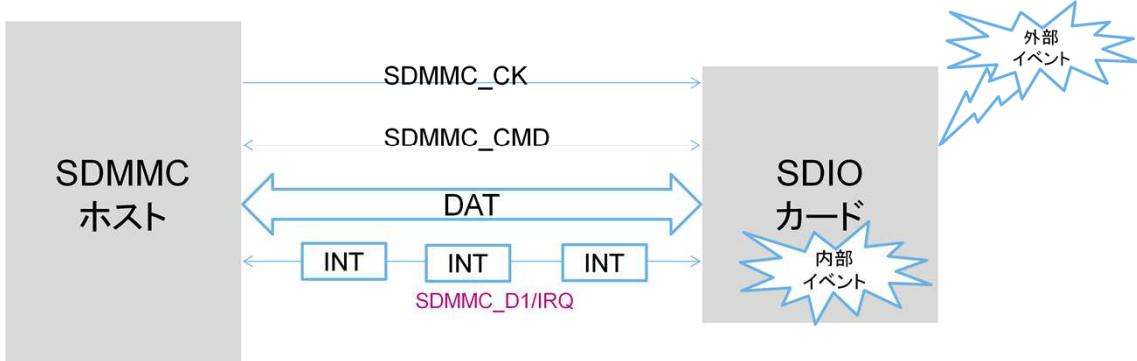

# SDIO割込み

23

## ステータスのポーリングのオーバーヘッドの低減

割込みの概念は、1ビットまたは4ビットデータバスモードの SDMMC\_D1/IRQピンを使って、カードステータスの変化をホストに知らせるために用いられます。[CLICK 1]

カードが外部のイベントを検出する時には、SDIO割込みはカードからSDMMCホストに送られます。. [CLICK 2]

いったんデータ制御レジスターの**SDIOEN**コンフィギュレーションビットが有効になったら、SDMMCホストは、割込みによりSDMMC\_D1ピンが転送されたのを検出します。[CLICK 3] [CLICK 4] [CLICK 5]

DPSMがアイドルステートにいる間、SDMMC\_D1ピンのすべてのLowレベルは、割込みとしてカードからホストに検出されます。

# 割込みとDMA

24

| 割込みイベント  | 内 容                                     |

|----------|-----------------------------------------|

| CCRCFAIL | コマンドレスポンスを受信したが、CRCチェックはエラー。            |

| CTIMEOUT | 64 SDMMC_CKのタイムアウト期間の後のコマンドレスポンス タイムアウト |

| CMDSENT  | コマンドを送付、レスポンス要求無し                       |

| CMDREND  | コマンドレスポンスを受信し、CRCチェックはパス。               |

| CMDACT   | コマンド転送は実行中(CPSMアクティブ)                   |

ここでは割込みイベントの概要が記述されています。このスライドはコマンドパスステートマシンと関連しています。

## 割込みとDMA

25

| 割込みイベント  | 内 容                             |

|----------|---------------------------------|

| DCRCFAIL | データブロック送信/受信。CRCエラー。            |

| DTIMEOUT | データタイムアウト- プログラムされたタイムアウト期間は経過。 |

| TXUNDERR | 送信FIFOアンダーランエラー                 |

| RXOVERR  | 受信FIFOオーバーランエラー                 |

| DBCKEND  | データブロック送信/受信。CRCパス              |

| TXACT    | データ送信は実行中(DPSMアクティブ)            |

| RXACT    | データ受信は実行中(DPSMアクティブ)            |

これは、転送方向と転送ステータスに関連したイベントを持つデータパスステートマシンのためのフラグのリストです。

## 割込みとDMA

26

| 割込みイベント  | 内 容                         |

|----------|-----------------------------|

| TXFIFOHE | 送信FIFOが半分空。最低8ワードがFIFOに書かれる |

| RXFIFOHF | 受信FIFOが半分空。最低8ワードがFIFOに存在する |

| TXFIFOF  | 送信FIFOフル                    |

| RXFIFOF  | 受信FIFOフル                    |

| TXFIFOE  | 送信FIFO空                     |

| RXFIFOE  | 受信FIFO空                     |

| TXDAVL   | 送信FIFOでデータ利用可能              |

| RXDAVL   | 受信FIFOでデータ利用可能              |

- DMAはデータ送信と受信転送可能を要求する。

これは割込みとポーリングモードにおいてFIFO管理で利用可能なフラグのリストです。[CLICK 2]

DMA要求は、FIFO閾値イベントにより引き起こされる時に、内部で発生する。

# 低消費電力モード

27

| モード             | 内 容                                     |

|-----------------|-----------------------------------------|

| Run             | アクティブ                                   |

| Sleep           | アクティブ。ペリフェラルの割込みでデバイスはスリープモードから復帰。      |

| Low-power run   | アクティブ                                   |

| Low-power sleep | アクティブ。ペリフェラルの割込みでデバイスはローパワースリープモードから復帰。 |

| Stop 1          | 停止、周辺機能のレジスタの内容は保持                      |

| Stop 2          | 停止、周辺機能のレジスタの内容は保持                      |

| Standby         | 電源OFF。周辺機能はStandbyモードから復帰の際は、再初期化が必要。   |

| Shutdown        | 電源OFF。周辺機能はShutdownモードから復帰の際は、再初期化が必要。  |

これは特別な低消費電力コンフィギュレーションモードの周辺機能のステータスの概要を示します。[CLICK 1]

デバイスはストップモードとそれ以下のモードでは通信機能を実行することはできません。

SDMMCコントローラが使かなくなるか、または、停止するようにシステムが切り替えられる前に、すべてのトランスマッシュョンが完成されることを保証することが重要です。

- 理論的な通信制限速度は最高50MHz

- 実際の通信速度は、以下の要因に依存する

- SDMMCバス能力負荷(カード静電容量+PCBトラック静電容量)

- GPIOの設定,  $V_{DD}$  レベルと周辺温度

- 与えられたSDMMCバス幅によってデータフローを維持するソフトウェア機能

パフォーマンスは主にSDMMCバス幅とクロック設定に依存します。[CLICK 1]

SDMMCインターフェースは最高50MHzにクロックシグナルを生成できます。

しかし、実際のスピードはアプリケーションによって低下され、いくつかのファクターに依存します。[CLICK 2]

PCBトラックとカードインプット容量が、影響を及ぼすので、SDMMCバス(寄生)静電容量を考慮する必要があります。GPIO設定も影響があります。速いGPIOモードを、コマンド、データ、およびクロックシグナルに適用しなければなりません。低電圧の電源電圧および極端な周囲温度は、エッジの速度を落とします。

そして、場合によっては、アプリケーションは、いつも、高速のデータフローを管理できるわけではない、特に、異常に頻度の高い例外サービスルーチンや例外ハンドラの処理が長い場合に影響します。

## 応用例

29

- SDメモリカードのインターフェース(高機能および拡張された能力のSD含)

- SD I/O デバイスのインターフェース

(Wi-Fi、Bluetoothモジュール、カメラモジュール ...)

- MMCとeMMCメモリカードのインターフェース

SDMMCインターフェースは、小ピンパッケージが必要な様々なアプリケーションにおいてリムーバブルなまたは永久的大容量記憶装置データメモリーによってインターフェースに使うことができます。

SDMMCコントローラは、外部のSDIOデバイスを使う時に、機器接続性を拡張するために使用できます(例えば、Bluetooth SDIOモジュール)。

## 関連周辺機能

30

- これは、SDMMCコントローラと関連した周辺機能のリストです。

必要であれば、これらの周辺機能のトレーニング資料をご参照ください。

- リセット &クロックコントロール (RCC)

- 割込み

- ダイレクトメモリアクセスコントローラ (DMA)

- 汎用IO (GPIO)

これは、STM32 SDMMCインターフェースと関連した周辺機能のリストです。ユーザーは、SDMMCコントローラを正しく設定し、使うために、これらの周辺機能の間のすべての関係に精通している必要があります。