## STM32MP15x lines using low-power modes

#### Introduction

STM32MP15x lines devices are built on an Arm<sup>®</sup> Cortex<sup>®</sup>-A7 with single or dual-core MPU subsystem combined with an Arm<sup>®</sup> Cortex<sup>®</sup>-M4 CPU.

STM32MP15x devices can be configured in various low-power modes in order to reduce power consumption when necessary. This application note explains the various low-power modes of the STM32MP15x lines devices, and how to configure and exit from them. This document also presents some guidance to be considered when using low-power modes at system level, and when using an external STPMIC1x power regulator component.

Table 1. Applicable products

| Туре       | Product lines                      |

|------------|------------------------------------|

| STM32MP15x | STM32MP151, STM32MP153, STM32MP157 |

In this document, "STM32MP15x", refers specifically to STM32MP151, STM32MP153 and STM32MP157 lines devices. For further information on STM32MP15x lines devices, refer to the following documents and deliverables available on www.st.com.

- STM32MP1 Series reference manuals (see Table 2. STM32MP15x lines configuration for details)

- · STM32MP1 Series datasheets

- STPMIC1x datasheet

- Getting started with STM32MP1 Series hardware development (AN5031)

- STM32MP1 Series and STPMIC1x hardware and software integration (AN5089)

- STM32CubeMP1 package

- STM32MP1 Series embedded software

## 1 Overview

This application note is applicable to all the devices of the STM32MP15x lines. The table below describes their main characteristics.

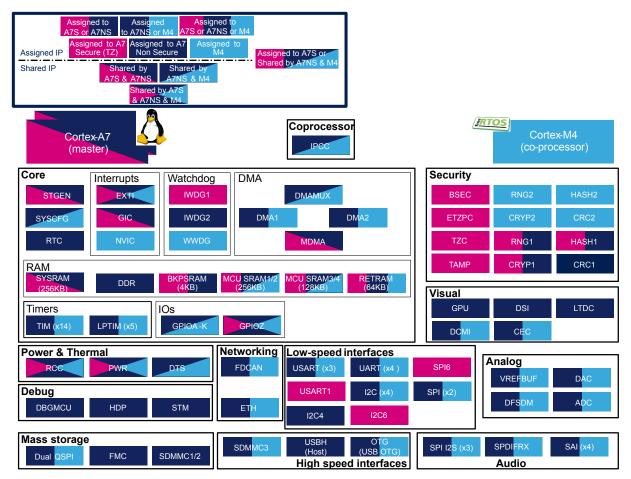

Depending on the device's part number, the system includes a Cortex-M4 and either a single-core or a dual-core Cortex-A7. In this document, the Cortex-A7 is called MPU and the Cortex-M4 is called MCU.

The full featured system (see the table below) is partitioned in:

- One MPU subsystem: dual Cortex-A7 with L2 cache

- One MCU subsystem: Cortex-M4 with associated peripherals clocked according to CPU activity

The present document assumes a full featured device (for example STM32MP157).

Table 2. STM32MP15x lines configuration

| Lines      | Reference<br>manual | Cortex-A7<br>configuration | Cortex-M4 | GPU | DSI | FDCAN |

|------------|---------------------|----------------------------|-----------|-----|-----|-------|

| STM32MP151 | RM0441              | Single-core                | Yes       | No  | No  | No    |

| STM32MP153 | RM0442              | Dual-core                  | Yes       | No  | No  | Yes   |

| STM32MP157 | RM0436              | Dual-core                  | Yes       | Yes | Yes | Yes   |

In this document MCU subsystems are sometimes referred to as "MCU" and MPU subsystems as "MPU" to facilitate the reading of the document.

This document applies to Arm®-based devices.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

AN5109 - Rev 5 page 2/37

# 2 Glossary

Table 3. Glossary

| Term      | Meaning                                          |

|-----------|--------------------------------------------------|

| AHB       | Advanced high-performance bus                    |

| ATF       | Arm® trusted firmware                            |

| AVD       | Analog voltage detector                          |

| BKPSRAM   | Backup SRAM                                      |

| BOR       | Brownout reset                                   |

| BUCK      | Step down switched-mode power-supply converter   |

| CSS       | Clock security system                            |

| DDR       | Double data-rate (SRAM)                          |

| DDRCTRL   | DDR controller                                   |

| DDRPHYC   | DDR physical interface control                   |

| DSI       | Display serial interface                         |

| ETH       | Ethernet controller                              |

| FDCAN     | Controller area network with flexible data-rate. |

| FDCAN     | Could also support time triggered CAN (TT)       |

| GPIO      | General purpose input output                     |

| GPU       | Graphic processing unit                          |

| HAL       | Hardware abstraction layer                       |

| HDP       | Hardware debug port                              |

| IRQ       | Interrupt request                                |

| IWDG      | Independent watchdog                             |

| LDO       | Low dropout regulator                            |

| LpDDR     | Low power DDR                                    |

| LSE       | Low-speed external quartz oscillator             |

| LSI       | Low-speed internal oscillator                    |

| MCU       | Microcontroller                                  |

| MLAHB     | Multi layer AHB / AHB based interconnect         |

| MPU       | Microprocessor                                   |

| PLL       | Phase locked loop                                |

| PVD       | Programmable voltage detector                    |

| PWR       | Power control block                              |

| QSPI      | Quad data lanes serial peripheral interface      |

| RCC       | Reset and clock control                          |

| RETRAM    | Retention memory                                 |

| RTC       | Real time clock                                  |

| SDMMC     | Secure digital and MultiMedia card interface.    |

| GDIVIIVIO | Supports SD, MMC, eMMC and SDIO protocols        |

| SMP       | Symmetric multiprocessing                        |

| SPL       | Secondary program loader                         |

AN5109 - Rev 5 page 3/37

| Term     | Meaning                                                                                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRAM     | Static random access memory                                                                                                                                         |

| STPMIC1x | Power management integrated circuit. External circuit that provides various platform power supplies with large controllability through signals and serial interface |

| SYSRAM   | System SRAM                                                                                                                                                         |

| SW       | Software                                                                                                                                                            |

| DTS      | Digital Temperature Sensor                                                                                                                                          |

| TEMPH-L  | Temperature sensor high-low monitoring                                                                                                                              |

| USART    | Universal synchronous asynchronous receiver transmitter                                                                                                             |

| USB OTG  | Universal Serial Bus (USB) on-the-go (OTG).                                                                                                                         |

| 038 019  | A standard USB interface able to become host or device                                                                                                              |

| VBATH-L  | VBAT high-low monitoring                                                                                                                                            |

| WFE      | Wait for event                                                                                                                                                      |

| WFI      | Wait for interrupt                                                                                                                                                  |

AN5109 - Rev 5 page 4/37

## 3 Power management concept

This section describes the STM32MP15x lines high-level power management concept.

Refer to the corresponding reference manual for more details (see Table 2. STM32MP15x lines configuration).

### 3.1 STM32MP15x lines system architecture

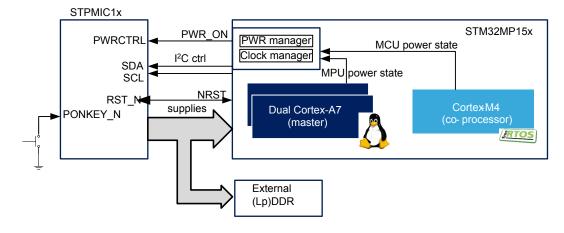

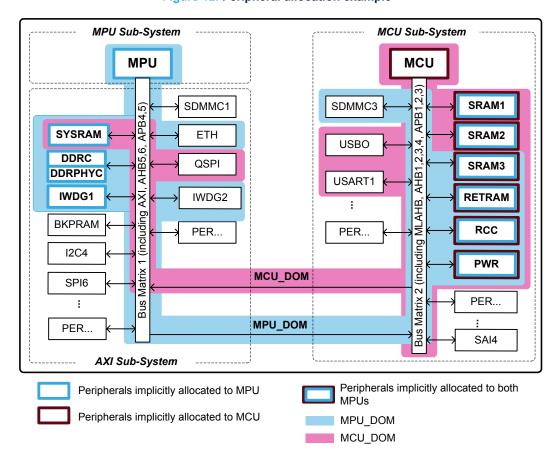

The STM32MP15x devices are based on a main dual-core MPU subsystem and a MCU subsystem. The multiple core architecture requires specific power modes both at system and at individual MPU and MCU subsystem level.

Internal digital logic is supplied externally in STM32MP15x lines devices, this is different than most STM32 MCUs which have an internal LDO (low dropout regulator) for such purpose. This key difference results in a different power-supply management for the STM32MP15x devices which require the use of external signals and/or programming of the external regulator to control the desired voltage supplies.

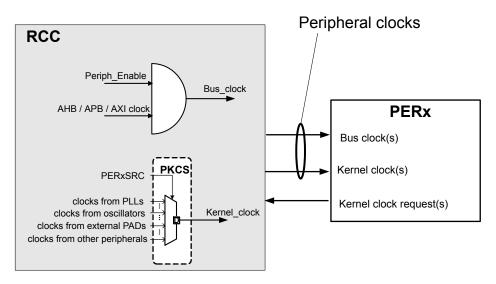

The power management features are spread between the RCC (reset and clock control) and the PWR (power) blocks of the STM32MP15x lines device.

- The RCC block ensures the clock tree handling (PLLs, muxes, dividers, clock gating) and the resets (local resets of the peripherals, Cortex-A7 reset, Cortex-M4 reset, platform reset)

- The RCC block permits to select the power mode based on the respective power states of the MCU and MPU subsystems

- The PWR block is responsible for low-power entry/exit. It drives the control pins (PWR\_ON, PWR\_LP) to the

external regulator based on the power mode.

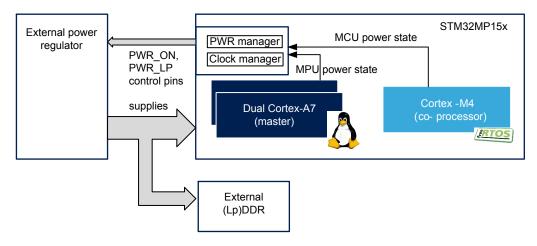

The figure below shows the STM32MP15x lines high-level system architecture.

Figure 1. STM32MP15x lines high-level system architecture

## 3.2 System supplies (V<sub>DD</sub> and V<sub>DDCORE</sub>)

The STM32MP15x lines devices require many power supplies that are detailed in the corresponding datasheet and reference manual (see Table 2. STM32MP15x lines configuration). Among those power supplies,  $V_{DD}$  and  $V_{DDCORE}$  play a key role in the low-power mode configuration.

- V<sub>DD</sub> power supply input for IOs and system analog such as reset, power management oscillators and PLLs.

- V<sub>DDCORE</sub> digital core domain supply, dependent on V<sub>DD</sub> supply. V<sub>DD</sub> shall be present before V<sub>DDCORE</sub>.

The various power pins of the STM32MP15x devices can be supplied either by some external discrete supplies or by using STPMIC1x as detailed in the reference design section of the application note *Getting started with STM32MP1 Series hardware development* (AN5031).

The STPMIC1x has several part numbers. Find below the part numbers appropriate for the STM32MP15x devices:

- STPMIC1APQR for application using VDD = 3.3 V

- STPMIC1BPQR for application using VDD = 1.8 V

AN5109 - Rev 5 page 5/37

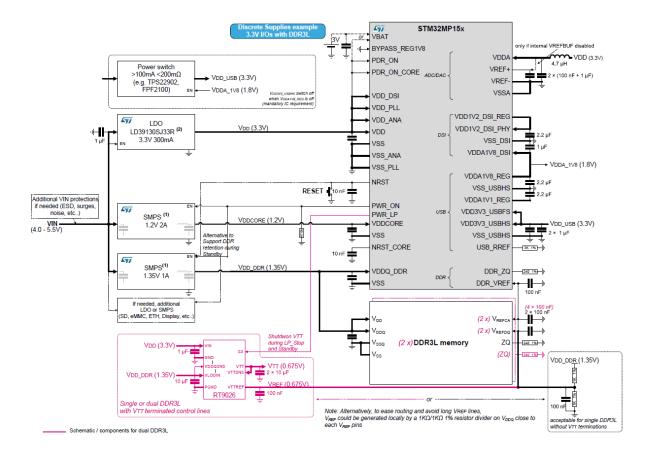

Figure 2. Discrete supplies example 3.3V I/Os with DDR3L

Note: Several types of DDR are supported (LpDDR2, LpDDR3, DDR3), this impacts the low-power mode management. Refer to Figure 7. Available power state transitions.

AN5109 - Rev 5 page 6/37

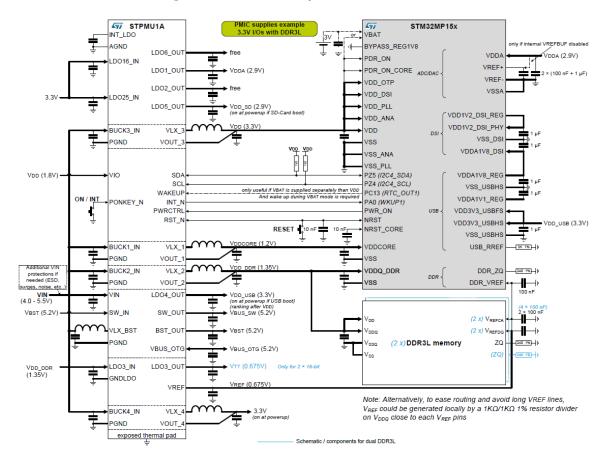

Figure 3. STPMIC1x example 3.3 V I/Os with DDR3L

The STPMIC1x provides the power distribution. It is driven by I<sup>2</sup>C and by control signals coming from the STM32MP15x device. Control is done by the Cortex-A7 MPU subsystem core. The main benefit of using the STPMIC1x versus using discrete regulator supplies is to have an integrated, smaller and cheaper solution. Refer to application note *STM32MP15x* and *STPMIC1x* HW and SW integration (AN5089) for more details.

AN5109 - Rev 5 page 7/37

## 4 Operating modes

This section describes the STM32MP15x lines various power modes and the ways of activating them.

### 4.1 Operating modes description

The operating modes allow the control of the clock distribution to the different system parts and the control of the power supplies of the system. The system operation mode is driven by the MPU subsystem and the MCU subsystem.

The power management controls the V<sub>DDCORE</sub> supply in accordance with the system operating modes.

The table below presents the operating modes available for the system and for the MPU and MCU subsystems. The power mode at system level is dependent on the power modes at each subsystem level (MPU and MCU).

| -         | Power mode | Description                                                                                      | Notes  |

|-----------|------------|--------------------------------------------------------------------------------------------------|--------|

|           | Run        | V <sub>DDCORE</sub> power on, clock on                                                           | -      |

|           | Stop       | V <sub>DDCORE</sub> power on, clock off                                                          | -      |

|           | LP-Stop    | V <sub>DDCORE</sub> power on, clock off                                                          | (1)    |

| System    | LPLV-Stop  | $\ensuremath{V_{\text{DDCORE}}}$ reduced power level and supply load, clock off                  | (1)(2) |

|           | Standby    | V <sub>DDCORE</sub> power off, clock off                                                         | -      |

|           | VBAT       | $V_{SW}$ is supplied by battery, $V_{DDCORE}$ is off, RTC is still active clocked by LSE crystal | (3)    |

|           | Power off  | All power supplies off                                                                           | -      |

|           | CRun       | V <sub>DDCORE</sub> power on, clock on                                                           | -      |

| MPU / MCU | CSleep     | V <sub>DDCORE</sub> power on, CPU clock off, peripheral clock on/off                             | (4)    |

|           | CStop      | V <sub>DDCORE</sub> power on, CPU subsystem clock off                                            | -      |

| MPU       | CStandby   | V <sub>DDCORE</sub> power on or off, clock off                                                   | (5)    |

Table 4. Power modes

- There is no difference in the output control pins PWR\_ON and PWR\_LP between LP-Stop and LPLVStop (see Section 4.3 External control signals PWR\_ON, PWR\_LP pins). While both LP-Stop and LPLV-Stop can be activated using STPMIC1x through programming of its internal register prior entering the targeted low-power mode (refer to Section 4.3.1 Using STPMIC1x power regulator), both modes may not be available using other external power regulators.

- 2. The main difference with Stop mode is that PWR\_ON output signal is toggling to 0 when using STPMIC1x external power regulator, enabling the possibility to take actions like powering off DDR termination resistance power supply.

- 3. To retain the content of the VSW domain (RTC, backup registers, backup RAM and retention RAM) when  $V_{DD}$  is turned off, the VBAT pin can be connected to an optional standby voltage supplied from a battery or from another source.

- 4. The MCU/MPU subsystems allocated peripheral(s) clock operate according to RCC PERxLPEN. When the MPU enters CSleep with WFE (wait for event), the MPU subsystem allocated peripheral(s) clock operate as in MPU CRun mode, irrespective of RCC PERxLPEN.

- In CStandby mode, the MPU is in power off only if the system mode is in Standby (when MCU is in CStop with PDDS=1).

Refer to Table 6. Power-system mode versus sub-system mode summary.

The choice of which low-power mode to use is dependent on power saving target and it must be chosen according to which wakeup interrupts are needed/available in the chosen low-power mode and the expected wakeup time duration.

User should always make sure that the chosen low-power mode is consistent with the available wakeup sources. For instance LPLV-Stop or Standby modes have very limited wakeup source capabilities.

Also the wakeup duration is longer if power supplies voltage have been reduced or switched off by reducing  $V_{DDCORE}$ , switching off DDR resistance termination supply with DDR in self refresh or switching off the full DDR (which may require reloading the firmware from the Flash memory). The system's low-power mode wakeup capabilities are presented in the below table.

AN5109 - Rev 5 page 8/37

| Table 5. System's | low-power mode | wakeup capabilities |

|-------------------|----------------|---------------------|

|-------------------|----------------|---------------------|

| System power mode | Wakeup sources                                                                   |

|-------------------|----------------------------------------------------------------------------------|

| Stop/LP-Stop      | DBG, PVD, AVD, USBH, OTG, CEC, ETH, MDIOS, USARTX, I2CX, SPIX DTS, LPTIMX, GPIOs |

| LPLV-Stop         | PVD, AVD, DTS, LPTIMx, GPIOs                                                     |

| Standby           | Six GPIO pins: PA0, PA2, PC1, PC13, PI8, PI11                                    |

| All modes         | BOR, VBATH/VBATL, TEMPH/TEMPL, LSE CSS, RTC/auto wakeup, tamper pins, IWDGx      |

## 4.2 Low-power mode control

#### 4.2.1 Low-power mode control registers

The control register bits presented below are related to the low-power modes (for description of low-power modes see Section 4 Operating modes).

#### PDDS bit in register PWR MPU control register (PWR\_MPUCR)

- 0: Keeps Stop mode when MPU enters to CStop.

- 1: Allows Standby mode when MPU enters to CStop.

When CSTBYDIS = 0 allows MPU to enter CStandby mode.

#### PDDS bit in register PWR MCU control register (PWR\_MCUCR)

- 0: Keeps Stop mode when MCU enters to CStop.

- 1: Allows Standby mode when MCU enters to CStop.

### CSTBYDIS bit in register PWR MPU control register (PWR\_MPUCR)

- 0: MPU CStandby mode enabled.

- 1: MPU CStandby mode disabled.

Both MPU and MCU can access the PWR\_MPUCR and PWR\_MCUCR. However the PWR\_MPUCR can be set in secure mode (Linux case) to only allow MPU write access.

MCU can write the PWR\_MCUCR register bits using HAL\_PWR\_EnterStandbyMode() function.

The HAL function HAL\_PWR\_EnterStandbyMode() sets the MCU PDDS bit to '1' and enters the CStop mode for the MCU subsystem through a WFI (wait for interrupt). The Standby mode is entered only once the MPU subsystem enters the CStop mode with PDDS=1 & CSTBYDIS=1 or the CStandby mode (see Section 4.4: Low-power mode entry sequence)

AN5109 - Rev 5 page 9/37

The tables below detail the possible combinations of the power modes between system and MPU/MCU subsystems and the system's low-power modes summary respectively.

**MPU**<sup>(1)</sup> **CStop** CStop **CRun CSleep** (PDDS = 1)CStandby<sup>(2)</sup> (PDDS = 0)CSTBYDIS=1) **CRun** Run Run Run<sup>(3)</sup> Run Run **CSleep** Run Run Run Run Run<sup>(3)</sup> Stop Stop Stop(3) **CStop** LP-Stop LP-Stop Run Run LP-Stop MCU (PDDS = 0)LPLV-Stop LPLV-Stop LPLV-Stop Stop **CStop** Run Run LP-Stop Standby<sup>(4)</sup> Standby<sup>(4)</sup> (PDDS = 1)LPLV-Stop

Table 6. Power-system mode versus sub-system mode summary

- 1. Refer to Section 4.6.7 Exit from MPU CStop and CStandby for additional details on CStop and CStandby.

- CStandby mode on MPU is not supported in the STM32MPU OpenSTLinux Distributions. System standby is reached with MPU in CStop mode (PDDS=1, CSTBYDIS=1).

- 3. When exit from MPU CStandby with System in Run, Stop, LP-Stop or LPLV-Stop, program execution restarts with a local MPU reset. This 'reboot' can affect MCU operation due to possible re-initialization of some peripheral registers by the BootROM when reloading MPU initialization code from external Flash.

- 4. When exit from MPU CStandby or CStop (PDDS=1, CSTBYDIS=1) with System in Standby, program execution restarts in the same way as after a power on reset (option bytes loading, reset vector fetched, or other).

|                                        |                                                                          |                                     |                               |                                |       |        | PWR_ON           |                         |

|----------------------------------------|--------------------------------------------------------------------------|-------------------------------------|-------------------------------|--------------------------------|-------|--------|------------------|-------------------------|

| System Mi                              | MPU                                                                      | DDR <sup>(1)</sup>                  | MCU                           | Sys-oscillators <sup>(2)</sup> | hclk4 | PWR_LP | LPCFG =          | LPCFG =<br>1            |

|                                        | CRun or<br>Csleep                                                        | Active / Auto refresh               | CRun<br>or                    |                                |       |        |                  |                         |

| Run                                    | CStop or<br>CStandby                                                     | Self refresh                        | CClean                        | On                             |       |        |                  |                         |

|                                        | CRun or<br>CSleep                                                        | Active / Auto refresh               | CStop                         |                                |       | 1      | 1                | 1                       |

| Stop                                   |                                                                          |                                     |                               |                                |       |        |                  |                         |

| $(LPDS = 0)^{(3)}$                     | CCton or                                                                 | CStop or CStandby Self refresh CSto | CStop                         | CStop On/Off <sup>(4)</sup>    |       |        |                  |                         |

| LP-Stop                                |                                                                          |                                     |                               |                                |       |        |                  |                         |

| LPLV-Stop <sup>(3)</sup><br>(LPDS = 1) |                                                                          |                                     |                               |                                |       | Off    | 0 <sup>(5)</sup> |                         |

| Standby                                | CStandby or<br>(CStop and<br>MPU PDDS<br>= 1 and MPU<br>CSTBYDIS =<br>1) | Off / Self<br>refresh               | CStop<br>and<br>MCU<br>PDDS = | Off                            |       | 0(6)   | 0(6)             | <b>O</b> <sup>(6)</sup> |

Table 7. System low-power modes summary

AN5109 - Rev 5 page 10/37

The DDR operation state is only presented for information. For example, the DDR may be Off when the MPU is in CRun like when executing from BootROM.

<sup>2.</sup> The sys-oscillators are the HSI, HSE or CSI oscillators configured ON in RCC.

<sup>3.</sup> At least 1 PDDS bit (MCU or MPU) selects Stop (PDDS = 0).

- 4. When the system oscillator HSI, HSE or CSI is used, the state is controlled by the respective xxxKERON (HSIKERON, HSEKERON or CSIKERON bits present in the RCC oscillator clock enable set register (RCC\_OCENSETR) and the RCC oscillator clock enable clear register (RCC\_OCENCLRR)), else the system oscillator is off.

- Settings in PWR control register 3 (PWR\_CR3) bits POPL have no impact on the LP-Stop and LPLV-Stop mode PWR\_ON and PWR\_LP pulse low time.

- 6. A guaranteed minimum PWR\_ON and PWR\_LP pulse low time can be defined in PWR control register 3 (PWR\_CR3) bits POPI

## 4.3 External control signals PWR\_ON, PWR\_LP pins

The two output pins PWR\_ON and PWR\_LP are related to the VDDCORE supply. They are used by external component/regulator to identify which voltage level should be applied on V<sub>DDCORE</sub>. Refer to Section 4 Operating modes for more details on PWR ON, PWR LP configuration.

- PWR\_ON: V<sub>DDCORE</sub> supply request

- It is automatically generated by the hardware depending on the state of the STM32MP15x device and on the value of **LPCFG** (PWR\_ON pin configuration) bit in PWR control register 1 (PWR\_CR1).

- PWR\_LP: V<sub>DDCORE</sub> low-power mode control (active low)

It is automatically generated by the hardware depending on the state of the STM32MP15x device and the value of LPDS (low voltage deepsleep LPLV-Stop mode selection) bit on PWR control register 1 (PWR\_CR1).

The table below indicates the PWR\_ON, PWR\_LP output pin values depending on the various configuration of power modes and LPDS, LPCFG, LVDS bits.

- LPDS is PWR control register 1 (PWR CR1) bit 0

- LPCFG is PWR control register 1 (PWR CR1) bit 1

- LVDS is PWR control register 1 (PWR CR1) bit 2

The table also shows the differences in the usage of pins PWR\_ON and PWR\_LP depending if the STM32MP15x device is to be used with STPMIC1x or with other external power supply components.

The power modes are detailed in the PWR section of the corresponding reference manual (see Table 2. STM32MP15x lines configuration).

Table 8. PRW\_ON, PWR\_LP levels according power modes, LPDS, LVDS and LPCFG bits

| STM32MP15x<br>state                                         | LPDS/LVDS bits | LPCFG bit        | PWR_ON           | PWR_LP           | V <sub>DDCORE</sub> |

|-------------------------------------------------------------|----------------|------------------|------------------|------------------|---------------------|

| Startup (until V <sub>DD</sub> reaches POR threshold level) | X/X            | Х                | 0                | 0                | Off                 |

| Run mode                                                    | X/X            | X                | 1                | 1                | On                  |

| Stop mode                                                   | 0/X            | Х                | 1                | 1                | On                  |

| LD Stan made                                                | 1/0            | 0                | 1                | 0                | On                  |

| LP-Stop mode                                                |                | 1 <sup>(1)</sup> | 0(2)             | 0(2)             | Oli                 |

| I DIV Oters are de                                          | 4/4            | 0(3)             | 1                | 0                | 0 (4)               |

| LPLV-Stop mode                                              | 1/1            | 1 <sup>(1)</sup> | 0 <sup>(2)</sup> | 0 <sup>(2)</sup> | On <sup>(4)</sup>   |

| Standby mode                                                | 0/0            | X                | 0(2)             | 0(2)             | Off                 |

| VBAT mode (V <sub>DD</sub> powered down)                    | X/X            | Х                | HiZ              | HiZ              | Off                 |

- 1. Configuration used with STPMIC1x PWRCTRL pin connected to PWR\_ON.

- 2. There is no difference between LP-Stop, LPLV-Stop and Standby mode on the PWR\_ON, PWR\_LP output values '00' with LPCFG bit=1.

- Depending on the external power regulator that is used, this configuration might not be available (not possible to reduce the power supply level).

- 4. V<sub>DDCORE</sub> supply level and power load can be decreased.

AN5109 - Rev 5 page 11/37

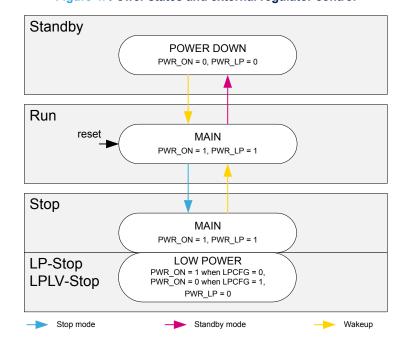

The figure below illustrates the relation between the system states and the PWR\_ON, PWR\_LP output pins for regulator control for STM32MP15x lines devices.

Figure 4. Power states and external regulator control

#### 4.3.1 Using STPMIC1x power regulator

The figure below shows the main differences at system level when using the STPMIC1x power regulator.

Figure 5. STM32MP15x lines high-level system architecture when using STPMIC1x

When using STPMIC1x power regulator, only PWR\_ON output control pin from STM32MP15x is needed for the control of the STPMIC1x power modes (through PWRCTRL pin). In that case, the user shall set the LPCFG bit of the PWR\_CR1 register to '1'.

Table 8. PRW\_ON, PWR\_LP levels according power modes, LPDS, LVDS and LPCFG bits highlights on the gray cells that there is no difference between LP-Stop, LPLV-Stop and Standby mode on the PWR\_ON, PWR\_LP output values '00' with LPCFG bit=1.

The STPMIC1x differentiates between those LP-Stop, LPLV-Stop and Standby low-power modes and apply the correct  $V_{DDCORE}$  value thanks to STPMIC1x internal registers. Those registers programming is done via the I2C interface and not through the PWR\_ON, PWR\_LP pins values.

AN5109 - Rev 5 page 12/37

When using STM32MPU OpenSTLinux Distributions, this programming is handled by the first stage bootloader (TF-A or OPTEE). Hence before entering LP-Stop, LPLV-Stop or Standby mode the application shall configure the STPMIC1x internal registers to the desired system power supplies level (like V<sub>DDCORE</sub>, V<sub>DD DDR</sub>, and others).

When entering LP-Stop mode, despite the fact that  $V_{DDCORE}$  level is not decreased (only in LPLV-Stop), it is still possible to program the STPMIC1x so that other power supplies are shut down if not needed (for example the power supply of the DDR termination resistances).

The STPMIC1x includes two 8-bit registers for each of the BUCK (1,2,3,4) and LDO (1,2,3,4,5,6):

- A BUCKx/LDOx control register (HP mode) that stores the expected output voltage value during Run mode.

- A BUCKx/LDOx control register (LP mode) that stores the expected output voltage during low-power mode.

Each of those registers have the following structure:

| 7               | 6    | 5 | 4 | 3 | 2 | 1    | 0   |

|-----------------|------|---|---|---|---|------|-----|

| output value <5 | 5:0> |   |   |   |   | hplp | ena |

Bits 7:2: **output value**: the output value on 6 bits corresponds to a specified voltage value (refer to STPMIC1x datasheet).

Bit 1: hplp: forces high/low load capability (allows more/less load on STPMIC1x output).

0: High load capability

1: Low load capability

Note: hplp bit is applicable only for BUCKx registers, not for LDOx.

Bits 0: ena: enable bit.

0: BUCK/LDO disabled

1: BUCK/LDO enabled

The following tables show how the STPMIC1x could be programmed in Run mode and how STPMIC1x could be programmed before entering LP-Stop, LPLV-Stop and Standby modes respectively. Both tables list all power supplies and not only the  $V_{\mbox{\scriptsize DDCORE}}$  one and the settings used on them are in line with the example presented on Section 3.2 .

Table 9. STPMIC1x (HP mode) programming for Run mode

| Supply name          | Control register (HP mode) /@ | Run           |

|----------------------|-------------------------------|---------------|

| V <sub>DDCORE</sub>  | BUCK1 / 0x20                  | 0x61 (1.2 V)  |

| V <sub>DD_DDR</sub>  | BUCK2 / 0x21                  | 0x79 (1.35 V) |

| $V_{DD}$             | BUCK3 / 0x22                  | 0xD9 (3.3 V)  |

| 3V3                  | BUCK4 / 0x23                  | 0xD9 (3.3V)   |

| V <sub>REF_DDR</sub> | VREFDDR / 0x24                | 0x1           |

| $V_{DDA}$            | LDO1 / 0x2A                   | 0x51 (2.9 V)  |

| V <sub>DD_USB</sub>  | LDO4 / 0x28                   | 0x1 (3.3 V)   |

| V <sub>DD_SD</sub>   | LDO5 / 0x29                   | 0x51 (2.9 V)  |

| V <sub>TT</sub>      | V <sub>TT</sub> LDO3 / 0x27   |               |

<sup>1.</sup> LDO3 output value is BUCK2 output /2 = 0.675 V for DDR3 use case.

AN5109 - Rev 5 page 13/37

| table for all the fact that th |                                  |               |                           |                     |                       |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------|---------------------------|---------------------|-----------------------|--|--|

| Supply name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Control register<br>(LP mode) /@ | LP-Stop       | LPLV-Stop                 | Standby with DDR SR | Standby w/o DDR<br>SR |  |  |

| V <sub>DDCORE</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | BUCK1 / 0x30                     | 0x61 (1.2 V)  | 0x61 (1.2 V) 0x33 (0.9 V) |                     | 0 (off)               |  |  |

| V <sub>DD_DDR</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | BUCK2 / 0x31                     | 0x79 (1.35 V) |                           |                     | 0x7A (off)            |  |  |

| $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BUCK3 / 0x32                     |               | 0xD9 (3.3 V)              |                     |                       |  |  |

| 3V3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | BUCK4 / 0x33                     | 0xD9          | 0xD9 (3.3 V) 0            |                     | 0xD8 (off)            |  |  |

| V <sub>REF_DDR</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | VREFDDR / 0x34                   |               | 0x1                       |                     | 0x0 (off)             |  |  |

| $V_{DDA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LDO1 / 0x3A                      | 0x51          | (2.9 V)                   | 0x5                 | 0 (off)               |  |  |

| V <sub>DD_USB</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | LDO4 / 0x38                      | 0x1 (3.3 V)   |                           | 0x0                 | ) (off)               |  |  |

| V <sub>DD_SD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | LDO5 / 0x39                      | 0x51          | (2.9 V)                   | 0x5                 | 0 (off)               |  |  |

| V <sub>TT</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LDO3 / 0x37                      | 0x7C (off)    |                           |                     |                       |  |  |

Table 10. STPMIC1x (LP mode) programming for LP-Stop LPLV-Stop and Standby mode

Note:

Setting bit0 to '0' disables the corresponding BUCK/LDO, and its value is set to "off".

Example:  $V_{DDA} = 2.9 \text{ V } (0x51) \text{ when bit0='1'}$  and is 'off' (0x50) when bit0='0'.

Application note "STM32MP15x and STPMIC1x HW and SW integration" (AN5089) provides more details on how to use STPMIC1x.

The NRST pin of the STM32MP15x lines can be activated by the STPMIC1x RST\_N pin when the user is setting STPMIC1x PONKEY N pin to '0', hence resetting both the STPMIC1x and the STM32MP15x devices.

#### 4.3.2 Using other external power supplies

When using external power supplies other than STPMIC1x, the use of both PWR\_ON and PWR\_LP output control pins is possible in order to control external power supply if low-power modes below Stop mode (such as LP-Stop, LPLV-Stop and Standby) are required by the application.

When the STM32MP15x device goes to LP-Stop or LPLV-Stop mode, PWR\_ON shall be set to '1'; when they are on Standby PWR ON shall be set to '0'. To activate this usage, the user must set the LPCFG bit to '0'.

#### 4.4 Low-power mode entry sequence

The STM32MP15x lines have dedicated power-modes at subsystems level (MPU, MCU) and at system level (see Section 4 Operating modes). This section details how to enter those power modes at subsystem and at system level.

#### MPU subsystem

The MPU subsystem's low-power modes (CSleep, CStop and CStandby) are entered by the MPU when executing the WFI (wait for interrupt) or WFE (wait for event) instructions. WFE being available only when entering CSleep. In order for the MPU to enter the subsystem's low-power modes, the RCC and PWR registers must be already correctly programmed (refer to Section 5.1 Peripheral assignment and allocation). When using STM32MPU OpenSTLinux Distributions those mechanisms are handled by the first stage bootloader (refer to Section 4.5 Power management under Linux).

#### MCU subsystem

MCU subsystem's low-power modes (CSleep and CStop) are entered by the MCU when executing the WFI (wait for interrupt), or WFE (wait for event) instructions, or when the SLEEPONEXIT bit in the Cortex<sup>®</sup>-M4 System Control register is set on Return from ISR.

When using STM32CubeMP1 package on the MCU, several functions are defined for low-power modes. The table below describes each function defined in STM32CubeMP1 package according to its dedicated low-power mode.

AN5109 - Rev 5 page 14/37

Table 11. Low-power modes functions used on MCU within STM32CubeMP1 package

| Low-power mode   | Function                     | Argument                                      | Description                                                                                                                                                                                             |

|------------------|------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | HAL_PWR_EnterSLE<br>EPMode   | PWR_MAINREGULATOR_ON PWR_LOWPOWERREGULATOR_ON | The regulator parameter is not used for STM32MP15x lines devices and it is kept as parameter just to maintain compatibility with the lower-power families (like STM32L Series)                          |

| CSleep           |                              | PWR_SLEEPENTRY_WFI PWR_SLEEPENTRY_WFE         | Specifies if SLEEP mode is entered with WFI or WFE instruction                                                                                                                                          |

|                  |                              |                                               | Set SLEEPONEXIT bit of SCR register.                                                                                                                                                                    |

|                  | HAL_PWR_EnableSI eepOnExit   | None                                          | When this bit is set, the processor reenters SLEEP mode when an interruption handling is over                                                                                                           |

|                  | HAL_PWR_DisableSI eepOnExit  | None                                          | Clears SLEEPONEXIT bit of SCR register                                                                                                                                                                  |

| CStop,<br>PDDS=0 | HAL_PWR_EnterSto pMode       | PWR_MAINREGULATOR_ON PWR_LOWPOWERREGULATOR_ON | The regulator parameter is not used for STM32MP15x devices and it is kept as parameter just to maintain compatibility with the lower-power families (like STM32L Series)                                |

|                  |                              | PWR_STOPENTRY_WFI PWR_STOPENTRY_WFE           | Specifies if Stop mode is entered with WFI or WFE instruction                                                                                                                                           |

| CStop,<br>PDDS=1 | HAL_PWR_EnterSta<br>ndbyMode | None                                          | This function makes the MCU to go to CStop (WFI) and puts the bit MCU PDDS = 1 allowing the system to go to Standby when the MPU is put in CStandby or in (CStop and MPU PDDS = 1 and MPU CSTBYDIS = 1) |

#### **System**

The system may enter Stop, LP-Stop, LPLV-Stop or Standby when all the EXTI wakeup sources are cleared and when both the MPU and MCU are in CStop or CStandby mode.

The system enters the Standby mode (power off, clock off) only when the MPU is in CStandby or in CStop with MPU PDDS=1 and MPU CSTBYDIS =1 and when MCU is in CStop with MCU PDDS = 1.

Standby mode entering must be carefully managed by the MCU coprocessor firmware: allowed via MCU "CStop with PDDS=1" only if it is able to manage the Standby state, so at least if it can lose the MCU SRAM content during this period.

It is possible to switch off the MCU clock and peripherals allocated to the MCU (equivalent to a CStop mode) by using the HOLD\_BOOT feature. This feature is controlled by the MPU via the BOOT\_MCU bit located into the RCC global control register (RCC\_MP\_GCR). It allows the system to be put in Stop, LPLV-Stop or Standby mode. This feature is activated after a reset of the MCU (when MPU is setting MCURST bit of RCC global reset control set register (RCC\_MP\_GRSTCSETR)).

It is also possible to only run code on MPU (MCU in CStop equivalent mode) simply by having MPU not loading any code on MCU side, hence by default when starting the system the MCU is kept inactive (except when boot mode BOOT[2:0] = 0b100).

Note:

When entering LPLV-Stop, if VDDQ\_DDR is not shutdown, to avoid overconsumption on VDDQ\_DDR, the DDR memory must be put in SelfRefresh and DDR PHY must be set in retention mode (setting bit DDRRETEN: DDR retention enable of PWR control register 3 (PWR\_CR3) register).

AN5109 - Rev 5 page 15/37

## 4.5 Power management under Linux

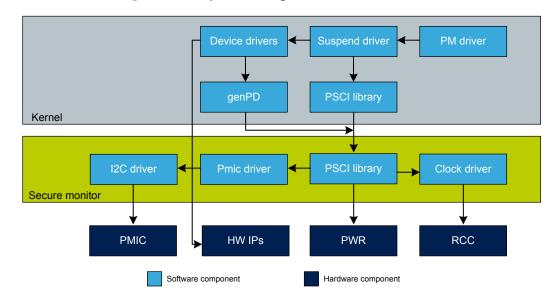

Linux power management is done through the software framework shown in the figure below.

Figure 6. Linux power management software framework

The Linux suspend framework is used to enter the low power modes. It relies on:

- genPD (generic power-domain) framework which allows the definition of power domains and allow the mapping of IPs on those power domains

- PSCI standard to perform the low-level power management process

Additional information can be found on the Power overview wiki article.

The secure monitor regulator framework is used to configure the external power-regulator voltages for each power mode and it relies on an ST STPMIC1x (PMIC) driver and an I2C driver.

#### 4.5.1 Linux power commands mapping to STM32MP15x lines power modes

When using Linux operating system, power mode commands are predefined and this section explains how they are mapped to the STM32MP15x lines hardware low-power modes. It also explains the low-power mode control using the MCU coprocessor.

Under Linux, the user can ask the system to enter into low-power mode with the following direct input command: To enter in Standby mode with DDR off:

'shutdown -h 0'

or to reach any low-power mode among Stop variants and Standby, with DDR in Self-refresh:

echo 'mem' > /sys/power/state

The 'disk', 'freeze' and 'standby' commands are not supported on STM32MP15x lines.

The Cortex®-A7 is put in WFI (wait for interrupt) when entering a low-power mode. However, the system only reaches the targeted low-power mode after the MCU subsystem has been previously configured in the expected low-power mode.

For instance the Linux 'mem' command puts the system in Standby mode only if the MCU has been previously set to CStop mode allowing Standby (for example using HAL PWR EnterStandbyMode() function).

The list of available wakeup sources is not the same for all low-power modes, so a software mechanism is implemented through the genPD framework to ensure that the low-power mode and the activated wakeup source are consistent.

The strategy is to allow the MPU to enter the deepest low-power mode available according to the currently activated wakeup source(s).

AN5109 - Rev 5 page 16/37

#### Example 1

The user activates the UART4 as wakeup source. The UART is powered by  $V_{DDCORE}$ , so all low-power modes that are modifying  $V_{DDCORE}$  are automatically forbidden.

Then, calling echo mem > /sys/power/state results in the MPU entering CStop allowing Stop or LP-Stop.

#### Example 2

The user selects the RTC as wake-up source. The RTC is always powered, whatever the low-power mode status. Then, calling echo mem > /sys/power/state results in the MPU entering CStop allowing Standby.

This mechanism ensures that a blocking situation such as activating UART4 as wakeup source and requesting SoC Standby can never happen.

The system's power mode is the result of both MPU and MCU power states.

The table below lists the deepest possible power mode according to wakeup source groups and lists the equivalence between Linux standard low-power modes and STM32MP15x lines system low-power modes, including the external (Lp)DDR power state (on, off, self refresh (SR)) as it is implemented in the STM32MPU OpenSTLinux Distributions BSP provided environment.

Systems using 32-bit DDR3 interface most likely use external resistance termination on address and command signals. Those systems shall be powered by a resistance termination power supply (VTT) that can be a significant contributor to the overall system consumption during low-power modes.

Hence, by using STPMIC1x, it is possible to switch off this power supply when PWR\_ON signals are pulled down (LP-Stop, LPLV-Stop, Standby) and it is preferred to use LP-Stop rather than Stop mode, because LP-Stop mode does not toggle PWR\_ON in such use case.

Table 12. Deepest power mode per wakeup source group and equivalence between Linux and STM32MP15x lines

| Wakeup<br>source                                                 | Linux<br>command | STM32MP15x<br>system<br>deepest power<br>mode | System<br>DDR   | Linux<br>kernel<br>state | Power consuming | Wakeup<br>time | Comment / Application guideline                                                                                                                                                                                                    |

|------------------------------------------------------------------|------------------|-----------------------------------------------|-----------------|--------------------------|-----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Group 1:<br>USB,<br>CEC, ETH,<br>USART,<br>I <sup>2</sup> C, SPI | "mem"            | Stop or LP-Stop                               | SR<br>(VTT off) | "Suspend-<br>to-ram"     | Medium          | Medium         | LP-Stop: driving external PWR_LP/PWR_ON permits to design custom strategy for external regulator. Typical application is to switch-off DDR3 termination supply (VTT) in DDR3 32 bit design                                         |

| Group 2:<br>PVD, AVD,<br>IWDG,<br>GPIO,<br>LPTIM,<br>DTS         | "mem"            | LPLV-Stop                                     | SR<br>(VTT off) | "Suspend-<br>to-ram"     | Low             | Medium         | LPLV-Stop: save power thanks to power retention. Can be suitable for applications with aggressive power constraints and tolerant with limitations of wakeup source (refer to Table 5. System's low-power mode wakeup capabilities) |

| Group<br>3:BOR,<br>Vbat mon,                                     | "mem"            | Standby                                       | SR              | "Suspend-<br>to-ram"     | Low             | Medium         | Standby saves more power at the expense of wakeup time                                                                                                                                                                             |

| Temp mon,<br>LSE CSS,<br>RTC,<br>TAMP,<br>Wakeup<br>pins         | "shutdown"       | Standby or Off/<br>VBAT                       | Off             | Shutdown                 | Very low        | High           | Wakeup sequence and applicative impact guide the choice between Standby and Off                                                                                                                                                    |

Note: This table assumes that Cortex®-M4 is in CStop mode for all expected Stop, LP-Stop, LPLV-Stop system power modes and in CStop with PDDS=1 for Standby system power mode.

AN5109 - Rev 5 page 17/37

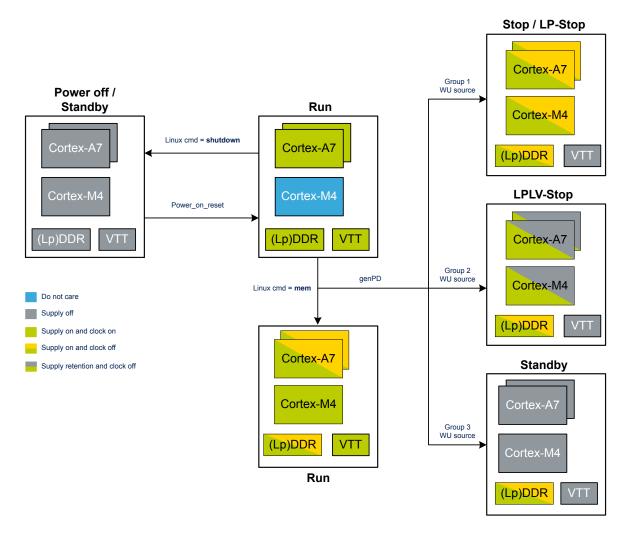

The following figure shows the power state transitions that are available in the system. The same definitions for each wakeup source group used in the table above are considered in this figure. Group 3 wakeup sources are also functional with Group 2 and Group 1 sources. Group 2 is also compatible with Group 1.

If several wakeup sources are activated in different groups, the low-power mode is chosen by respecting the hierarchy stated in the table above. the choice between Stop or LP-Stop is done through settings in the tree of the secure monitor device tree.

Figure 7. Available power state transitions

#### 4.5.2 Controlling MCU power modes under Linux

There are two possible ways to have the MCU control the power modes under Linux; either using "rpmsg" through inter process communication (IPC) or using "independent clusters".

## "rpmsg" through inter process communication (IPC)

The MPU can be seen as the master and the MCU as a coprocessor. Communication between both processors is done using rpmsg. A Linux kernel is running on the dual core MPU in SMP mode, and a free-rtos is running on the MCU.

Some IPs are shared between the processors and a protection is set in place to ensure the registers consistency. When a core needs to access an IP which is under the responsibility of the other core, it sends a request through rpmsg to get the action done.

AN5109 - Rev 5 page 18/37

Regarding entering/exiting into/from Standby state, before MPU "CStop with PDDS=1 CSTBYDIS=1" state, Linux notifies the MCU that the IPC link is suspended. When waking up from system Standby state with MCU\_BEN, the MCU firmware does not communicate with Linux via the IPC. It is only able to send an event (SEV instruction) to the MPU when it needs to wake it up. Then, Linux establishes again the IPC link with the MCU.

#### **Independent clusters**

The MCU may manage its low-power mode states in its SW code (no need for rpmsg from MPU).

## 4.6 Low-power mode exit sequence

Exit from low-power mode (except Standby) can be triggered by interrupt or event depending on how the low-power mode was entered (WFI or WFE). Exit from Standby on MPU can only be triggered by an application reset (like NRST, IWDG), WKUPx pins event or an RTC event.

On exit from low-power mode, it is possible to wake up only MPU, only MCU or both.

- On exit from low-power mode (except Standby) waking up of MPU, MCU or both depends on how the IRQ detection was programmed (visible on MPU, MCU or both).

- On exit from Standby, it is done by setting the two bits MPU\_BEN and MCU\_BEN in RCC boot control register (RCC\_MP\_BOOTCR). This configuration is used by the BootROM during the wakeup from Standby. The BootROM then wakesup MPU, MCU or both.

Note:

- When using STM32MPU OpenSTLinux Distributions, the system always boots only one subsystem: we assume that MCU\_BEN and MPU\_BEN are exclusive to avoid race conditions that may occur during a parallel start up of both subsystems.

- As a consequence, the MCU should be able to interpret some wake up sources that target the MPU subsystem. For instance, if the wake up is due to an RTC alarm (expected by Linux) then the MCU should wake up the MPU.

When the STM32MP15x devices exit from low-power modes, it is important to make sure all external regulators output voltage are setup to the appropriate level and stable before the Run mode can be applied.

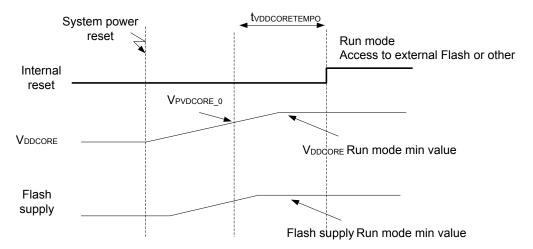

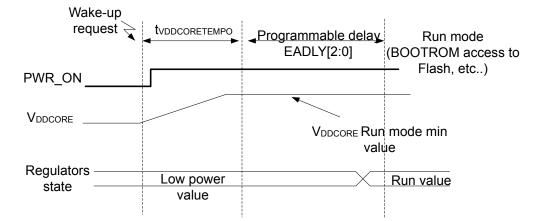

#### 4.6.1 Exit from system power-reset

On system power-reset, the STM32MP15x device monitors the  $V_{DD}$  until it reaches its specified VBOR threshold. Also, the STM32MP15x device monitors  $V_{DDCORE}$  until it reaches the minimum voltage detector threshold ( $V_{PVDCORE}_0$ ) after which it is expected that the  $V_{DDCORE}$  is correctly established before the  $t_{VDDCORETEMPO}$  delay when the internal STM32MP15x device reset signal is deactivated.

In order to find the value of  $t_{VDDCORETEMPO}$ , refer to the table "Embedded reset and Power Control block characteristics" in the STM32MP15x datasheet ( $t_{VDDCORETEMPO}$  minimum value is 200 us). It is expected that the external Flash power supply is ready before STM32MP15x device enters Run mode and reads data from Flash to boot.

- When using STPMIC1x, this is automatically handled since the STPMIC1x does not release the STM32MP15x device NRST pin until all supplies are at their expected value.

- When using a discrete regulator component, the design should make sure those constraints are correctly handled.

AN5109 - Rev 5 page 19/37

Figure 8. Wakeup sequence from system reset

#### 4.6.2 Exit from Stop mode

On exit from Stop mode, the voltages are not changed so there is no issue. However, note that while the PLL1 and PLL2 settings are restored thanks to the hardware "clock restore" automatic feature, other PLL have to be reconfigured if needed. MCU is restarted on HSI clock (HSI clock frequency setting is kept similar to the setting prior entering Stop mode). This also applies for all other "Stop" modes (LP-Stop, LPLV-Stop).

#### 4.6.3 Exit from LP-Stop mode

On exit from LP-Stop mode, V<sub>DDCORE</sub> is not changed, however other voltages at system level might have been switched off or reduced and may need to be set back to their Run mode value.

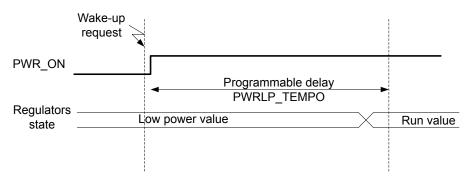

For example the DDR3/DDR3L (x32-bit bus width) termination resistance power supply VTT can be switched off during LP-Stop. The STM32MP15x device waits a programmable delay (PWRLP\_TEMPO) in RCC PWR\_LP delay control register (RCC PWRLPDLYCR) to allow external regulators Run mode value recovery.

- When using STPMIC1x, the exit from LP-Stop mode is notified from STM32MP15x device by the PWR\_ON

pin which toggles back to 1 thus requesting changing supply level on STPMIC1x output supplies. The

STPMIC1x ensures that the PWRLP\_TEMPO can be set to a minimum value of around 1000 us (typical

condition).

- The STM32MP15x maximum output voltage rise time is given by the formula:

For BUCK output: Max {100 us; V2-V1/3.6 10<sup>-3</sup> us} (typical)

with V2: minimum Run mode voltage V1: voltage during low-power mode.

- For LDO output: ramp-up time is defined by the current limit and total amount of capacitance on LDO output. For 10 μF total output capacitance on LDO3, ramp-up time is 20 μs typical.

- For a VDD\_USB of 3.3 V (from BUCK output), the max rise time would be  $3.3/3.6 \ 10^{-3} = 917$  us (typical).

- Exact values in worst case condition must be computed from STPMIC1x datasheet but if wakeup time

is not critical it is recommended to use some reasonable margin (for example 5 ms).

- When using discrete external regulator components, the hardware should set the required power supplies to their Run mode value within the PWRLP\_TEMPO delay.

AN5109 - Rev 5 page 20/37

Figure 9. Wakeup sequence from LP-Stop

#### 4.6.4 Exit from LPLV-Stop mode

On exit from LPLV-Stop mode, on top of power supplies changed like in LP-Stop mode, the  $V_{DDCORE}$  voltage that has been reduced during LPLV-Stop, needs to be set back to its Run mode value.

The STM32MP15x device waits a  $t_{SEL\_VDDCORETEMPO}$  delay during which  $V_{DDCORE}$  is expected to reach its minimum Run mode value. After this  $t_{SEL\_VDDCORETEMPO}$  delay, the STM32MP15x device waits a programmable delay (PWRLP\_TEMPO) in **RCC PWR\_LP delay control register (RCC\_PWRLPDLYCR)** to allow other external regulators Run mode value recovery (as for LP-Stop mode exit sequence described above).

In order to find the value of  $t_{SEL\_VDDCORETEMPO}$  refer to the table "Embedded reset and power control block characteristics" of the corresponding STM32MP15x device datasheet ( $t_{SEL\_VDDCORETEMPO}$  minimum value is 234 us).