# Migration guide from STM32F7 Series to STMH74x/75x, STM32H72x/73x and STMH7A3/7Bx devices

#### Introduction

STM32H74x/75x

Designers of STM32 microcontroller applications must be able to replace easily one microcontroller type with another one from the same product family or from a different family. The reasons for migrating an application to a different microcontroller can be for example:

- To fulfill extended product requirements, extra demands on memory size, or an increased number of I/Os

- Meet cost reduction constraints that require a switch to smaller components and a shrunk PCB area

This application note analyzes the steps required to migrate applications from an existing STM32F7 Series device to one of the following STM32H7 lines below:

Type(1)

Product lines

STM32H7A3/7Bx

STM32H7A3/7B3 and STM32H7B0 Value

STM32H72x/73x

STM32H723/733, STM32H725/735, and STM32H730 Value

STM32H742, STM32H743/753, STM32H745/755 and STM32H750(2)

**Table 1. Applicable products**

- 1. These generic names are sometimes used on this document to refer to the corresponding STM32H7 lines defined on the product lines column

- 2. The dual core aspect of this line's devices is not considered for the purposes of this document.

This application note provides a guideline on both hardware and peripheral migration. To understand fully all the information provided by this application note, the user must be familiar with the STM32 microcontroller family.

For additional information, refer to the following documents available on www.st.com:

- STM32F75xxx and STM32F74xxx advanced Arm<sup>®</sup>-based 32-bit MCUs reference manual (RM0385)

- STM32H745/755 and STM32H747/757 advanced Arm®-based 32-bit MCUs reference manual (RM0399)

- STM32F76xxx and STM32F77xxx advanced Arm<sup>®</sup>-based 32-bit MCUs reference manual (RM0410)

- STM32H742, STM32H743/753 and STM32H750 Value line advanced Arm®-based 32-bit MCUs" reference manual (RM0433)

- STM32H7A3/7B3 and STM32H7B0 Value line advanced Arm<sup>®</sup>-based 32-bit MCUs reference manual (RM0455)

- STM32H723/733, STM32H725/735, and STM32H730 Value line advanced Arm<sup>®</sup>-based 32-bit MCUs reference manual (RM0468)

# 1 General information

This document applies to all STM32F7 Series devices and to the STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx lines devices. All these products are  $Arm^{@}$ -based microcontrollers.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

AN5293 - Rev 6 page 2/60

#### 2 STM32H7 devices overview

STM32H7 devices offer extra performance compared to the STM32F7 Series devices without additional complexity. STM32H7 delivers its maximum theoretical performance by taking advantage of an L1-cache regardless of whether the code is executed from the embedded flash memory or the external memory.

STM32H7 devices, as Cortex<sup>®</sup>-M7 variants, are compatible with the STM32F7 Series devices (for the common packages). This compatibility allows customers to easily migrate from STM32F7 towards STM32H7 devices and to benefit from their significantly higher performance and their advanced peripherals.

STM32H7 devices include a larger set of peripherals with advanced features and optimized power consumption compared to the STM32F7 devices such as:

- Low-power universal asynchronous receiver transmitter (LPUART)

- Single wire protocol master interface (SWPMI)

- FD controller area network (FDCAN)

- Operational amplifiers (OPAMP)

- Comparator (COMP)

- Voltage reference buffer (VREFBUF)

- Switch mode power supply step down converter (SMPS)

This migration guide covers the migration from STM32F7 Series devices towards STM32H7A3/7Bx, STM32H72x/73x, and STM32H74x/75x devices.

The new features present on STM32H7 devices but not already present on STM32F7 Series devices or other STM32H7 devices are not covered in this document. Refer to the STM32H7 devices reference manual and datasheets for more details.

The following table presents the main differences between STM32H7A3/7Bx, STM32H72x/73x, and STM32H74x/75x devices at a glance. The following sections describe the differences in detail.

Table 2. STM32H7 lines differences at a glance

| Fe     | eature                | STH32H74x/75x                                                                                                                            | STH32H7Ax/7Bx                                                                                  | STH32H72x/73x                                                                                                                                    |

|--------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Core   |                       | Arm Cortex-M7, MPU, DP-FPU,<br>L1 16KB-D/16KB-I<br>ARM Cortex-M4, MPU, SP-FPU,<br>ART                                                    | Arm Cortex-M7, MPU, DP-FPU, L1 16KB-D/16KB-I -                                                 | Arm Cortex-M7, MPU, DP-FPU,<br>L1 32KB-D/32KB-I                                                                                                  |

| Opera  | ting range            | 1.62 to 3.6 V and Tj–40 to +125° C Up to +140° C with SMPS VOS1 limited to 125°C Vcore @VOS0: Tj limited to 105°C, VDD min 1.7 V No SMPS | 1.62 to 3.6 V and Tj–40 to<br>+130 ° C<br>Vcore @VOS0:<br>Tj limited to 105°C<br>VDD min 1.7 V | 1.62 to 3.6 V and Tj-40 to +125° C Up to 140° C with SMPS VOS1 up to 140°C Vcore @VOS0: Tj limited to 105°C VDD min 1.7 V LDO VDD min 2.2 V SMPS |

|        | 17 frequency/<br>MIPS | 480 MHz / 1027 DMIPS in VOS0<br>400 MHz / 856 DMIPS in VOS1                                                                              | 280 MHz / 599 DMIPS in<br>VOS0<br>225 MHz / 481 DMIPS in<br>VOS1                               | 550 MHz / 1177 DMIPS in VOS0<br>400 MHz / 856 DMIPS in VOS1                                                                                      |

|        | d AHB max<br>quency   | 240 MHz                                                                                                                                  | 280 MHz                                                                                        | 275 MHz                                                                                                                                          |

| APB ma | x frequency           | 120 MHz                                                                                                                                  | 140 MHz                                                                                        | 137.5 MHz                                                                                                                                        |

| Debug  | SWD/<br>JTAG/ETM      | I/I/4 Kbytes                                                                                                                             | I/I/4 Kbytes                                                                                   | I /I/2 Kbytes                                                                                                                                    |

| Low-po | ower modes            | Sleep, Stop, Standby, Vbat                                                                                                               | Sleep, Stop, <b>Retention,</b><br>Standby, Vbat                                                | Sleep, Stop, Standby, Vbat                                                                                                                       |

AN5293 - Rev 6 page 3/60

#### 2.1 STM32H74x/75x devices

The migration from STM32F7 Series devices towards STM32H743/753 devices is covered in detail in the application note *Migration of microcontroller applications from STM32F7 Series to STM32H743/753 Line* (AN4936).

The maximum theoretical performance of the STM32H74x/75x devices  $Cortex^{@}$  -M7 core is 1414 CoreMark / 1027 DMIPS at 480 MHZ  $f_{CPLI}$ .

When compared to other STM32H7 devices, STM32H74x/75x devices offer the following additional features:

- one Cortex<sup>®</sup>-M4 (STM32H745/755 only)

- one high-resolution timer

- one additional 16b ADC

- MIPI-DSI interface for driving the DSI display (STM32H747/757)

- two additional SAI

- one additional USB (FS)

When compared to STM32H72x/73x devices, STM32H74x/75x devices offer the following additional features:

- additional flash and RAM memory

- one additional passive tamper

- · additional RAM for debug trace

When compared to STM32H7A3/7Bx devices, STM32H74x/75x devices offer the following additional features:

two additional low-power timers.

#### 2.2 STM32H72x/73x devices overview

The maximum theoretical performance of the STM32H72/73x devices  $Cortex^{\$}$  -M7 core is 2778CoreMark / 1177 DMIPS at 550 MHz  $f_{CPU}$ .

STM32H72x/73x devices are the fastest STM32H7 Series devices.

When compared to other STM32H7 devices, STM32H72x/73x devices offer the following additional features:

- · more data and instruction cache

- possibility to increase instruction tightly coupled memory size

- FMAC (filtering) and Cordic (trigonometric) blocks for mathematical acceleration

- low pin-count package (UFQFPN68)

- more 32b timers, FDCAN, UART, USART, I2C

- one low-power 12b ADC in the low-power domain

- increased acceptable temperature at high frequency (400 MHz)

When compared to STM32H74x/75x devices, STM32H72/73x devices offer the following additional features:

- two OCTOSPI interfaces, instead of a single QUADSPI

- possibility to store encrypted code or data on external Octo-SPI memories (for STM32H73x devices)

- a parallel synchronous slave interface (PSSI)

- · a digital temperature sensor

When compared to STM32H7A3/7Bx devices, STM32H72x/73x devices offer the following additional features:

- Ethernet

- · two low-power timers added.

#### 2.3 STM32H7A3/7Bx devices

The maximum theoretical performance of the STM32H7A3/7Bx devices  $Cortex^{\$}$  -M7 core is 1414 CoreMark / 599 DMIPS at 280-MHZ  $f_{CPU}$ .

STM32H7A3/7Bx devices are also the entry point of the wider STM32H7 Series devices, which can be seen as an easy stepladder to benefit from the high performance, the rich connectivity and the enhanced features of this advanced platform.

AN5293 - Rev 6 page 4/60

When compared to other STM32H7 devices, STM32H7A3/7Bx devices offer the following additional features:

- · further optimized power consumption, significant in the low-power modes

- simplification of the power domains

- · increased internal RAM size, very useful for graphics applications

- DFSDM increased to nine filters with dedicated DMA

- graphical oriented memory management unit (GFXXMMU)

- one DAC in low-power domain

- new tampers and active tamper which increases the security level

When compared to STM32H743/753 devices, STM32H7A3/7Bx devices offer the following additional features:

- two OCTOSPI interfaces, instead of a single QUADSPI

- possibility to store encrypted code or data on external Octo-SPI memories (for STM32H7B3 devices)

- a parallel synchronous slave interface (PSSI)

- a digital temperature sensor

When compared to STM32H72x/73x devices, STM32H7A3/7Bx devices offer the following additional features:

- · increased flash memory size

- ipeg decoder

- DFSDM increased to nine filters with dedicated DMA

- graphical oriented memory management unit (GFXXMMU)

- additional RAM for debug trace.

AN5293 - Rev 6 page 5/60

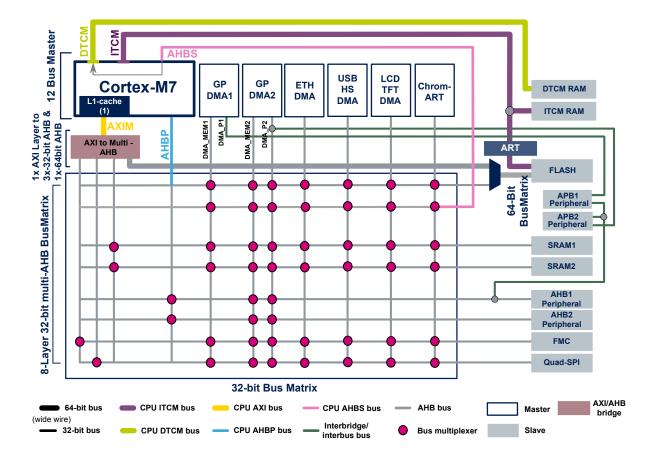

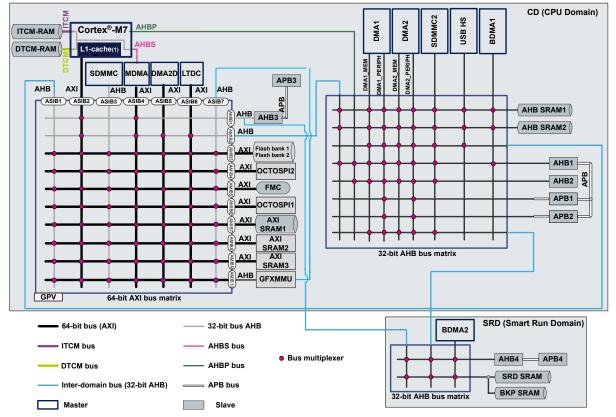

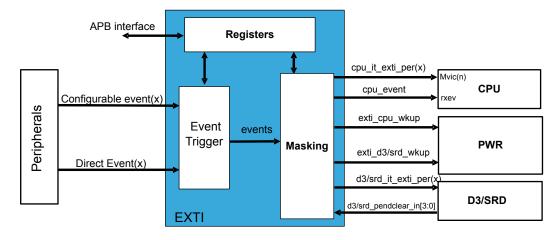

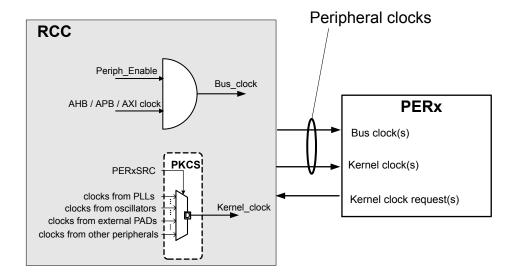

# System architecture differences between STM32F7 and STM32H7 Series

STM32F7 Series devices have one single available domain: an embedded AHB bus matrix.

In STM32H72x/73x and STM32H74x/75x devices there are three domains: an AXI bus matrix and two AHB bus matrices. Bus bridges permit the interconnection of the bus masters with the bus slaves:

- **D1 domain**: is the high bandwidth / high performance domain with the Cortex-M7 core and acceleration mechanisms. This domain encompasses the high-bandwidth features and the smart management thanks to the AXI bus matrix.

- D2 domain: is the "I/O processing" domain. It encompasses most peripherals that are less bandwidth demanding.

- **D3 domain**: it embeds up to 64-Kbyte RAM and has a subset of peripherals to run the basic functions while the domains 1 and 2 can be shut-off to save power (autonomous mode).

For the STM32H7A3/7Bx devices, the D1 and D2 domains are merged in a single domain called CD domain (or CPU domain) and the D3 domain evolved into a domain called SRD domain (or smart-run domain).

- **CD domain**: the CPU domain encompasses the Cortex-M7 core, the AXI bus matrix, an AHB bus matrix and most of the peripherals.

- **SRD domain**: it embeds a 32-Kbyte RAM and some peripherals to run basic functions while the CPU domain is in low-power mode (autonomous mode). For STM32H7A37Bx devices the power consumption in autonomous and Stop modes of this domain has been further optimized.

The differences in power modes are addressed on the Power (PWR) section of this application note.

The table below and the two subsequent figures illustrate the system architecture differences between STM32F7 Series, STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices.

Table 3. Available bus matrix on STM32F7 Series, STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices

| Device                          | AHB bus matrix | AXI bus matrix |

|---------------------------------|----------------|----------------|

| STM32F7 Series                  | 1              | NA             |

| STM32H74x/75x and STM32H72x/73x | 2              | 1              |

| STM32H7A3/7Bx                   | 2              | 1              |

AN5293 - Rev 6 page 6/60

Figure 1. STM32F7 Series devices system architecture

#### Note: I/D cache size:

- For STM32F74xxx and STM32F75xxx devices: 4 Kbytes.

- For STM32F72xxx and STM32F73xxx devices: 8 Kbytes.

- For STM32F76xxx and STM32F77xxx devices: 16 Kbytes.

AN5293 - Rev 6 page 7/60

AHB bus matrix (D3 domain)

Masters Masters

Note 1: Not available in STM32H742xx devices DMA1 AHBP USB HS1 USB HS2 ITCM-RAM Cortex®-M7 Note 2: Not available in DTCM-RAM STM32H750xx devices DMA1\_PERIP DMA1\_MEM DMA2\_MEM DMA2\_PERIP MDMA DMA2D SDMMC1 D1-to-D2 AHB bus AHB AHB ASIB1 (ASIB2) (ASIB3) (ASIB4) (ASIB5) (AS APB3 SRAM1 APB AHB3 SRAM2 Flash 1 SRAM3(1) Flash 2(2) AHB1 AHB2 A QUADSPI APB1 AXI SRAM APB2 5 GPV 64-bit AXI bus matrix 1 D1 Domain D2-to-D1 AHB bus 32-bit AHB bus matrix 2 - 64-bit bus (AXI) 32-bit bus AHB D2 Domain D2-to-D1 AHB bus - ITCM bus AHBS bus D1-to-D3 AHB bus D2-to-D3 AHB bus AHBP bus Bus multiplexer DTCM bus BDMA n The domain number Inter-domain bus (32-bit AHB) APB bus 3 AHB4 APB4 AXI bus matrix (D1 domain) AHBx pripherals Master AHB bus matrix (D2 domain) APBx pripherals SRAM4

interfaces

Slave

interfaces

32-bit AHB bus matrix

D3 Domain

Bckp SRAM

MSv44011V13

Figure 2. STM32H74x/75x devices system architecture

Note: STM32H74x/75x devices supports 16-Kbyte instruction cache and 16-Kbyte data cache.

Internal memory

External interface

AN5293 - Rev 6 page 8/60

USB HS1 Cortex®-M7 ITCM-RAM L1-Cache DTCM-RAM Shared SRAM MA1\_PERIPH PERIP DMA2\_MEM D1-to-D2 DMA2D SDMMC1 MDMA AHB bus DMA2 AHB AXI. SIB2 ASIB3 ASIE ASIB1 AS 34 ASIB5 SRAM1 SRAM2 Flash FMC AHB1 AHB2 A OTFDEC2 -OCTOSPI2 OTFDEC1 OCTOSPI1 -APB1 APB2 AHB AHB3 APB3 ⊨ GPV 64-bit AXI bus matrix 1 **D1** Domain 32-bit AHB bus matrix 2 D2-to-D1 AHB bus D2-to-D1 AHB bus D1-to-D3 AHB bus D2-to-D3 AHB bus 32-bit bus AHB • 64-bit bus (AXI) ITCM bus AHBS bus AHBP bus Bus multiplexer DTCM bus **BDMA** n The domain number Inter-domain bus (32-bit APB bus AHB) 6 3 AXI bus matrix (D1 domain) AHBx pripherals AHB4 APB4 AHB bus matrix (D2 Master APBx pripherals SRAM4 interfaces AHB bus matrix (D3 Internal memory 32-bit AHB bus matrix Bckp SRAM domain) Slave D3 Domain interfaces Masters External interface

Figure 3. STM32H72x/73x devices system architecture

MSv66817V2

Note: STM32H72x/73x devices supports 32-Kbyte instruction cache and 32-Kbyte data cache.

AN5293 - Rev 6 page 9/60

Figure 4. STM32H7A3/7Bx devices system architecture

Note: STM32H7B0x support a single bank (flash Bank1 only)

AN5293 - Rev 6 page 10/60

# 4 Hardware migration

#### 4.1 Available packages

The available packages on STM32F7 Series, STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices are listed in the table below.

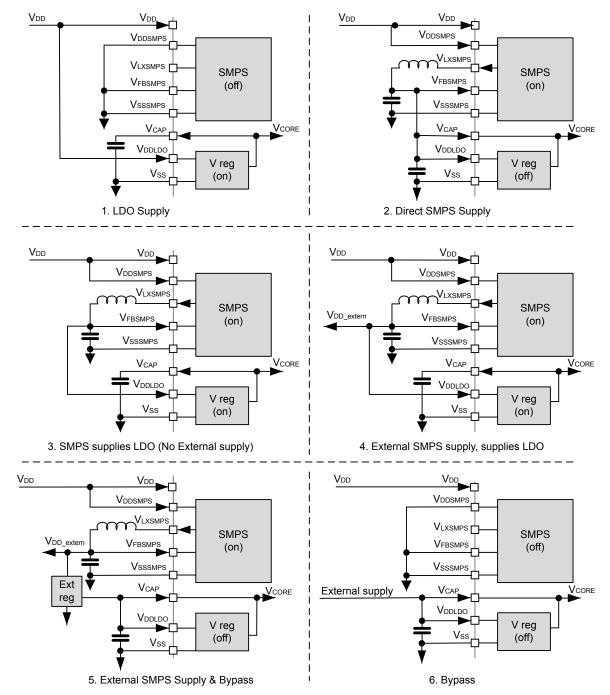

STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices support the switched-mode power supply (SMPS) step-down converter available in some specific packages, which are not compatible with the legacy packages (see table below and refer to Figure 6).

Table 4. Available packages on STM32F7 Series, STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices

| Package             | STM32F7 Series           | STM32H74x/75x | STM32H72x/73x | STM32H7A3/7Bx | Regulator          |  |  |

|---------------------|--------------------------|---------------|---------------|---------------|--------------------|--|--|

| LQFP64              |                          | NA            | NA            |               |                    |  |  |

| LQFP100             |                          |               |               |               |                    |  |  |

| TFBGA100            | Available Available      |               | Available     | Available     |                    |  |  |

| LQFP144             |                          |               | Available     |               |                    |  |  |

| UFBGA144            |                          | NA            |               | NA            |                    |  |  |

| UFBGA169            | NA                       |               |               | INA           | LDO <sup>(1)</sup> |  |  |

| UFBGA176+25         |                          | Available     |               | Available     |                    |  |  |

| LQFP176             | Available NA Available   |               | NA            | Available     |                    |  |  |

| LQFP208             |                          |               |               | NA            |                    |  |  |

| TFBGA216            |                          | NA            |               | Available     |                    |  |  |

| TFBGA240            |                          | Available     | NA            | NA            |                    |  |  |

| VFQFPN68 SMPS       |                          |               |               |               |                    |  |  |

| LQFP100 SMPS        |                          | NA            |               |               |                    |  |  |

| TFBGA100 SMPS       |                          |               |               |               |                    |  |  |

| LQFP144 SMPS        |                          | Available     | Available     |               |                    |  |  |

| UFBGA169 SMPS       | NA                       | NA            |               | Available     | LDO/SMPS/          |  |  |

| UFBGA176+25<br>SMPS |                          |               |               |               | regulator bypass   |  |  |

| LQFP176 SMPS        |                          | Available     |               |               |                    |  |  |

| LQFP208 SMPS        |                          |               | NA            | NA            |                    |  |  |

| TFBGA225 SMPS       |                          | NA            |               | Available     |                    |  |  |

| WLCSPxxx            | Specific for each device |               |               |               |                    |  |  |

<sup>1.</sup> STM32F7 Series and STM32H7A3/7Bx Ines devices can be used in Regulator bypass mode.

AN5293 - Rev 6 page 11/60

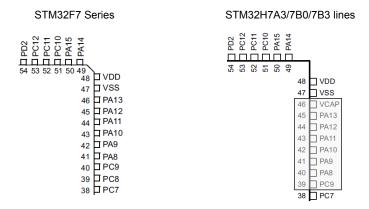

#### 4.2 Pinout compatibility

STM32F7 Series devices and STM32H74x/75x devices are pin to pin compatible with the STM32H7A3/7Bx devices (with some restrictions for the LQFP64, TFBGA100, LQFP176, UFBGA176 and TFBGA216 packages). In STM32H72x/73x devices, LQFP100 SMPS pin 72 is VCAP whereas it is PE0 for STM32H7A3/7Bx.

In STM32H7A3/7Bx devices, a second VCAP pin is added for the LQFP64 package; in consequence, several GPIOs are no longer compatible with STM32F7 Series devices. See below table and figure for more details.

| Package | Pin | STM32F7 Series | STM32H7A3/7Bx |

|---------|-----|----------------|---------------|

|         | 38  | PC7            | PC7           |

|         | 39  | PC8            | PC9           |

|         | 40  | PC9            | PA8           |

|         | 41  | PA8            | PA9           |

| LQFP64  | 42  | PA9            | PA10          |

|         | 43  | PA10           | PA11          |

|         | 44  | PA11           | PA12          |

|         | 45  | PA12           | PA13          |

|         | 46  | PA13           | VCAP          |

Table 5. LQFP64 package compatibility between STM32F7 Series and STM32H7A3/7Bx devices

Figure 5. LQFP64 package compatibility

For the TFBGA100, LQFP176, UFBGA176 and TFBGA216 packages, the BYPASS\_REG pin is replaced in the STM32H7 Series with a VSS pin.

For the STM32F7 Series devices, the BYPASS\_REG pin connected to VDD permits to select the mode where the internal regulator is switched off and the core supply is externally provided.

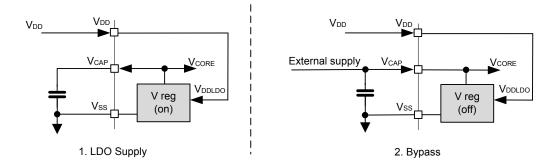

For the STM32H7 Series devices, there is no dedicated pin that defines if the regulator is in bypass mode or which regulator(s) is/are used. It is done through software at system startup. Both LDO and SMPS regulators are enabled by default during startup and the user software defines if the LDO or the SMPS or both are switched off (see Figure 6).

Note:

Special care has to be taken if an STM32F7 Series device is replaced with an STM32H7 device on a PCB board where the BYPASS\_REG pin is set to VDD (see the table below).

The following table and figure illustrate the BYPASS\_REG pin incompatibility in TFBGA100, LQFP176, UFBGA176 and TFBGA216 packages and the system supply configuration on the STM32F7 Series devices and STM32H74x/75x devices.

AN5293 - Rev 6 page 12/60

Table 6. BYPASS\_REG pin incompatibility between STM32F7 Series, STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices

| Package     | Pin/<br>ball | STM32F7<br>Series | STM32H74x/<br>75x | STM32H72x/<br>73x | STM32H7A3/7Bx | Comment                                                                                                            |

|-------------|--------------|-------------------|-------------------|-------------------|---------------|--------------------------------------------------------------------------------------------------------------------|

| TFGA100     | Ball<br>E6   | BYPASS_REG        | VSS               | VSS               | VSS           | Impacts only the boards designed with STM32F7 Series devices in the regulator bypass mode  (BYPASS REG set to VDD) |

| LQFP176     | Pin<br>48    |                   | VSS               | NA                |               |                                                                                                                    |

| UFBGA176+25 | Ball<br>L4   |                   | VSS               | NA                |               |                                                                                                                    |

| TFBGA216    | Ball<br>L5   |                   | NA                | NA                |               | _ ,                                                                                                                |

AN5293 - Rev 6 page 13/60

Figure 6. System supply configuration on STM32H74x/75x and STM32H7A3/7Bx devices with SMPS

MSv48170V3

AN5293 - Rev 6 page 14/60

Figure 7. System supply configuration on STM32H74x/75x and STM32H7A3/7Bx devices without SMPS

AN5293 - Rev 6 page 15/60

### 4.3 System bootloader

The system bootloader is located in the system memory, programmed by ST during production. The system bootloader permits to reprogram the flash memory using one of the supported serial interfaces. More details are provided in the following table:

Table 7. STM32F7 Series, STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices bootloader communication peripherals

| System bootloader peripherals | STM32F7 Series<br>I/O pin | STM32H74x/75x I/O pin     | STM32H7A3/7Bx I/O pin      | STM32H72x/73x I/O pin |  |  |

|-------------------------------|---------------------------|---------------------------|----------------------------|-----------------------|--|--|

| DFU                           |                           | USB OTG FS (PA            | .11 / PA12) in device mode |                       |  |  |

| USART1                        |                           | P                         | A9 / PA10                  |                       |  |  |

| USART 2                       | NA                        |                           | PA2 / PA3                  |                       |  |  |

| LICARTO                       | PB10 / PB11               | DD40                      | / PB11                     | PB10 / PB11           |  |  |

| USART3                        | PC10 / PC11               | PB10                      | PD8 / PD9                  |                       |  |  |

| I2C1                          |                           | F                         | PB6 / PB9                  |                       |  |  |

| I2C2                          |                           | F                         | PF0 / PF1                  |                       |  |  |

| I2C3                          |                           | F                         | PA8 / PC9                  |                       |  |  |

| SPI1                          |                           | PA7 / F                   | PA6 / PA5 / PA4            |                       |  |  |

| SPI2                          |                           | PI3 / PI2 / PI1 / PI0     | )                          | NA                    |  |  |

| SPI3                          | NA                        |                           | PC12 / PC11/ PC10 / PA15   |                       |  |  |

| SPI4                          |                           | PE14 / PE13 / PE12 / PE11 |                            |                       |  |  |

| FDCANA                        | PB5 / PB13 <sup>(1)</sup> | NIA                       | PH13 / PH14                | PH13 / PH14           |  |  |

| FDCAN1                        | PD0 / PD1 <sup>(2)</sup>  | NA                        | PD1 / PD0                  | PD1 / PD0             |  |  |

<sup>1.</sup> Available on the STM32F74xxx/75xxx and STM32F76xxx/77xxx devices.

AN5293 - Rev 6 page 16/60

<sup>2.</sup> Available on the STM32F72xxx/73xxx devices.

# 5 Boot mode compatibility

The STM32F7 Series devices, the STM32H74x/75x, STM32H72x/73x, and the STM32H7A3/7Bx devices boot spaces are based on BOOT0 and boot address option bytes as described in the table below.

For the STM32F7 Series devices, the boot base address supports any address in the range from 0x0000 0000 to 0x3FFF FFFF while in STM32H74x/75x, STM32H72x/73x, and the STM32H7A3/7Bx, the boot base address supports any address in the range from 0x0000 0000 to 0x3FFF 0000.

Table 8. Boot mode compatibility between STM32F7 Series, STM32H74x/75x, STM32H72x/73x, and STM32H7A3/7Bx devices

| Boot mode selection |                           | STM32F7 Series                                           | STM32H74x/75x, STM32H72x/73x,                            |  |

|---------------------|---------------------------|----------------------------------------------------------|----------------------------------------------------------|--|

| Boot                | Boot address option bytes | STWISZET Series                                          | and STM32H7A3/7Bx                                        |  |

| 0                   | BOOT ADD0[15:0]           | Boot address defined by user option byte BOOT_ADD0[15:0] | Boot address defined by user option byte BOOT_ADD0[15:0] |  |

| 0                   | BOO1_ADD0[15.0]           | ST programmed value: flash on ITCM at 0x0020 0000        | ST programmed value: flash memory at 0x0800 0000         |  |

| 1 DOOT ADDIVIS O    |                           | Boot address defined by user option byte BOOT_ADD1[15:0] | Boot address defined by user option byte BOOT_ADD1[15:0] |  |

| 1                   | BOOT_ADD1[15:0]           | ST programmed value: System bootloader at 0x0010 0000    | ST programmed value: System bootloader at 0x1FF0 0000    |  |

AN5293 - Rev 6 page 17/60

## 6 Peripheral migration

#### 6.1 STM32 product cross-compatibility

The STM32 microcontrollers embed a set of peripherals, which can be classed in three categories:

- The first category is for the peripherals that are by definition common to all products. Those peripherals are identical, so they have the same structure, registers, and control bits. There is no need to perform any firmware change to keep the same functionality at the application level after migration. All the features and behavior remain the same.

- The second category is for the peripherals that are shared by all STM32 products but have only minor differences (in general to support new features), so the migration from one product to another is very easy and does not need any significant new development effort.

- The third category is for peripherals that have been considerably changed from one product to another (new architecture, new features...). For this category of peripherals, the migration requires a new development at application level.

This table below shows the STM32 peripheral compatibility between the STM32F7 Series, STM32H74x/75x and STM32H7A3/7Bx devices. The software compatibility mentioned in this table refers only to the register description for *low-level* drivers. The Cube hardware abstraction layer (HAL) is compatible between STM32F7 Series devices, STM32H74x/75x and STM32H7A3/7Bx devices.

Table 9. Peripheral summary for STM32F7 Series, STM32H74x/75x, STM32H72x/73x, and STM32H7A3/7Bx devices

| Peripheral   |                   | STM32F7<br>Series                                                                                       | STM32H74x/75x                                                                                      | STM32H7A3/7Bx                | STM32H72x/73x              | Compatibility/<br>comments                                                                                      |

|--------------|-------------------|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|

| Power supply |                   | <ul> <li>Power supply for I/Os: 1.71 to 3.6 V</li> <li>Internal regulator VDD = 1.7 to 3.6 V</li> </ul> | <ul> <li>Power supply</li> <li>Internal regula</li> <li>SMPS step do</li> <li>VDDSMPS =</li> </ul> | -                            |                            |                                                                                                                 |

| Maximum      | frequency         | 216 MHz                                                                                                 | 480 MHz                                                                                            | 280 MHz                      | 550 MHz                    | -                                                                                                               |

| MPU regio    | n number          | 8                                                                                                       |                                                                                                    | 16                           |                            | -                                                                                                               |

| Flash m      | Flash memory      |                                                                                                         | Up to 2 Mbytes single or dual bank                                                                 |                              |                            | With ECC protection<br>for STM32H7 Series<br>devices                                                            |

|              | System            | 512 Kbytes                                                                                              | ~1 Mbyte<br>(992 Kbytes)                                                                           | ~1.3 Mbytes<br>(1312 Kbytes) | 564 Kbytes                 | With ECC<br>protection for<br>STM32H72/72/724/75,<br>ECC protection on<br>TCM and cache only<br>for STM32H7A/7B |

| SRAM         | ITCM              | 16 Kbytes                                                                                               | 64 Kbytes                                                                                          |                              | 64 Kbytes to<br>256 Kbytes | -                                                                                                               |

|              | DTCM              |                                                                                                         | 128                                                                                                | 8 Kbytes                     |                            | -                                                                                                               |

|              | Data cache        |                                                                                                         | 16 Kbytes                                                                                          |                              | 32 Kbytes                  | -                                                                                                               |

|              | Instruction cache |                                                                                                         | 16 Kbytes                                                                                          |                              | 32 Kbytes                  | -                                                                                                               |

|              | Backup            |                                                                                                         | 4                                                                                                  | Kbytes                       |                            | -                                                                                                               |

| Common       | FMC               |                                                                                                         |                                                                                                    | 1                            |                            | -                                                                                                               |

| peripherals  | QUADSPI           |                                                                                                         | 1                                                                                                  | N                            | IA                         | _                                                                                                               |

AN5293 - Rev 6 page 18/60

| Peripheral         |                                              | STM32F7<br>Series        | STM32H74x/75x                                                       | STM32H7A3/7Bx                                     | STM32H72x/73x                                               | Compatibility/<br>comments                           |

|--------------------|----------------------------------------------|--------------------------|---------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------|

| Common peripherals |                                              |                          | 2                                                                   | All QUADSPI features<br>are covered by<br>OCTOSPI |                                                             |                                                      |

|                    | Ethernet                                     |                          | 1                                                                   | NA                                                | 1                                                           | -                                                    |

|                    | High resolution                              | NA                       | 1                                                                   | N                                                 | A                                                           | -                                                    |

| Timers             | General purpose                              |                          | 10                                                                  |                                                   | 12                                                          | -                                                    |

| Timero             | PWM                                          |                          |                                                                     | 2                                                 |                                                             | -                                                    |

|                    | Basic                                        |                          |                                                                     | 2                                                 |                                                             | -                                                    |

|                    | Low-power                                    | 1                        | 5                                                                   | 3                                                 | 5                                                           | -                                                    |

| RNO                | 3                                            |                          |                                                                     | Yes                                               |                                                             | -                                                    |

|                    | SPI/I2S                                      | 4/3                      | 6/3                                                                 | 6/                                                | /4                                                          | Wakeup from<br>stop capability for<br>STM32H7 Series |

|                    | I2C                                          |                          | 4                                                                   |                                                   | 5                                                           | -                                                    |

|                    | USART                                        |                          | 4                                                                   | Ę                                                 | 5                                                           | -                                                    |

|                    | UART                                         |                          | 4                                                                   | Ę                                                 | 5                                                           | -                                                    |

|                    | LPUART                                       | NA                       |                                                                     | 1                                                 |                                                             | -                                                    |

|                    | SAI                                          | 2                        | 4                                                                   | 2                                                 |                                                             | -                                                    |

|                    | SPDIFRX                                      |                          | 4 inputs                                                            |                                                   |                                                             |                                                      |

|                    | SWPMI                                        | NA 1                     |                                                                     |                                                   |                                                             | -                                                    |

| Communication      | MDIO                                         |                          | -                                                                   |                                                   |                                                             |                                                      |

| interfaces         | SDMMC                                        |                          | -                                                                   |                                                   |                                                             |                                                      |

|                    | CAN                                          | x3 CANs<br>(2.0B active) | x2 CAN FD (FDCAN1 supports TTCAN)  x3 CAN FD (FDCAN1 support TTCAN) |                                                   | (FDCAN1 supports                                            | -                                                    |

|                    | USB OTG<br>FS                                |                          | 1 NA                                                                |                                                   | A                                                           | -                                                    |

|                    | USB OTG<br>HS                                | 1                        |                                                                     |                                                   |                                                             | Support FS and HS with ULPI                          |

|                    | HDMI-CEC                                     |                          |                                                                     | 1                                                 |                                                             | -                                                    |

|                    | DFSDM                                        |                          | 1                                                                   | 2                                                 | 1                                                           | -                                                    |

|                    | number of filters                            |                          | 4                                                                   | 8/1                                               | 4                                                           | -                                                    |

| Digital camera     | DCMI                                         |                          |                                                                     | 1                                                 |                                                             | -                                                    |

| interface          | PSSI                                         |                          | NA                                                                  | 1                                                 |                                                             | -                                                    |

| MIPI-DS            | l host                                       |                          | 1                                                                   | NA NA                                             |                                                             | Available only on specific packages                  |

|                    | LCD-TFT                                      |                          |                                                                     | 1                                                 |                                                             | -                                                    |

| Graphics           | Chrom-<br>ART<br>Accelerator<br>™<br>(DMA2D) |                          |                                                                     | 1                                                 | YCbCr to RGB color<br>space conversion on<br>STM32H7 Series |                                                      |

|                    | JPEG<br>Codec                                |                          | 1                                                                   |                                                   | NA                                                          |                                                      |

AN5293 - Rev 6 page 19/60

| Periph                     | eral                              | STM32F7<br>Series                                                           | STM32H74x/75x                                                                                                                                                                                                                                                        | STM32H7A3/7Bx                                                                                                                                                                                                                                                                     | STM32H72x/73x                                                                                                                                                                                                                                                        | Compatibility/<br>comments                                                                                                                                                                                                                 |

|----------------------------|-----------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Graphics                   | GFXMMU                            |                                                                             | NA                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                 | NA                                                                                                                                                                                                                                                                   | Graphical oriented memory management unit                                                                                                                                                                                                  |

| GPIC                       | Os                                | Up to 159                                                                   | Up to                                                                                                                                                                                                                                                                | 168                                                                                                                                                                                                                                                                               | Up to 128                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                                          |

|                            | ADC 12b                           | 3                                                                           | N                                                                                                                                                                                                                                                                    | A                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                                                                                    | Available down to                                                                                                                                                                                                                          |

|                            | ADC 16b                           | NA                                                                          | 3                                                                                                                                                                                                                                                                    | 2                                                                                                                                                                                                                                                                                 | 2                                                                                                                                                                                                                                                                    | 1.62 V for STM32H7<br>Series                                                                                                                                                                                                               |

| Analog                     | 12-bit DAC                        | 2 c                                                                         | hannels                                                                                                                                                                                                                                                              | 3 channels                                                                                                                                                                                                                                                                        | 2 channels                                                                                                                                                                                                                                                           | -                                                                                                                                                                                                                                          |

| peripherals                | Operational amplifiers            | NA                                                                          |                                                                                                                                                                                                                                                                      | 2                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                          |

|                            | Ultra-low-<br>power<br>comparator | NA                                                                          | 2                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                          |

|                            |                                   | General- purpose DMA: 16-stream DMA controller with FIFOs and burst support | 4 DMA controllers to unload the CPU  • x1 high-speed general-purpose master direct memory access controller (MDMA)  • x2 dual-port DMAs with FIFO and request router capabilities for optimal peripheral management  • x1 basic DMA with request router capabilities | to unload the CPU  X1 high-speed general-purpose master direct memory access controller (MDMA)  X2 dual-port DMAs with FIFO and request router capabilities for optimal peripheral management  X1 basic DMA with request router capabilities  X1 basic DMA dedicated to the DFSDM | 4 DMA controllers to unload the CPU  • x1 high-speed general-purpose master direct memory access controller (MDMA)  • x2 dual-port DMAs with FIFO and request router capabilities for optimal peripheral management  • x1 basic DMA with request router capabilities | On STM32H7 Series:  No limitation for peripheral requests thanks to DMAMUX  DMA1 and DMA2 can access to peripherals in APB1/APB2 buses  Peripheral request mapping is no longer managed by the DMA controller but by the DMAMUX controller |

| Cryptographic acceleration |                                   | • HMAC                                                                      | D5, SHA-1, SHA-2)                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                      | -                                                                                                                                                                                                                                          |

|                            | ROP                               | True rand     ROP                                                           | om number generato                                                                                                                                                                                                                                                   | r<br>one secure-only area                                                                                                                                                                                                                                                         | e ner flach hank                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                          |

| Security                   | Tamper                            | Tamper                                                                      | Tamper                                                                                                                                                                                                                                                               | Active tamper                                                                                                                                                                                                                                                                     | Tamper                                                                                                                                                                                                                                                               | <u>-</u><br>-                                                                                                                                                                                                                              |

|                            | F -                               | 10.0                                                                        | F -                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   | F -                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                            |

AN5293 - Rev 6 page 20/60

## 6.2 Memory organization

#### 6.2.1 RAM size

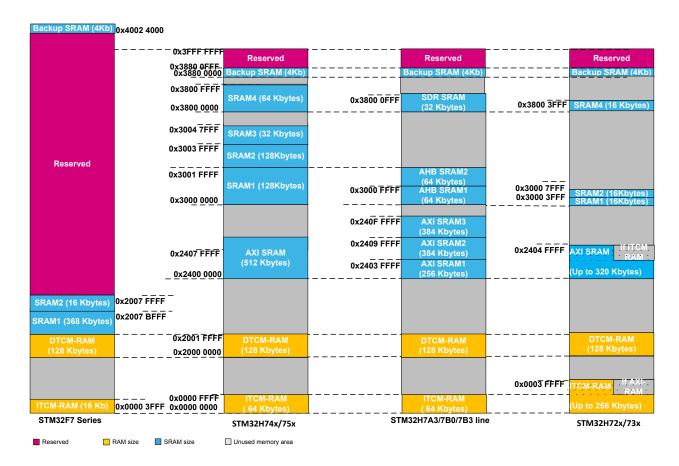

The following table illustrates the difference of RAM size between STM32F7 Series, STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices.

Table 10. Comparison of RAM size between STM32F7 Series, STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices

| Memory      | STM32F7 Series     | STM32H74x/75x | STM32H7A3/7Bx      | STM32H72x/73x      | Units |  |

|-------------|--------------------|---------------|--------------------|--------------------|-------|--|

| ITCM-RAM    | 16                 |               | 64                 | 64 <sup>(1)</sup>  |       |  |

| DTCM-RAM    | 128 <sup>(2)</sup> |               | 128                |                    |       |  |

| AXI-SRAM    | _                  | 512           | 1024               | 128 <sup>(1)</sup> |       |  |

| AXI-SIXAW   | -                  | 312           | (split in 3 SRAMs) | 12007              |       |  |

| SRAM1       | 368                | 128 64        |                    | 16                 | Kbyte |  |

| SRAM2       | 16                 | 128           | 64                 | 16                 | Royle |  |

| SRAM3       | NA                 | 32            | NA                 | NA                 |       |  |

| SRAM4       | NA                 | 64            | 32                 | 16                 |       |  |

| Backup SRAM |                    | 4             |                    |                    |       |  |

| Total       | 532                | 1060          | 1380               | 564                |       |  |

<sup>1.</sup> Can be increased with ITCM / AXI hared memory.

AN5293 - Rev 6 page 21/60

<sup>2. 64</sup>k bytes for STM32F74xxx/75xxx devices.

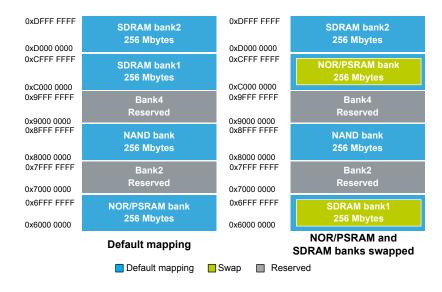

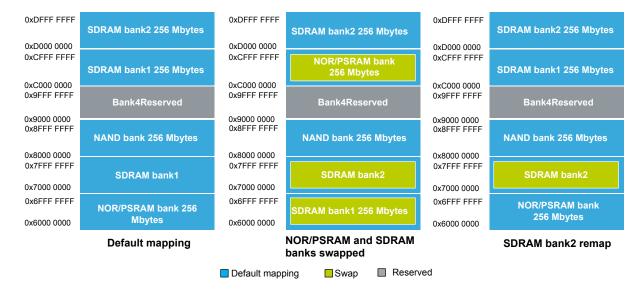

#### 6.2.2 Memory map and peripherals register boundary addresses

The table and figure below illustrate the memory addresses between STM32F7 Series, STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices.

Table 11. Memory organization and compatibility between STM32F7 Series, STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices

| Mem    | ory                               | STM32F7                                               | STM32H74/75                                               | STM32H7A/7B | STM32H72/73                                                                                                                  | Comments                                                   |

|--------|-----------------------------------|-------------------------------------------------------|-----------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| ITCM-  | RAM                               | 0x0000 0000 –<br>0x0000 3FFF                          | 0x0000 0000 – 0x0000 FFFF 0x0<br>0x0<br>0x0<br>0x0<br>0x0 |             | 0x0000 0000 –<br>0x0000 FFFF<br>0x0000 0000 –<br>0x0001 FFFF<br>0x0000 0000 –<br>0x0002 FFFF<br>0x0000 0000 –<br>0x0003 FFFF | STM32H72/73 size<br>depends on shared<br>memory assignment |

| DTCM   | ГСМ-RAM 0x2000 0000 – 0x2001 FFFF |                                                       |                                                           |             | Some STM32F7<br>devices feature only<br>64 Kbytes                                                                            |                                                            |

|        |                                   |                                                       | 0x0800 0000 - 0x080F FFFF                                 |             |                                                                                                                              | STM2H74/75xxI<br>STM32H7B3/H7A3xI<br>STM32H72/73xxG        |

|        | Bank1                             | Plash bank 1  0x0800 0000 - 0x080F FFFF  Flash bank 2 | 0x0800 0000 - 0x0807 FFFF                                 |             |                                                                                                                              | STM2H74/75xxG<br>STM32H7B3/<br>H7A3xG<br>STM32H72/73xxE    |

|        |                                   |                                                       | 0x08                                                      | Value line  |                                                                                                                              |                                                            |

| FLASH  |                                   | 0x0810 0000 -<br>0x081F FFFF                          | 0x0810 0000 -                                             | 0x081F FFFF | NA                                                                                                                           | STM2H74/75xxl<br>STM32H7B3/H7A3xl                          |

|        | Bank2                             |                                                       | 0x0810 0000 - 0x0817 FFFF                                 |             | NA                                                                                                                           | STM2H74/75xxG<br>STM32H7B3/<br>H7A3xG                      |

|        |                                   |                                                       |                                                           |             | Value line                                                                                                                   |                                                            |

|        | Flash -<br>ITCM                   | 0x0020 0000 –<br>0x003FF FFFF                         | NA                                                        |             |                                                                                                                              | NA                                                         |

| System | Bank1                             | 0x1FF0 0000 –<br>0x1FF0 EDBF                          | 0x1FF0 0000 –<br>0x1FF1 FFFF                              |             |                                                                                                                              | NA                                                         |

| memory | •                                 |                                                       | NA                                                        |             |                                                                                                                              |                                                            |

AN5293 - Rev 6 page 22/60

Figure 8. RAM memory organization of STM32F7 Series, STM32H743/753 and STM32H7A3/7Bx devices

#### Note: DTCM-RAM size:

- 128 Kbytes STM32F76xxx, STM32F77xxx and STM32H743/753 and STM32H7A3/7B0/7B3 devices

- 64 Kbytes for the STM32F75xxx and STM32F74xxx devices

AN5293 - Rev 6 page 23/60

#### 6.2.3 Peripheral register boundary addresses

The peripheral address mapping has been changed for most of peripherals in the STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices versus the STM32F7 Series devices.

For more details about registers boundary addresses differences refer to Memory map and register boundary addresses section of RM0368, RM0385, RM0410, RM0433 and RM0455 reference manuals.

Section 6.2.2 Memory map and peripherals register boundary addresses shows the detail of all the peripherals address mapping differences between STM32F7 Series, STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices.

Table 12. Examples of peripheral address mapping differences between STM32F7 Series,STM32H74x/75x, STM32H72x/73x and STM32H7A3/7Bx devices

| Peripheral             | STM32F<br>7 Series<br>devices | STM32H<br>74/75<br>devices | STM32H<br>72/73<br>devices | STM32H<br>7A/7B<br>devices | STM32F7<br>Series<br>devices    | STM32H74/75<br>devices       | STM32H72/73<br>devices    | STM32H7A/7<br>B devices         |

|------------------------|-------------------------------|----------------------------|----------------------------|----------------------------|---------------------------------|------------------------------|---------------------------|---------------------------------|

|                        |                               | В                          | us                         |                            |                                 | Base a                       | ddress                    |                                 |

| QUADSPI<br>control     | AF                            | IB3                        | N                          | Α                          | 0xA000 1000<br>- 0xA000<br>1FFF |                              | NA                        |                                 |

| GPIOA                  | AHB1                          | ДНІ                        | B4 (D3 or S                | PD)                        | 0x4002 0000 -<br>0x4002 03FF    | 0x580                        | 2 0000 - 0x5802           | : 03FF                          |

| RCC                    | AIIDI                         | AIII                       | D4 (D3 01 3                |                            | 0x40023800 -<br>0x40023BFF      | 0x58                         | 024400 - 0x5802           | 47FF                            |

| DFSDM2                 |                               | NA                         |                            | AHB4<br>(SRD)              |                                 | NA                           |                           | 0x5800 6C00<br>- 0x5800<br>73FF |

| DTS                    | N                             | IA                         | AHB4 (D                    | 3 or SRD)                  | N                               | IA                           | 0x5800 6800 ·             | 0x5800 6BFF                     |

| RTC2 and<br>Backup reg | AHB1                          | AHB4                       | 1 (D3)                     | NA                         | 0x4000 2800 -<br>0x4000 2BFF    | 0x5800 4000                  | - 0x5800 43FF             | NA                              |

| Tamp and<br>Backup reg | NA                            |                            |                            |                            | NA                              |                              |                           | 0x5800 4400 -<br>0x5800 47FF    |

| RTC3                   |                               |                            |                            | AHB4<br>(SRD)              |                                 |                              |                           |                                 |

| DAC2                   |                               |                            | NA                         |                            |                                 |                              | NA                        | 0x5800 3400 -<br>0x5800 37FF    |

| GFXMMU                 |                               |                            |                            | AHB3                       |                                 |                              |                           | 0x5200 C000<br>- 0x5200<br>EFFF |

| OTFDEC2                |                               |                            |                            |                            | -                               |                              | 0x5200 BC00 - 0x5200 BFFF |                                 |

| OTFDEC1                |                               |                            |                            |                            |                                 |                              | 0x5200 B800 - 0x5200 BBFF |                                 |

| OTCOSPI I/O            | N                             | IA                         |                            |                            | N                               | IA                           | 0v5200P400                | 0v5200D7EE                      |

| manager                |                               |                            |                            |                            |                                 |                              | 0x5200B400 - 0x5200B7FF   |                                 |

| Delay block            |                               |                            | ΔΗ                         | IB3                        |                                 |                              | 0x5200 B000 - 0x5200 B3FF |                                 |

| OCTOSPI2               |                               |                            | 741                        |                            |                                 |                              | 0x5200 B000 - 0x5200 B3FF |                                 |

| OCTOSPI2               |                               |                            |                            |                            |                                 |                              | 0x5200 A000 - 0x5200 AFFF |                                 |

| Delay block            |                               |                            |                            |                            |                                 | 0x5200 6000 - 0x             |                           | - 0x5200 63FF                   |

| OCTOSPI1               |                               |                            |                            |                            |                                 |                              | 5,0200 0000 - 0,0200 0011 |                                 |