## 概要

このリファレンスマニュアルは、アプリケーション開発者を対象としています。STM8TL5xxx マイクロコントローラファミリのメモリおよびペリフェラルの使用方法について詳細に説明しています。

注文情報、ピンの説明、機械的および電気的特性については、製品データシートを参照してください。

STM8 SWIM 通信プロトコルとデバッグモジュールについては、ユーザマニュアル (UM0470) を参照してください。

フラッシュメモリ関連の詳細については、STM8TL5xxx フラッシュメモリプログラミングマニュアル (PM0212) を参照してください。

STM8 コアについては、STM8 CPU プログラミングマニュアル (PM0044) を参照してください。

## 目次

|       |                                                   |    |

|-------|---------------------------------------------------|----|

| 1     | メモリおよびレジスタマップ                                     | 18 |

| 1.1   | レジスタの説明の略語                                        | 18 |

| 2     | 中央演算処理装置 (CPU)                                    | 19 |

| 2.1   | 概要                                                | 19 |

| 2.2   | CPU レジスタ                                          | 19 |

| 2.2.1 | CPU レジスタの説明                                       | 19 |

| 2.2.2 | STM8 CPU レジスタマップ                                  | 23 |

| 2.3   | グローバル設定レジスタ (CFG_GCR)                             | 24 |

| 2.3.1 | 起動レベル                                             | 24 |

| 2.3.2 | SWIM ディセーブル                                       | 24 |

| 2.3.3 | グローバル設定レジスタの説明 (CFG_GCR)                          | 24 |

| 2.3.4 | グローバル設定レジスタマップとリセット値                              | 24 |

| 3     | シングルワイヤインターフェースモジュール (SWIM) および<br>デバッグモジュール (DM) | 25 |

| 3.1   | 概要                                                | 25 |

| 3.2   | 主な特長                                              | 25 |

| 3.3   | SWIM モード                                          | 25 |

| 4     | フラッシュプログラムメモリとデータ EEPROM                          | 26 |

| 4.1   | 概要                                                | 26 |

| 4.2   | 用語                                                | 26 |

| 4.3   | メインフラッシュメモリの機能                                    | 26 |

| 4.4   | メモリ構成                                             | 27 |

| 4.4.1 | 独自仕様コード領域 (PCODE)                                 | 28 |

| 4.4.2 | ユーザブート領域 (UBC)                                    | 28 |

| 4.4.3 | データ EEPROM (DATA)                                 | 29 |

| 4.4.4 | メインプログラム領域                                        | 29 |

| 4.4.5 | オプションバイト                                          | 29 |

| 4.5   | メモリ保護                                             | 30 |

| 4.5.1 | 読み出し保護                                            | 30 |

| 4.5.2 | メモリアクセスセキュリティシステム (MASS)                          | 30 |

|          |                                            |           |

|----------|--------------------------------------------|-----------|

| 4.6      | メモリのプログラミング .....                          | 32        |

| 4.6.1    | バイトのプログラミング .....                          | 32        |

| 4.6.2    | ワードプログラミング .....                           | 32        |

| 4.6.3    | ブロックプログラミング .....                          | 33        |

| 4.7      | ICP と IAP .....                            | 34        |

| 4.8      | フラッシュレジスタ .....                            | 37        |

| 4.8.1    | フラッシュ制御レジスタ 1 (FLASH_CR1) .....            | 37        |

| 4.8.2    | フラッシュ制御レジスタ 2 (FLASH_CR2) .....            | 38        |

| 4.8.3    | フラッシュプログラムメモリ保護解除キーレジスタ (FLASH_PUKR) ..... | 38        |

| 4.8.4    | データ EEPROM 保護解除キーレジスタ (FLASH_DUKR) .....   | 39        |

| 4.8.5    | フラッシュステータスレジスタ (FLASH_IAPSR) .....         | 39        |

| 4.8.6    | フラッシュレジスタマップとリセット値 .....                   | 40        |

| <b>5</b> | <b>割り込みコントローラ (ITC) .....</b>              | <b>41</b> |

| 5.1      | ITC の概要 .....                              | 41        |

| 5.2      | 割り込みマスクと処理の流れ .....                        | 41        |

| 5.2.1    | ペンドィング割り込みの処理 .....                        | 42        |

| 5.2.2    | 割り込みソース .....                              | 43        |

| 5.3      | 割り込みと低電力モード .....                          | 44        |

| 5.4      | 起動レベル／低電力モードの制御 .....                      | 45        |

| 5.5      | 同時およびネスト割り込み管理 .....                       | 45        |

| 5.5.1    | 同時割り込み管理モード .....                          | 45        |

| 5.5.2    | ネスト割り込み管理モード .....                         | 46        |

| 5.6      | 外部割り込み .....                               | 47        |

| 5.7      | 割り込み命令 .....                               | 48        |

| 5.8      | 割り込みの配置 .....                              | 48        |

| 5.9      | ITC および EXTI レジスタ .....                    | 49        |

| 5.9.1    | コンディションコードレジスタ割り込みビット (CCR) .....          | 49        |

| 5.9.2    | ソフトウェア優先順位レジスタ x (ITC_SPRx) .....          | 50        |

| 5.9.3    | 外部割り込み制御レジスタ 1 (EXTI_CR1) .....            | 51        |

| 5.9.4    | 外部割り込み制御レジスタ 2 (EXTI_CR2) .....            | 52        |

| 5.9.5    | 外部割り込み制御レジスタ 3 (EXTI_CR3) .....            | 53        |

| 5.9.6    | 外部割り込みステータスレジスタ 1 (EXTI_SR1) .....         | 53        |

| 5.9.7    | 外部割り込みステータスレジスタ 2 (EXTI_SR2) .....         | 54        |

| 5.9.8    | 外部割り込みポート選択レジスタ (EXTI_CONF) .....          | 54        |

| 5.9.9    | ITC および EXTI レジスタマップとリセット値 .....           | 55        |

|       |                                            |    |

|-------|--------------------------------------------|----|

| 6     | 電源 .....                                   | 56 |

| 7     | リセット (RST) と電圧検出 .....                     | 57 |

| 7.1   | 「リセット状態」と「リセット中」の定義 .....                  | 57 |

| 7.2   | 外部リセット (NRST ピン) .....                     | 57 |

| 7.2.1 | 非同期外部リセットの説明 .....                         | 57 |

| 7.2.2 | NRST/PA5 ピンの汎用出力としての設定 .....               | 58 |

| 7.3   | 内部リセット .....                               | 58 |

| 7.3.1 | パワーオンリセット (POR) .....                      | 58 |

| 7.3.2 | 独立型ウォッチドッグリセット .....                       | 58 |

| 7.3.3 | SWIM リセット .....                            | 58 |

| 7.3.4 | 不正オペコードリセット .....                          | 58 |

| 7.4   | RST レジスタ .....                             | 59 |

| 7.4.1 | リセットピン設定レジスタ (RST_CR) .....                | 59 |

| 7.4.2 | リセットステータスレジスタ (RST_SR) .....               | 59 |

| 7.5   | RST レジスタマップとリセット値 .....                    | 60 |

| 8     | クロック制御 (CLK) .....                         | 61 |

| 8.1   | マスタクロック (HSI クロック) .....                   | 62 |

| 8.1.1 | ペリフェラルクロックゲーティング (PCG) .....               | 62 |

| 8.2   | LSI クロック .....                             | 63 |

| 8.3   | 設定可能クロック出力機能 (CCO) .....                   | 63 |

| 8.4   | CLK レジスタ .....                             | 63 |

| 8.4.1 | クロック分周器レジスタ (CLK_CKDIVR) .....             | 63 |

| 8.4.2 | ペリフェラルクロックゲーティングレジスタ 1 (CLK_PCKENR1) ..... | 64 |

| 8.4.3 | ペリフェラルクロックゲーティングレジスタ 2 (CLK_PCKENR2) ..... | 64 |

| 8.4.4 | 設定可能クロック出力レジスタ (CLK_CCOR) .....            | 65 |

| 8.4.5 | CLK レジスタマップとリセット値 .....                    | 65 |

| 9     | 電源管理 .....                                 | 66 |

| 9.1   | 一般的な考慮事項 .....                             | 66 |

| 9.2   | 低消費電力のためのクロック管理 .....                      | 67 |

| 9.2.1 | システムクロックの低速化 .....                         | 67 |

| 9.2.2 | ペリフェラルクロックゲーティング .....                     | 67 |

|           |                                |           |

|-----------|--------------------------------|-----------|

| 9.3       | ペリフェラルのスイッチオフ .....            | 67        |

| 9.4       | 低電力モード .....                   | 68        |

| 9.4.1     | WAIT モード .....                 | 69        |

| 9.4.2     | HALT モード .....                 | 70        |

| 9.4.3     | アクティブ HALT モード .....           | 70        |

| 9.5       | WFE レジスタ .....                 | 71        |

| 9.5.1     | WFE 制御レジスタ 1 (WFE_CR1) .....   | 71        |

| 9.5.2     | WFE 制御レジスタ 2 (WFE_CR2) .....   | 72        |

| 9.6       | WFE レジスタマップとリセット値 .....        | 73        |

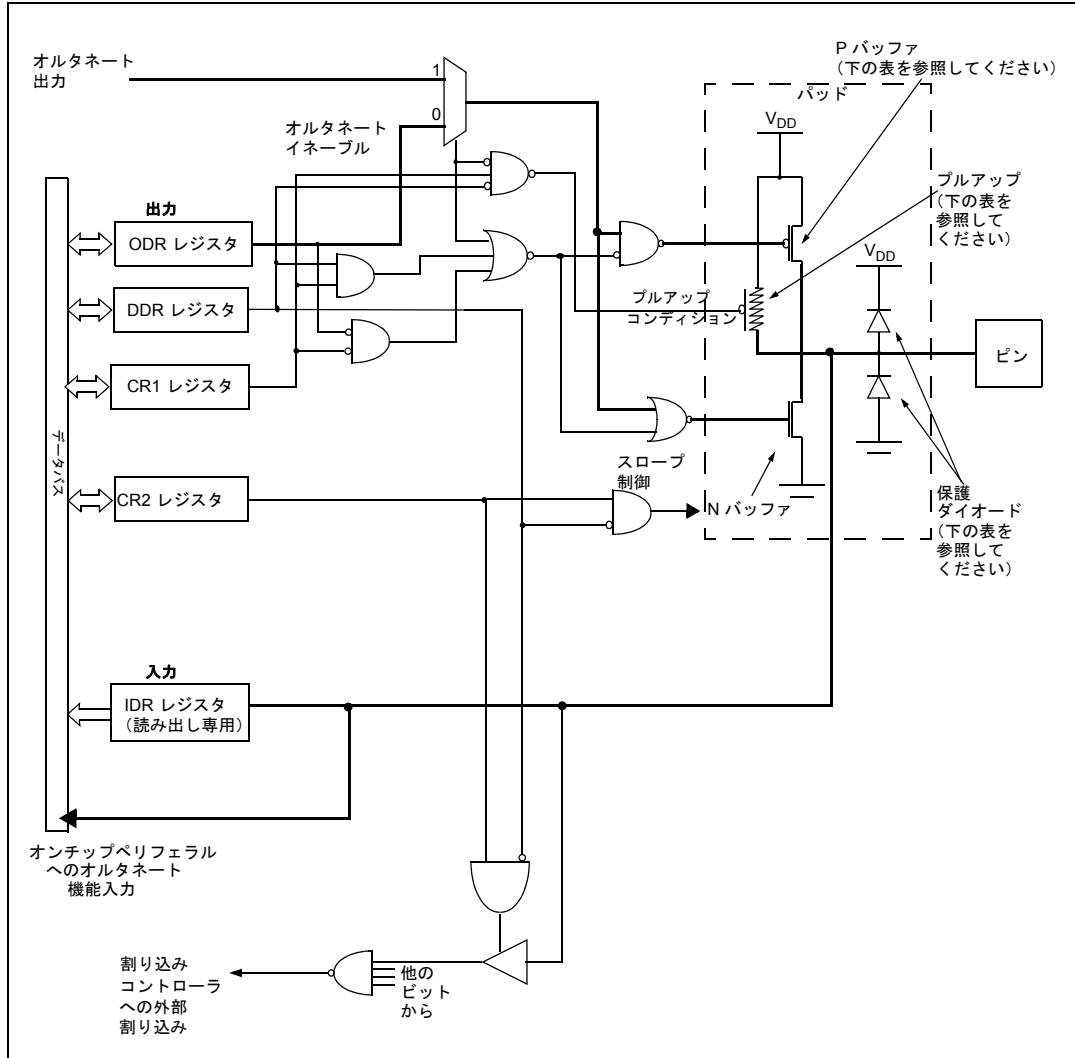

| <b>10</b> | <b>汎用入出力ポート (GPIO) .....</b>   | <b>74</b> |

| 10.1      | 概要 .....                       | 74        |

| 10.2      | GPIO の主な機能 .....               | 74        |

| 10.3      | ポートの設定と使い方 .....               | 75        |

| 10.3.1    | 入力モード .....                    | 76        |

| 10.3.2    | 出力モード .....                    | 76        |

| 10.4      | リセット設定 .....                   | 77        |

| 10.5      | 未使用の入出力ピン .....                | 77        |

| 10.6      | 低電力モード .....                   | 77        |

| 10.7      | 入力モードの詳細 .....                 | 77        |

| 10.7.1    | オルタネート機能入力 .....               | 77        |

| 10.7.2    | 割り込み機能 .....                   | 78        |

| 10.8      | 出力モードの詳細 .....                 | 78        |

| 10.8.1    | オルタネート機能出力 .....               | 78        |

| 10.8.2    | スロープ制御 .....                   | 78        |

| 10.9      | GPIO レジスタ .....                | 79        |

| 10.9.1    | ポート x 出力データレジスタ (Px_ODR) ..... | 79        |

| 10.9.2    | ポート x ピン入力カレジスタ (Px_IDR) ..... | 79        |

| 10.9.3    | ポート x データ方向レジスタ (Px_DDR) ..... | 80        |

| 10.9.4    | ポート x 制御レジスタ 1 (Px_CR1) .....  | 80        |

| 10.9.5    | ポート x 制御レジスタ 2 (Px_CR2) .....  | 81        |

| 10.9.6    | GPIO レジスタマップとリセット値 .....       | 81        |

|           |                                   |           |

|-----------|-----------------------------------|-----------|

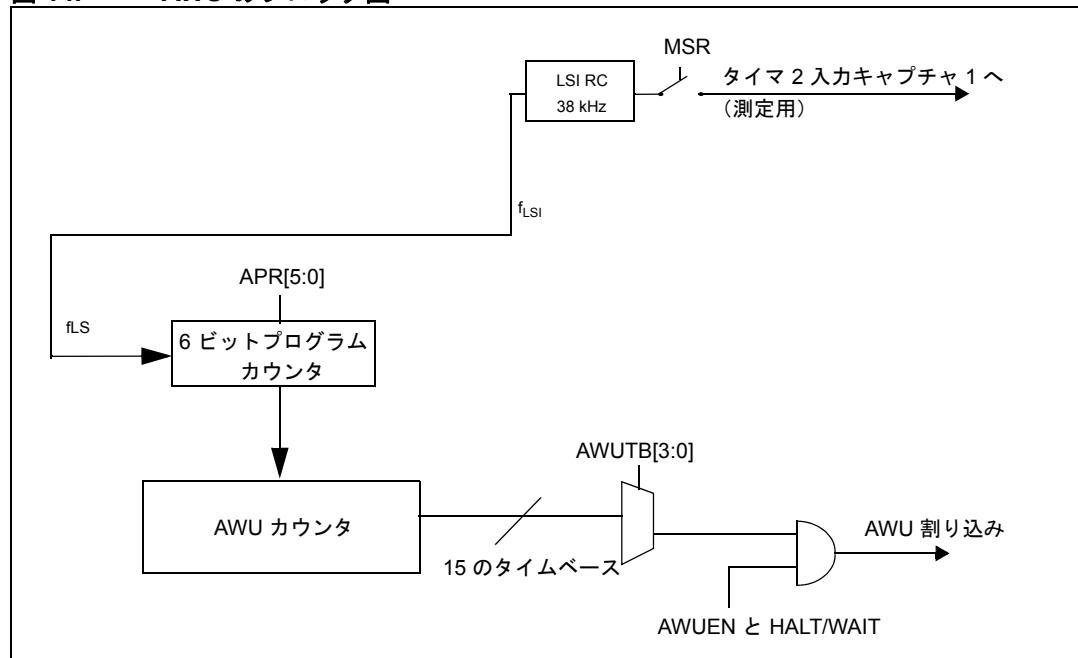

| <b>11</b> | <b>自動ウェイクアップ (AWU) .....</b>      | <b>82</b> |

| 11.1      | 概要 .....                          | 82        |

| 11.2      | LSI クロックの測定 .....                 | 82        |

| 11.3      | AWU 機能の説明 .....                   | 83        |

| 11.3.1    | AWU 動作 .....                      | 83        |

| 11.3.2    | タイムベースの選択 .....                   | 84        |

| 11.3.3    | LSI クロック周波数の測定 .....              | 85        |

| 11.4      | AWU レジスタ .....                    | 86        |

| 11.4.1    | 制御／ステータスレジスタ (AWU_CSR) .....      | 86        |

| 11.4.2    | 非同期プリスケーラレジスタ (AWU_APR) .....     | 86        |

| 11.4.3    | タイムベース選択レジスタ (AWU_TBR) .....      | 87        |

| 11.4.4    | AWU レジスタマップとリセット値 .....           | 87        |

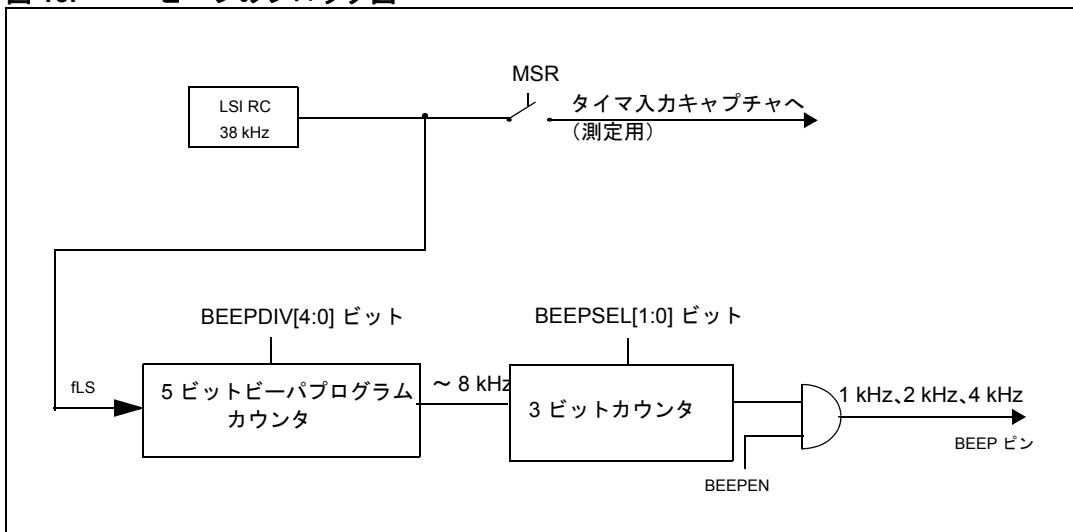

| <b>12</b> | <b>ビーパ (BEEP) .....</b>           | <b>88</b> |

| 12.1      | 概要 .....                          | 88        |

| 12.2      | ビーパ機能の説明 .....                    | 88        |

| 12.2.1    | ビーパ動作 .....                       | 88        |

| 12.2.2    | ビーパ較正 .....                       | 89        |

| 12.3      | ビーパレジスタ .....                     | 89        |

| 12.3.1    | ビーパ制御／ステータスレジスタ (BEEP_CSR) .....  | 89        |

| 12.3.2    | ビーパレジスタマップとリセット値 .....            | 89        |

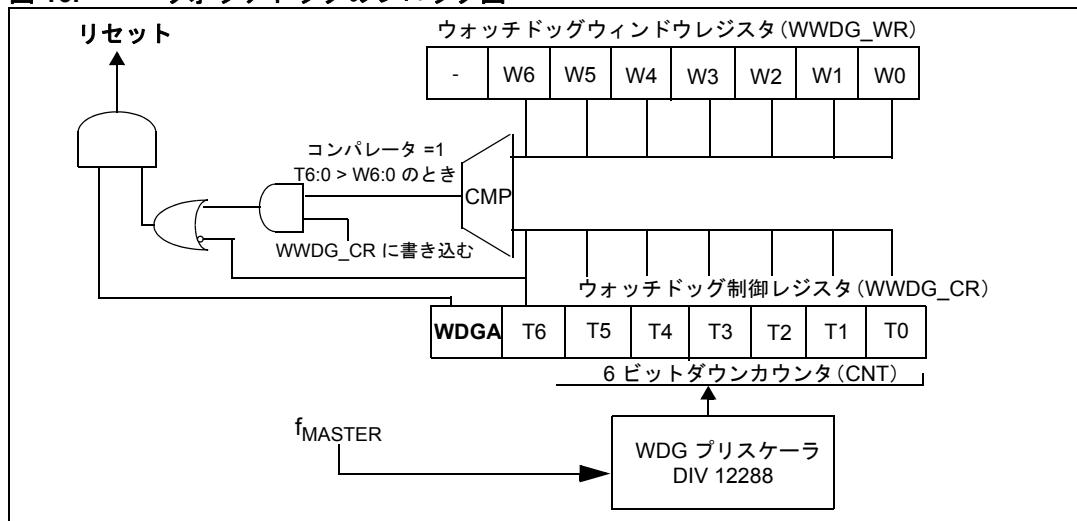

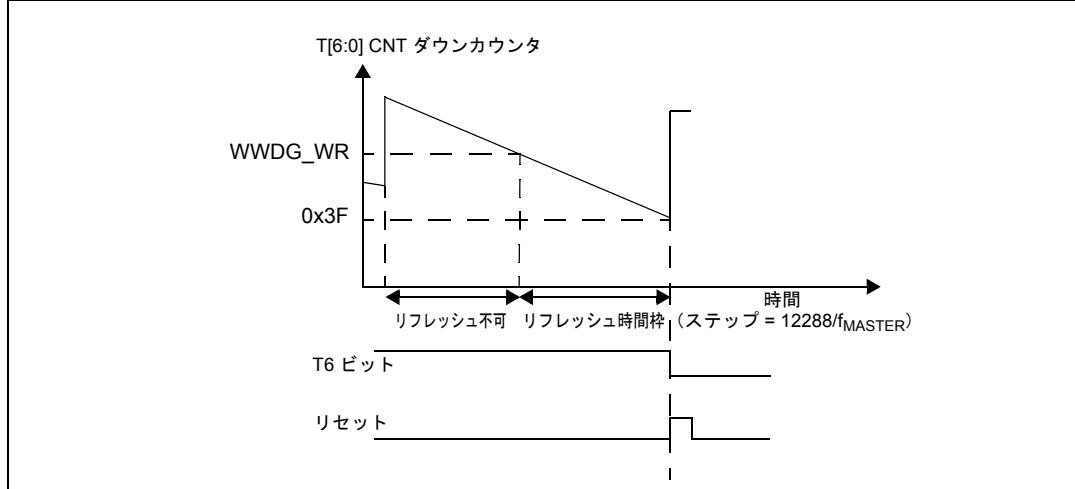

| <b>13</b> | <b>ウィンドウ型ウォッチドッグ (WWDG) .....</b> | <b>90</b> |

| 13.1      | 概要 .....                          | 90        |

| 13.2      | WWDG の主な機能 .....                  | 90        |

| 13.3      | WWDG 機能の説明 .....                  | 90        |

| 13.4      | ウォッチドッグタイムアウトをプログラムするには .....     | 91        |

| 13.5      | WWDG 低電力モード .....                 | 92        |

| 13.6      | ハードウェアウォッチドッグオプション .....          | 92        |

| 13.7      | WWDG 割り込み .....                   | 93        |

| 13.8      | WWDG レジスタ .....                   | 93        |

| 13.8.1    | Control register (WWDG_CR) .....  | 93        |

| 13.8.2    | Window register (WWDG_WR) .....   | 93        |

|           |                                    |            |

|-----------|------------------------------------|------------|

| 13.9      | ウィンドウ型ウォッチドッグレジスタマップとリセット値         | 93         |

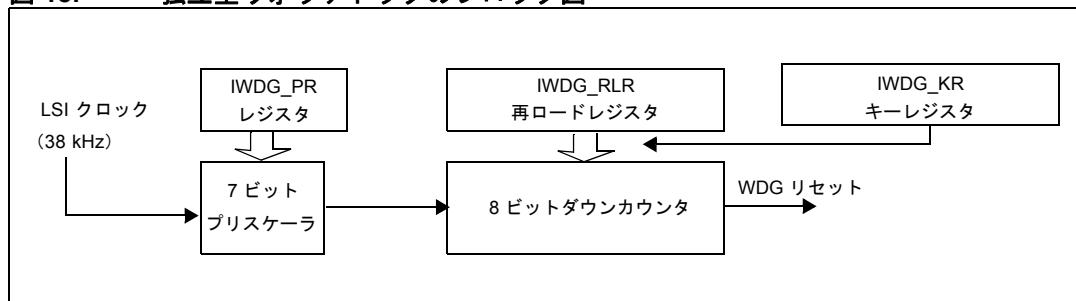

| <b>14</b> | <b>独立型ウォッチドッグ (IWDG)</b>           | <b>94</b>  |

| 14.1      | 概要                                 | 94         |

| 14.2      | IWDG 機能の説明                         | 94         |

| 14.3      | IWDG レジスタ                          | 96         |

| 14.3.1    | キーレジスタ (IWDG_KR)                   | 96         |

| 14.3.2    | プリスケーラレジスタ (IWDG_PR)               | 96         |

| 14.3.3    | 再ロードレジスタ (IWDG_RLR)                | 97         |

| 14.3.4    | IWDG register map and reset values | 97         |

| <b>15</b> | <b>タイマの概要</b>                      | <b>98</b>  |

| 15.1      | タイマ機能の比較                           | 98         |

| 15.2      | タイマ信号名の用語                          | 99         |

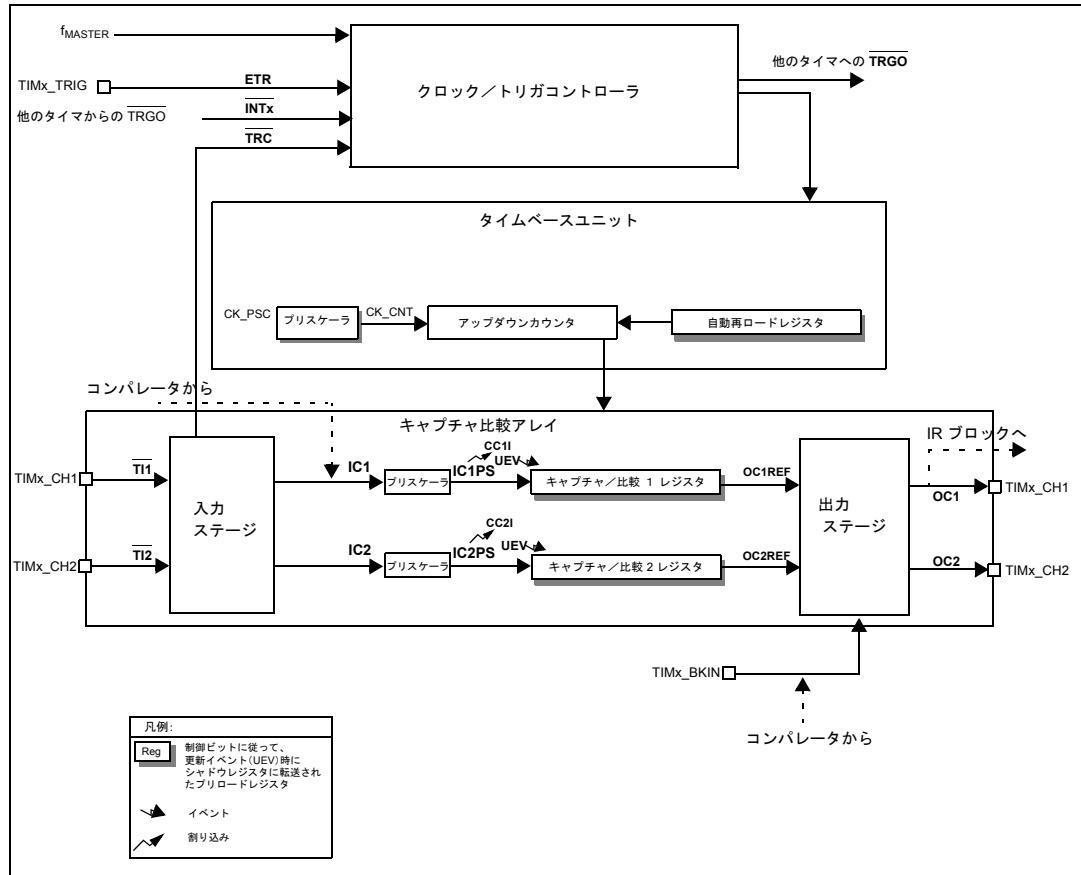

| <b>16</b> | <b>16 ビット汎用タイマ (TIM2/TIM3)</b>     | <b>100</b> |

| 16.1      | 概要                                 | 100        |

| 16.2      | TIMx の主な機能                         | 100        |

| 16.3      | TIMx タイムベースユニット                    | 102        |

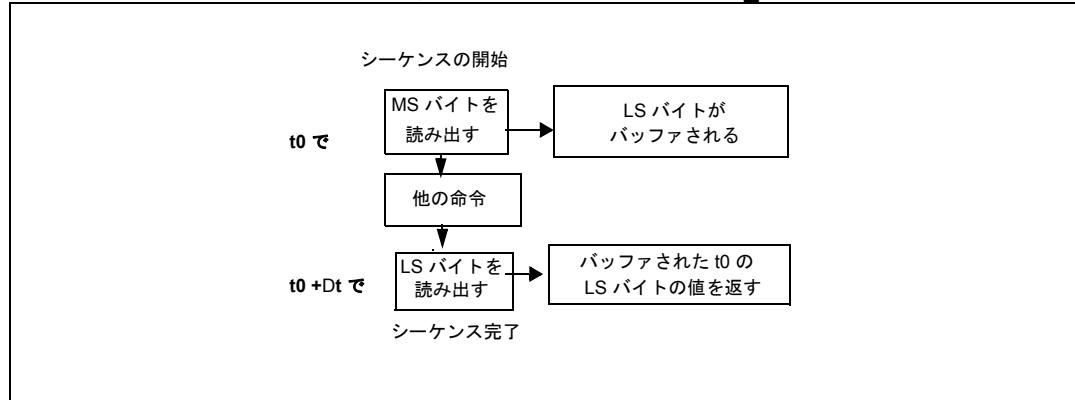

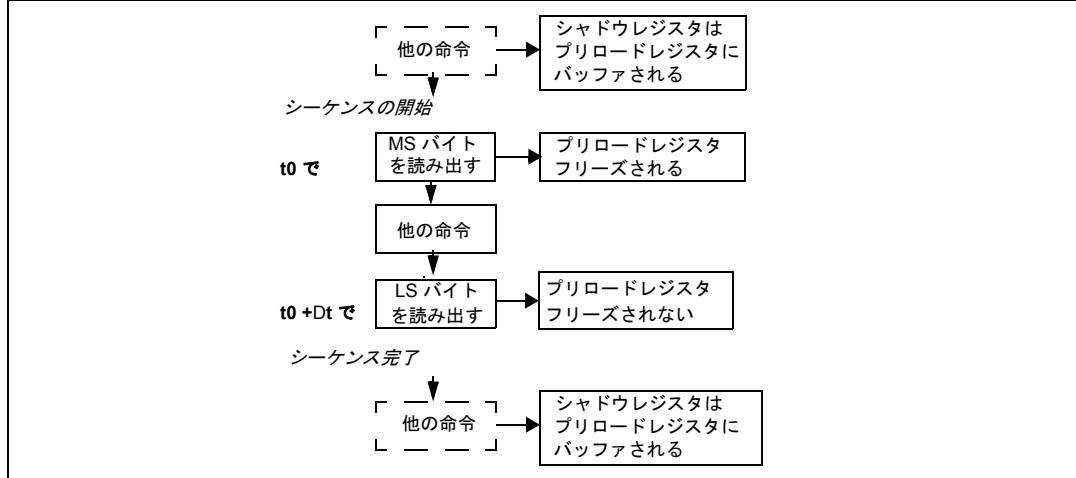

| 16.3.1    | 16 ビットカウンタの読み出しと書き込み               | 103        |

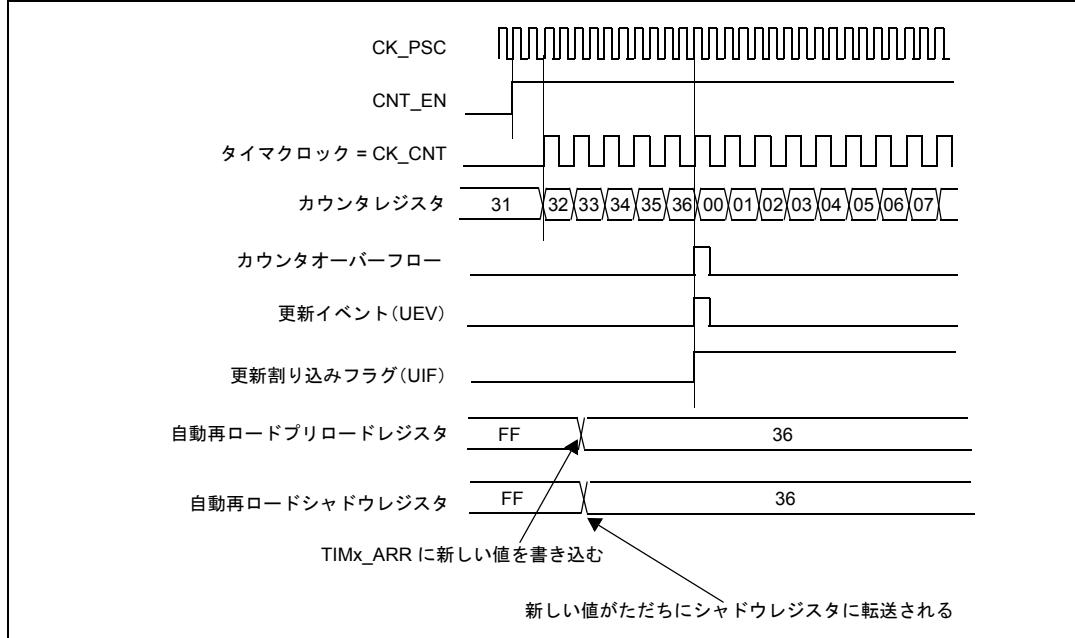

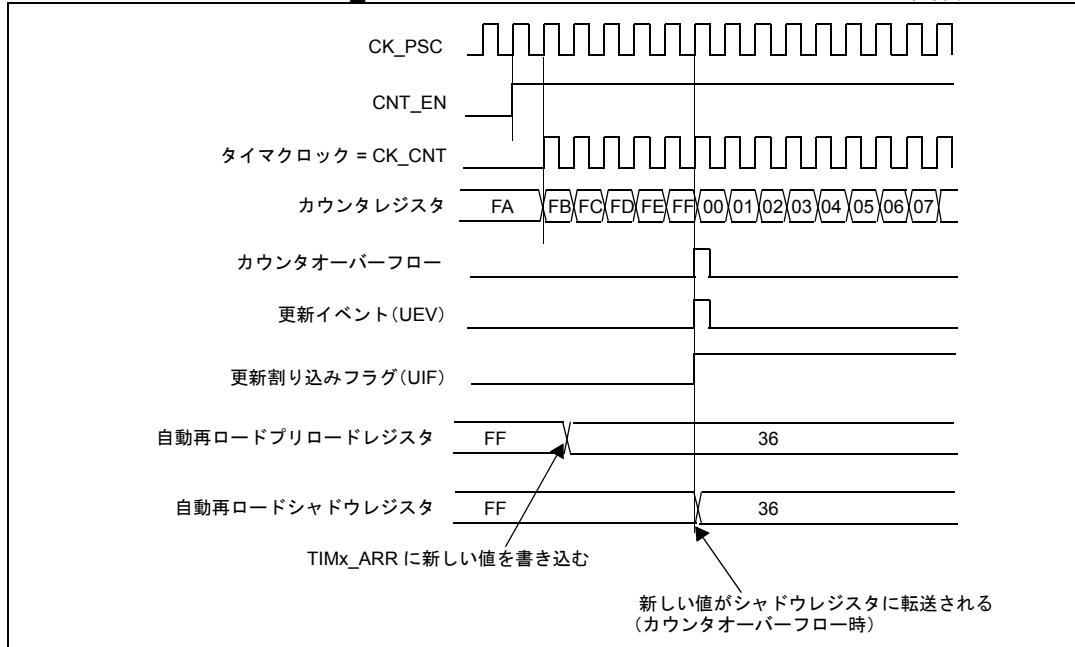

| 16.3.2    | 16 ビット TIMx_ARR レジスタの書き込みシーケンス     | 103        |

| 16.3.3    | プリスケーラ                             | 103        |

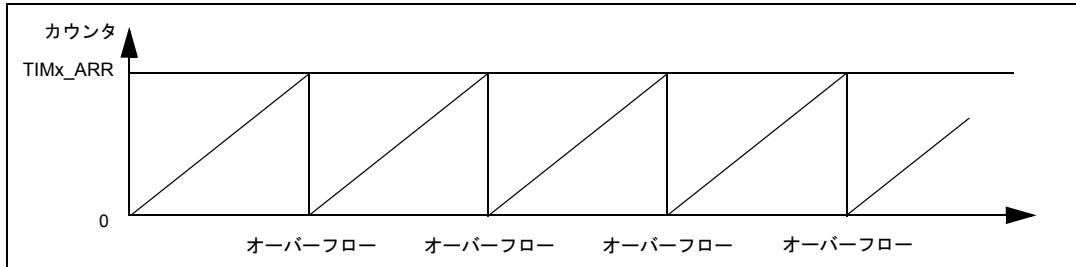

| 16.3.4    | アップカウントモード                         | 104        |

| 16.3.5    | ダウンカウントモード                         | 106        |

| 16.3.6    | センターラインモード (アップ/ダウンカウント)           | 108        |

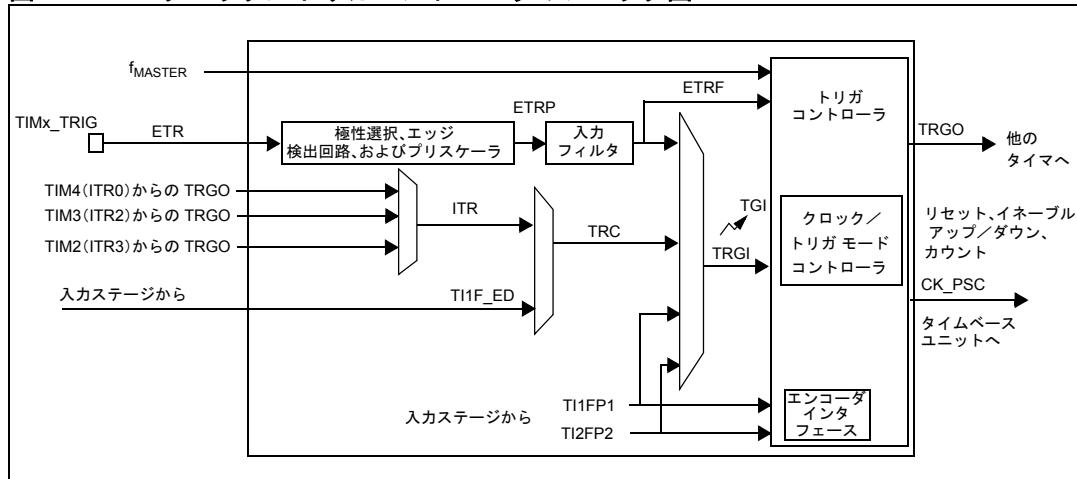

| 16.4      | TIMx クロック/トリガコントローラ                | 110        |

| 16.4.1    | プリスケーラクロック (CK_PSC)                | 110        |

| 16.4.2    | 内部クロックソース                          | 110        |

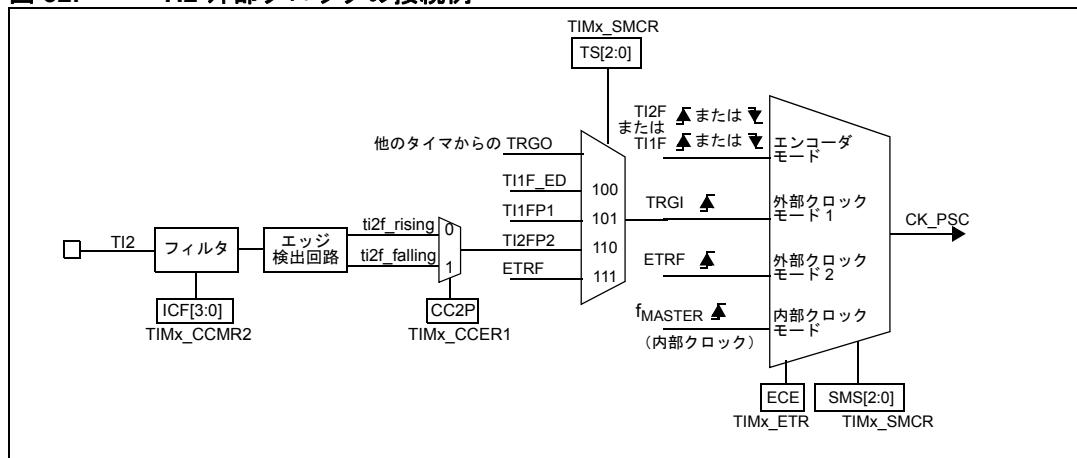

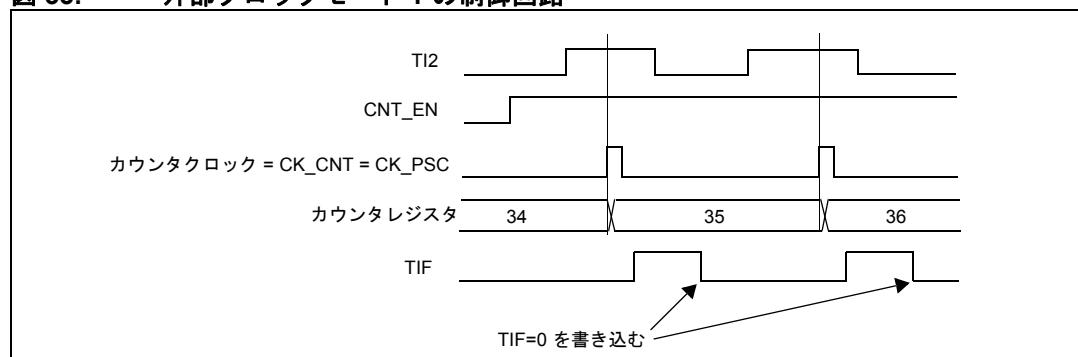

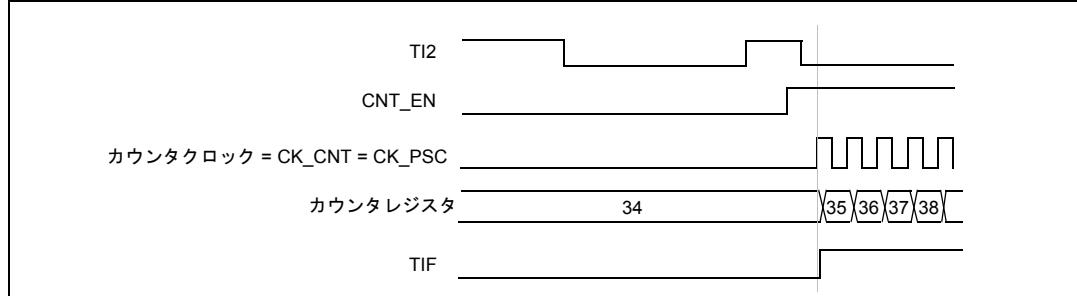

| 16.4.3    | 外部クロックソースモード 1                     | 111        |

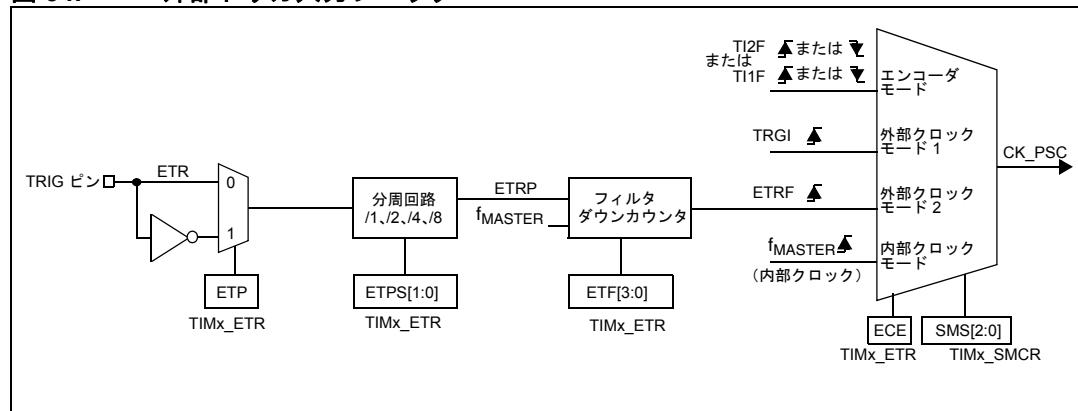

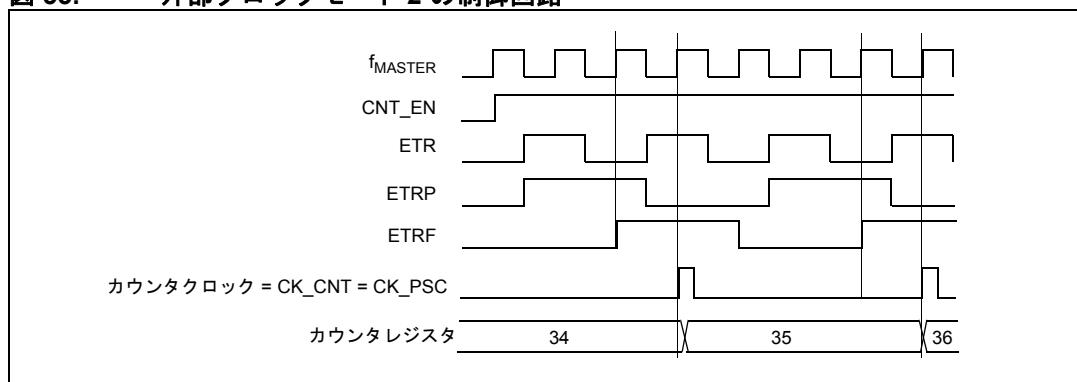

| 16.4.4    | 外部クロックソースモード 2                     | 112        |

| 16.4.5    | トリガの同期                             | 113        |

| 16.4.6    | 他のタイマからの同期                         | 117        |

| 16.5      | TIMx キャプチャ/比較チャネル                  | 123        |

| 16.5.1    | 16 ビット TIMx_CCRi レジスタの書き込みシーケンス    | 124        |

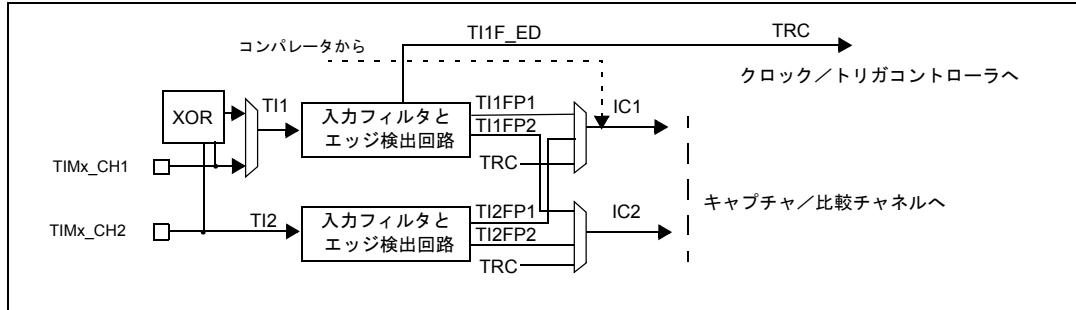

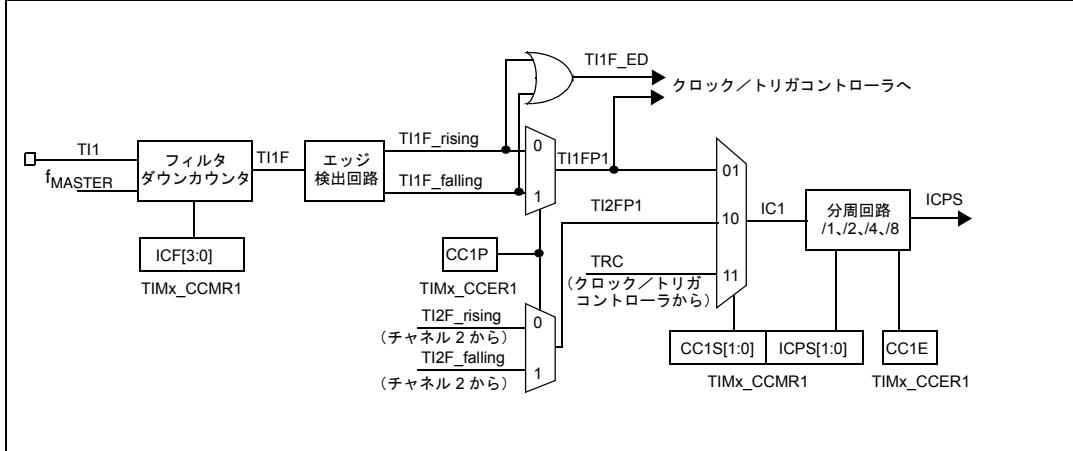

| 16.5.2    | 入力ステージ                             | 124        |

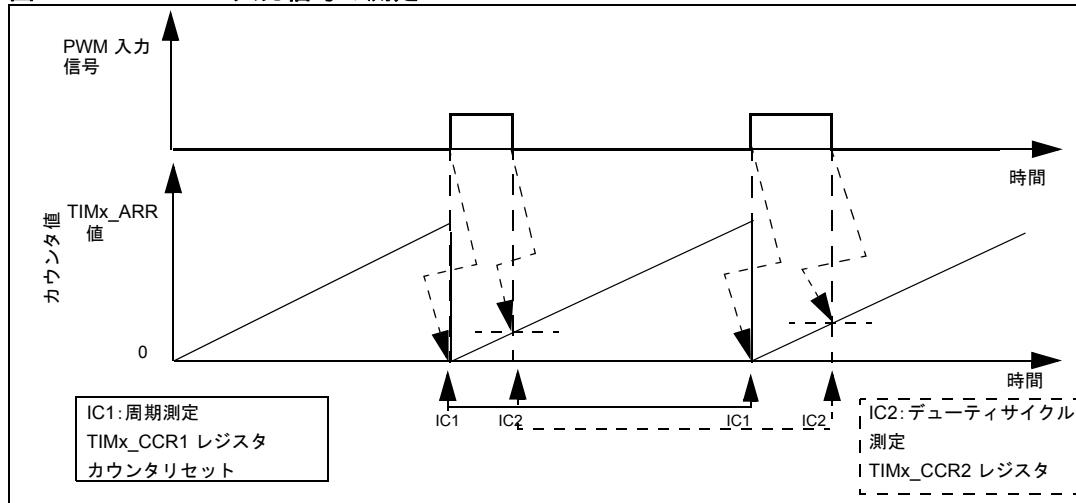

| 16.5.3    | 入力キャプチャモード                         | 125        |

|         |                                  |     |

|---------|----------------------------------|-----|

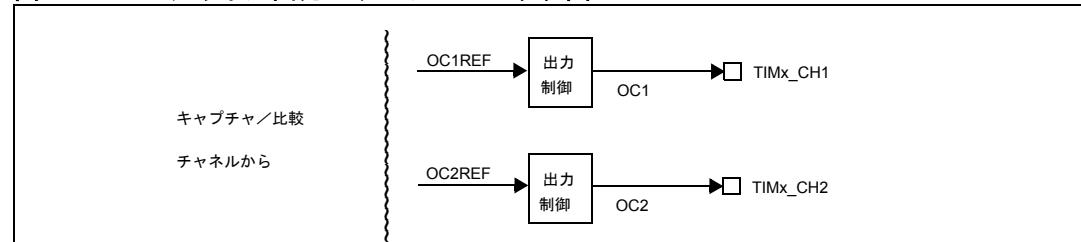

| 16.5.4  | 出力ステージ                           | 127 |

| 16.5.5  | 強制出力モード                          | 128 |

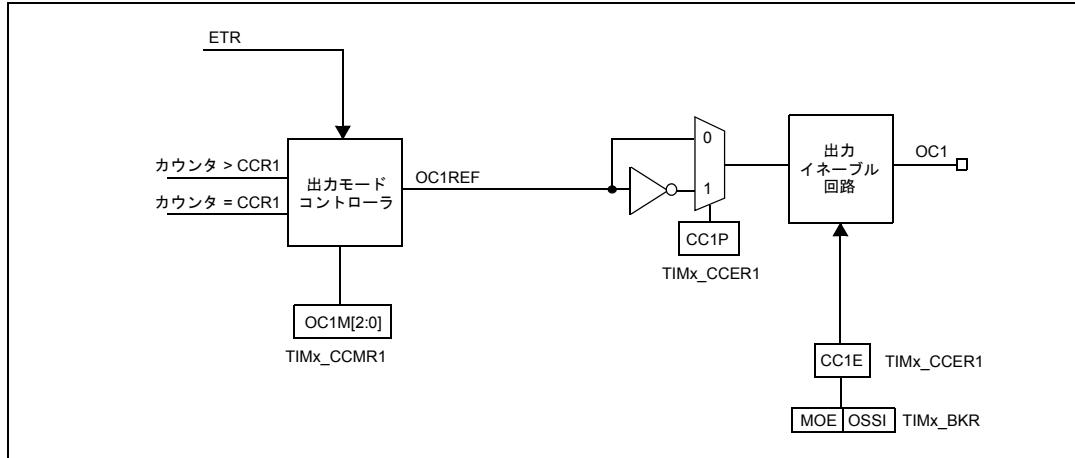

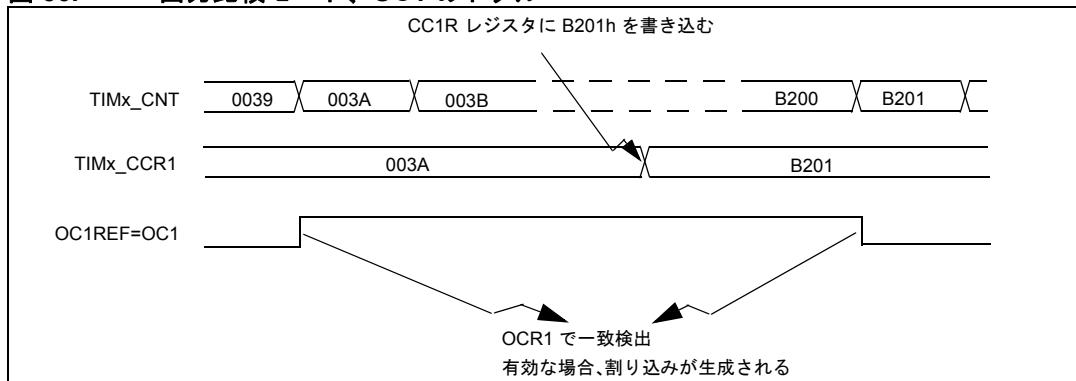

| 16.5.6  | 出力比較モード                          | 128 |

| 16.5.7  | PWM モード                          | 129 |

| 16.5.8  | ブレーク機能の使用                        | 133 |

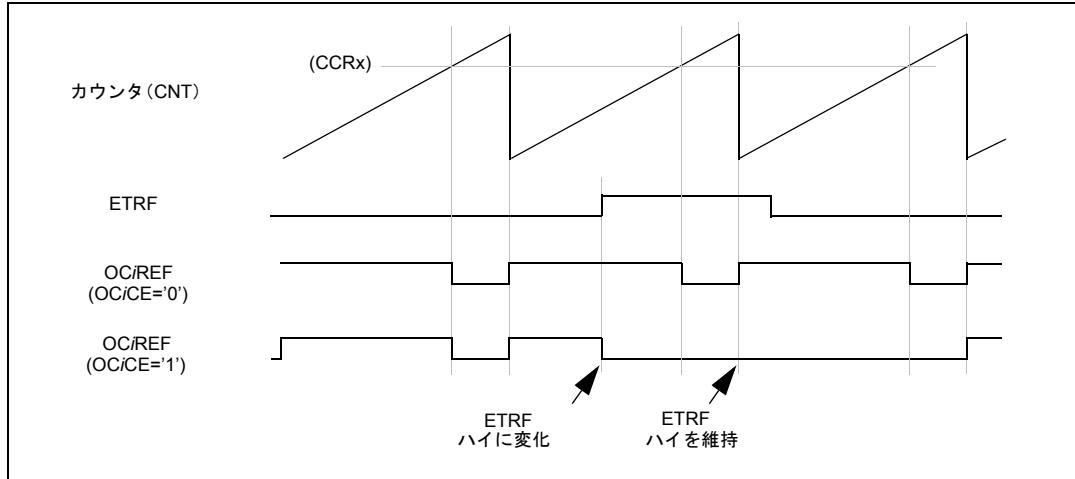

| 16.5.9  | 外部イベント時の OCiREF 信号のクリア           | 134 |

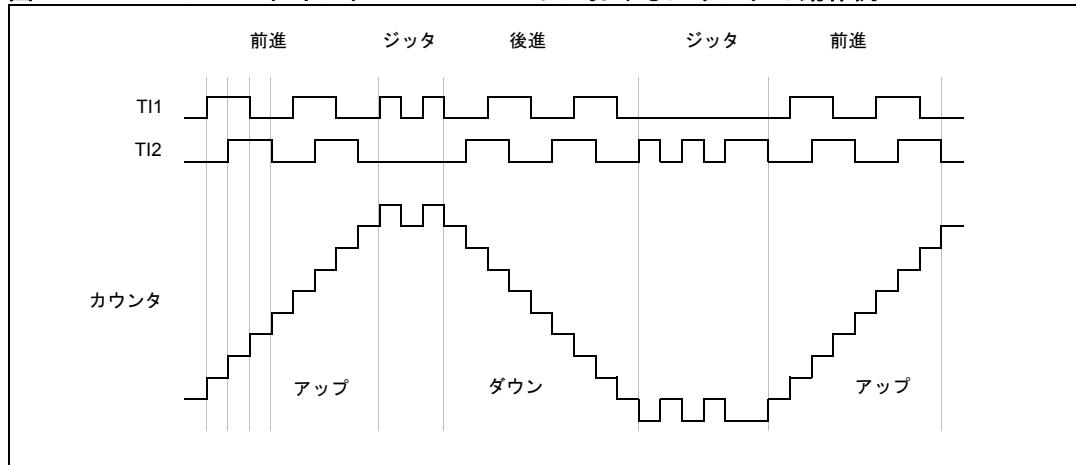

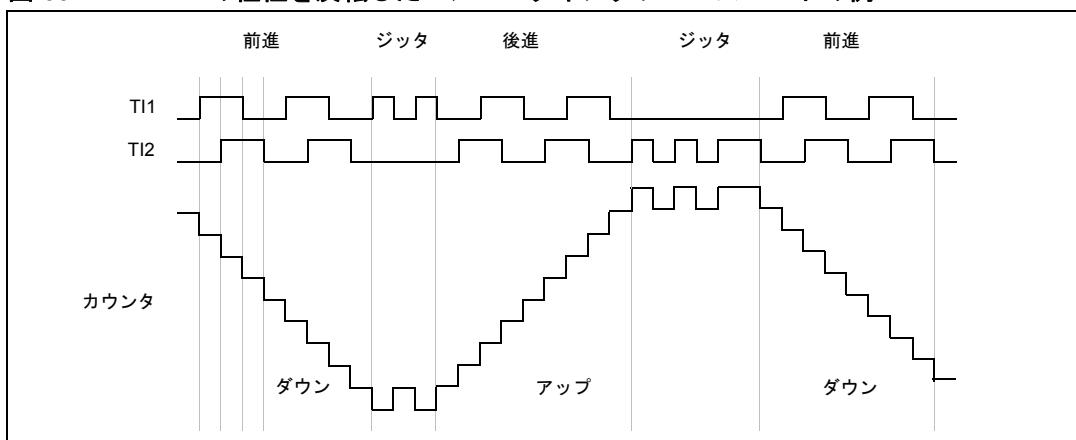

| 16.5.10 | エンコーダインターフェースモード                 | 135 |

| 16.6    | TIMx 割り込み                        | 138 |

| 16.6.1  | TIMx イベント待ち機能                    | 138 |

| 16.7    | TIMx レジスタ                        | 139 |

| 16.7.1  | 制御レジスタ 1 (TIMx_CR1)              | 139 |

| 16.7.2  | 制御レジスタ 2 (TIMx_CR2)              | 140 |

| 16.7.3  | スレーブモード制御レジスタ (TIMx_SMCR)        | 141 |

| 16.7.4  | 外部トリガレジスタ (TIMx_ETR)             | 142 |

| 16.7.5  | 割り込みイネーブルレジスタ (TIMx_IER)         | 143 |

| 16.7.6  | ステータスレジスタ 1 (TIMx_SR1)           | 143 |

| 16.7.7  | ステータスレジスタ 2 (TIMx_SR2)           | 144 |

| 16.7.8  | イベント生成レジスタ (TIMx_EGR)            | 145 |

| 16.7.9  | キャプチャ／比較モードレジスタ 1 (TIMx_CCMR1)   | 146 |

| 16.7.10 | キャプチャ／比較モードレジスタ 2 (TIMx_CCMR2)   | 148 |

| 16.7.11 | キャプチャ／比較イネーブルレジスタ 1 (TIMx_CCER1) | 149 |

| 16.7.12 | カウンタハイ (TIMx_CNTRH)              | 150 |

| 16.7.13 | カウンタロー (TIMx_CNTRL)              | 150 |

| 16.7.14 | プリスケーラレジスタ (TIMx_PSCR)           | 150 |

| 16.7.15 | 自動再ロードレジスタハイ (TIMx_ARRH)         | 151 |

| 16.7.16 | 自動再ロードレジスタロー (TIMx_ARRL)         | 151 |

| 16.7.17 | キャプチャ／比較レジスタ 1 ハイ (TIMx_CCR1H)   | 151 |

| 16.7.18 | キャプチャ／比較レジスタ 1 ロー (TIMx_CCR1L)   | 152 |

| 16.7.19 | キャプチャ／比較レジスタ 2 ハイ (TIMx_CCR2H)   | 152 |

| 16.7.20 | キャプチャ／比較レジスタ 2 ロー (TIMx_CCR2L)   | 152 |

| 16.7.21 | ブレークレジスタ (TIMx_BKR)              | 153 |

| 16.7.22 | 出力アイドル状態レジスタ (TIMx_OISR)         | 155 |

| 16.7.23 | TIMx レジスタマップとリセット値               | 155 |

|           |                                                                    |            |

|-----------|--------------------------------------------------------------------|------------|

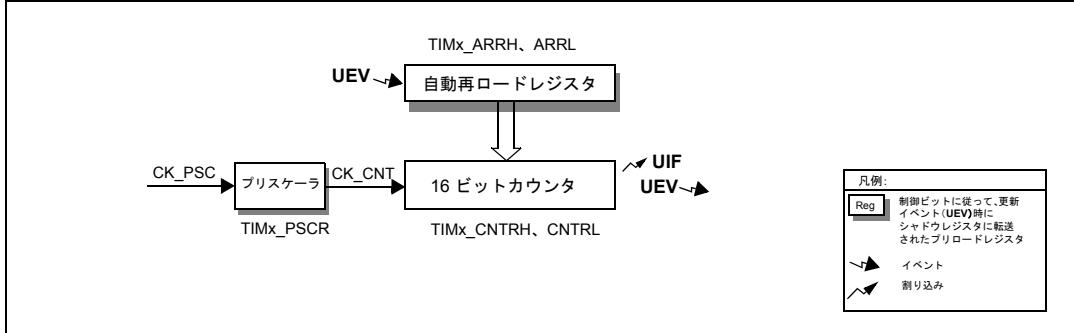

| <b>17</b> | <b>8 ビット基本タイマ (TIM4) . . . . .</b>                                 | <b>157</b> |

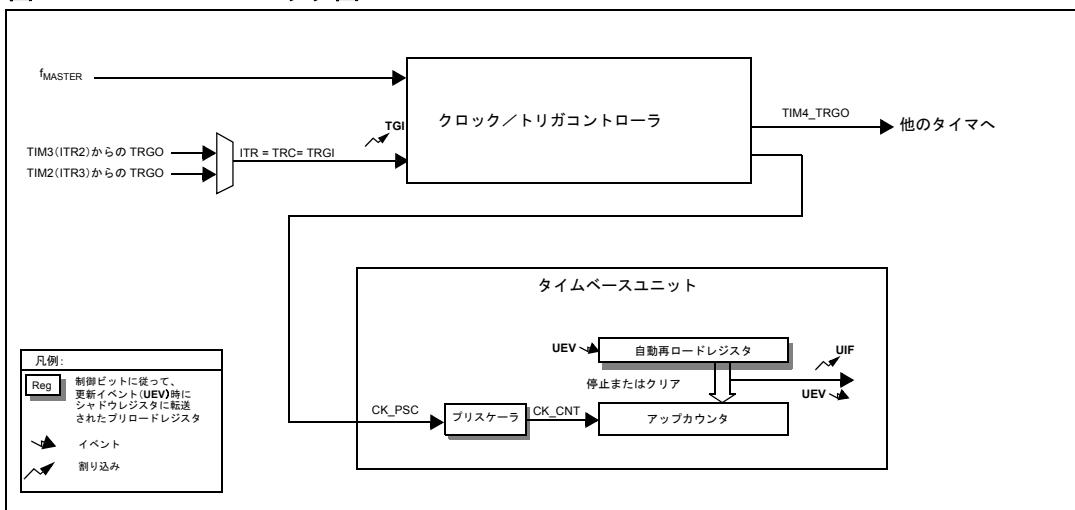

| 17.1      | 概要 . . . . .                                                       | 157        |

| 17.2      | TIM4 の主な機能 . . . . .                                               | 157        |

| 17.3      | TIM4 割り込み . . . . .                                                | 157        |

| 17.4      | TIM4 クロックの選択 . . . . .                                             | 158        |

| 17.5      | TIM4 レジスタ . . . . .                                                | 159        |

| 17.5.1    | 制御レジスタ 1 (TIM4_CR1) . . . . .                                      | 159        |

| 17.5.2    | 制御レジスタ 2 (TIM4_CR2) . . . . .                                      | 160        |

| 17.5.3    | スレーブモード制御レジスタ (TIM4_SMCR) . . . . .                                | 161        |

| 17.5.4    | 割り込みイネーブルレジスタ (TIM4_IER) . . . . .                                 | 162        |

| 17.5.5    | ステータスレジスタ 1 (TIM4_SR1) . . . . .                                   | 162        |

| 17.5.6    | イベント生成レジスタ (TIM4_EGR) . . . . .                                    | 163        |

| 17.5.7    | カウンタ (TIM4_CNTR) . . . . .                                         | 163        |

| 17.5.8    | プリスケーラレジスタ (TIM4_PSCR) . . . . .                                   | 163        |

| 17.5.9    | 自動再ロードレジスタ (TIM4_ARR) . . . . .                                    | 164        |

| 17.5.10   | TIM4 レジスタマップとリセット値 . . . . .                                       | 164        |

| <b>18</b> | <b>I<sup>2</sup>C (Inter-Integrated Circuit) インタフェース . . . . .</b> | <b>165</b> |

| 18.1      | 概要 . . . . .                                                       | 165        |

| 18.2      | I <sup>2</sup> C の主な機能 . . . . .                                   | 165        |

| 18.3      | I <sup>2</sup> C の概要 . . . . .                                     | 166        |

| 18.4      | I <sup>2</sup> C 機能の説明 . . . . .                                   | 168        |

| 18.4.1    | I <sup>2</sup> C スレーブモード . . . . .                                 | 168        |

| 18.4.2    | I <sup>2</sup> C マスタモード . . . . .                                  | 170        |

| 18.4.3    | エラー条件 . . . . .                                                    | 175        |

| 18.4.4    | SDA/SCL ライン制御 . . . . .                                            | 176        |

| 18.5      | I <sup>2</sup> C 低電力モード . . . . .                                  | 176        |

| 18.6      | I <sup>2</sup> C 割り込み . . . . .                                    | 177        |

| 18.7      | I <sup>2</sup> C レジスタ . . . . .                                    | 178        |

| 18.7.1    | 制御レジスタ 1 (I2C_CR1) . . . . .                                       | 178        |

| 18.7.2    | 制御レジスタ 2 (I2C_CR2) . . . . .                                       | 179        |

| 18.7.3    | 周波数レジスタ (I2C_FREQR) . . . . .                                      | 180        |

| 18.7.4    | 自己アドレスレジスタ 1 LSB (I2C_OAR1L) . . . . .                             | 181        |

| 18.7.5    | 自己アドレスレジスタ 1 MSB (I2C_OAR1H) . . . . .                             | 181        |

| 18.7.6    | 自己アドレスレジスタ 2 (I2C_OAR2) . . . . .                                  | 181        |

| 18.7.7    | データレジスタ (I2C_DR) . . . . .                                         | 182        |

|           |                                                                              |            |

|-----------|------------------------------------------------------------------------------|------------|

| 18.7.8    | ステータスレジスタ 1 (I2C_SR1) .....                                                  | 182        |

| 18.7.9    | ステータスレジスタ 2 (I2C_SR2) .....                                                  | 184        |

| 18.7.10   | ステータスレジスタ 3 (I2C_SR3) .....                                                  | 185        |

| 18.7.11   | 割り込みレジスタ (I2C_ITR) .....                                                     | 186        |

| 18.7.12   | クロック制御レジスタロー (I2C_CCRL) .....                                                | 187        |

| 18.7.13   | クロック制御レジスタハイ (I2C_CCRH) .....                                                | 188        |

| 18.7.14   | TRISE レジスタ (I2C_TRISER) .....                                                | 189        |

| 18.7.15   | I <sup>2</sup> C レジスタマップとリセット値 .....                                         | 190        |

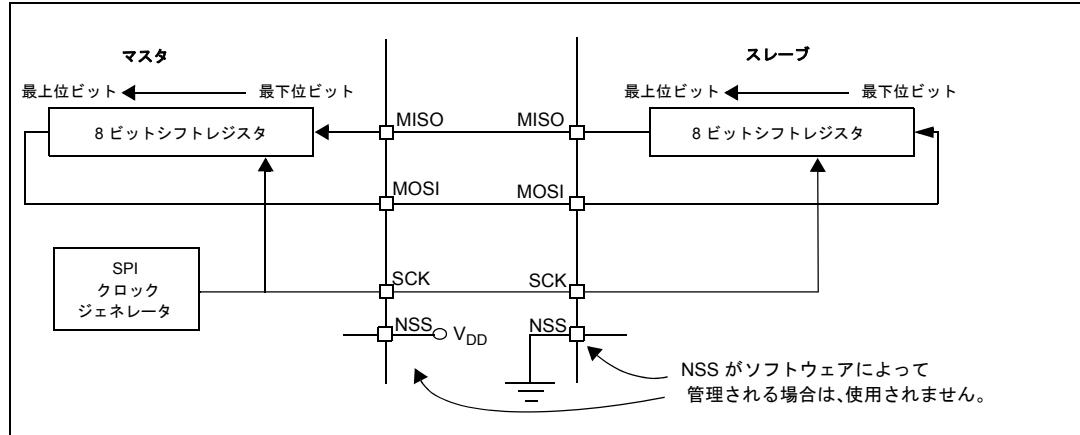

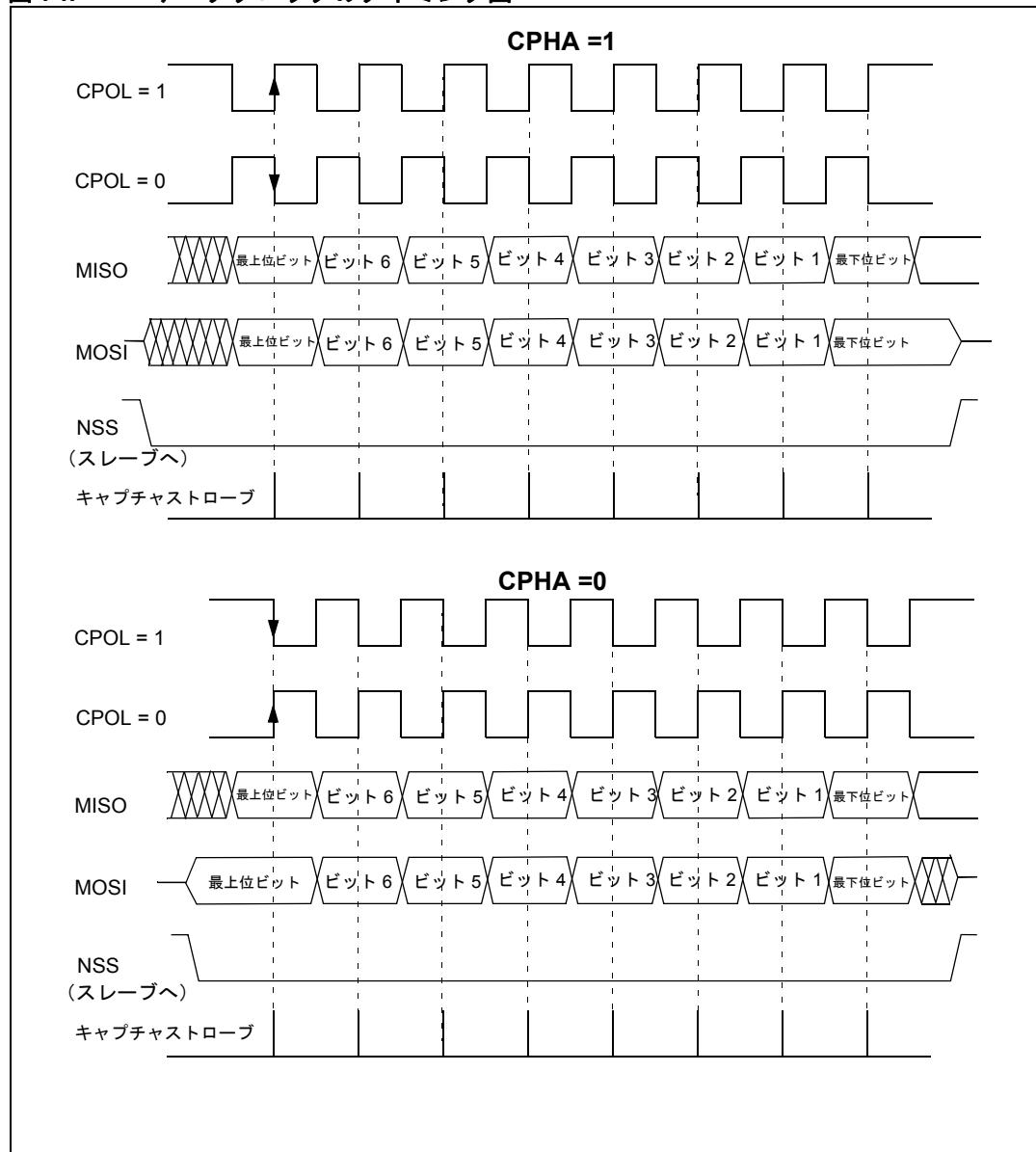

| <b>19</b> | <b>シリアルペリフェラルインターフェース (SPI) .....</b>                                        | <b>191</b> |

| 19.1      | 概要 .....                                                                     | 191        |

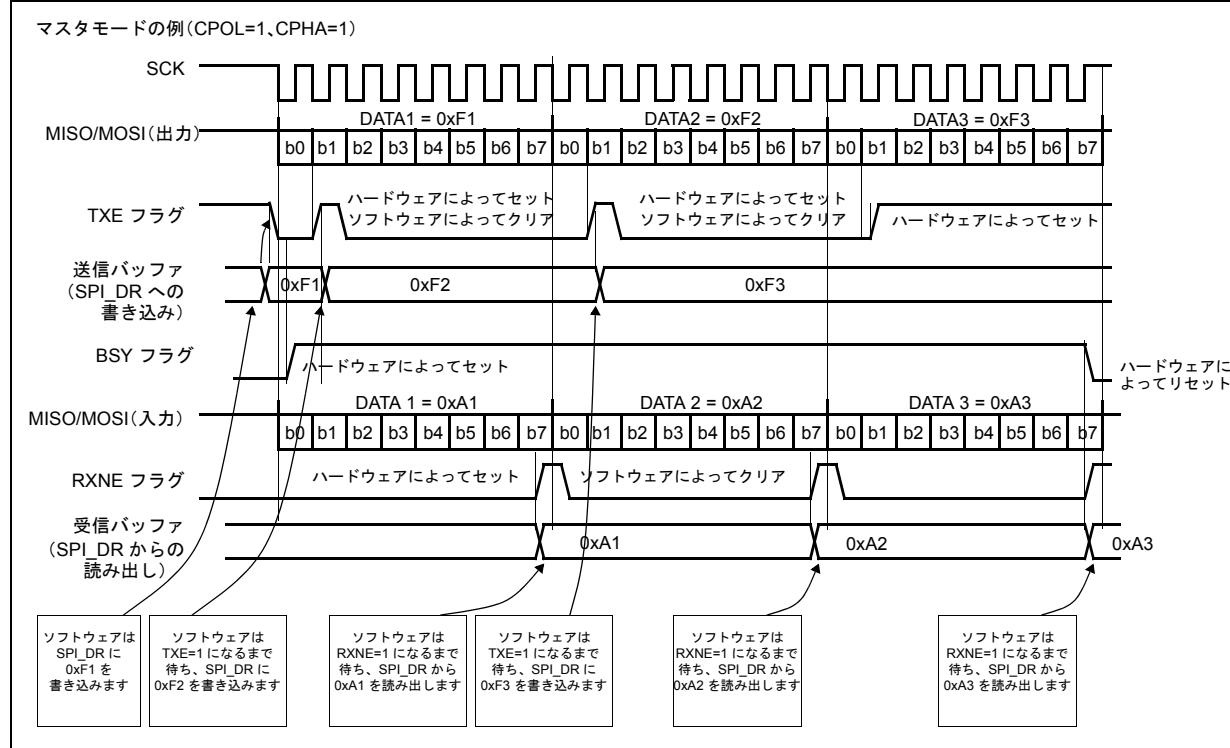

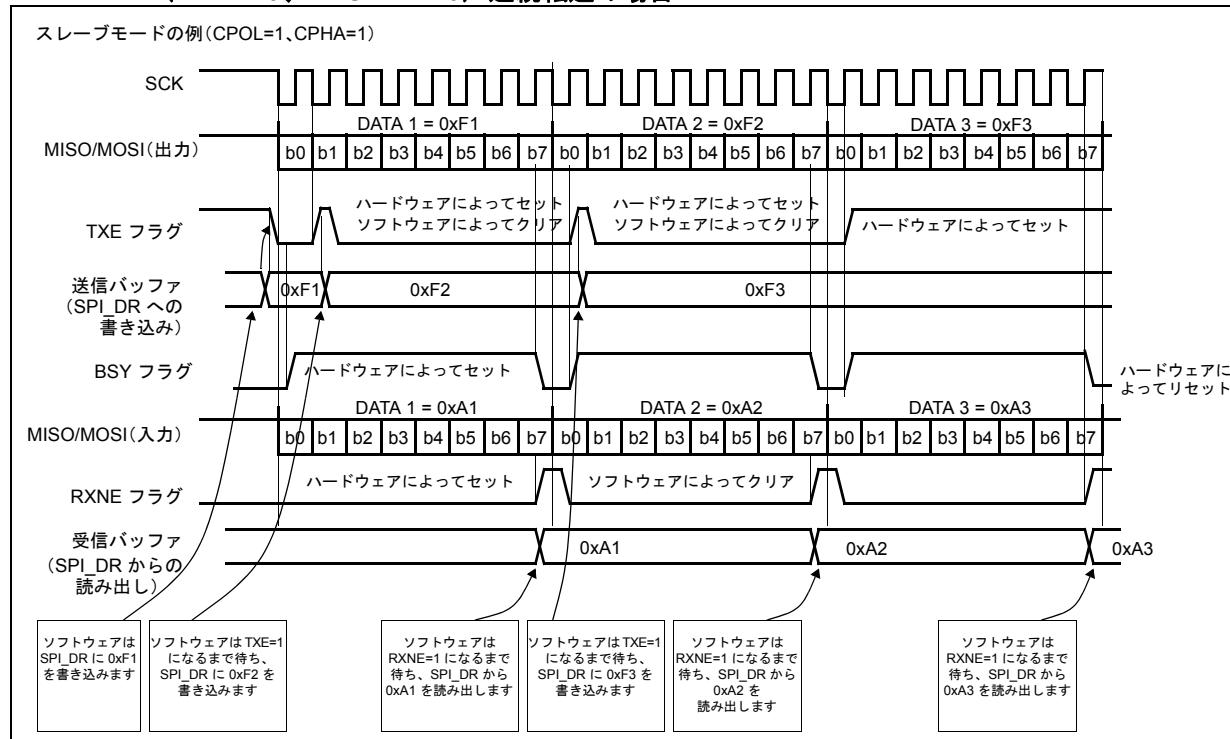

| 19.2      | SPI の主な機能 .....                                                              | 191        |

| 19.3      | SPI 機能の説明 .....                                                              | 192        |

| 19.3.1    | 概要 .....                                                                     | 192        |

| 19.3.2    | SPI のスレーブモード設定 .....                                                         | 196        |

| 19.3.3    | SPI のマスタモード設定 .....                                                          | 196        |

| 19.3.4    | SPI の単方向通信設定 .....                                                           | 197        |

| 19.3.5    | データの送受信手順 .....                                                              | 197        |

| 19.3.6    | ステータスフラグ .....                                                               | 204        |

| 19.3.7    | SPI の無効化 .....                                                               | 205        |

| 19.3.8    | エラーフラグ .....                                                                 | 206        |

| 19.3.9    | SPI 低電力モード .....                                                             | 207        |

| 19.3.10   | SPI 割り込み .....                                                               | 207        |

| 19.4      | SPI レジスタ .....                                                               | 208        |

| 19.4.1    | SPI 制御レジスタ 1 (SPI_CR1) .....                                                 | 208        |

| 19.4.2    | SPI 制御レジスタ 2 (SPI_CR2) .....                                                 | 209        |

| 19.4.3    | SPI 割り込み制御レジスタ (SPI_ICR) .....                                               | 210        |

| 19.4.4    | SPI ステータスレジスタ (SPI_SR) .....                                                 | 211        |

| 19.4.5    | SPI データレジスタ (SPI_DR) .....                                                   | 212        |

| 19.5      | SPI レジスタマップとリセット値 .....                                                      | 212        |

| <b>20</b> | <b>Universal synchronous/asynchronous receiver transmitter (USART) .....</b> | <b>213</b> |

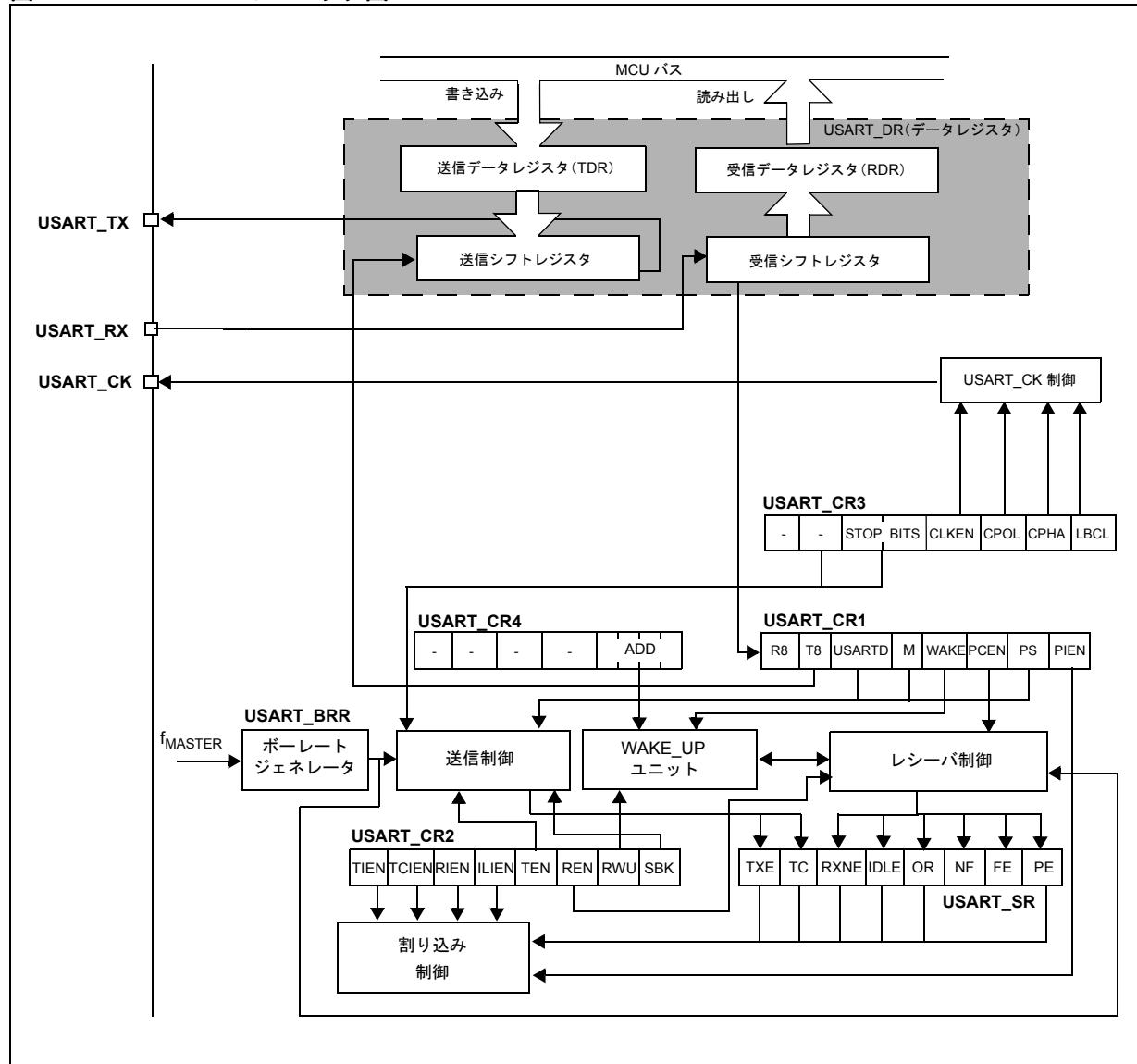

| 20.1      | USART の概要 .....                                                              | 213        |

| 20.2      | USART の主な機能 .....                                                            | 213        |

| 20.3      | USART 機能の説明 .....                                                            | 214        |

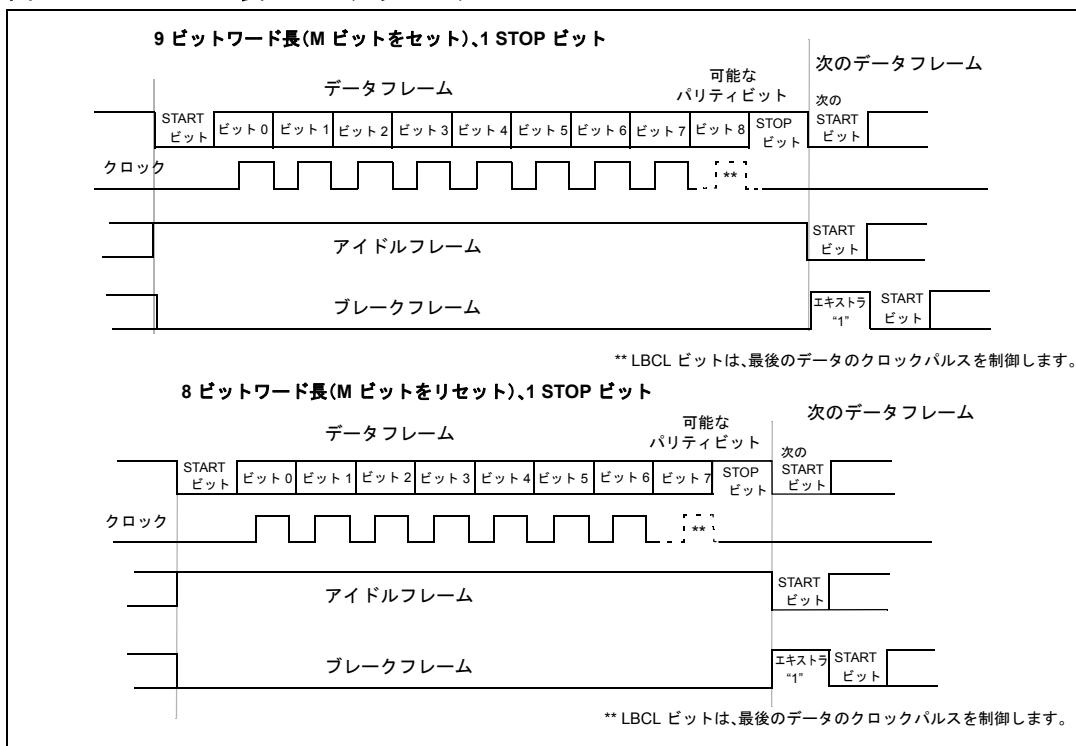

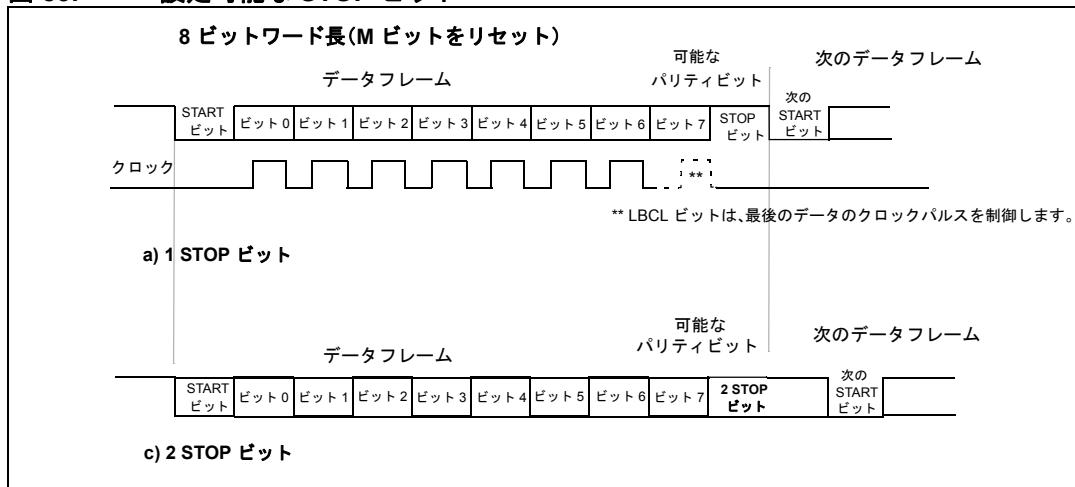

| 20.3.1    | USART キャラクタの説明 .....                                                         | 216        |

|           |                            |            |

|-----------|----------------------------|------------|

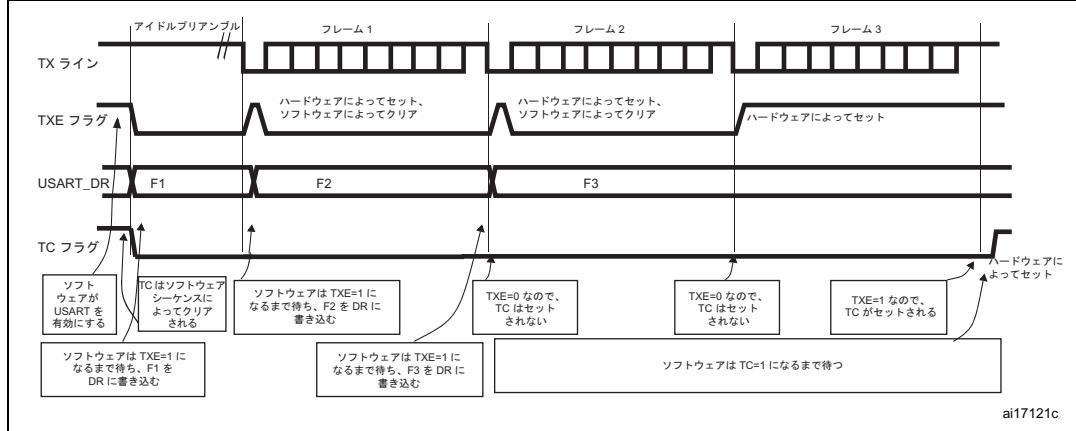

| 20.3.2    | トランスマッタ                    | 217        |

| 20.3.3    | レシーバ                       | 219        |

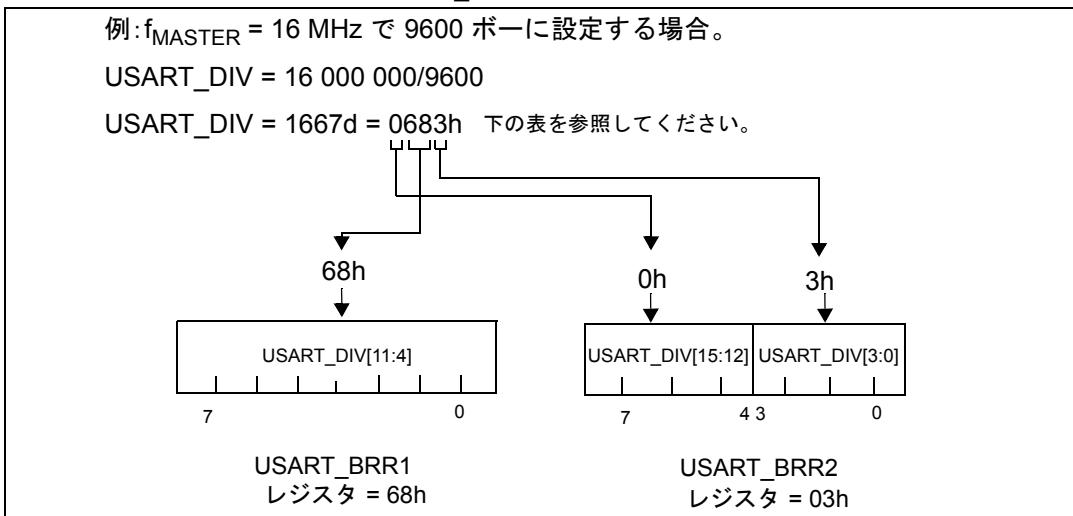

| 20.3.4    | 高精度ボーレートジェネレータ             | 223        |

| 20.3.5    | クロック偏差に対する USART レシーバの許容誤差 | 224        |

| 20.3.6    | パリティ制御                     | 224        |

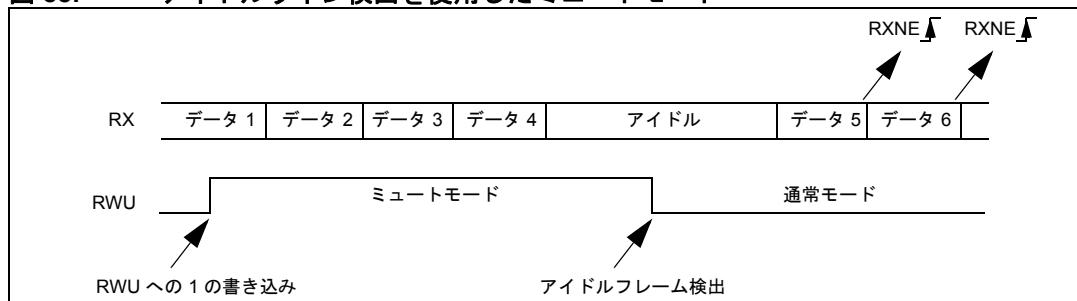

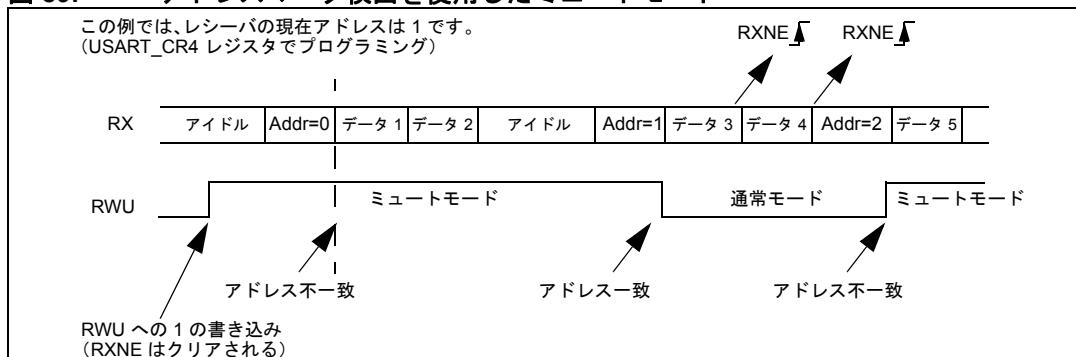

| 20.3.7    | マルチプロセッサ通信                 | 226        |

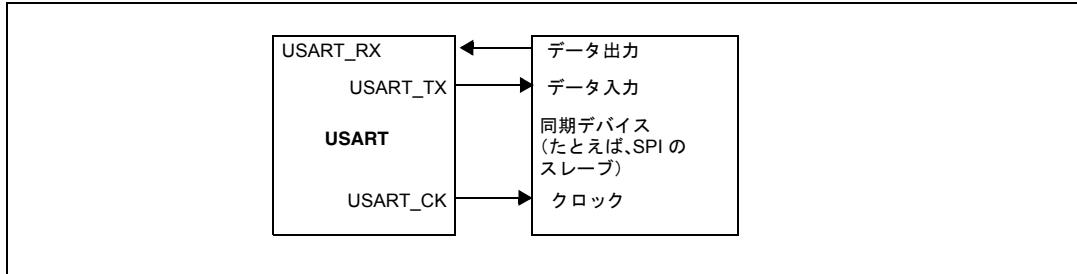

| 20.3.8    | USART 同期通信                 | 227        |

| 20.4      | USART 低電力モード               | 230        |

| 20.5      | USART 割り込み                 | 230        |

| 20.6      | USART レジスタ                 | 231        |

| 20.6.1    | ステータスレジスタ (USART_SR)       | 231        |

| 20.6.2    | データレジスタ (USART_DR)         | 232        |

| 20.6.3    | ボーレートレジスタ 1 (USART_BRR1)   | 233        |

| 20.6.4    | ボーレートレジスタ 2 (USART_BRR2)   | 233        |

| 20.6.5    | 制御レジスタ 1 (USART_CR1)       | 234        |

| 20.6.6    | 制御レジスタ 2 (USART_CR2)       | 235        |

| 20.6.7    | 制御レジスタ 3 (USART_CR3)       | 236        |

| 20.6.8    | 制御レジスタ 4 (USART_CR4)       | 237        |

| 20.6.9    | USART レジスタマップとリセット値        | 237        |

| <b>21</b> | <b>ProxSense™ (PXS)</b>    | <b>238</b> |

| 21.1      | 概要                         | 238        |

| 21.2      | ProxSense ペリフェラルの主な機能      | 238        |

| 21.3      | PXS ピン                     | 239        |

| 21.4      | 機能の説明                      | 239        |

| 21.4.1    | 概要                         | 239        |

| 21.4.2    | ProxSense 電荷移動シーケンス        | 240        |

| 21.5      | ProxSense の操作              | 241        |

| 21.5.1    | PXS のオン／オフ制御               | 241        |

| 21.5.2    | PXS の初期化                   | 241        |

| 21.5.3    | PXS 取得の起動                  | 242        |

| 21.5.4    | PXS 取得の結果                  | 243        |

| 21.5.5    | PXS 取得の停止                  | 243        |

| 21.6      | 特殊機能                       | 243        |

| 21.6.1    | サンプリングコンデンサの選択             | 243        |

| 21.6.2    | EPCC の選択                   | 243        |

|         |                                                                |     |

|---------|----------------------------------------------------------------|-----|

| 21.6.3  | RF の検出                                                         | 243 |

| 21.7    | 低電力モード                                                         | 244 |

| 21.7.1  | 低電力モードでの動作                                                     | 244 |

| 21.7.2  | 消費電力の低減                                                        | 244 |

| 21.8    | PXS 割り込み                                                       | 245 |

| 21.9    | ProxSense レジスタ                                                 | 246 |

| 21.9.1  | ProxSense 制御レジスタ 1 (PXS_CR1)                                   | 246 |

| 21.9.2  | ProxSense 制御レジスタ 2 (PXS_CR2)                                   | 247 |

| 21.9.3  | ProxSense 制御レジスタ 3 (PXS_CR3)                                   | 248 |

| 21.9.4  | ProxSense 割り込みおよびステータスレジスタ (PXS_ISR)                           | 249 |

| 21.9.5  | ProxSense クロック制御レジスタ 1 (PXS_CKCR1)                             | 250 |

| 21.9.6  | ProxSense クロック制御レジスタ 2 (PXS_CKCR2)                             | 251 |

| 21.9.7  | Rx[9:8] のレシーバイネーブルレジスタ (PXS_RXENRH)                            | 251 |

| 21.9.8  | Rx[7:0] のレシーバイネーブルレジスタ (PXS_RXENRL)                            | 251 |

| 21.9.9  | Rx[9:8] のレシーバ制御レジスタ 1 (PXS_RXCR1H)                             | 252 |

| 21.9.10 | Rx[7:0] のレシーバ制御レジスタ 1 (PXS_RXCR1L)                             | 252 |

| 21.9.11 | Rx[9:8] のレシーバ制御レジスタ 2 (PXS_RXCR2H)                             | 252 |

| 21.9.12 | Rx[7:0] のレシーバ制御レジスタ 2 (PXS_RXCR2L)                             | 252 |

| 21.9.13 | Rx[9:8] のレシーバ制御レジスタ 3 (PXS_RXCR3H)                             | 252 |

| 21.9.14 | Rx[7:0] のレシーバ制御レジスタ 3 (PXS_RXCR3L)                             | 253 |

| 21.9.15 | Rx[9:8] のレシーバインアクティブ状態レジスタ (PXS_RXINSRH)                       | 253 |

| 21.9.16 | Rx[7:0] のレシーバインアクティブ状態レジスタ (PXS_RXINSRL)                       | 253 |

| 21.9.17 | Tx[15:8] の送信イネーブルレジスタ (PXS_TXENRH)                             | 254 |

| 21.9.18 | Tx[7:0] の送信イネーブルレジスタ (PXS_TXENRL)                              | 254 |

| 21.9.19 | Rx[9:8] の最大カウンタ値レジスタ (PXS_MAXRH)                               | 254 |

| 21.9.20 | Rx[7:0] の最大カウンタ値レジスタ (PXS_MAXRL)                               | 254 |

| 21.9.21 | Rx[9:8] の最大カウンタインエーブルレジスタ (PXS_MAXENRH)                        | 255 |

| 21.9.22 | Rx[7:0] の最大カウンタインエーブルレジスタ (PXS_MAXENRL)                        | 255 |

| 21.9.23 | Rx[9:8] のレシーバステータスレジスタ (PXS_RXSRH)                             | 255 |

| 21.9.24 | Rx[7:0] のレシーバステータスレジスタ (PXS_RXSRL)                             | 255 |

| 21.9.25 | レシーバチャネル n のビット [15:8] のカウンタレジスタ (PXS_RXnCNTRH)                | 256 |

| 21.9.26 | レシーバチャネル n のビット [7:0] のカウンタレジスタ (PXS_RXnCNTRL)                 | 256 |

| 21.9.27 | レシーバ 0 ~ 9 のサンプリングコンデンサ (CS) サイズ選択レジスタ 0-9 (PXS_RXnCSSELR)     | 256 |

| 21.9.28 | レシーバ 0 ~ 9 の電極寄生補償コンデンサ (EPCC) サイズ選択レジスタ 0-9 (PXS_RXnEPCCSELR) | 257 |

# 参考資料

RM0312

目次

|           |                         |            |

|-----------|-------------------------|------------|

| 21.9.29   | ProxSense レジスタマップとリセット値 | 258        |

| <b>22</b> | <b>改版履歴</b>             | <b>260</b> |

この資料は、STMicroelectronics NV 並びにその子会社（以下 ST）が英文で記述した資料（以下、「正規英語版資料」）を、皆様のご理解の一助として頂くために ST マイクロエレクトロニクス㈱が英文から和文へ翻訳して作成したものです。この資料は現行の正規英語版資料の近時の更新に対応していない場合があります。この資料は、あくまでも正規英語版資料をご理解頂くための補助的参考資料のみにご利用下さい。この資料で説明される製品のご検討及びご採用にあたりましては、必ず最新の正規英語版資料を事前にご確認下さい。ST 及び ST マイクロエレクトロニクス㈱は、現行の正規英語版資料の更新により製品に関する最新の情報を提供しているにも関わらず、当該英語版資料に対応した更新がなされていないこの資料の情報に基づいて発生した問題や障害などにつきましては如何なる責任も負いません。

## 表の一覧

|       |                                                       |     |

|-------|-------------------------------------------------------|-----|

| 表 1.  | 略語一覧                                                  | 18  |

| 表 2.  | 割り込みレベル                                               | 22  |

| 表 3.  | CPU レジスタマップ                                           | 23  |

| 表 4.  | CFG_GCR レジスタマップ                                       | 24  |

| 表 5.  | ブロックサイズ                                               | 34  |

| 表 6.  | メモリアクセスとプログラミング法                                      | 35  |

| 表 7.  | フラッシュレジスタマップ                                          | 40  |

| 表 8.  | ソフトウェア優先順位レベル                                         | 41  |

| 表 9.  | ISR の内部で割り込みを有効／無効にする方法                               | 42  |

| 表 10. | ベクタアドレスマップとソフトウェア優先順位ビット                              | 47  |

| 表 11. | 外部割り込みトリガ                                             | 48  |

| 表 12. | 専用割り込み命令セット                                           | 48  |

| 表 13. | ITC および EXTI レジスタマップ                                  | 55  |

| 表 14. | RST レジスタマップとリセット値                                     | 60  |

| 表 15. | ペリフェラルクロックゲーティングビット                                   | 64  |

| 表 16. | CLK レジスタマップとリセット値                                     | 65  |

| 表 17. | 低電力モードの管理                                             | 68  |

| 表 18. | WFE レジスタマップ                                           | 73  |

| 表 19. | 入出力ポート設定の要約                                           | 76  |

| 表 20. | 低電力モードが GPIO ポートに与える影響                                | 77  |

| 表 21. | GPIO レジスタマップ                                          | 81  |

| 表 22. | タイムベースの計算テーブル                                         | 84  |

| 表 23. | AWU レジスタマップ                                           | 87  |

| 表 24. | ビーパレジスタマップ                                            | 89  |

| 表 25. | ウインドウ型ウォッチドッグのタイミング例                                  | 92  |

| 表 26. | 低電力モードが WWWDG に与える影響                                  | 92  |

| 表 27. | WWWDG レジスタマップとリセット値                                   | 93  |

| 表 28. | IWDG タイムアウト時間の最小値／最大値 (LSI クロック周波数 = 38 kHz)          | 95  |

| 表 29. | IWDG register map                                     | 97  |

| 表 30. | タイマの特性                                                | 98  |

| 表 31. | タイマ機能の比較                                              | 98  |

| 表 32. | 内部タイマ信号の用語                                            | 99  |

| 表 33. | カウント方向とエンコーダ信号                                        | 136 |

| 表 34. | ブレーキ機能を持つ OCx チャンネルの出力制御ビット                           | 154 |

| 表 35. | TIMx レジスタマップ                                          | 155 |

| 表 36. | TIM4 レジスタマップ                                          | 164 |

| 表 37. | 低電力モードでの I <sup>2</sup> C インタフェースの動作                  | 176 |

| 表 38. | I <sup>2</sup> C 割り込みリクエスト                            | 177 |

| 表 39. | SCL 周波数に対する I <sup>2</sup> C_CCR 値 (fMASTER = 16 MHz) | 189 |

| 表 40. | I <sup>2</sup> C レジスタマップ                              | 190 |

| 表 41. | 低電力モードでの SPI 動作                                       | 207 |

| 表 42. | SPI 割り込みリクエスト                                         | 207 |

| 表 43. | SPI レジスタマップとリセット値                                     | 212 |

| 表 44. | サンプリングされたデータからのノイズ検出                                  | 222 |

| 表 45. | ボーレートのプログラミングと誤差計算                                    | 223 |

| 表 46. | USART レシーバの許容誤差 (USART_DIV が 0 の場合)                   | 224 |

| 表 47. | USART レシーバの許容誤差 (USART_DIV が 0 でない場合)                 | 224 |

| 表 48. | フレームフォーマット                                            | 224 |

| 表 49. | 低電力モードでの USART インタフェースの動作                             | 230 |

# 参考資料

RM0312

表の一覧

|       |                      |     |

|-------|----------------------|-----|

| 表 50. | USART 割り込みリクエスト      | 230 |

| 表 51. | USART レジスタマップ        | 237 |

| 表 52. | PXS ピン               | 239 |

| 表 53. | UP および PASS フェーズ中の動作 | 240 |

| 表 54. | 低電力モードでの動作           | 244 |

| 表 55. | ProxSense レジスタマップ    | 258 |

| 表 56. | 改版履歴                 | 260 |

## 図の一覧

|       |                                                    |     |

|-------|----------------------------------------------------|-----|

| 図 1.  | プログラミングモデル                                         | 20  |

| 図 2.  | スタッキングの順序                                          | 21  |

| 図 3.  | SWIM ピンの接続                                         | 25  |

| 図 4.  | STM8TL5xxx フラッシュプログラムおよびデータ EEPROM の構成             | 27  |

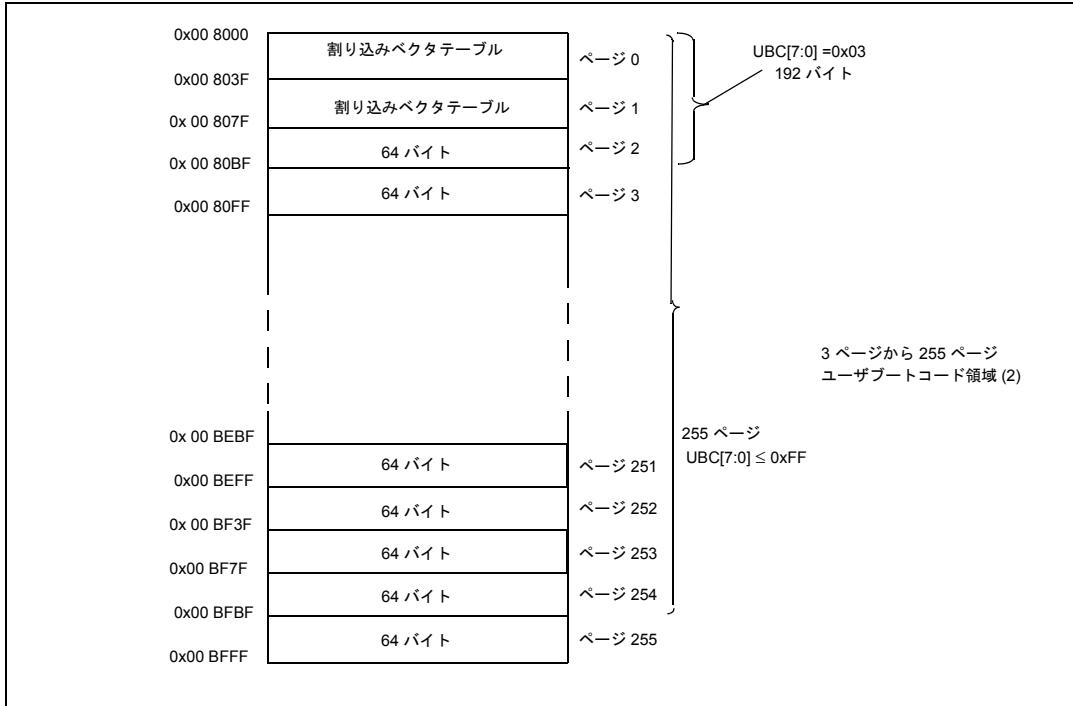

| 図 5.  | タッチセンシング STM8TL5xxx デバイスの UBC 領域サイズの定義             | 29  |

| 図 6.  | 割り込み処理のフローチャート                                     | 42  |

| 図 7.  | 優先順位決定プロセス                                         | 43  |

| 図 8.  | 同時割り込み管理                                           | 46  |

| 図 9.  | ネスト割り込み管理                                          | 47  |

| 図 10. | 電源の概要                                              | 56  |

| 図 11. | リセット回路                                             | 57  |

| 図 12. | クロック構造                                             | 61  |

| 図 13. | GPIO ブロック図                                         | 75  |

| 図 14. | AWU のブロック図                                         | 82  |

| 図 15. | ビープのブロック図                                          | 88  |

| 図 16. | ウォッチドッグのブロック図                                      | 90  |

| 図 17. | ウインドウ型ウォッチドッグのタイミング図                               | 92  |

| 図 18. | 独立型ウォッチドッグのブロック図                                   | 94  |

| 図 19. | TIMx の一般的なブロック図                                    | 101 |

| 図 20. | タイムベースユニット                                         | 102 |

| 図 21. | カウンタの 16 ビット読み出しシーケンス (TIMx_CNT)                   | 103 |

| 図 22. | アップカウントモードのカウンタ                                    | 104 |

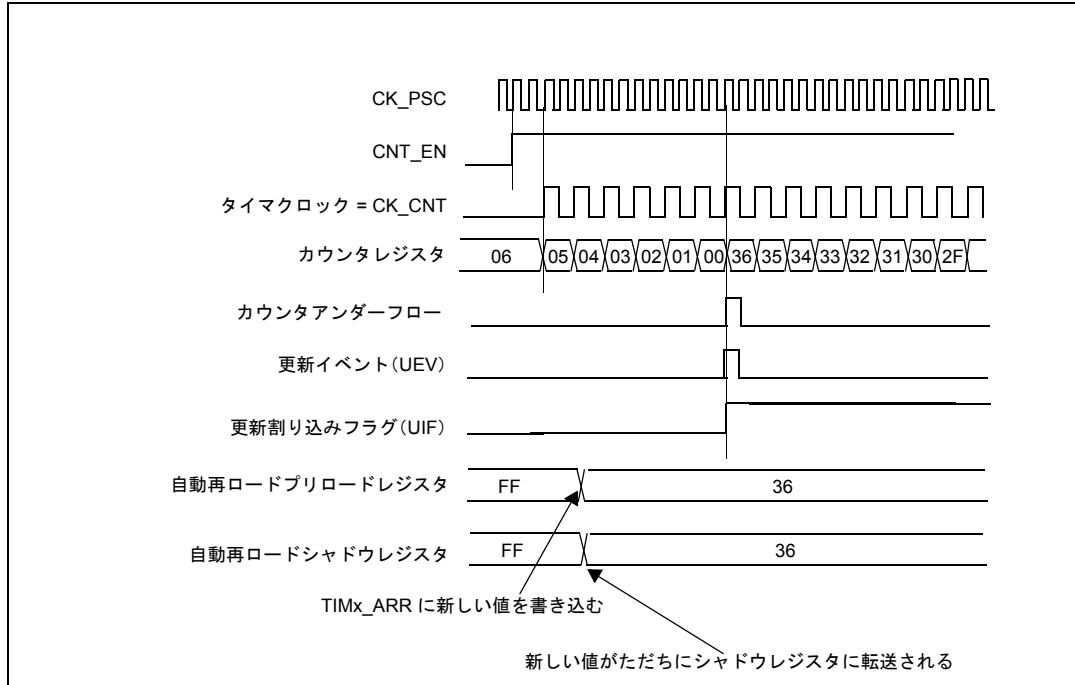

| 図 23. | プリスケーラ = 2 で ARPE = 0 (ARR はプリロードされない) のときのカウンタの更新 | 105 |

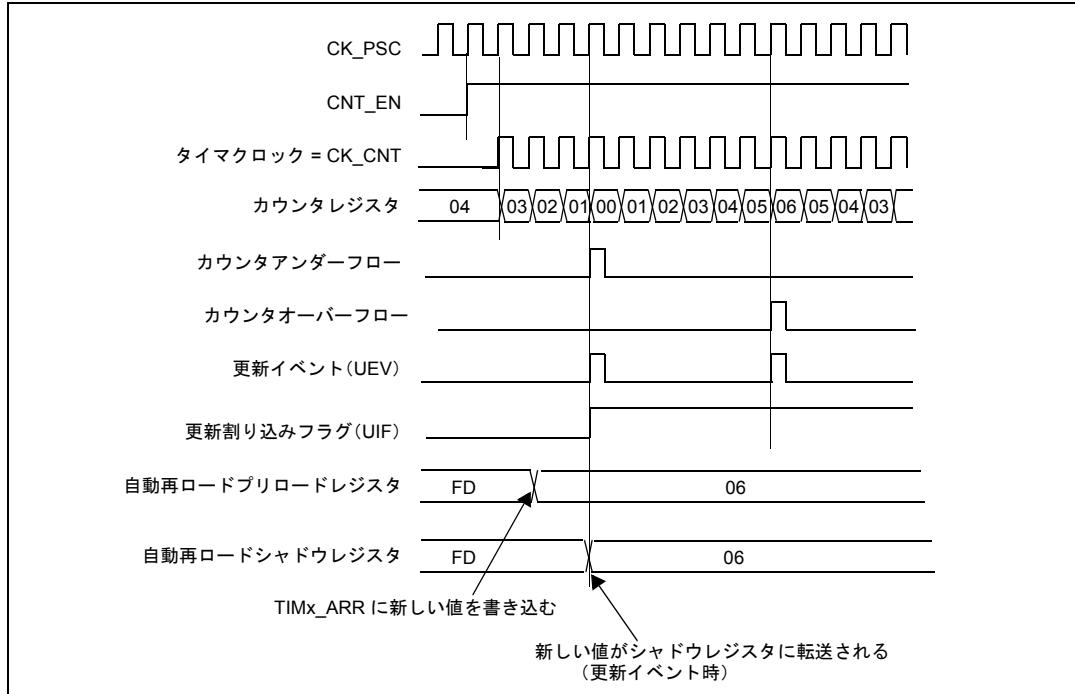

| 図 24. | ARPE=1 (TIMx_ARR はプリロードされる) のときのカウンタ更新イベント         | 105 |

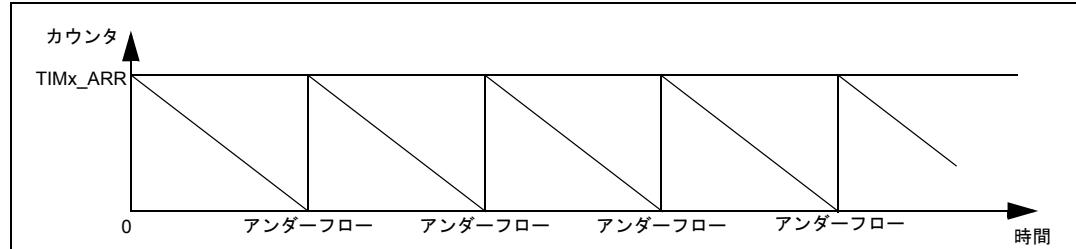

| 図 25. | ダウンカウントモードのカウンタ                                    | 106 |

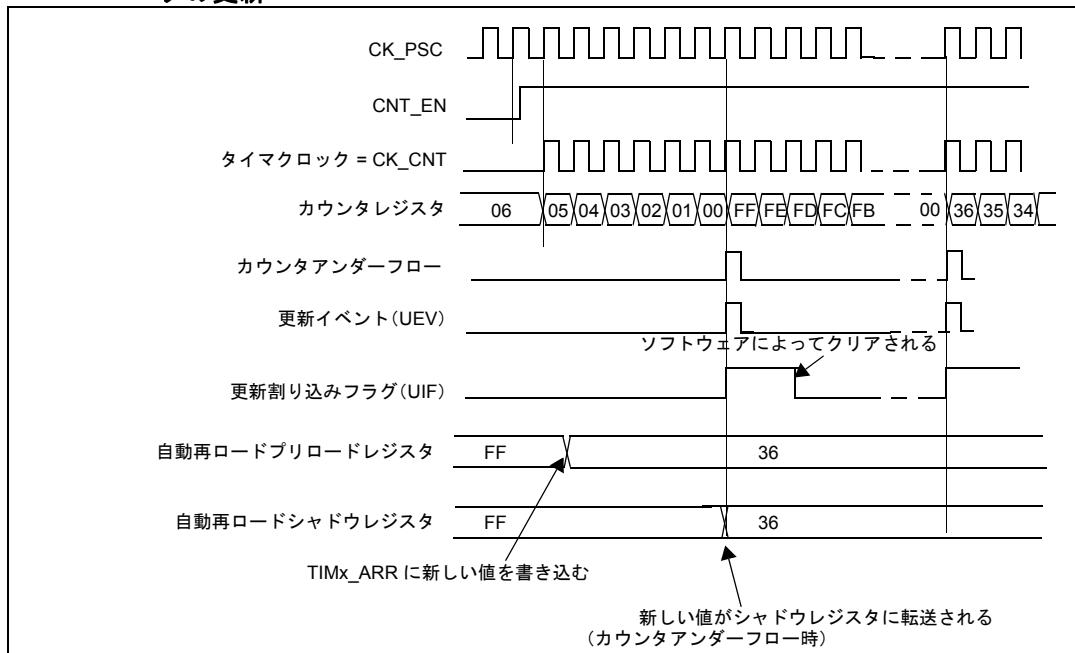

| 図 26. | プリスケーラ = 2 で ARPE = 0 (ARR はプリロードされない) のときのカウンタの更新 | 107 |

| 図 27. | プリスケーラ = 1 で ARPE = 1 (ARR はプリロードされる) のときのカウンタの更新  | 107 |

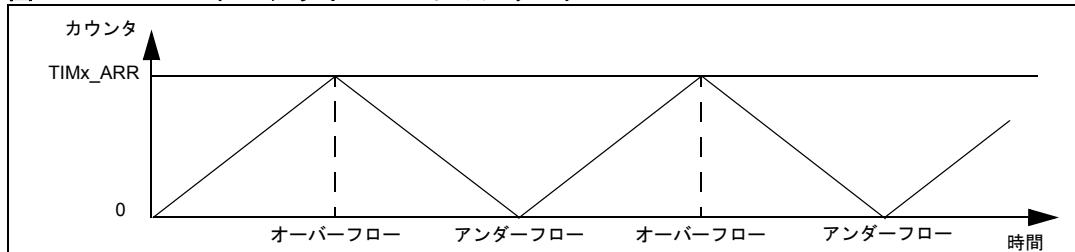

| 図 28. | センターラインモードのカウンタ                                    | 108 |

| 図 29. | カウンタのタイミング図、CK_PSC を 1 分周、TIMx_ARR=06h、ARPE=1      | 109 |

| 図 30. | クロック／トリガコントローラのブロック図                               | 110 |

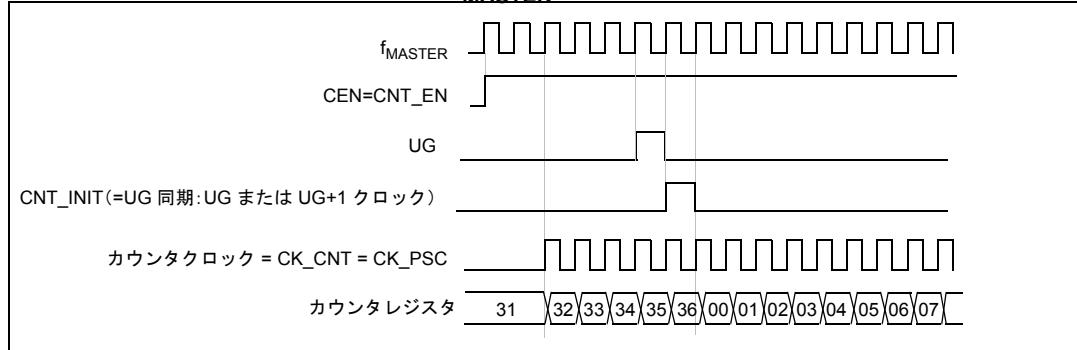

| 図 31. | 通常モードの制御回路、fMASTER を 1 分周                          | 111 |

| 図 32. | TI2 外部クロックの接続例                                     | 111 |

| 図 33. | 外部クロックモード 1 の制御回路                                  | 112 |

| 図 34. | 外部トリガ入力ブロック                                        | 112 |

| 図 35. | 外部クロックモード 2 の制御回路                                  | 113 |

| 図 36. | トリガモードの制御回路                                        | 114 |

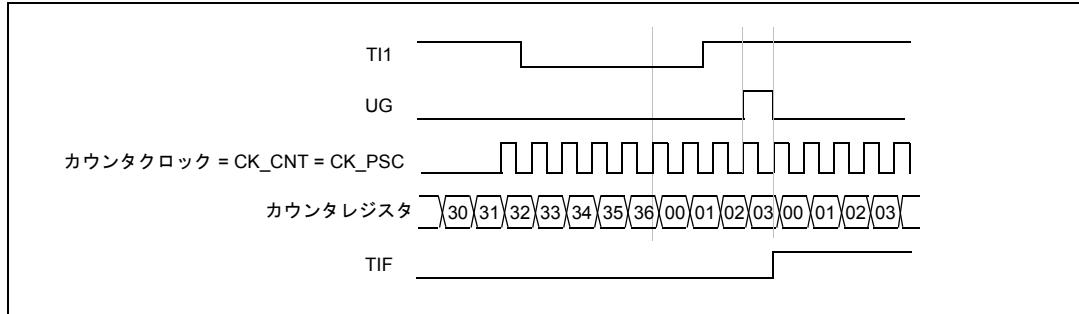

| 図 37. | トリガリセットモードの制御回路                                    | 115 |

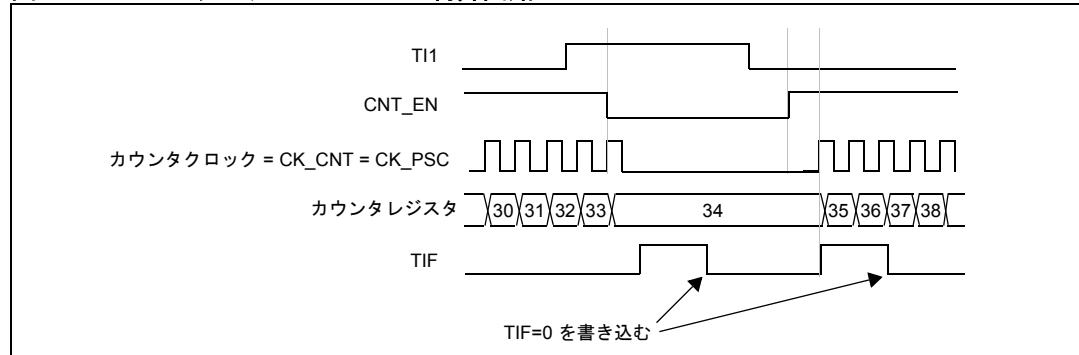

| 図 38. | トリガゲートモードの制御回路                                     | 115 |

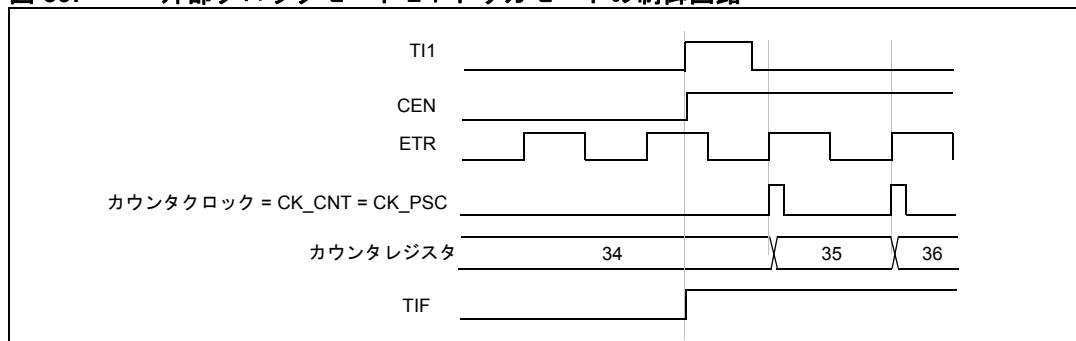

| 図 39. | 外部クロックモード 2 + トリガモードの制御回路                          | 116 |

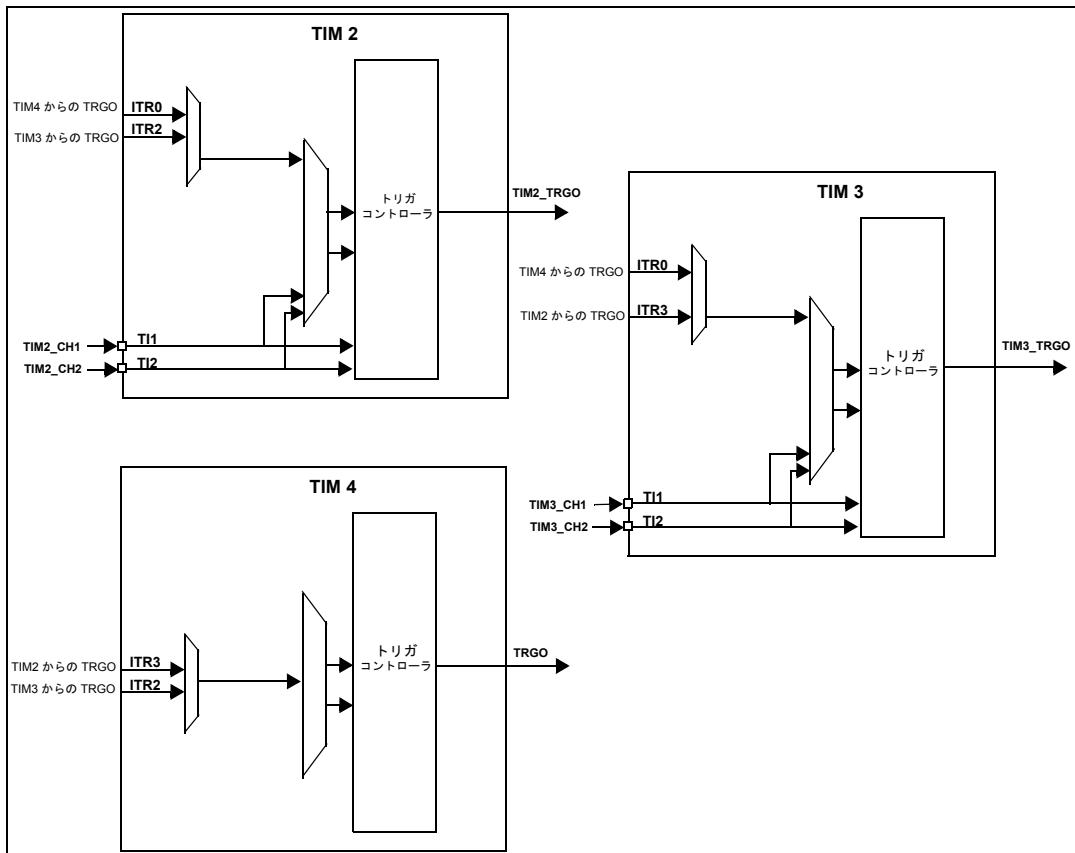

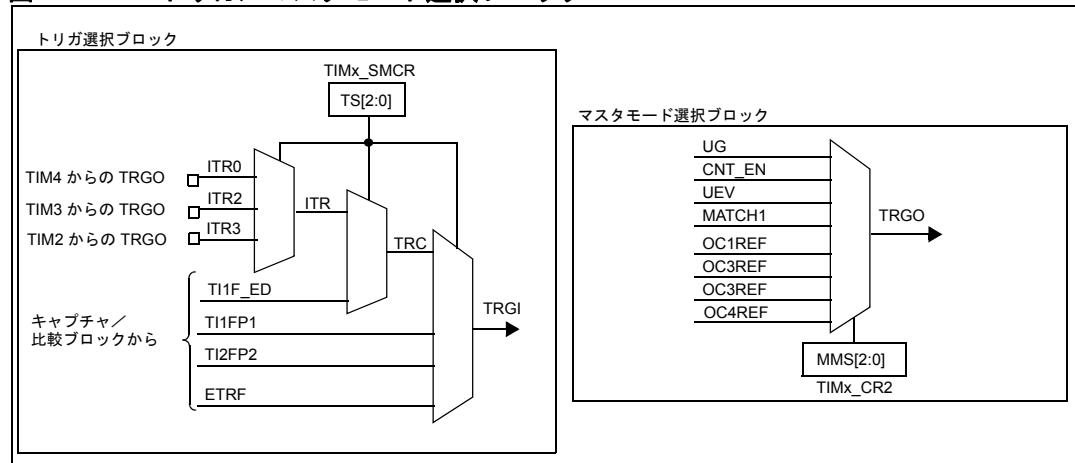

| 図 40. | タイマ連続システムの実装例                                      | 117 |

| 図 41. | トリガ／マスタモード選択ブロック                                   | 117 |

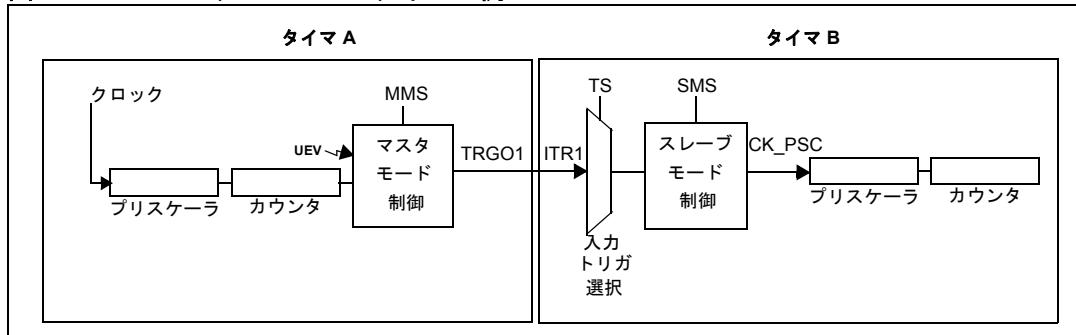

| 図 42. | マスタ／スレーブタイマの例                                      | 118 |

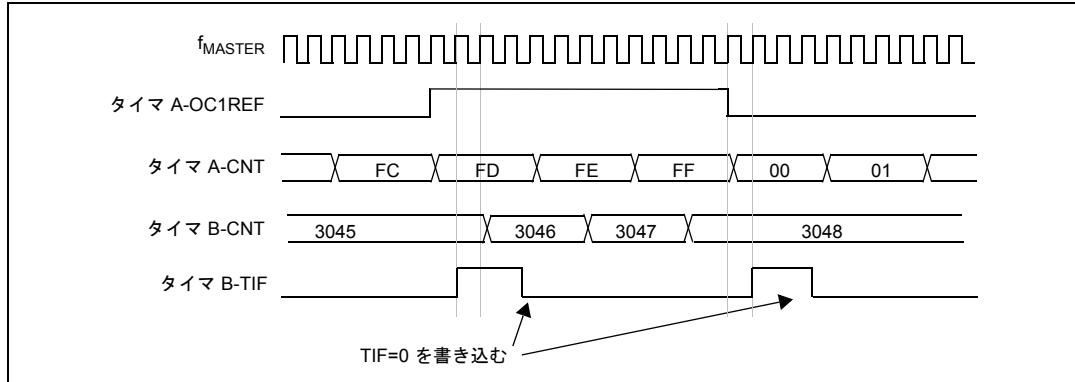

| 図 43. | タイマ A の OC1REF によるタイマ B のゲート操作                     | 119 |

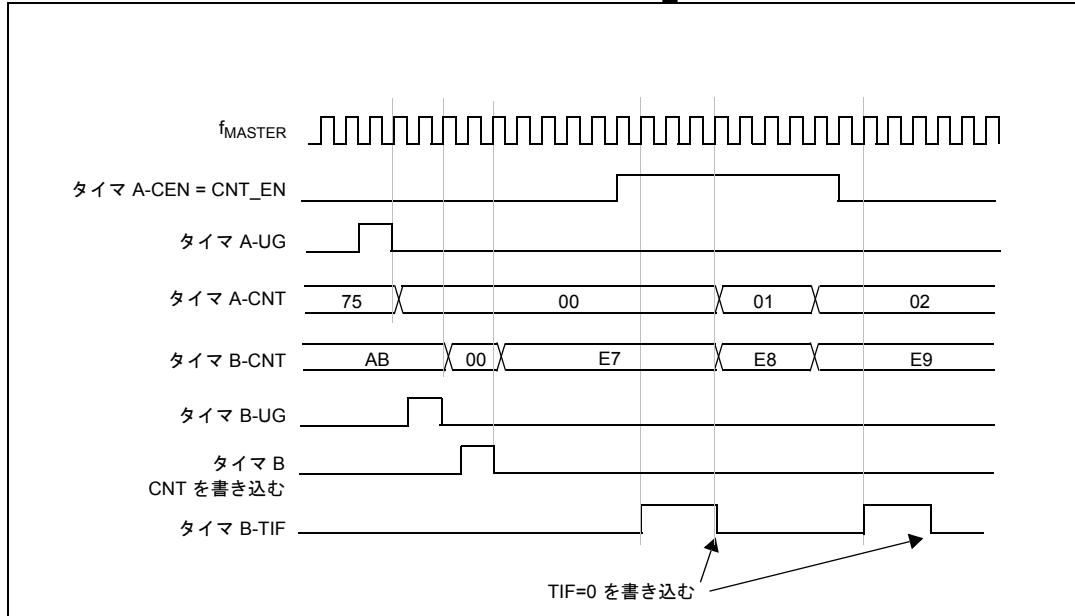

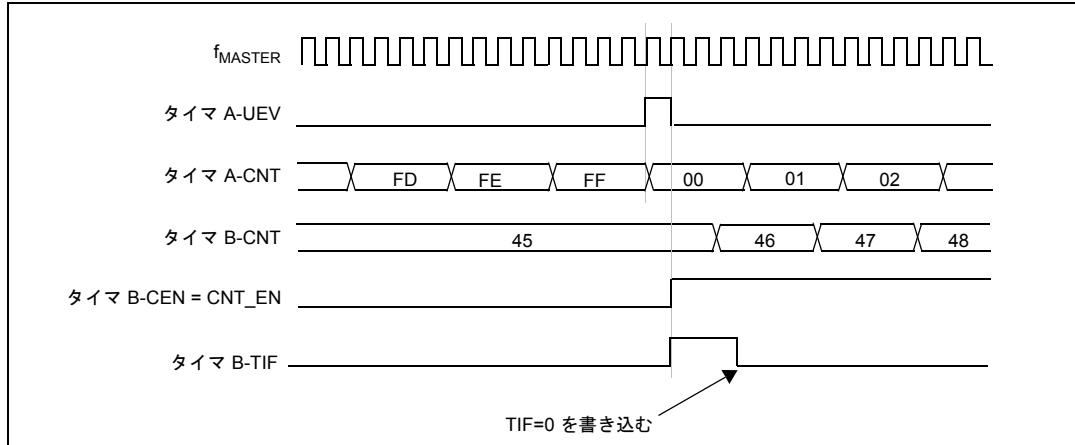

| 図 44. | タイマ A のカウンタネーブル信号 (CNT_EN) によるタイマ B のゲート操作         | 120 |

| 図 45. | タイマ A の更新イベント (TIMERA-UEV) によるタイマ B のトリガ           | 121 |

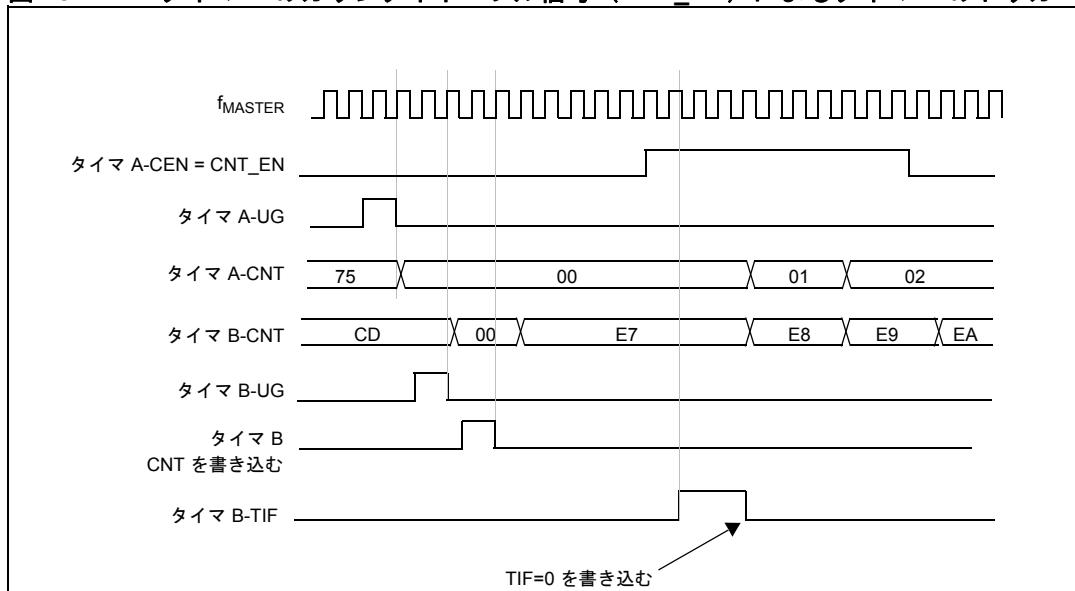

| 図 46. | タイマ A のカウンタネーブル信号 (CNT_EN) によるタイマ B のトリガ           | 121 |

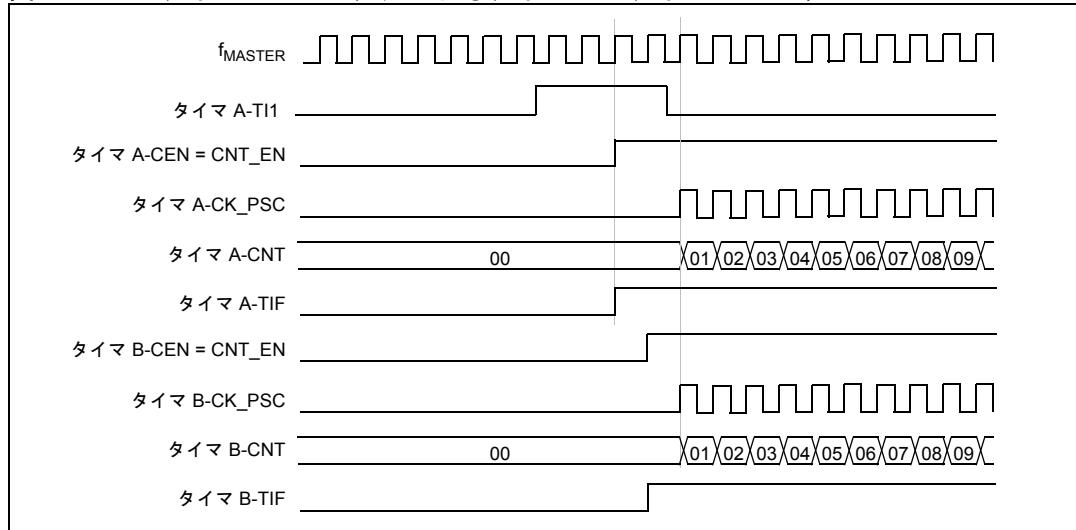

| 図 47. | タイマ A の TI1 入力によるタイマ A とタイマ B のトリガ                 | 122 |

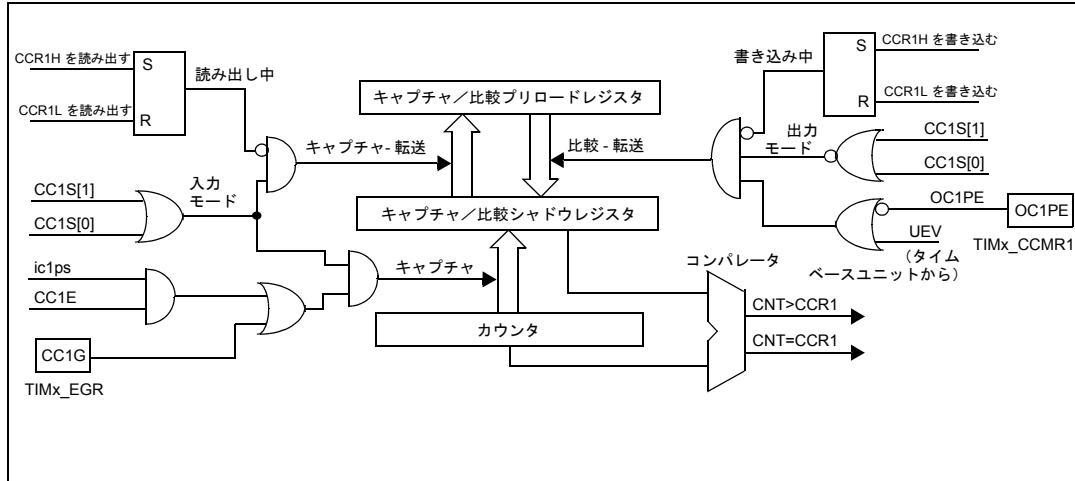

| 図 48. | キャプチャ／比較チャネル 1 メイン回路                               | 123 |

| 図 49. | キャプチャモードでの TIMx_CCRI レジスタの 16 ビット読み出しシーケンス         | 124 |

# 参考資料

|       |                                                               |     |

|-------|---------------------------------------------------------------|-----|

| 図 50. | チャネル入力ステージのブロック図                                              | 124 |

| 図 51. | TIM 1 チャネル 1 の入力ステージ                                          | 125 |

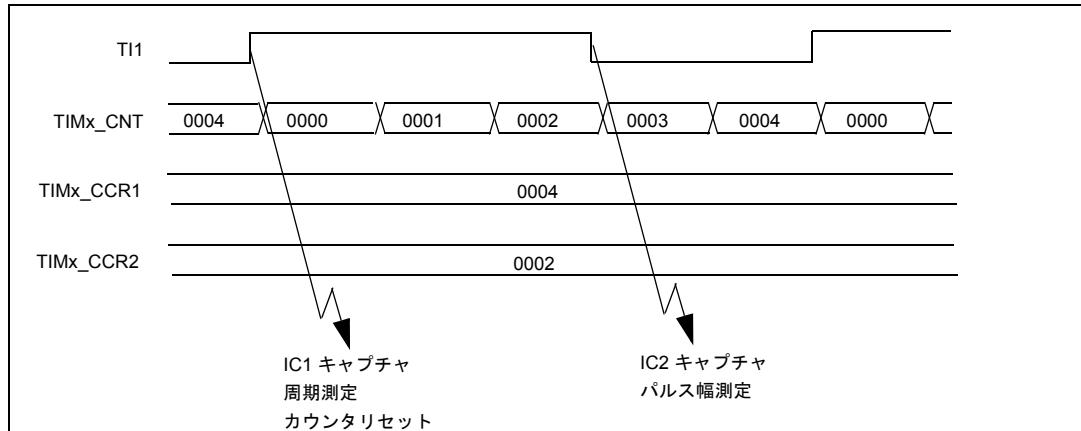

| 図 52. | PWM 入力信号の測定                                                   | 126 |

| 図 53. | PWM 入力信号測定の例                                                  | 127 |

| 図 54. | チャネル出力ステージのブロック図                                              | 127 |

| 図 55. | チャネル 1 の出力ステージ                                                | 128 |

| 図 56. | 出力比較モード、OC1 のトグル                                              | 129 |

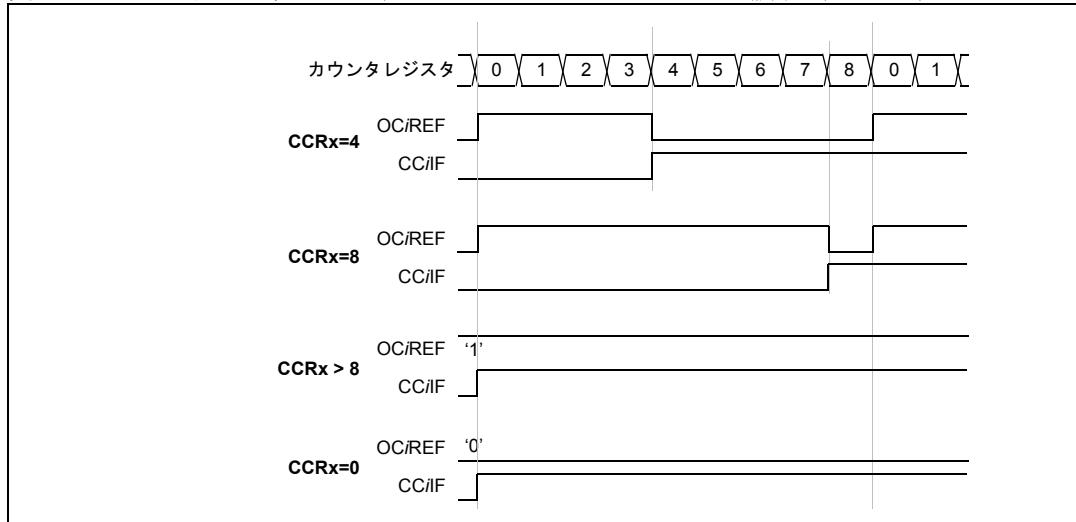

| 図 57. | エッジアラインカウントモード PWM モード 1 の波形 (ARR=8)                          | 130 |

| 図 58. | センターライン PWM 波形 (ARR=8)                                        | 131 |

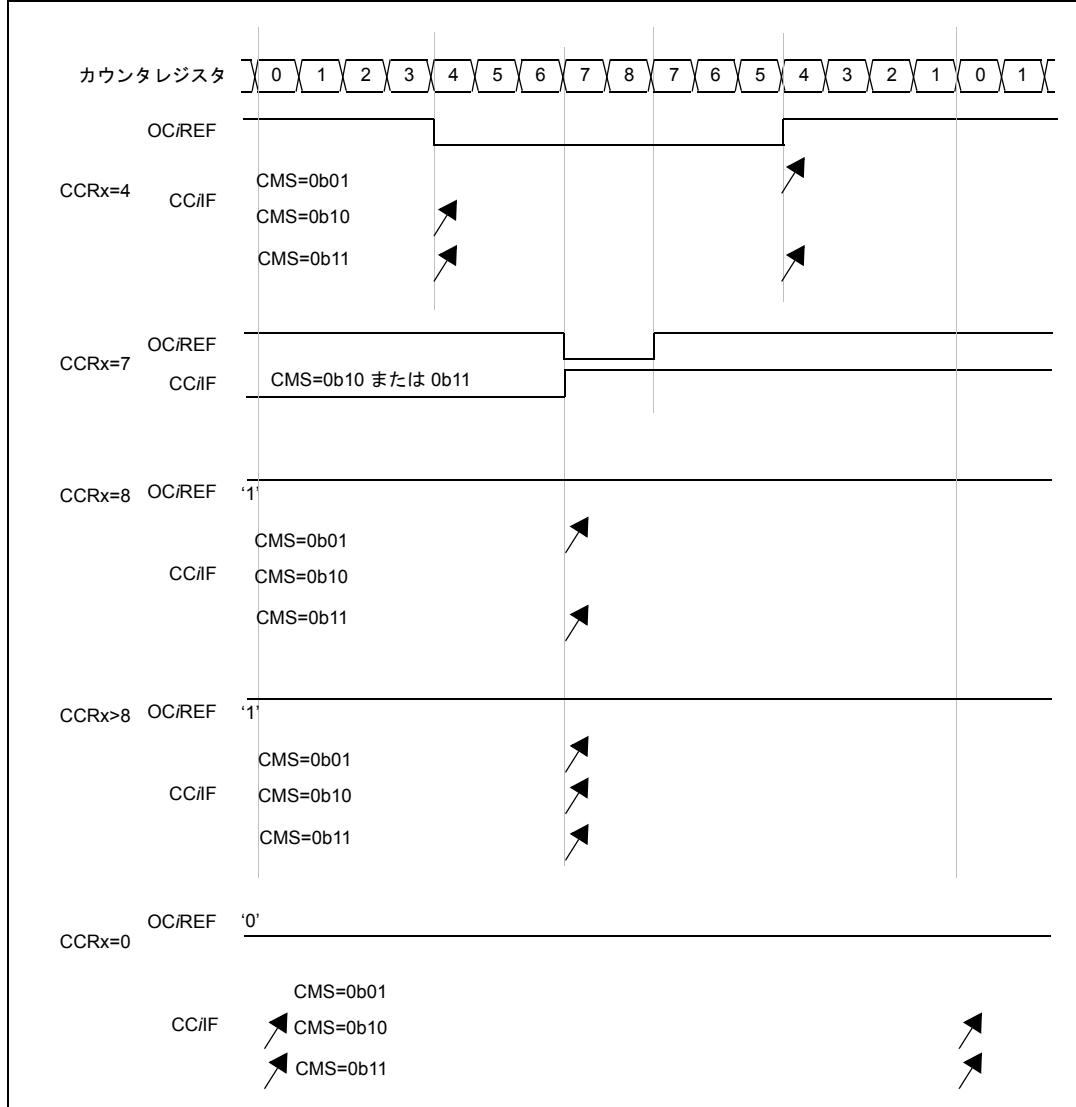

| 図 59. | ワンパルスモードの例                                                    | 132 |

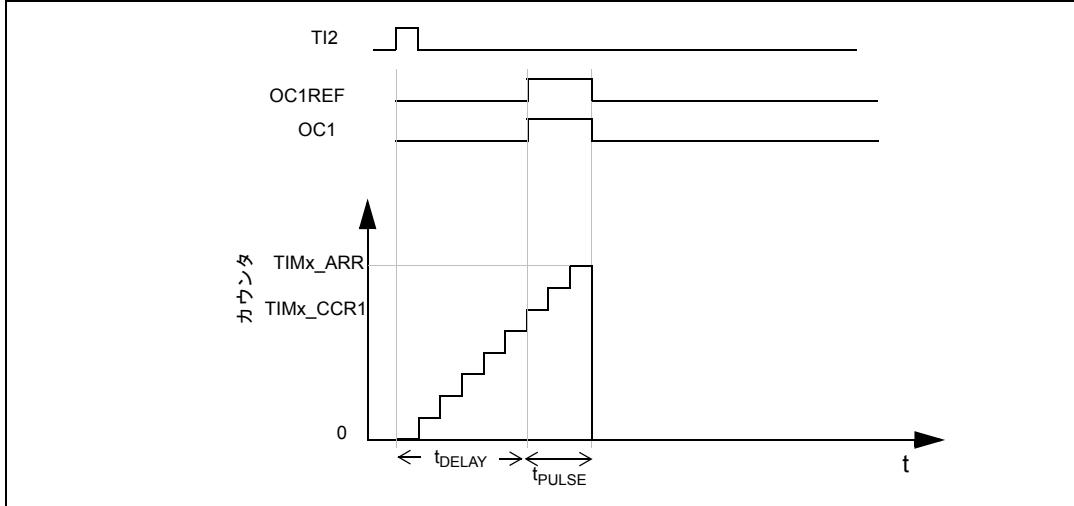

| 図 60. | ブレークに対する出力の動作                                                 | 134 |

| 図 61. | ETR のアクティブ化                                                   | 135 |

| 図 62. | エンコーダインタフェースモードにおけるカウンタの動作例                                   | 137 |

| 図 63. | IC1 の極性を反転したエンコーダインタフェースモードの例                                 | 137 |

| 図 64. | TIM4 ブロック図                                                    | 157 |

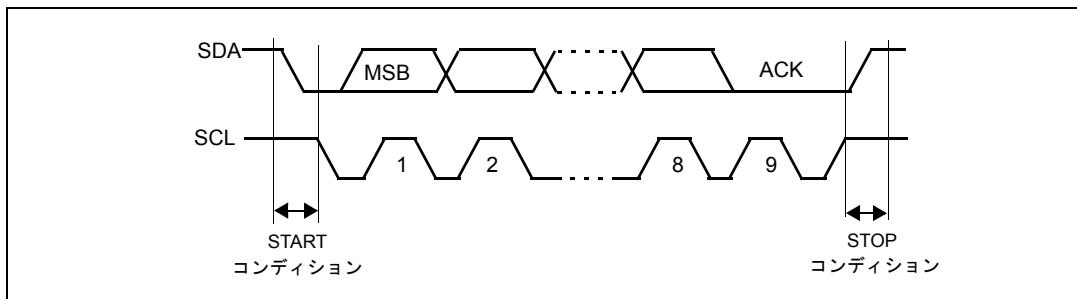

| 図 65. | I <sup>2</sup> C バスプロトコル                                      | 166 |

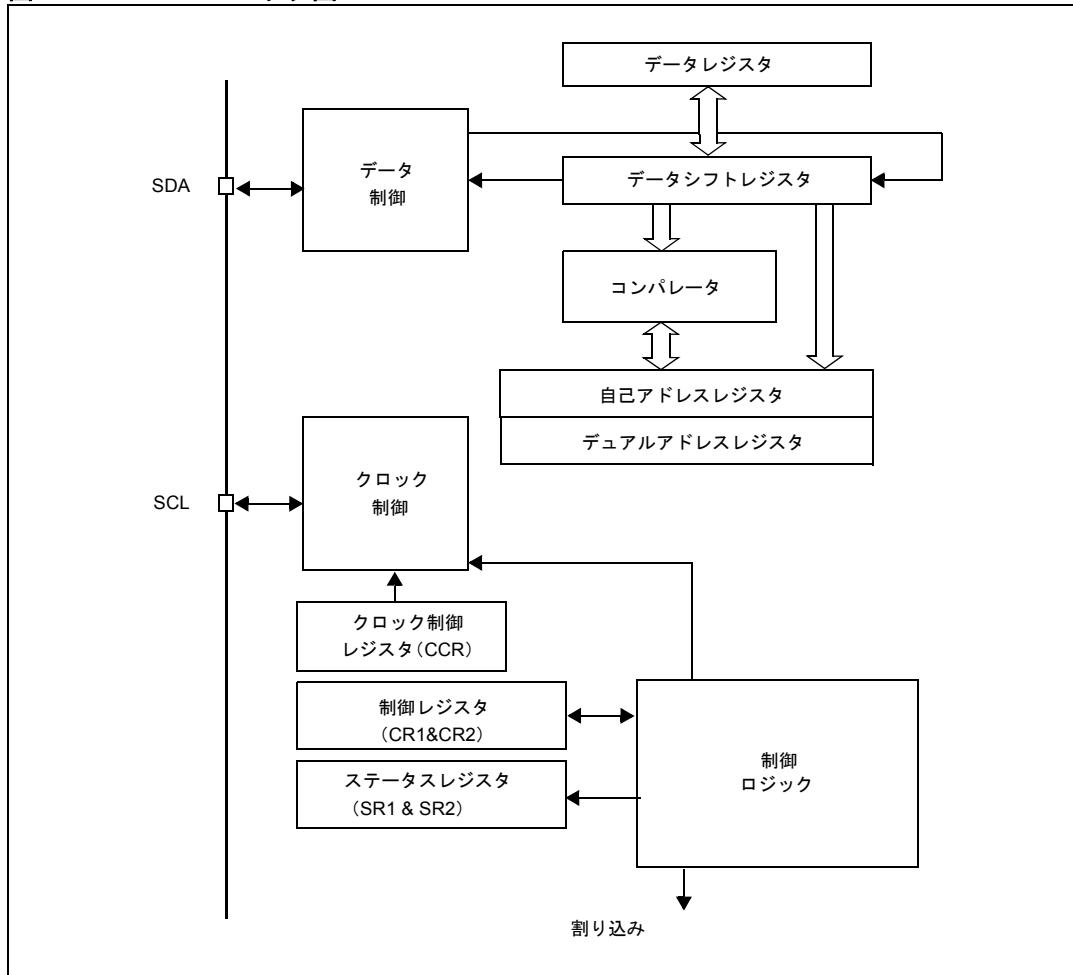

| 図 66. | I <sup>2</sup> C ブロック図                                        | 167 |

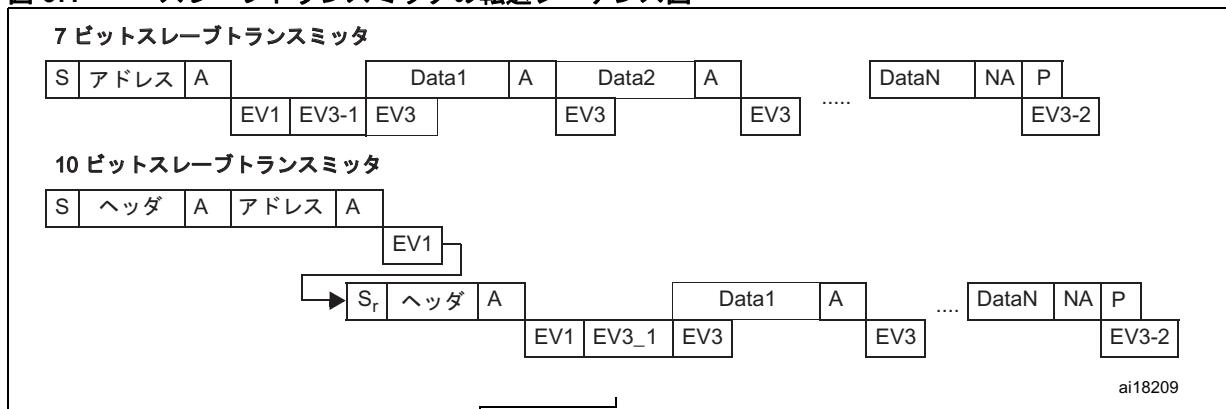

| 図 67. | スレーブトランスマッタの転送シーケンス図                                          | 169 |

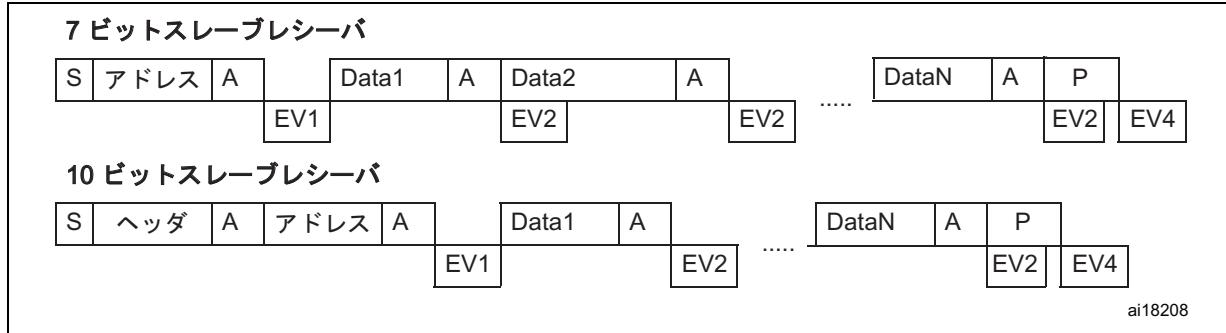

| 図 68. | スレーブレシーバの転送シーケンス図                                             | 170 |

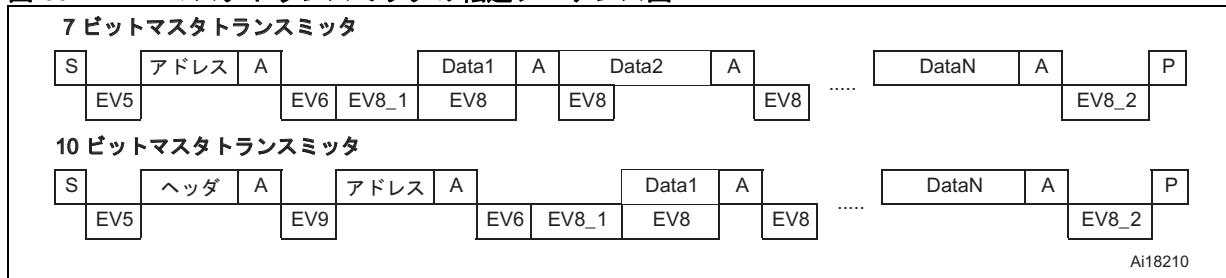

| 図 69. | マスタトランスマッタの転送シーケンス図                                           | 172 |

| 図 70. | マスタレシーバの転送シーケンス図                                              | 173 |

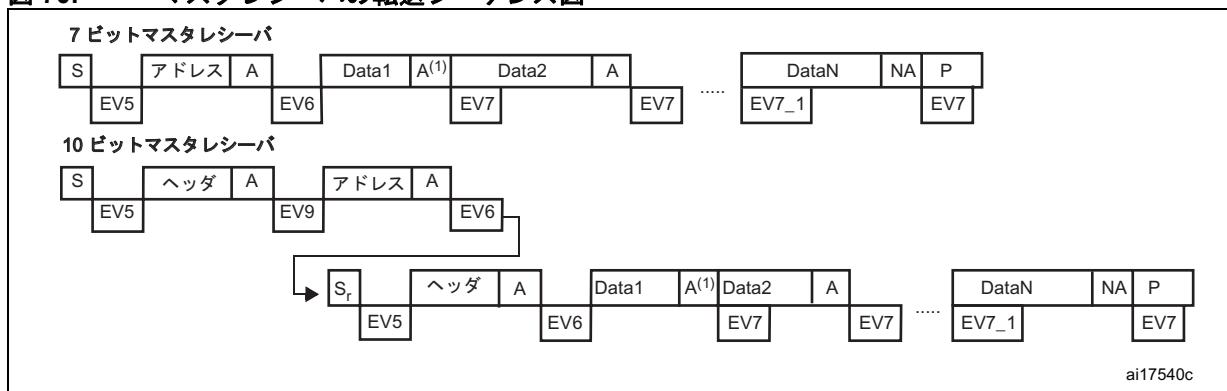

| 図 71. | I <sup>2</sup> C 割り込みマッピング図                                   | 177 |

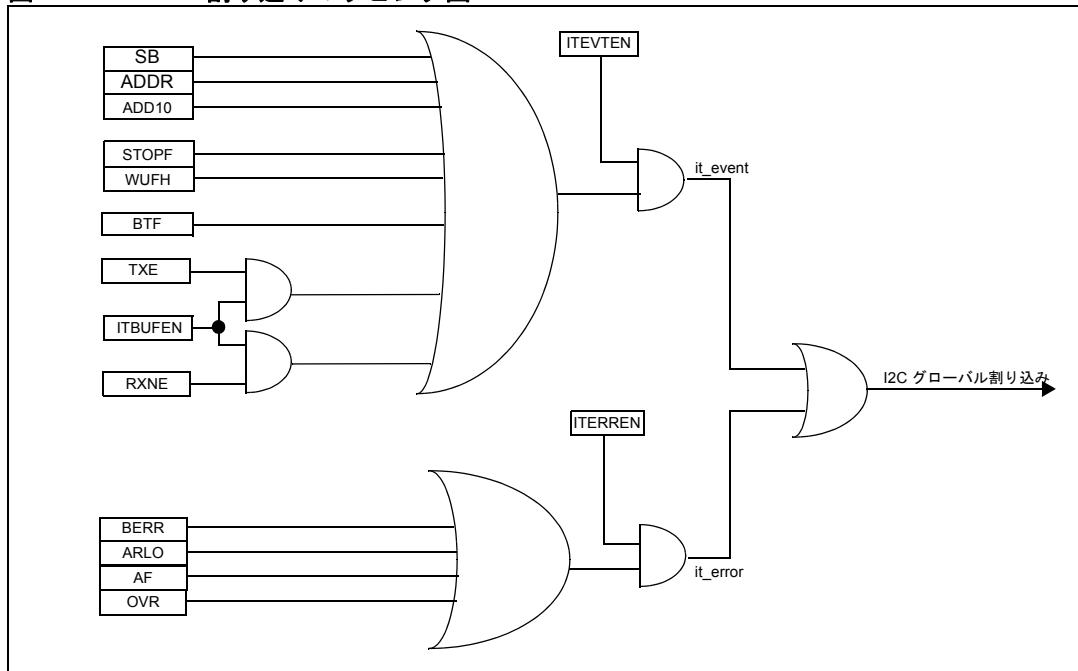

| 図 72. | SPI のブロック図                                                    | 192 |

| 図 73. | シングルマスタ／シングルスレーブアプリケーション                                      | 193 |

| 図 74. | データクロックのタイミング図                                                | 195 |

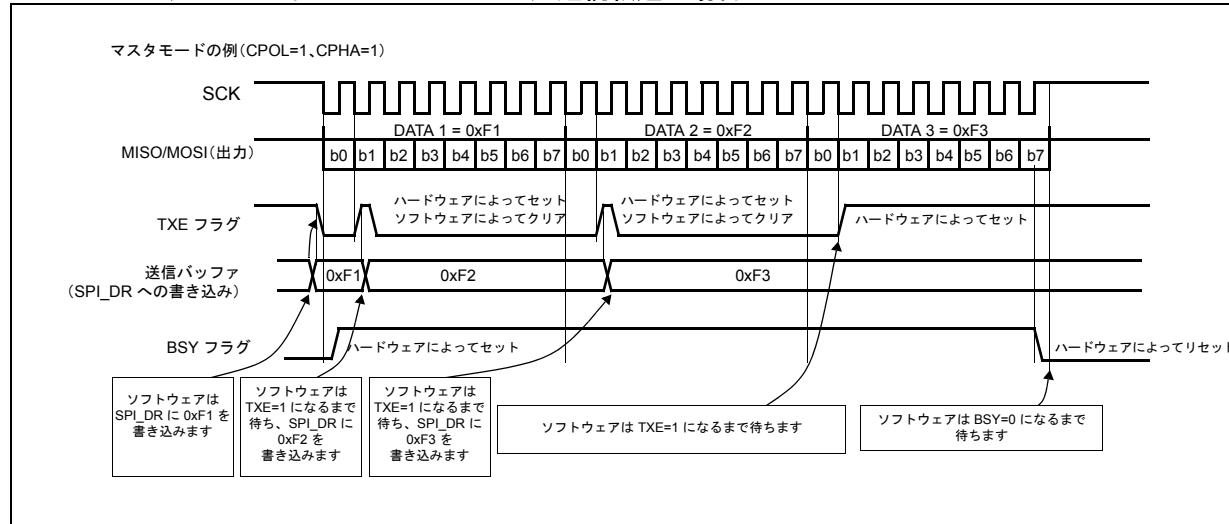

| 図 75. | 全二重モードでの TXE/RXNE/BSY 動作 (RXONLY = 0) 連続転送の場合                 | 200 |

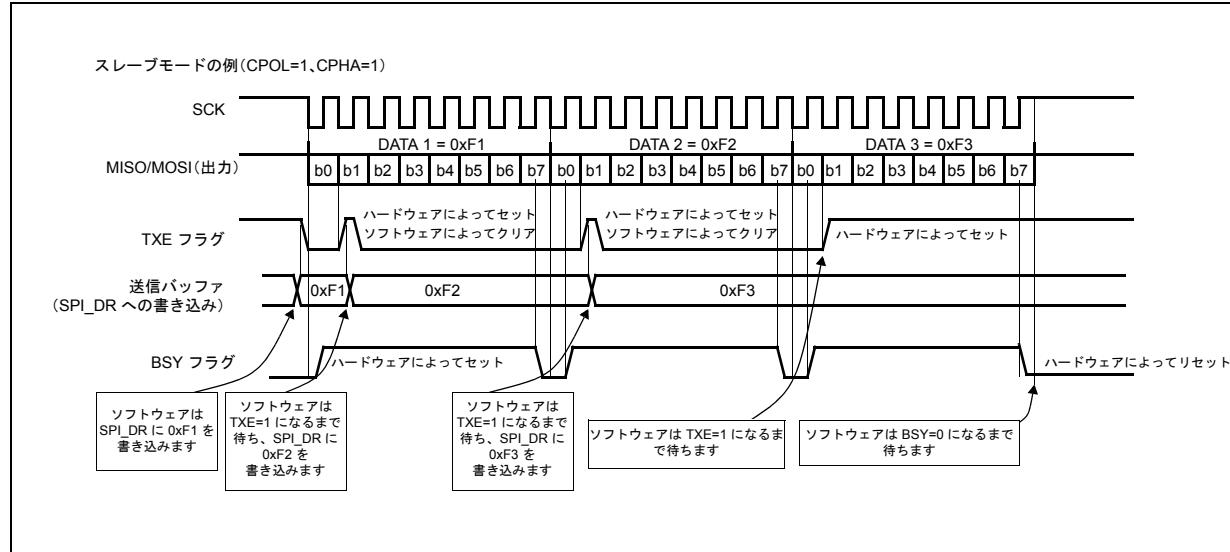

| 図 76. | スレーブ／全二重モードでの TXE/RXNE/BSY 動作 (BDM = 0、RXONLY = 0)<br>連続転送の場合 | 200 |

| 図 77. | マスタ送信専用モードでの TXE/BSY 動作 (BDM = 0 および RXONLY = 0) 連続転送の場合      | 201 |

| 図 78. | スレーブ送信専用モードでの TXE/BSY 動作 (BDM = 0 および RXONLY = 0) 連続転送の場合     | 202 |

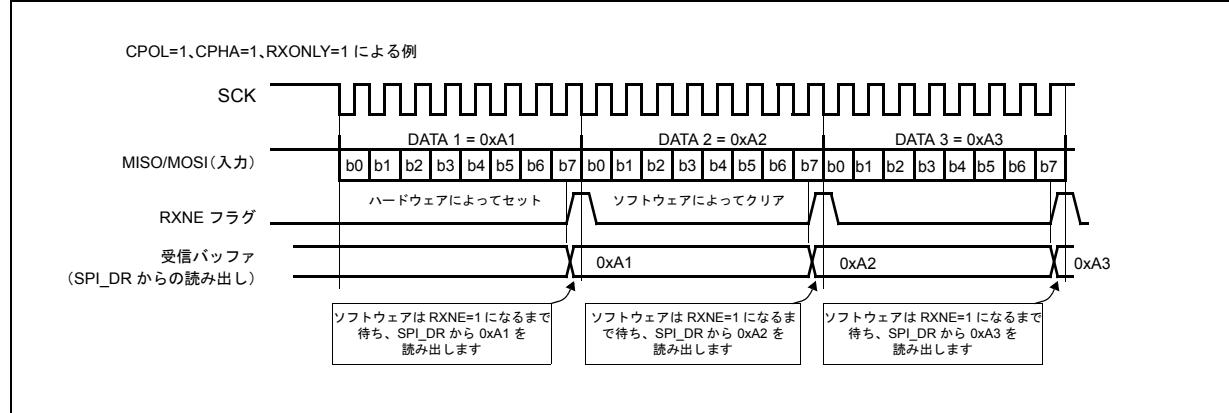

| 図 79. | 受信専用モードでの RXNE 動作 (BDM = 0 および RXONLY = 1)<br>連続転送の場合         | 203 |

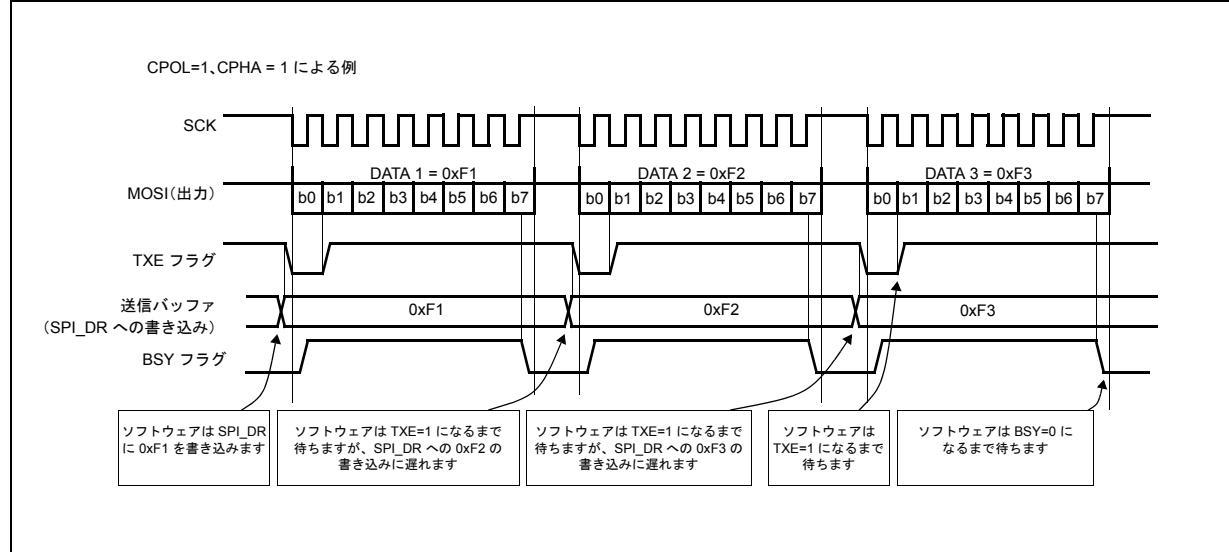

| 図 80. | 送信時の TXE/BSY 動作 (BDM = 0 および RXONLY = 0) 不連続転送の場合             | 204 |

| 図 81. | USART のブロック図                                                  | 215 |

| 図 82. | ワード長のプログラミング                                                  | 216 |

| 図 83. | 設定可能な STOP ビット                                                | 217 |

| 図 84. | 送信時の TC/TXE の動作                                               | 219 |

| 図 85. | START ビットの検出                                                  | 220 |

| 図 86. | ノイズ検出のためのデータサンプリング                                            | 221 |

| 図 87. | BRR レジスタで USART_DIV をコード化する方法                                 | 223 |

| 図 88. | アイドルライン検出を使用したミュートモード                                         | 226 |

| 図 89. | アドレスマーク検出を使用したミュートモード                                         | 227 |

| 図 90. | USART の同期送信の例                                                 | 228 |

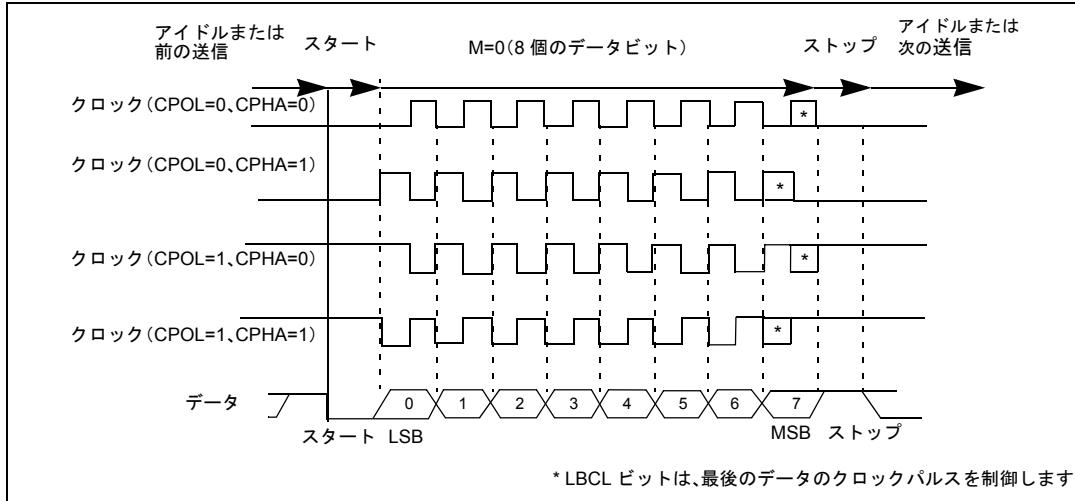

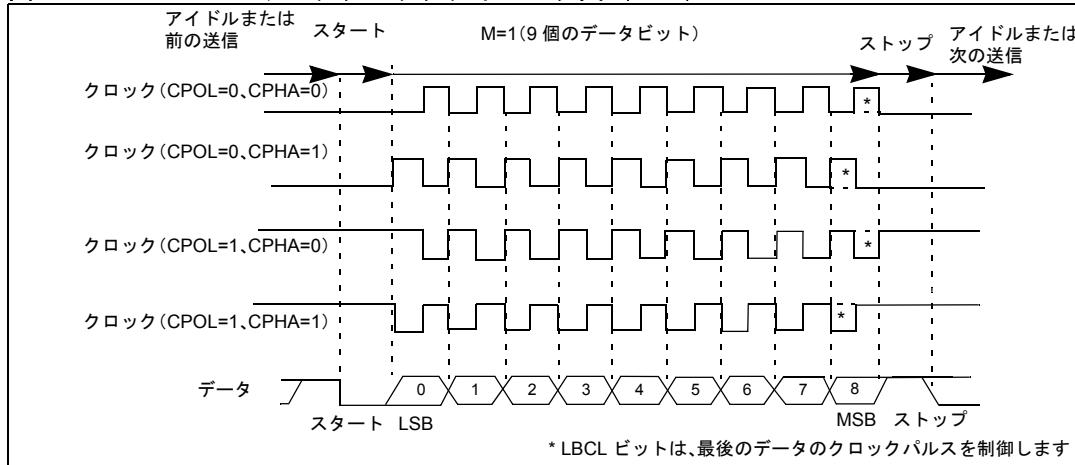

| 図 91. | USART データクロックタイミング図 (M=0)                                     | 229 |

| 図 92. | USART データクロックタイミング図 (M=1)                                     | 229 |

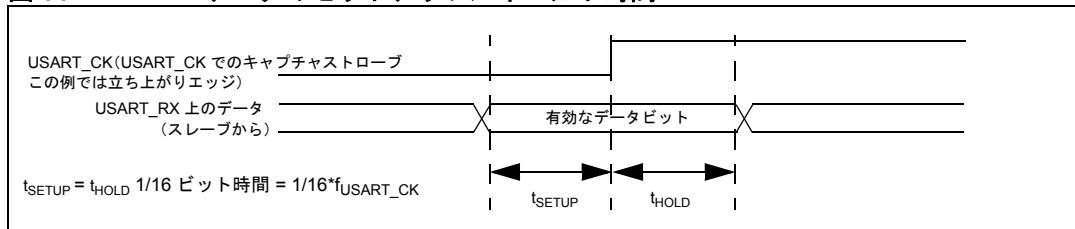

| 図 93. | RX データのセットアップ／ホールド時間                                          | 229 |

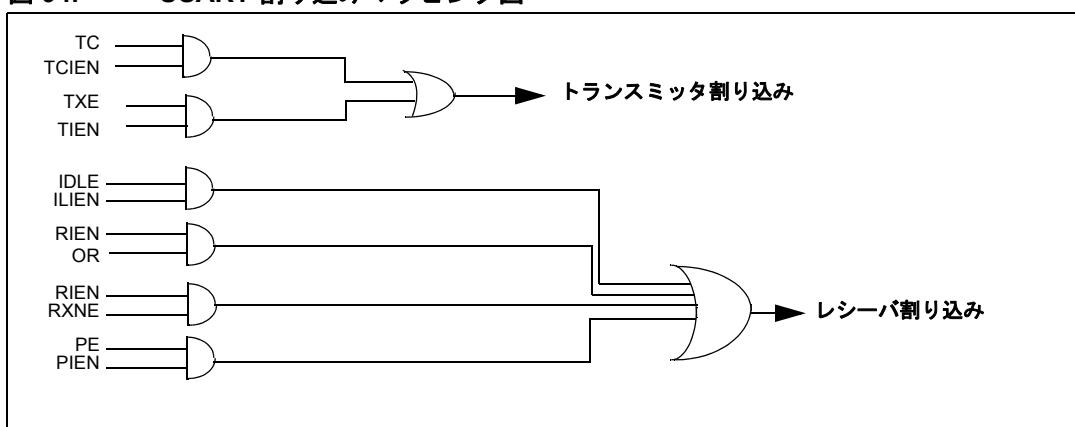

| 図 94. | USART 割り込みマッピング図                                              | 230 |

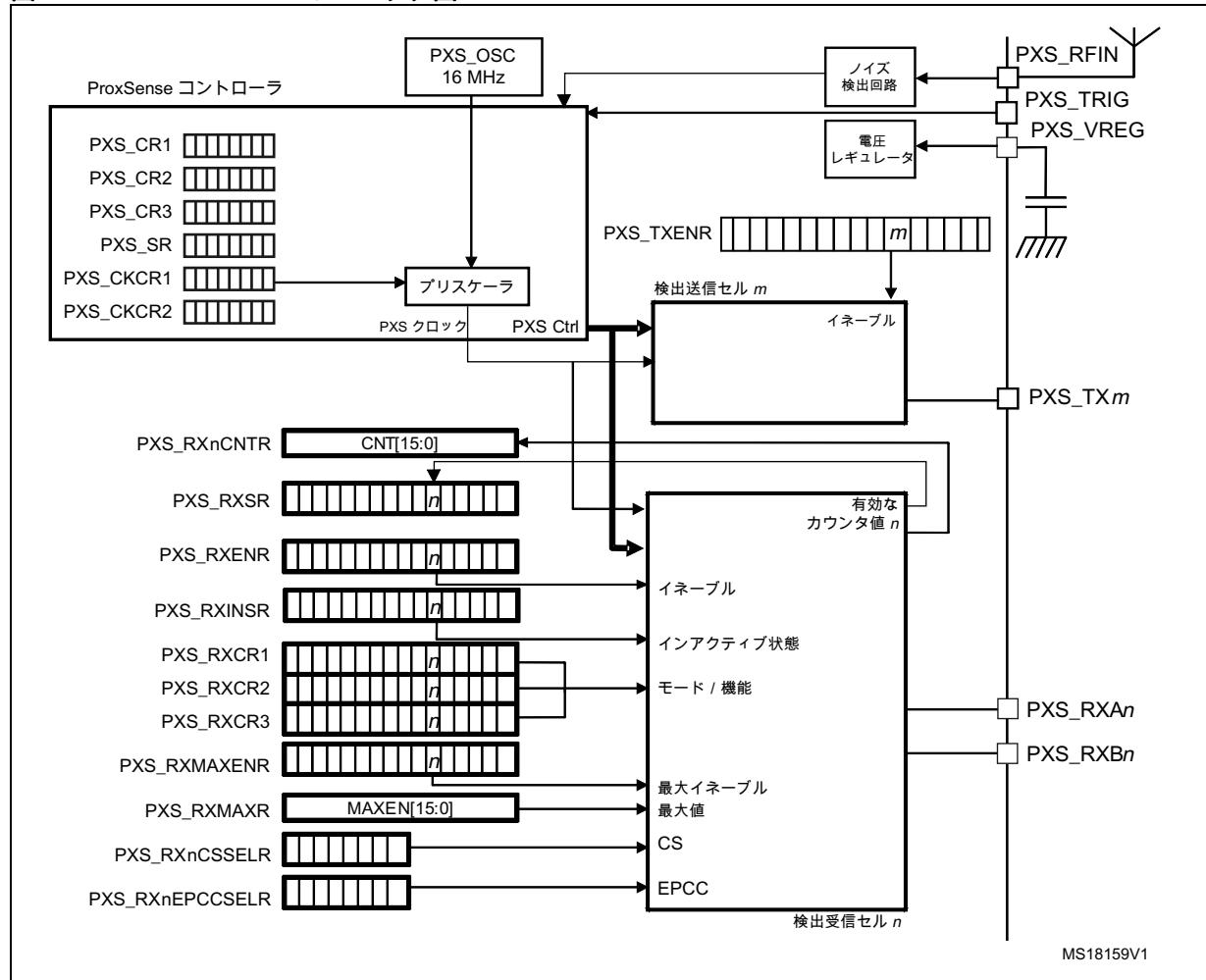

| 図 95. | ProxSense のブロック図                                              | 240 |

### 1 メモリおよびレジスタマップ

メモリマップ、I/O ポートハードウェアレジスタマップ、および CPU/SWIM/デバッグモジュール/割り込み制御レジスタの詳細については、製品データシートを参照してください。

#### 1.1 レジスタの説明の略語

このリファレンスマニュアルの各章のレジスタの説明では、以下の略語が使用されています。

表 1. 略語一覧

| 略語                     | 説明                                                                             |

|------------------------|--------------------------------------------------------------------------------|

| 読み出し/書き込み (rw)         | ソフトウェアは、これらのビットの読み出し/書き込みができます。                                                |

| 読み出し専用 (r)             | ソフトウェアは、これらのビットの読み出しのみが可能です。                                                   |

| 書き込み専用 (w)             | ソフトウェアは、このビットへの書き込みのみが可能です。ビットを読み出した場合、意味のない値が返されます。                           |

| 読み出し/1回書き込み (rwo)      | ソフトウェアは、このビットに1回だけ書き込むことができますが、読み出しありでも可能です。このビットをリセット値に戻すには、リセットする必要があります。    |

| 読み出し/クリア (rc_w1)       | ソフトウェアは、このビットを読み出すことができ、1を書き込むことによってクリアできます。“0”を書き込んでも、ビットの値は変化しません。           |

| 読み出し/クリア (rc_w0)       | ソフトウェアは、このビットを読み出すことができ、0を書き込むことによってクリアできます。“1”を書き込んでも、ビットの値は変化しません。           |

| 読み出し/セット (rs)          | ソフトウェアは、このビットの読み出しとセットを行うことができます。“0”を書き込んでも、ビットの値は変化しません。                      |

| 読み出し/読み出しによるクリア (rc_r) | ソフトウェアは、このビットを読み出すことができます。このビットを読み出すと、自動的に“0”にクリアされます。“0”を書き込んでも、ビットの値は変化しません。 |

| 予約済み (Res.)            | 予約済みのビットであり、リセット値のままにしておかなければなりません。                                            |

## 2 中央演算処理装置 (CPU)

### 2.1 概要

この CPU は 8 ビットアーキテクチャを採用しています。6 つの内部レジスタにより効率的なデータ処理が可能です。この CPU は 80 個の基本命令を実行することができます。20 通りのアドレスモードをサポートし、6 つの内部レジスタを指定することができます。命令セットの詳しい説明については、STM8 マイクロコントローラファミリプログラミングマニュアル (PM0044) を参照してください。

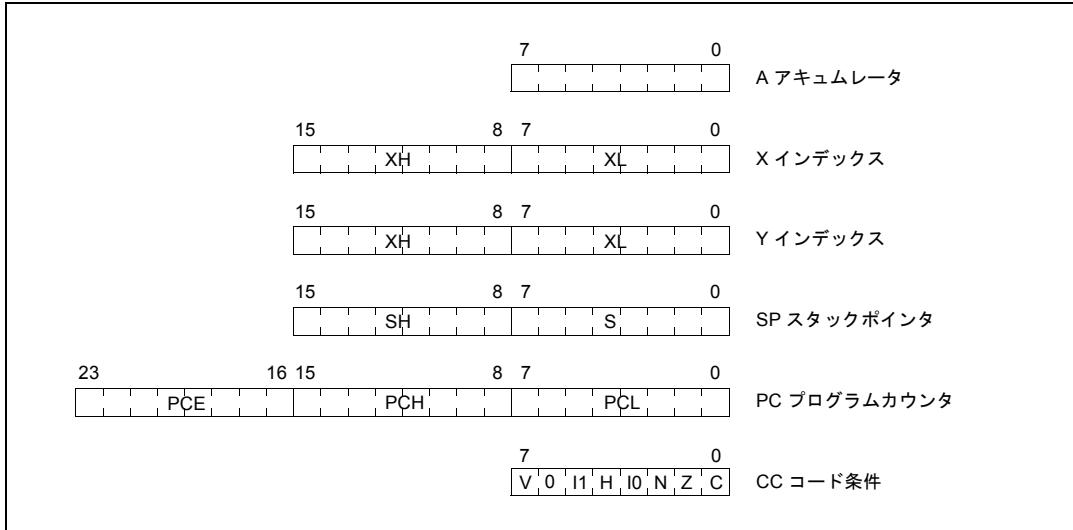

### 2.2 CPU レジスタ

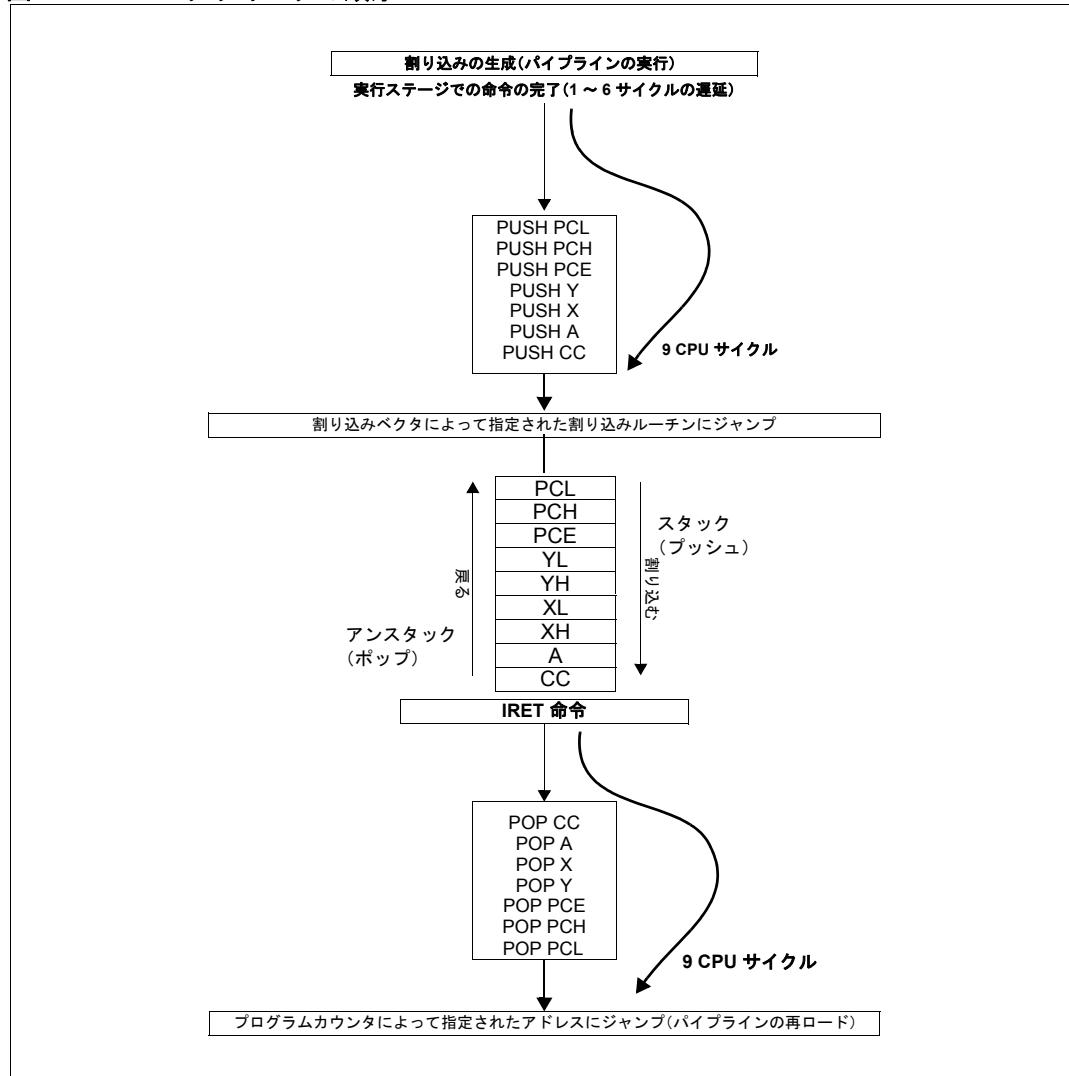

6 つの CPU レジスタが [図 1](#) のプログラミングモデルに示されています。割り込みの後、レジスタは [図 2](#) に示されている順序でスタックにプッシュされます。逆の順序でスタックからポップされます。したがって、割り込みルーチンは必要に応じて、POP および PUSH 命令を使って処理する必要があります。

#### 2.2.1 CPU レジスタの説明

##### アキュムレータ (A)

アキュムレータは、オペランドと算術演算および論理演算の結果に加えて、データ操作の結果を保持するために使用される 8 ビットの汎用レジスタです。

##### インデックスレジスタ (X および Y)

これらは、有効なアドレスを作成するために使用される 16 ビットのレジスタです。また、データ操作のための一時的なストレージ領域としても使用され、特定の命令（乗算／除算）のために本来使用されるメモリとしての役割も持っています。ほとんどの場合、後続の命令が Y レジスタを参照することを示すために、クロスアセンブラーは PRECODE 命令 (PRE) を生成します。

##### プログラムカウンタ (PC)

プログラムカウンタは、CPU によって実行される次の命令のアドレスを格納するために使用される 24 ビットのレジスタです。各命令が処理された後、自動的にリフレッシュされます。その結果、STM8 コアは最大 16 MB のメモリにアクセスできます。

図 1. プログラミングモデル

### スタックポインタ (SP)

スタックポインタは、16 ビットのレジスタです。スタックの次の空き位置のアドレスを含みます。製品によって異なりますが、最上位ビットを強制的にプリセット値に設定できます。

スタックは、サブルーチンコールまたは割り込み時に CPU コンテキストを保存するために使用されます。ユーザは、POP および PUSH 命令を使って直接使用することもできます。

スタックポインタは、C コンパイラで提供されるスタートアップ関数によって初期化できます。C 言語で書かれたアプリケーションの場合、初期化は、C ユーザ用リンクファイルで指定されたアドレスに従って実行されます。ユーザ固有のリンクファイルまたはスタートアップファイルを使用する場合は、スタックポインタが正しく（データシートに示されているアドレスで）初期化されていることを確認してください。アセンブラーで書かれたアプリケーションの場合、ST によって提供されるスタートアップ機能を使用するか、正しいアドレスでスタックポインタを初期化することによってユーザ独自のスタートアップ機能をプログラムすることができます。

スタックポインタは、データがスタックにプッシュされるとデクリメントされ、スタックからポップされるとインクリメントされます。アプリケーションでは、下限値を超えないようにする必要があります。

サブルーチンコールは、2 つまたは 3 つのスタックを占有します。割り込みは、すべての内部レジスタ（SP を除く）を保存するために、9 つのスタックを占有します。詳細については、図 2 を参照してください。

**注：** WFI/HALT 命令は、コンテキストを事前に保存します。CPU がこれらのモードにあるときに割り込みが発生した場合、遅延は小さくなります。

図 2. スタッキングの順序

## 条件コードレジスタ (CC)

条件コードレジスタは、実行直後の命令の結果とプロセッサの状態を示す 8 ビットのレジスタです。このレジスタの第 6 ビット (MSB) は予約済みです。これらのビットは、プログラムによって個別にテストでき、その状態の結果としてとられるアクションを指定できます。各ビットについて、以下に説明します。

- V : オーバーフロー

セットされたとき、V は、最後の符号付き算術演算中に MSB 結果ビットのオーバーフローが発生したことを示します。INC、INCW、DEC、DECW、NEG、NEGW、ADD、ADDW、ADC、SUB、SUBW、SBC、CP、および CPW 命令を参照してください。

- I1 : 割り込みマスクレベル 1

I1 フラグは、表 2 に示されているように、I0 フラグとともに現在の割り込み可能レベルを定義します。これらのフラグは、RIM、SIM、HALT、WFI、IRET、TRAP、および POP 命令を使って、ソフトウェアによってセット／クリアでき、割り込みサービスルーチンに入ったときにハードウェアによって自動的にセットされます。

# 参考資料

表 2. 割り込みレベル

| 割り込み可能      | 優先度 | I1 | I0 |

|-------------|-----|----|----|

| 割り込み可能メイン   | 最低  | 1  | 0  |

| 割り込み可能レベル 1 |     | 0  | 1  |

| 割り込み可能レベル 2 |     | 0  | 0  |

| 割り込み不可      | 最高  | 1  | 1  |

● H : ハーフキャリービット

H ビットは、ADD または ADC 命令の実行中に ALU のビット 3 とビット 4 の間で桁上げが発生したときに 1 にセットされます。H ビットは、BCD 算術演算サブルーチンで役立ちます。

● I0 : 割り込みマスクレベル 0

フラグ I1 を参照してください。

● N : ネガティブ

1 にセットされた場合、このビットは、最後の算術演算、論理演算、またはデータ操作の結果が負である（すなわち、最上位ビットが論理 1 である）ことを示します。

● Z : ゼロ

1 にセットされた場合、このビットは、最後の算術演算、論理演算、またはデータ操作の結果がゼロであることを示します。

● C : 桁上げ

セットされた場合、C は、最後の算術演算中に MSB 演算結果ビットで ALU の桁上げまたは桁下げが発生したことを示します。このビットは、ビットテスト、ブランチ、シフト、ローテート、およびロード命令中にも影響されます。ADD、ADC、SUB、および SBC 命令を参照してください。

除算演算では、C は、実行中に問題（商のオーバーフロー、ゼロでの除算）が発生したかどうかを示します。DIV 命令を参照してください。

ビットテスト演算では、C は、テストされたビットのコピーです。BTJF および BTJT 命令を参照してください。

シフトおよびローテート演算では、桁上げは更新されます。RRC、RLC、SRL、SLL、および SRA 命令を参照してください。

このビットは、SCF、RCF、および CCF 命令を使用して、ソフトウェアによってセット、リセット、または補数化できます。

## 例：加算

$$\$B5 + \$94 = "C" + \$49 = \$149$$

|     |                 |   |

|-----|-----------------|---|

| C   | 7               | 0 |

| 0   | 1 0 1 1 0 1 0 1 |   |

| C   | 7               | 0 |

| + 0 | 1 0 0 1 0 1 0 0 |   |

| C   | 7               | 0 |

| = 1 | 0 1 0 0 1 0 0 1 |   |

## 2.2.2 STM8 CPU レジスタマップ

CPU レジスタは、[表 3](#) に示されているように、STM8 アドレス空間に配置されます。これらのレジスタは、デバッグモジュールからのみアクセスでき、コアで実行されるメモリアクセス命令によってアクセスすることはできません。

表 3. CPU レジスタマップ

| アドレスオフセット | レジスタ名 | 7   | 6 | 5  | 4 | 3  | 2 | 1 | 0   |

|-----------|-------|-----|---|----|---|----|---|---|-----|

| 0x00      | A     | MSB | - | -  | - | -  | - | - | LSB |

| 0x01      | PCE   | MSB | - | -  | - | -  | - | - | LSB |

| 0x02      | PCH   | MSB | - | -  | - | -  | - | - | LSB |

| 0x03      | PCL   | MSB | - | -  | - | -  | - | - | LSB |

| 0x04      | XH    | MSB | - | -  | - | -  | - | - | LSB |

| 0x05      | XL    | MSB | - | -  | - | -  | - | - | LSB |

| 0x06      | YH    | MSB | - | -  | - | -  | - | - | LSB |

| 0x07      | YL    | MSB | - | -  | - | -  | - | - | LSB |

| 0x08      | SPH   | MSB | - | -  | - | -  | - | - | LSB |

| 0x09      | SPL   | MSB | - | -  | - | -  | - | - | LSB |

| 0x0A      | CC    | V   | 0 | I1 | H | I0 | N | Z | C   |

## 2.3 グローバル設定レジスタ (CFG\_GCR)

### 2.3.1 起動レベル

MCU 起動レベルは、CFG\_GCR レジスタの AL ビットをプログラムすることによって設定されます。

このビットの詳細については、[セクション 5.4 : 起動レベル／低電力モードの制御 \(45 ページ\)](#) を参照してください。

### 2.3.2 SWIM ディセーブル

デフォルトでは、MCU リセット後、SWIM ピンは、デバッグ用またはフラッシュ／EEPROM プログラミング用の外部ツールとの通信ができるように設定されます。このピンをアプリケーションによって汎用 I/O として使用できるように設定できます。このためには、CFG\_GCR レジスタの SWD ビットをセットします。

### 2.3.3 グローバル設定レジスタ (CFG\_GCR) の説明

アドレスオフセット : 0x00

リセット値 : 0x00

| 7    | 6 | 5 | 4 | 3 | 2 | 1  | 0   |

|------|---|---|---|---|---|----|-----|

| 予約済み |   |   |   |   |   | AL | SWD |

|      |   |   |   |   |   | rw | rw  |

ビット 7:2 予約済み

ビット 1 AL : 起動レベル

このビットは、ソフトウェアによってセット／クリアされます。メインまたは割り込み専用起動レベルを設定します。

0 : メイン起動レベル。IRET 命令があると、スタックからコンテキストが取り出され、メインプログラムは WFI 命令後から続行します。

1 : 割り込み専用起動レベル。IRET 命令があると、CPU はコンテキストを復元せずに、WFI/HALT モードに戻ります。

ビット 0 SWD : SWIM ディセーブル

0 : SWIM モードは有効です。

1 : SWIM モードは無効です。

SWIM モードが有効なときには、SWIM ピンを汎用 I/O として使用することはできません。

### 2.3.4 グローバル設定レジスタマップとリセット値

CFG\_GCR は、STM8 アドレス空間に配置されます。ベースアドレスについては、対応するデータシートを参照してください。

表 4. CFG\_GCR レジスタマップ

| アドレスオフセット | レジスタ名            | 7      | 6      | 5      | 4      | 3      | 2      | 1       | 0        |

|-----------|------------------|--------|--------|--------|--------|--------|--------|---------|----------|

| 0x00      | CFG_GCR<br>リセット値 | -<br>0 | -<br>0 | -<br>0 | -<br>0 | -<br>0 | -<br>0 | AL<br>0 | SWD<br>0 |

## 3 シングルワイヤインタフェースモジュール (SWIM) およびデバッグモジュール (DM)

### 3.1 概要

インサーキットデバッグモードまたはインサーキットプログラミングモードは、超高速のメモリプログラミング機能を備えたシングルワイヤハードウェアインタフェースを通じて管理されます。インサーキットデバッグモジュールとの組み合わせによって非侵入型エミュレーションモードも提供し、インサーキットデバッガをフル装備のエミュレータに近い性能の、非常に強力なツールにします。

### 3.2 主な特長

- 非同期の大電流シンク (8 mA)、オープンドレイン、双方向通信。

- メモリ空間のどの部分でも読み出しありまたは書き込みが可能です。

- CPU レジスタ (A, X, Y, CC, SP) へのアクセスが可能です。読み出しありまたは書き込みアクセスについてメモリマッピングされます。

- RAM およびペリフェラルレジスタへの非侵入型の迅速な読み出しあり/書き込みが可能です。

- [リセットステータスレジスタ \(RST\\_SR\)](#) のステータスフラグによるデバイスリセット機能。

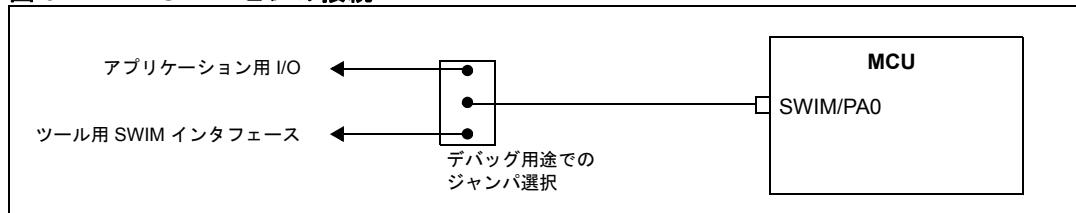

SWIM ピンは、標準 I/O として使用でき、デバッグ用途で使いたい場合は、いくつかの制約があります。最も安全な方法は、PCB でストラップオプションを提供することです。

図 3. SWIM ピンの接続

### 3.3 SWIM モード

パワーオンリセット後、SWIM はリセットされ、OFF モードに入ります。

1. **OFF** : パワーオンリセット後のデフォルト状態。SWIM ピンは、アプリケーションが I/O として使用することはできません。

2. **I/O** : [グローバル設定レジスタ \(CFG\\_GCR\)](#) の SWD ビットに書き込むことによって、ソフトウェアによってこの状態になります。この状態では、アプリケーションは SWIM を標準 I/O ピンとして使用できます。リセットの場合、SWIM は OFF モードに戻ります。

3. **SWIM** : SWIM ピンに対して特定のシーケンスが実行されると、この状態になります。この状態では、SWIM ピンは、ホストツールによって STM8 を 3 つのコマンド (SRST システムリセット、ROTF 実行時読み出し、WOTF 実行時書き込み) で制御するために使用されます。

注 : [SWIM およびデバッグモジュール \(DM\) について](#)は、[STM8 SWIM 通信プロトコルおよびデバッグモジュールユーザマニュアル](#)を参照してください。[グローバル設定レジスタ \(CFG\\_GCR\) の説明 \(24 ページ\)](#) も参照してください。

## 4 フラッシュプログラムメモリとデータ EEPROM

### 4.1 概要

内蔵のフラッシュプログラムメモリとデータ EEPROM は、共通のレジスタセットによって制御されます。これらのレジスタを使用して、アプリケーションは、メモリ内容をプログラムまたは消去したり、書き込み保護を設定することができます。アプリケーションは、デバイスのオプションバイトをプログラムすることもできます。

### 4.2 用語

- ブロック

ブロックとは、1回のプログラミング操作で一括プログラムまたは一括消去できるバイトのセットです。ブロック単位で実行される操作は、標準のプログラミングおよび消去より高速に実行されます。ブロックサイズの詳細については、[表 5](#) を参照してください。

- ページ

ページとは、ブロックのセットです。

専用オプションバイトを使用して、ユーザブートコード、データ EEPROM、および独自仕様コードのサイズを1ページ単位で設定できます。

### 4.3 メインフラッシュメモリの機能

- STM8TL5xxx タッチセンシングデバイス用の EEPROM は、2つのメモリ配列に分けられます (メモリマッピングの詳細については、[セクション 4.4 : メモリ構成](#) を参照)。

- 最大 16 KB の組み込みフラッシュプログラムメモリ (最大 2 KB のデータ EEPROM を含む)。データ EEPROM およびフラッシュプログラムメモリ領域は、メモリアクセスセキュリティシステム (MASS) を使用して、個別に書き込み保護することができます。

- 64 バイトのオプションバイト (1 ブロック) : そのうち 5 バイトはすでにデバイス用に使用されています。

- プログラミングモード

- バイトプログラミングと自動高速バイトプログラミング (消去操作なし)

- ワードプログラミング

- ブロックプログラミングおよび高速ブロックプログラミングモード (消去操作なし)

- プログラム／消去操作の終了時と不正プログラム操作時の割り込み生成。

- アプリケーション内プログラミング (IAP) およびインサーキットプログラミング (ICP) 機能

- 保護機能

- メモリ読み出し保護 (ROP)

- メモリアクセスセキュリティシステムによるプログラムメモリの書き込み保護 (MASS キー)

- メモリアクセスセキュリティシステムによるデータメモリの書き込み保護 (MASS キー)

- プログラマブルな、書き込み保護されたユーザブートコード領域 (UBC)

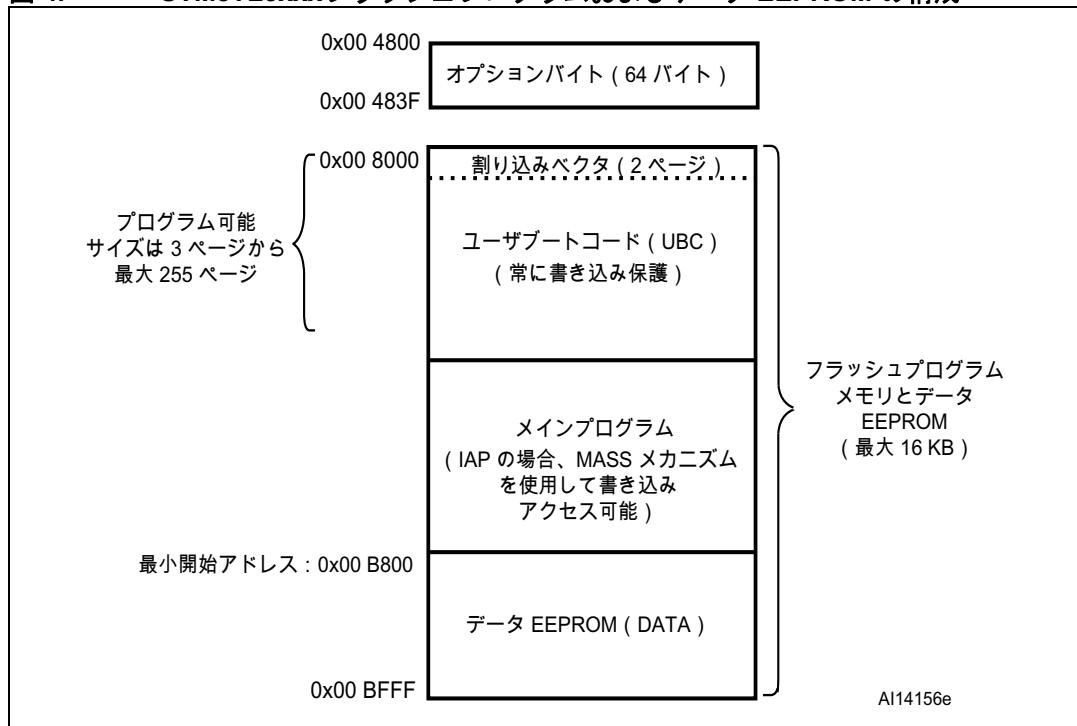

## 4.4 メモリ構成

STM8TL5xxx タッチセンシングフラッシュプログラムメモリは、ページ単位（1 ページあたり 64 バイト）で分割すると 256 ページになり、32 ビットワード（1 ワードあたり 4 バイト）で構成されます。

メモリ配列は、4 つの領域に分けられます。

- 独自仕様コード領域（PCODE）

- ユーザブートコード領域（UBC）

- メインプログラム領域

- データ EEPROM（DATA）

フラッシュプログラムメモリ（アドレス 0x00 8000 から開始）の最初の 2 ページは、割り込みベクタを含みます。

デバイスは、別のメモリ配列に 1 ブロックのオプションバイト（64 バイト）も備えています。

メモリ構成については、[図 4](#) を参照してください。

図 4. STM8TL5xxx フラッシュプログラムおよびデータ EEPROM の構成

### 4.4.1 独自仕様コード領域 (PCODE)

独自仕様コード領域 (PCODE) は、ペリフェラルを駆動する独自仕様ソフトウェアライブラリを保護するために使用できます。

PCODE 領域のサイズは、ICP モードで (SWIM インタフェースを使用して) PCODE オプションバイト (PCODESIZE) によって設定できます。このオプションバイトは、アドレス 0x00 8000 から始まる PCODE 領域に割り当てるページ数 (64 バイト単位) を指定します。PCODE オプションバイトは一度プログラムされると、消去できなくなり、PCODE 領域のサイズは固定されます。

PCODESIZE に値 3 が設定されているとき、PCODE 領域の最小実効サイズは、アドレス 0x8080 から 0x80BF までの 1 ページです。PCODE 領域の最大サイズは、アドレス 0x00 8080 から 0x00 BFBF までの 253 ページです (PCODESIZE が 0xFF のとき)。この場合、メインプログラム領域用またはデータ EEPROM 用に使えるのは 1 ページのみです。PCODE が有効である間、TRAP 割り込みベクタは書き込み保護されます。

PCODE 領域は、TRAP 割り込みベクタを除き、自動的に読み出し保護されます ([セクション 4.5.1: 読み出し保護](#) を参照)。読み出し保護は、この領域内では無効にできません。これは、PCODE の内容を読み出したり、変更できないことを意味します。

PCODE 領域は、TRAP ベクタを通してのみアクセスできます。

### 4.4.2 ユーザブート領域 (UBC)

ユーザブート領域 (UBC) は、リセットベクタおよび割り込みベクタ群を含みます。IAP および通信ルーチンを格納するために使用できます。UBC 領域は、IAP プログラミング中の意図しない消去や変更を防ぐために、第 2 レベルの保護対策が施されています。これは、常に書き込み保護され、MASS キーを使用して書き込み保護をロック解除できないことを意味します。

UBC 領域のサイズは、UBC オプションバイトを読み出すことによって確認できます。

UBC 領域のサイズは、ICP モードで (SWIM インタフェースを使用して) UBC オプションバイトによって設定できます。UBC オプションバイトは、アドレス 0x00 8000 から始まる UBC 領域に割り当てるページ数を指定します。

UBC 領域の最小実効サイズは 3 ページであり、そのうち 2 ページは割り込みベクタを格納するため使用されます。

**注:** *PCODE 領域が定義されているとき、UBC の最小サイズは PCODESIZE+1 となります。UBC 領域内でブートコードの格納に使用できる部分は、PCODE 領域の終端と定義済み UBC 領域の終端との間に位置する領域です。*

ブート領域の最大サイズは 255 ページであり、アドレス範囲は 0x00 8000 から 0x00 BFBF です (割り込みベクタを含む)。この場合、メインプログラム領域用またはデータ EEPROM 用に使えるのは 1 ページのみです。

UBC 領域のメモリマッピングの説明については [図 5](#) を、UBC オプションバイトの詳細については、データシートのオプションバイトのセクションを参照してください。

図 5. タッチセンシング STM8TL5xxx デバイスの UBC 領域サイズの定義

1. UBC[7:0]= 0x00 は、UBC 領域にメモリ空間が割り当てられないことを意味します。

2. ページ 255 は、メインプログラム領域またはデータ EEPROM 用に予約済みです。

#### 4.4.3 データ EEPROM (DATA)

データ EEPROM 領域は、アプリケーションデータを格納するために使用できます。初期状態で、データ領域は、IAP モードでメインプログラムを更新する際の意図しない変更を防ぐため、書き込み保護されています。書き込み保護は、特定の MASS キーシーケンスを使用することによってのみロック解除できます（[データ領域への書き込みアクセスの有効化](#)を参照）。

データ領域のサイズは、ICP モードで DATA オプションバイト (DATASIZE) によって設定できます。このオプションバイトは、アドレス 0x00 BFFF から下位アドレスに向かって連なるページ数 (1 ページあたり 64 バイト) を指定します。

データ領域の最大サイズは 2 KB であり、開始アドレス 0x00 B800 に対応します（[図 4](#) を参照）。つまり、最大 32 ページの 64 バイトをデータ EEPROM として定義できます。

#### 4.4.4 メインプログラム領域

メインプログラム領域は、UBC または PCODE の終わりから始まり、アドレス 0x00 BFFF で終わります。アプリケーションコードを格納するために使用できます（[図 4](#) を参照）。

#### 4.4.5 オプションバイト

オプションバイトは、デバイスハードウェア機能とメモリ保護を設定するために使用されます。1 ブロックの専用メモリ配列にあります。

オプションバイトは、FLASH\_CR2 レジスタの OPT ビットに 1 をセットして、ICP/SWIM モードでのみ変更できます（[セクション 4.8.2 : フラッシュ制御レジスタ 2 \(FLASH\\_CR2\)](#) を参照）。

オプションバイトの詳細については、データシートのオプションバイトのセクションを、プログラミングの詳細については、STM8 SWIM プロトコルおよびデバッグモジュールユーザマニュアル (UM0470) を参照してください。

## 4.5 メモリ保護

### 4.5.1 読み出し保護

読み出し保護は、ROP オプションバイトを 0xAA にプログラミングすることによって選択されます。読み出し保護が有効なときには、ICP モード (SWIM インタフェースを使用) でのフラッシュプログラムメモリおよびデータ領域の読み出しと変更は、書き込み保護の設定とは関係なく禁止されます。

絶対に打ち破れない保護とは言えないまでも、読み出し保護機能は、汎用マイクロコントローラに対して非常に高いレベルの保護を提供します。

読み出し保護機能は、ICP モードで ROP オプションバイトをプログラミングすることによって、プログラムメモリ、UBC、PCODE、およびデータ領域について無効にできます。この場合、フラッシュプログラムメモリ、データ領域、およびオプションバイトは自動的に消去され、デバイスの再プログラムを行うことができます。

初期状態で、PCODE 領域は、割り込みベクタ TRAP を除いて、常に読み出し保護されます ([セクション 4.4.1 : 独自仕様コード領域 \(PCODE\)](#) を参照)。

読み出し保護が有効または無効なときのメモリアクセスの詳細については、[表 6 : メモリアクセスとプログラミング方法](#) を参照してください。

### 4.5.2 メモリアクセスセキュリティシステム (MASS)

リセット後、メインプログラムおよびデータ領域（存在する場合）は、意図しない書き込み操作に対して保護されます。内容の変更を試みる前に、ロック解除が必要があります。このロック解除メカニズムは、メモリアクセスセキュリティシステム (MASS) によって管理されます。

UBC オプションバイトで指定された UBC 領域は、常に書き込み保護されます ([セクション 4.4.2 : ユーザブート領域 \(UBC\)](#) を参照)。

メインプログラムおよびデータ領域の内容が破壊されないように、これらの内蔵不揮性メモリの内容を変更した後すぐに書き込み保護を再度有効にすることを推奨します。

#### メインプログラムメモリへの書き込みアクセスの有効化

デバイスのリセット後、MASS キーと呼ばれる 2 つの値を FLASH\_PUKR レジスタに連続して書き込むことによって、メインプログラムメモリの書き込み保護を無効にできます ([セクション 4.8.3 : フラッシュプログラムメモリ保護解除キーレジスタ \(FLASH\\_PUKR\)](#) を参照)。これらのプログラムキーは、次に 2 つのハードウェアキーと比較されます。

- 最初のハードウェアキー : 0b0101 0110 (0x56)

- 2 番目のハードウェアキー : 0b1010 1110 (0xAE)

メインプログラム領域の書き込み保護を無効にするには、以下の手順が必要です。

- 最初の 8 ビットキーを FLASH\_PUKR レジスタに書き込みます。このレジスタがリセット後に初めて書き込まれるときには、データバスの内容はレジスタにラッチされず、最初のハードウェアキーの値 (0x56) と比較されます。

- データバス上で使用可能なキーが正しくなかった場合、FLASH\_PUKR レジスタは、次のリセットまでロックされたままです。このアドレスに送信された新しい書き込みコマンドは破棄されます。

- FLASH\_PUKR レジスタが 2 回目に書き込まれたとき、最初のハードウェアキーが正しい場合、データバスの内容はレジスタにラッチされず、2 番目のハードウェアキーの値 (0xAE) と比較されます。

- データバス上で使用可能なキーが正しくなかった場合、プログラムメモリの書き込み保護は、次のリセットまでロックされたままです。このアドレスに送信された新しい書き込みコマンドは破棄されます。

- 2 番目のハードウェアキーが正しい場合、メインプログラムメモリの書き込み保護が解除され、FLASH\_IAPSR レジスタの PUL ビットに 1 がセットされます ([セクション 4.8.5 : フラッシュステータスレジスタ \(FLASH\\_IAPSR\)](#) レジスタを参照)。

プログラミングを開始する前に、アプリケーションは、PUL ビットに 1 が確実にセットされていることを確認する必要があります。アプリケーションはいつでも、PUL ビットをクリアすることによって、フラッシュプログラムメモリへの書き込みアクセスを再び無効にできます。

## データ領域への書き込みアクセスの有効化

デバイスのリセット後、MASS キーと呼ばれる 2 つの値を連続して FLASH\_DUKR レジスタに書き込むことによって、データ領域書き込み保護を無効にできます ([セクション 4.8.6 : フラッシュレジスタマップとリセット値](#) を参照)。これらのプログラムキーは、次に 2 つのハードウェアキーと比較されます。

- 最初のハードウェアキー : 0b1010 1110 (0xAE)

- 2 番目のハードウェアキー : 0b0101 0110 (0x56)

データ領域の書き込み保護を無効にするには、以下の手順が必要です。

- 最初の 8 ビットキーを FLASH\_DUKR レジスタに書き込みます。このレジスタがリセット後に初めて書き込まれるときには、データバスの内容はレジスタにラッチされず、最初のハードウェアキーの値 (0xAE) と比較されます。

- データバス上に存在するキーが正しくなかった場合、アプリケーションは、2 つの MASS キーを再入力することによって、データ領域の保護解除を試みることができます。

- 最初のハードウェアキーが正しい場合に、2 番目のキーを FLASH\_DUKR レジスタに書き込むと、データバスの内容は、やはりレジスタにラッチされず、2 番目のハードウェアキーの値 (0x56) と比較されます。

- データバス上で使用可能なキーが正しくなかった場合、データ EEPROM 領域は、次のリセットまで書き込み保護されたままです。このアドレスに送信された新しい書き込みコマンドは無視されます。

- 2 番目のハードウェアキーが正しい場合、データ領域の書き込み保護が解除され、FLASH\_IAPSR レジスタの DUL ビットに 1 がセットされます ([セクション 4.8.5 : フラッシュステータスレジスタ \(FLASH\\_IAPSR\)](#) を参照)。

プログラミングを開始する前に、アプリケーションは、DUL ビットに 1 が確実にセットされているかどうかを確認して、データ領域が書き込み保護されていないことを確かめる必要があります。アプリケーションはいつでも、DUL ビットをクリアすることによって、データ領域への書き込みアクセスを再び無効にできます。

### 4.6 メモリのプログラミング

メインプログラムメモリとデータ領域は、プログラム操作の実行を試みる前にロック解除する必要があります。ロック解除のメカニズムは、[セクション 4.5.2 : メモリアクセスセキュリティシステム \(MASS\)](#) で説明されているように、プログラムされるメモリ領域によって異なります。

**注 :** *PCODE 領域は、常に読み出し保護されています。PCODE 領域を再プログラムする唯一の方法は、ROP オプションバイトをリセットする方法ですが、フラッシュプログラムメモリ、データ領域、およびオプションバイトは消去されます。*

#### 4.6.1 バイトのプログラミング

メインプログラムメモリとデータ領域は、バイトレベルでプログラムできます。1バイトをプログラムするには、アプリケーションは、目的のアドレスに直接書き込みます。バイトプログラム操作の間、アプリケーションは停止します。

バイトを消去するには、対応するアドレスに 0x00 を書き込むだけです。

アプリケーションは、FLASH\_IAPSR レジスタを読み出すことによって、プログラミングまたは消去操作が正しく実行されたかどうかを確かめることができます。

- プログラミング操作が成功すると、EOP フラグがセットされます。

- ソフトウェアが保護されたページへの書き込みを試みると、WR\_PG\_DIS がセットされます。この場合、書き込み処理は実行されません。

FLASH\_CR1 レジスタの IE ビットをセットすることによって、前もってフラッシュ割り込みが有効にされていた場合、これらのフラグの 1 つがセットされると、フラッシュ割り込みが生成されます。

#### 自動高速バイトプログラミング

プログラミング時間は、目的アドレスの初期内容によって変わることがあります。プログラムされるバイトを含むワード (4 バイト) が空でない場合、プログラム操作の前にワード全体が自動的に消去されます。逆に、ワードが空の場合、消去操作は行われず、プログラミング時間は短くなります ([データシートの表「フラッシュプログラムメモリ」](#) の  $t_{PROG}$  を参照)。

ただし、FLASH\_CR1 レジスタの FIX ビットをセットすると、バイトの内容に関係なく、プログラム操作によってバイトの内容が強制的に消去されるので、プログラミング時間を固定できます ([セクション 4.8.1 : フラッシュ制御レジスタ 1 \(FLASH\\_CR1\)](#) を参照)。結果として、プログラミング時間は固定され、消去時間と書き込み時間の合計に等しくなります ([データシートの表「フラッシュプログラムメモリ」](#) の  $t_{PROG}$  を参照)。

**注 :** *バイト書き込みを高速で（消去なしで）行うには、書き込まれるワード全体の内容が、あらかじめ消去されていなければなりません。このため、同じワードに 2 回の高速書き込みを行う（2 番目の書き込みの前に消去を行わない）ことはできません。最初の書き込みは高速ですが、他のバイトへの 2 番目の書き込みでは消去が必要です。*

#### 4.6.2 ワードプログラミング

ワード書き込み操作では、4 バイトのワード全体を 1 回でプログラムできるので、プログラミング時間により速くできます。

バイトプログラミングと同様、ワード操作は、メインプログラムメモリとデータ EEPROM の両方にについて可能です。

ワードをプログラムするには、FLASH\_CR2 レジスタの WPRG ビットがあらかじめセットされていて、ワードプログラミングモードが有効になっている必要があります ([セクション 4.8.2 : フラッシュ制御レジスタ 2 \(FLASH\\_CR2\)](#) を参照)。次に、プログラムされるワードの 4 バイトが、最初のアド

レスからロードされなければなりません。プログラミングサイクルは、4 バイトが書き込まれた時点で自動的に開始します。

バイト操作と同様、FLASH\_IAPSR の EOP および WR\_PG\_DIS 制御フラグとフラッシュ割り込みを使用して、操作が正常に完了したかどうかを確認できます。

## 4.6.3 ブロックプログラミング

ブロックプログラム操作は、バイトやワードのプログラム操作よりもはるかに高速です。ブロックプログラム操作では、1 つのプログラミングサイクルでブロック全体がプログラムまたは消去されます。デバイスに応じたブロックサイズの詳細については、[表 5](#) を参照してください。

ブロック操作は、メインプログラムメモリとデータ領域の両方に対して実行可能です。ブロック操作は、完全に RAM から実行されます。

次の 3 つのブロック操作が可能です。

- ブロックプログラミング（標準ブロックプログラミングとも呼ばれます）：ブロックはプログラムされる前に自動的に消去されます。

- 高速ブロックプログラミング：事前の消去操作は行われません。

- ブロック消去

ブロックプログラミング中は、割り込みはハードウェアによってマスクされます。

### 標準ブロックプログラミング

標準ブロックプログラム操作では、1 回でブロック全体を書き込むことができます。ブロックは、プログラムの前に自動的に消去されます。

標準モードでブロック全体をプログラムするには、FLASH\_CR2 レジスタの PRG ビットがあらかじめセットされていて、標準ブロックプログラミングが有効になっている必要があります（[セクション 4.8.2 : フラッシュ制御レジスタ 2 \(FLASH\\_CR2\)](#) を参照）。次に、プログラムされるデータのブロックがメインプログラムメモリまたはデータ領域のデスティネーションアドレスに順にロードされなければなりません。これによって、データのすべてのバイトがラッチされます。ブロック全体のプログラミングを開始するには、データのすべてのバイトが書き込まれなければなりません。プログラミングシーケンスで書き込まれるすべてのバイトは、同じブロック内に存在していなければなりません。これは、同じ上位アドレスを持っていなければならないことを意味します。アドレスの最下位 6 ビットのみが変更可能です。目的ブロックの最後のバイトがロードされると、プログラミングは自動的に開始します。その前にブロック全体が自動的に消去されます。

FLASH\_IAPSR の EOP および WR\_PG\_DIS 制御フラグとフラッシュ割り込みを使用して、操作が正常に完了したかどうかを確認できます。

### 高速ブロックプログラミング

高速ブロックプログラミングでは、あらかじめメモリの内容を消去せずにプログラミングできます。したがって、高速ブロックプログラミングは標準プログラミングの 2 倍程度高速です。

このモードは、すでに消去された部分のプログラミングのみを目的としています。時間が節約できるので、空白部分を完全なアプリケーションコードでプログラムするときに役立ちます。

高速ブロックプログラミングは、標準ブロックプログラミングと同じシーケンスを使用して実行されます。高速ブロックプログラミングを有効にするには、FLASH\_CR2 レジスタの FPRG ビットが事前にセットされていなければなりません。

FLASH\_IAPSR レジスタの EOP および WR\_PG\_DIS ビットをチェックすることで、高速ブロックプログラミング操作が正常に完了したかどうかを確認できます。

**注：** 高速ブロックプログラミング操作の前にブロックが空白になっていない場合、そのブロックでプログラムされたデータは保証されません。

### ブロック消去

ブロック消去操作では、ブロック全体を消去できます。

ブロック全体を消去するには、FLASH\_CR2 レジスタの ERASE ビットがあらかじめセットされていて、ブロック消去が有効になっている必要があります（[セクション 4.8.2 : フラッシュ制御レジスタ 2 \(FLASH\\_CR2\)](#) を参照）。次に、ブロック内の任意のワードに '0x00 00 00 00' を書き込むことによってブロックが消去されます。ワードの開始アドレスは、'0'、'4'、'8'、または'C'で終わらなければなりません。

FLASH\_IAPSR の EOP および WR\_PG\_DIS 制御フラグとフラッシュ割り込みを使用して、操作が正常に完了したかどうかを確認できます。

表 5. ブロックサイズ

| STM8 マイクロコントローラファミリ | ブロックサイズ |

|---------------------|---------|

| STM8TL5xxx タッチセンシング | 64 バイト  |

## 4.7 ICP と IAP

インサーキットプログラミング (ICP) は、SWIM インタフェースを使用してユーザアプリケーションをマイクロコントローラにロードして、メモリの内容全体を更新するために使用されます。ICP は、迅速かつ効率的なデザインの繰り返しを提供し、不必要的パッケージの取り扱いやデバイスへの脱着をなくします。SWIM インタフェース（シングルワイヤインターフェースモジュール）は、プログラミングツールへの接続に SWIM ピンを使用します。

ICP とは対照的に、アプリケーション内プログラミング (IAP) は、マイクロコントローラによってサポートされる任意の通信インターフェース (I/O, I<sup>2</sup>C, SPI, USART など) を使用して、プログラムされるデータをメモリにダウンロードできます。IAP では、フラッシュプログラムメモリの内容を、アプリケーションの実行中に再プログラムできます。ただし、アプリケーションの一部は、ICP を使用して、フラッシュプログラムメモリに事前にプログラムされていなければなりません。

プログラミング手順の詳細については、STM8TL5xxx フラッシュプログラミングマニュアル (PM0212) および STM8 SWIM プロトコルおよびデバッグマニュアル (UM0470) を参照してください。

# 参考資料

表 6. メモリアクセスとプログラミング方法<sup>(1)</sup>

| モード                      | ROP<br>(読み出し保護機能) | メモリ領域                | コアからの<br>アクセス                     |

|--------------------------|-------------------|----------------------|-----------------------------------|

| ユーザモード、IAP、<br>およびブートローダ | 読み出し保護有効          | TRAP を除く割り込みベクタ      | R/W <sup>(2)</sup> /E             |

|                          |                   | TRAP                 | R/W <sup>(3)</sup> /E             |

|                          |                   | 独自仕様コード領域 (PCODE)    | R/E <sup>(6)</sup>                |

|                          |                   | ユーザブートコード領域 (UBC)    | R/E                               |

|                          |                   | メインプログラム             | R/W/E <sup>(4)</sup>              |

|                          |                   | データ EEPROM 領域 (DATA) | R/W <sup>(5)</sup>                |

|                          |                   | オプションバイト             | R                                 |

|                          | 読み出し保護無効          | TRAP を除く割り込みベクタ      | R/W <sup>(2)</sup> /E             |

|                          |                   | TRAP                 | R/W <sup>(3)</sup> /E             |

|                          |                   | 独自仕様コード領域 (PCODE)    | R/E <sup>(6)</sup>                |

|                          |                   | ユーザブートコード領域 (UBC)    | R/E <sup>(7)</sup>                |

|                          |                   | メインプログラム             | R/W/E <sup>(4)</sup>              |

|                          |                   | データ EEPROM 領域 (DATA) | R/W <sup>(5)</sup>                |

|                          |                   | オプションバイト             | R/W <sup>(8)</sup>                |

| SWIM アクティブ<br>(ICP モード)  | 読み出し保護有効          | TRAP を除く割り込みベクタ      | P                                 |

|                          |                   | TRAP                 | P                                 |

|                          |                   | 独自仕様コード領域 (PCODE)    | P <sup>(6)</sup>                  |

|                          |                   | ユーザブートコード領域 (UBC)    | P                                 |

|                          |                   | メインプログラム             | P                                 |

|                          |                   | データ EEPROM 領域 (DATA) | P                                 |

|                          |                   | オプションバイト             | P/W <sub>ROP</sub> <sup>(9)</sup> |

|                          | 読み出し保護無効          | TRAP を除く割り込みベクタ      | R/W <sup>(2)</sup> /E             |

|                          |                   | TRAP                 | R/W/E                             |

|                          |                   | 独自仕様コード領域 (PCODE)    | R/E <sup>(6)</sup>                |

|                          |                   | ユーザブートコード領域 (UBC)    | R/E <sup>(7)</sup>                |

|                          |                   | メインプログラム             | R/W/E <sup>(4)</sup>              |

|                          |                   | データ EEPROM 領域 (DATA) | R/W <sup>(5)</sup>                |

|                          |                   | オプションバイト             | R/W <sup>(7)</sup>                |

1. R/W/E = Read (読み出し)、Write (書き込み)、および Execute (実行)

R/E = 読み出しと実行 (書き込み操作は禁止)

R = 読み出し (書き込みおよび実行操作は禁止)

P = アクセスできない領域 (読み出し、実行、書き込み操作がすべて禁止)

P/W<sub>ROP</sub> = 保護されていて、ROP オプションバイト以外の書き込みは禁止。

2. UBC 領域が定義されていない場合、TRAP を除く割り込みベクタは、ユーザ/IAP モードで変更できます。

3. PCODE 領域が定義されている場合、TRAP ベクタは、ユーザおよび IAP モードでは変更できません。そうでない場合、TRAP は他の割り込みベクタと同じルールに従います。

4. フラッシュプログラムメモリは、FLASH\_PUKR レジスタに正しい MASS キーが書き込まれるまで、書き込み保護されます (ロックされます)。FLASH\_PUKR レジスタの PUL ビットをリセットすることによって、メモリを再びロックできます。ロック解除は、2 回のリセットの間に 1 回だけ行うことができます。正しくないキーを指定した場合は、デバイスをリセットして、新しいキーをプログラムしなければなりません。

# 参考資料

5. データメモリは、FLASH\_DUKR レジスタに正しい MASS キーが書き込まれるまで、書き込み保護されます（ロックされます）。FLASH\_IAPSR レジスタの DUL ビットをリセットすることによって、メモリを再びロックできます。正しくないキーを指定した場合は、デバイスをリセットしなくとも、別のキープログラムシーケンスを実行できます。

6. PCODE 領域は、TRAP ベクタを通じて、特権モードでのみ読み出しおよび実行が可能です。PCODE は、SWIM を通じて直接アクセスすることはできません。

7. UBC 領域をプログラムするには、アプリケーションは、まず、UBC オプションバイトをクリアする必要があります。

8. オプションバイトは、FLASH\_DUKR レジスタ（OPT が 1 にセットされた）に正しい MASS キーが書き込まれるまで、書き込み保護されます（ロックされます）。FLASH\_IAPSR レジスタの DUL ビットをリセットすることによって、メモリを再びロックできます。正しくないキーを指定した場合は、デバイスをリセットしなくとも、別のキープログラムシーケンスを実行できます。

9. ROP が解除されると、オプションバイトを含むメモリ全体が消去されます。

## 4.8 フラッシュレジスタ

### 4.8.1 フラッシュ制御レジスタ 1 (FLASH\_CR1)

アドレスオフセット : 0x00

リセット値 : 0x00

| 7    | 6 | 5  | 4 | 3  | 2 | 1  | 0   |

|------|---|----|---|----|---|----|-----|

| 予約済み |   |    |   |    |   | IE | FIX |

|      |   | rw |   | rw |   |    |     |

ビット 7:2 予約済み

ビット 1 **IE** : フラッシュ割り込みイネーブル

このビットは、ソフトウェアによってセット／クリアされます。

0 : 割り込みは無効です。

1 : 割り込みは有効です。FLASH\_IAPSR レジスタの EOP または WR\_PG\_DIS フラグがセットされている場合、割り込みが生成されます。

ビット 0 **FIX** : 固定のバイトプログラミング時間

このビットは、ソフトウェアによってセット／クリアされます。

0 : メモリがすでに消去されている場合は標準のプログラミング時間 ( $1/2 t_{prog}$ ) 、そうでない場合は  $t_{prog}$ 。

1 : プログラミング時間は  $t_{prog}$  に固定されます。

### 4.8.2 フラッシュ制御レジスタ 2 (FLASH\_CR2)

アドレスオフセット : 0x01

リセット値 : 0x00

| 7   | 6    | 5     | 4    | 3 | 2    | 1 | 0   |

|-----|------|-------|------|---|------|---|-----|

| OPT | WPRG | ERASE | FPRG |   |      |   | PRG |

| RW  | RW   | RW    | RW   |   | 予約済み |   | RW  |

ビット 7 OPT : オプションバイトの書き込み

このビットは、ソフトウェアによってセット／クリアされます。

0 : オプションバイトへの書き込みアクセスは無効です。

1 : オプションバイトへの書き込みアクセスは有効です。

ビット 6 WPRG : ワードプログラミング

このビットはソフトウェアによってセットされ、操作が完了したときにハードウェアによってクリアされます。

0 : ワードプログラム操作は無効です。

1 : ワードプログラム操作は有効です。

ビット 5 ERASE<sup>(1)</sup> : ブロック消去

このビットはソフトウェアによってセットされ、操作が完了したときにハードウェアによってクリアされます。

0 : ブロック消去操作は無効です。

1 : ブロック消去操作は有効です。

ビット 4 FPRG<sup>(1)</sup> : 高速ブロックプログラミング

このビットはソフトウェアによってセットされ、操作が完了したときにハードウェアによってクリアされます。

0 : 高速ブロックプログラム操作は無効です。

1 : 高速ブロックプログラム操作は有効です。

ビット 3:1 予約済み

ビット 0 PRG : 標準ブロックプログラミング

このビットはソフトウェアによってセットされ、操作が完了したときにハードウェアによってクリアされます。

0 : 標準ブロックプログラミング操作は無効です。

1 : 標準ブロックプログラミング操作は有効です（自動的に最初に消去）。

1. メモリがビジーのとき、ERASE および FPRG ビットはロックされます。

### 4.8.3 フラッシュプログラムメモリ保護解除キーレジスタ (FLASH\_PUKR)

アドレスオフセット : 0x02

リセット値 : 0x00

| 7             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|---|---|---|---|---|---|---|

| MASS_PRG KEYS |   |   |   |   |   |   |   |

| RW            |   |   |   |   |   |   |   |

ビット 7:0 PUK [7:0] : メインプログラムメモリロック解除キー

このビットはソフトウェアによって書き込まれます（すべてのモード）。読み出し時、0x00 を返します。

メインプログラム領域の書き込み保護解除メカニズムの説明については、[メインプログラムメモリへの書き込みアクセスの有効化 \(30 ページ\)](#) を参照してください。

## 4.8.4 データ EEPROM 保護解除キーレジスタ (FLASH\_DUKR)

アドレスオフセット : 0x03

リセット値 : 0x00

| 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------|---|---|---|---|---|---|---|

| MASS_DATA KEYS |   |   |   |   |   |   |   |

| RW             |   |   |   |   |   |   |   |

ビット 7:0 **DUK[7:0]** : データ EEPROM 書き込みロック解除キー

このビットはソフトウェアによって書き込まれます（すべてのモード）。読み出し時、0x00 を返します。

メインプログラム領域の書き込み保護解除メカニズムの説明については、[データ領域への書き込みアクセスの有効化 \(31 ページ\)](#) を参照してください。

## 4.8.5 フラッシュステータスレジスタ (FLASH\_IAPSR)

アドレスオフセット : 0x04

リセット値 : 0xX0 (X は未定義)

| 7    | 6 | 5 | 4 | 3 | 2     | 1    | 0     |

|------|---|---|---|---|-------|------|-------|

| 予約済み |   |   |   |   | DUL   | EOP  | PUL   |

|      |   |   |   |   | rc_w0 | rc_r | rc_w0 |

|      |   |   |   |   |       |      | rc_r  |

ビット 7:4 予約済み

ビット 3 **DUL** : データ EEPROM 領域ロック解除フラグ

このビットは、ハードウェアによってセットされ、0 を書き込むことでソフトウェアによってクリアされます。

0 : データ EEPROM 領域書き込み保護は有効です。

1 : データ EEPROM 領域の書き込み保護は、正しい MASS キーを書き込むことによって無効にされました。

ビット 2 **EOP** : プログラミング（書き込みまたは消去操作）の終了フラグ

このビットは、ハードウェアによってセットされます。レジスタを読み出すことによってソフトウェアによって、または新しい書き込み／消去操作が開始したときにクリアされます。

0 : EOP イベントは発生していません。

1 : EOP 操作が発生しました。FLASH\_CR1 レジスタの IE ビットがセットされている場合、割り込みが生成されます。

ビット 1 **PUL** : フラッシュプログラムメモリロック解除フラグ

このビットは、ハードウェアによってセットされ、0 を書き込むことでソフトウェアによってクリアされます。

0 : メインプログラム領域の書き込み保護は有効です。

1 : メインプログラム領域の書き込み保護は、正しい MASS キーを書き込むことによって無効にされました。

ビット 0 **WR\_PG\_DIS** : 保護ページへの書き込み試行フラグ

このビットは、ハードウェアによってセットされ、レジスタを読み出すことによってソフトウェアによってクリアされます。

0 : WR\_PG\_DIS イベントは発生していません。

1 : 書き込み保護されているページへの書き込みの試みが行われました。FLASH\_CR1 レジスタの IE ビットがセットされている場合、割り込みが生成されます。

### 4.8.6 フラッシュレジスタマップとリセット値

フラッシュレジスタ境界アドレスの詳細については、データシートの一般ハードウェアレジスタマップを参照してください。

表 7. フラッシュレジスタマップ

| アドレスオフセット | レジスタ名       | 7     | 6     | 5      | 4     | 3     | 2     | 1     | 0          |

|-----------|-------------|-------|-------|--------|-------|-------|-------|-------|------------|

| 0x00      | FLASH_CR1   | -0    | -0    | -0     | -0    | -0    | -0    | IE0   | FIX0       |

| 0x01      | FLASH_CR2   | OPT0  | WPRG0 | ERASE0 | FPRG0 | -0    | -0    | -0    | PRG0       |

| 0x02      | FLASH_PUKR  | PUK70 | PUK60 | PUK50  | PUK40 | PUK30 | PUK20 | PUK10 | PUK00      |

| 0x03      | FLASH_DUKR  | DUK70 | DUK60 | DUK50  | DUK40 | DUK30 | DUK20 | DUK10 | DUK00      |

| 0x04      | FLASH_IAPSR | -0    | -0    | -0     | -0    | DUL0  | EOP0  | PUL0  | WR_PG_DIS0 |

## 5 割り込みコントローラ (ITC)

### 5.1 ITC の概要

- ハードウェア割り込みの管理

- ペリフェラル割り込み機能

- ソフトウェア割り込みの管理 (TRAP)

- 柔軟な割り込み優先順位とレベル管理による、ネスト型／同時割り込み管理：

- ソフトウェアでプログラムできる最大 4 つのネストレベル

- ハードウェアによって固定された 22 の割り込みベクタ

- 2 つのノンマスカブルイベント：RESET、TRAP

この割り込み管理は、以下に基づきます。

- CPU 条件コードレジスタ (CCR) のビット I1 と I0

- ソフトウェア優先順位レジスタ (ITC\_SPRx)

- プログラムメモリの先頭の 0x00 8000 にあるリセットベクタ。リセット初期化ルーチンは、STMicroelectronics によって ROM にプログラミングされます。

- メモリマップの上位アドレス (0x00 8004~0x00 807C) にあり、ハードウェアの優先順位によって分類される固定の割り込みベクタアドレス

### 5.2 割り込みマスクと処理の流れ

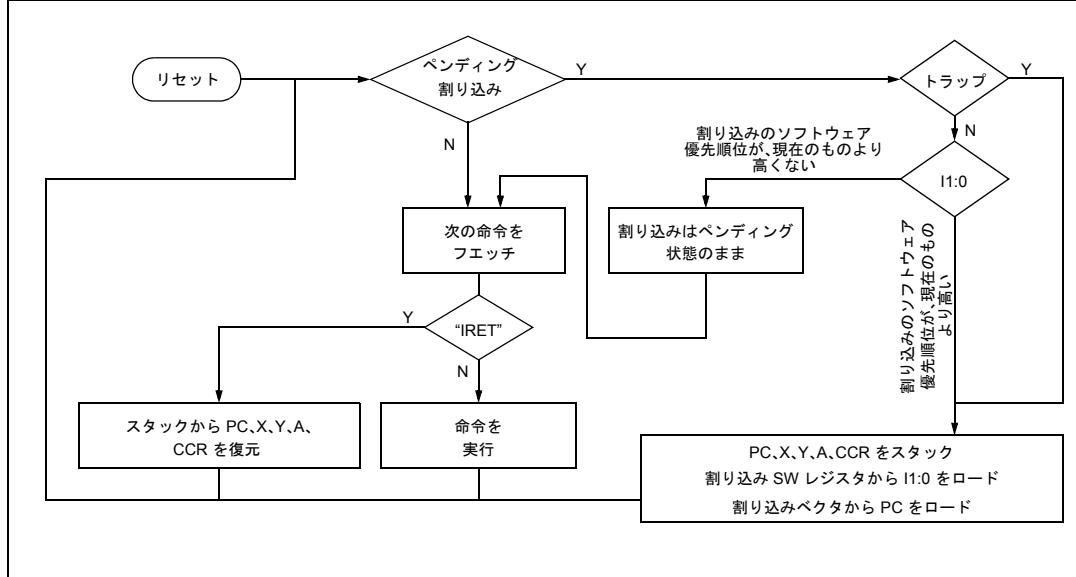

割り込みマスキングの管理は、CCR レジスタのビット I1 と I0 に加えて、各割り込みベクタのソフトウェア優先順位レベル（表 8 を参照）を設定する ITC\_SPRx レジスタによって行われます。処理フローを図 6 に示します。

割り込みリクエストを処理する必要がある場合、

1. 通常の処理は、現在の命令実行の終わりに中断されます。

2. PC、X、Y、A、および CCR レジスタは、スタックに保存されます。

3. CCR レジスタのビット I1 と I0 は、処理された割り込みベクタに対応する ITC\_SPRx レジスタの値に基づいてセットされます。

4. 続いて、PC には処理する割り込みの割り込みベクタがロードされ、割り込みサービスルーチンの最初の命令がフェッチされます（ベクタアドレスの詳細については、データシートの割り込みマッピングテーブルを参照）。

割り込みサービスルーチンは IRET 命令で終わるようにします。これによって、保存されたレジスタの内容がスタックから復旧されます。IRET 命令の結果として、ビット I1 と I0 はスタックから復元され、プログラム実行が再開されます。

表 8. ソフトウェア優先順位レベル

| ソフトウェア優先順位             | レベル    | I1 | I0 |

|------------------------|--------|----|----|

| レベル 0 (メイン)            | ↓<br>高 | 1  | 0  |

| レベル 1                  |        | 0  | 1  |

| レベル 2                  |        | 0  | 0  |

| レベル 3 (= ソフトウェア優先順位無効) |        | 1  | 1  |

図 6. 割り込み処理のフローチャート

注：

割り込みサービスルーチン (ISR) の内部で SIM 命令によって割り込みマスクビット I0 と I1 がセットされた場合、RIM 命令による割り込みマスクの解除によって、ソフトウェア優先順位はレベル 0 に設定されます。

ISR の内部で割り込みを有効／無効にするとき、正しい優先順位を復元するには、[表 9](#) に示す手順に従ってください。

表 9. ISR の内部で割り込みを有効／無効にする方法

| 割り込みを無効にするとき                                                   | 割り込みを有効にするとき                                            |

|----------------------------------------------------------------|---------------------------------------------------------|

| #asm<br>PUSH CC<br>POP ISR_CC <sup>(1)</sup><br>SIM<br>#endasm | #asm<br>PUSH ISR_CC <sup>(1)</sup><br>POP CC<br>#endasm |

1. IRS\_CC は、CC レジスタの現在値を格納する変数です。

### 5.2.1 ペンドィング割り込みの処理

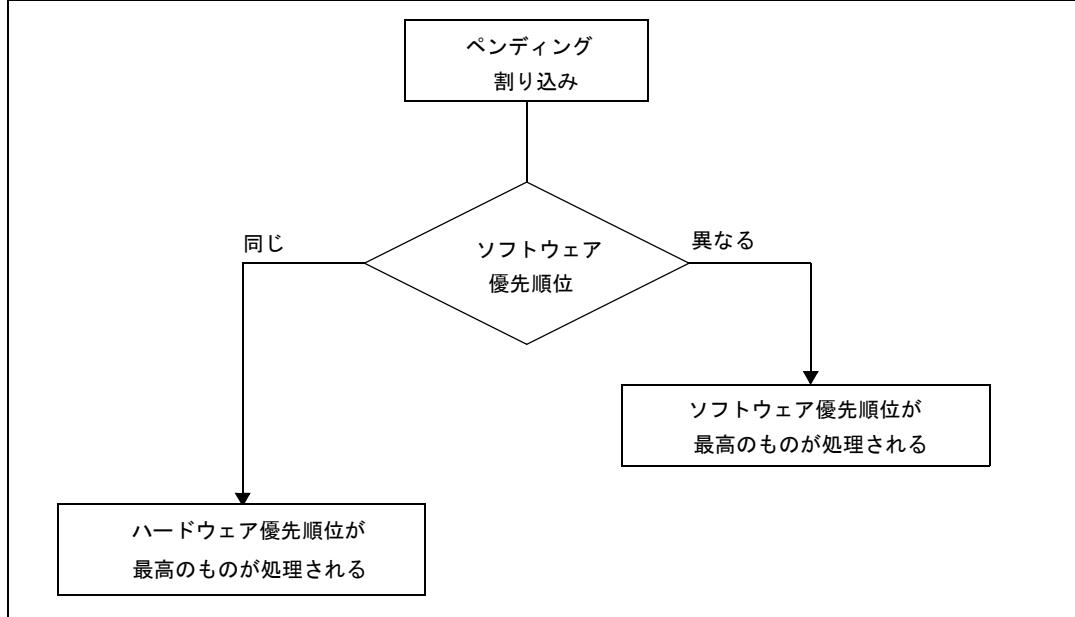

いくつかの割り込みは同時にペンドィング状態になることがあります。ペンドィングされる割り込みは、次の 2 ステップのプロセスによって決まります。

1. ソフトウェア優先順位が最も高い割り込みが処理されます。

2. いくつかの割り込みのソフトウェア優先順位が同じ場合、ハードウェア優先順位が最も高い割り込みから処理されます。

割り込みリクエストがすぐに処理されないときにはラッチされ、そのソフトウェア優先順位とハードウェア優先順位を組み合わせた値が最も高くなったときに処理されます。

注：

- 1 ハードウェア優先順位は排他的ですが、ソフトウェア優先順位はそうではありません。このため、先行するプロセスは、ただ 1 つの割り込みを処理できます。

- 2 リセットとトラップは、決定プロセスにおいて最高のソフトウェア優先順位を持つとみなされます。

ペンドィング割り込み処理プロセスについては、[図 7](#) を参照してください。

図 7. 優先順位決定プロセス

## 5.2.2 割り込みソース

STM8 割り込みコントローラは、2 種類の割り込みソースを管理します。

- ノンマスカブル割り込み：リセットとトラップ

- マスク可能割り込み：外部割り込みまたは内部ペリフェラルによって生成された割り込み

### ノンマスカブル割り込みソース

ノンマスカブル割り込みソースは、CCR レジスタのビット I1 と I0 の状態に関係なく処理されます（図 6 を参照）。PC、X、Y、A、および CCR レジスタは、トラップ割り込みが発生したときにのみスタッカれます。対応するベクタが PC レジスタにロードされ、CCR レジスタのビット I1 と I0 がセットされて、割り込みを無効にします（レベル 3）。

- トラップ（ノンマスカブルソフトウェア割り込み）

このソフトウェア割り込みソースは、トラップ命令が実行されるときに処理されます。この処理は、図 6 に示されるフローチャートに従って行われます。

トラップ割り込みでは、プロセッサは HALT モードから抜けることができません。

- リセット

リセット割り込みソースは、最も高い STM8 ソフトウェアおよびハードウェア優先順位です。これは、リセットルーチンの始めに、すべての割り込みが無効になることを意味します。RIM 命令によって再び有効にする必要があります（表 12：専用割り込み命令セットを参照）。

リセット割り込みでは、プロセッサは HALT モードから抜けることができます。

リセット割り込み管理の詳細については、リセットの章を参照してください。

## マスク可能な割り込みソース

マスク可能な割り込みベクタソースが処理されるのは、対応する割り込みが有効であり、ITC\_SPRxレジスタの割り込みソフトウェア優先順位が現在処理中のもの (CCR レジスタの I1 と I0) より高い場合です。2 つの条件のいずれかが満たされない場合、割り込みはラッチされ、ペンディング状態のままです。

### ● 外部割り込み

外部割り込みを使用して、MCU を HALT モードからウェイクアップできます。外部割り込みに対するトリガは、外部割り込み制御レジスタ (EXTI\_CRx) を介して、ソフトウェアによって選択できます。

同じ割り込みラインに接続された複数の入力ピンが同時に選択されたときには、論理和 (OR) がとられます。

レベルトリガされた外部割り込みがラッチされたとき、割り込みルーチンの終わりにそのレベルがまだ存在した場合には、その割り込みは有効なままで (ルーチンで無効にされた場合を除きます)。

### ● ペリフェラル割り込み

いくつかのペリフェラル割り込みによって、MCU は HALT モードからウェイクアップします。データシートの割り込みベクタテーブルを参照してください。

ペリフェラル割り込みが発生するのは、ペリフェラルステータスレジスタの特定のフラグがセットされ、ペリフェラル制御レジスタの対応するイネーブルビットがセットされたときです。

ペリフェラル割り込みをクリアするための標準的なシーケンスでは、ステータスレジスタへのアクセスを行い、関連するレジスタへの読み出しありは書き込みを行います。このクリアシーケンスによって、内部ラッチがリセットされます。したがって、クリアシーケンスが実行されると、ペンディング割り込み (すなわち、処理を待っている割り込み) は失われます。

## 5.3 割り込みと低電力モード

すべての割り込みで、プロセッサは WAIT モードから抜けることができます。

プロセッサが低電力 WAIT モードから抜けられるのは、リセットまたはイベントに限られます。このモードに入るには、低電力 RUN モードで WFE 命令を実行します。イベントによるウェイクアップでは、システムは低電力 RUN モードに戻ります (詳細については [セクション 9: 電源管理](#) を参照)。

プロセッサが HALT／アクティブ HALT モードから抜けられるのは、外部割り込みやその他の特定の割り込みに限られます (データシートの割り込みベクタテーブルにある HALT からのウェイクアップおよびアクティブ HALT からのウェイクアップを参照)。

HALT モードからのウェイクアップ中に複数のペンディング割り込みが存在する場合、最初に処理される割り込みは、HALT モードから抜けれる機能を備えた割り込みに限られます。これは、[図 7](#) に示す決定プロセスを通じて選択されます。優先順位が最も高いペンディング割り込みがデバイスを HALT モードからウェイクアップできない場合、その処理は次に回されます。

HALT 命令の実行中に内部割り込みやタイマなどからの外部割り込みが発生した場合、HALT 命令は実行されますが、HALT 命令が実行を終了した直後に、割り込みはウェイクアッププロセスを呼び出します。この場合、MCU は実際には HALT モードから RUN モードへのウェイクアップ中であり、データシートで指定された対応する遅延  $t_{WUH}$  が伴います。

## 5.4 起動レベル／低電力モードの制御

MCU 起動レベルは、CFG\_GCR レジスタの AL ビットをプログラミングすることによって設定されます（グローバル設定レジスタ（CFG\_GCR）を参照）。

このビットは、MCU の低電力モードを制御するために使用されます。きわめて低電力のアプリケーションでは、MCU は大部分の時間を WFI/HALT モードで費やし、特定のタスクを実行するために、特定の時点で割り込みによってウェイクアップされます。これらの反復的なタスクのいくつかは十分に短いため、メインプログラムに戻らずに、ISR（割り込みサービスルーチン）で直接処理されます。このようなケースに対応するため、低電力モードに入る前に WFI/HALT 命令を実行して AL ビットをセットすることができます。これによって、割り込みルーチンは低電力モードに直接戻ります。レジスタのコンテキストは最初の割り込み時にのみ保存されるので、実行時間／ISR 実行は削減されます。

結果として、きわめて簡単なアプリケーションでは、すべての操作を ISR で実行できます。より複雑なアプリケーションでは、割り込みルーチンは、AL ビットをリセットするだけでメインプログラムを再起動できます。

たとえば、ピン／センサ／押しボタンのステータスをチェックするために、自動ウェイクアップユニット（AWU）によってアプリケーションを 50 ms ごとにウェイクアップすることが必要な場合もあります。ほとんどの場合、これらのピンは無効になっているので、MCU は、メインプログラムを実行しなくても低電力モードに戻ることができます。1 本でも有効なピンがある場合、ISR は、AL ビットをリセットすることによってメインプログラムを起動します。

## 5.5 同時およびネスト割り込み管理

STM8 デバイスは、2 つの割り込み管理モードを備えています。

- 同時モード

- ネストモード

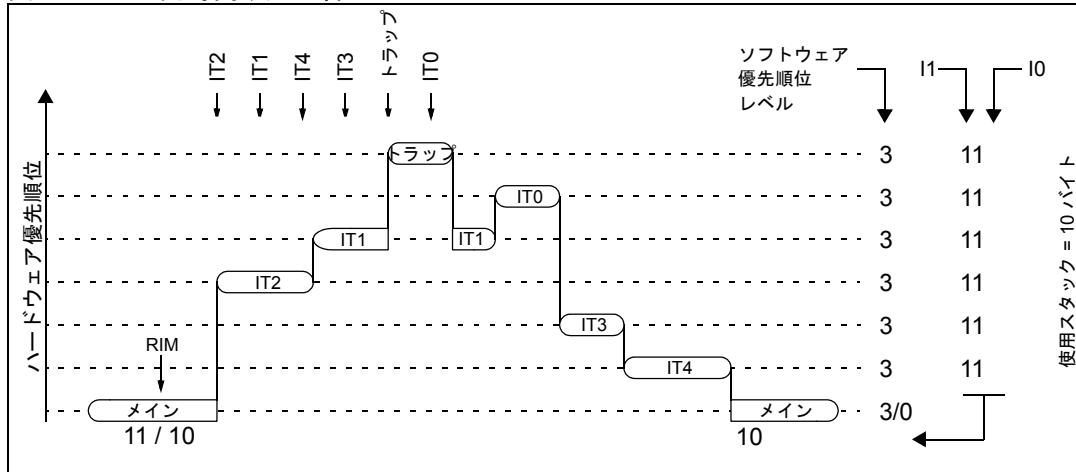

### 5.5.1 同時割り込み管理モード

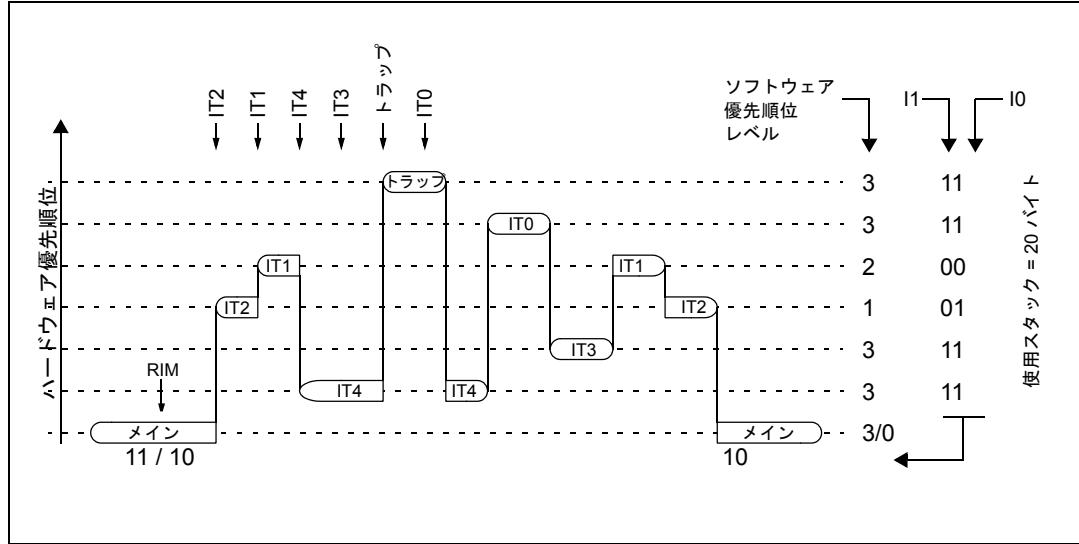

このモードでは、すべての割り込みの割り込み優先順位レベルが 3 なので、リセットやトラップによる場合を除いて、割り込みを受けることはありません。

ハードウェア優先順位は、最低から最高の優先順位まで、メイン、IT4、IT3、IT2、IT1、IT0、トラップ（同じ優先順位）、およびリセットの順です。

図 8 に同時割り込み管理モードの例を示します。

図 8. 同時割り込み管理

### 5.5.2 ネスト割り込み管理モード

このモードでは、割り込みルーチンの処理中の割り込みが可能です。このモードは、レベル 3 を下回る割り込み優先順位レベルが設定されると有効になります。