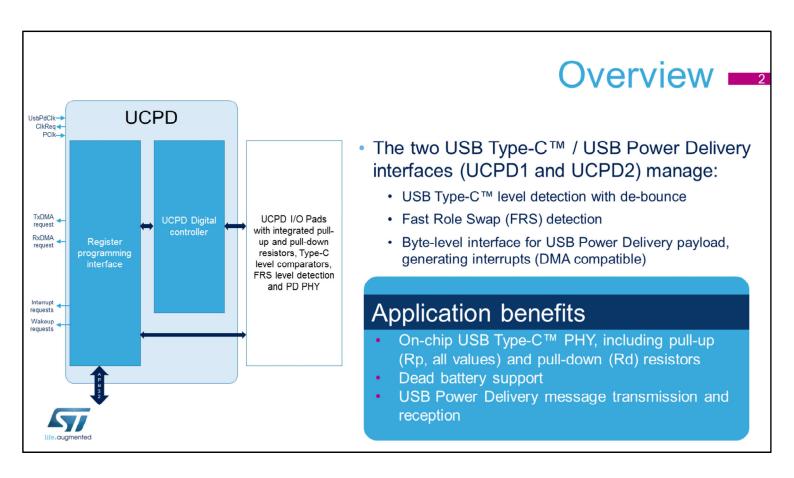

Welcome to the presentation of the STM32G0 UCPD (USB Type C / Power Delivery) interface. It covers the main features of this module.

The UCPD units embed a PD physical layer (PHY) with a direct connection to the Configuration Channel pins (CC1 and CC2).

The UCPD can be configured as a Downstream Facing Port (DFP) or an Upstream Facing Port (UFP) and also supports the Fast Role Swap protocol that enables swapping DFP and UFP states.

In order to implement the protocol layers based on message exchange over CC1 or CC2, the UCPD offers a programming interface, enabling software to receive or send message payload bytes. Requests to external DMA channels may also be used to automatically transfer protocol messages to/from memory.

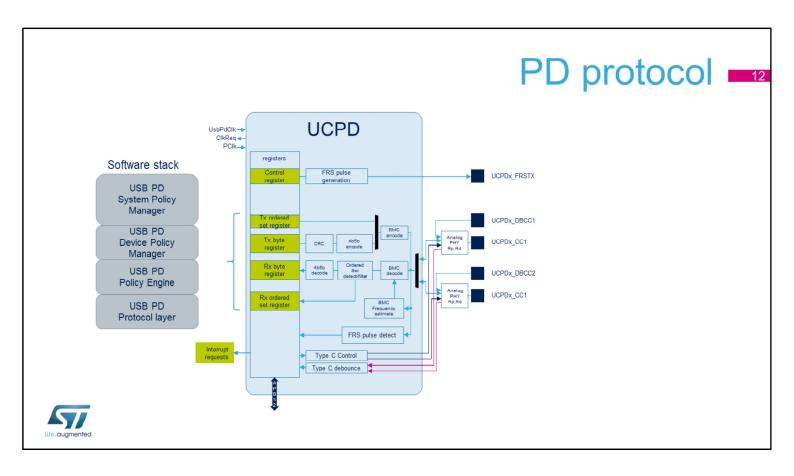

The block diagram shows the two important parts of the UCPD module:

The register interface on the left clocked by PCLK, that is used by software to configure and determine

- the current state of the module. Messages are transferred byte per byte by means of the Tx and Rx registers

- The PD physical layer that encodes/decodes bytes, appends and checks the CRC and also manages the transmission of ordered sets.

#### The application benefits are:

- Integrated on-chip PD PHY, including Rp and Rd resistors

- Dead Battery mode supported allowing connection detection at the peer device in a dead battery situation

- PD message transmission and reception, software is only in charge of handling the payloads.

#### UCPD features **■**

- The USB Type-C<sup>™</sup> / USB Power Delivery interface supports the physical layer of the USB Power Delivery specification

- Supports Universal Serial Bus Power Delivery specification: Revision 3.0, V1.2

- Supports Universal Serial Bus Type-C<sup>™</sup> Cable and Connector Specification: Release 1.3

- Primary function is the physical layer implementation of the Power Delivery (PD) specification, CC signaling method (not VBUS), specific to Type-C™ cables

The UCPD controller is compliant with

- USB Type-C Rev. 1.2 and

- USB Power Delivery Rev. 3.0 specifications.

Regarding the PHY, only the CC signaling method is supported, so the Type-C cable is required.

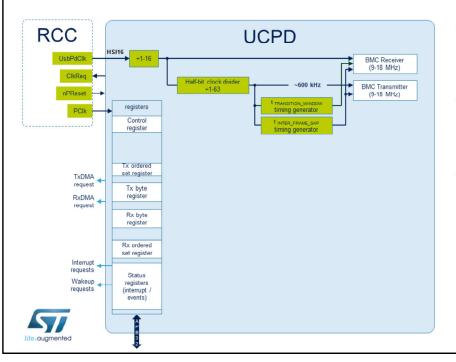

#### UCPD resets and clocks •

- A single reset signal nPReset (APB bus reset) is used

- The register section of UCPD is directly clocked on PClk

- The main functional part is clocked on UsbpdClk

- · This clock can be pre-scaled

- The receiver is designed to work for any clock input from 6 to 18 MHz

- Performance may be lower in the range 6 to 9 MHz

The Reset and Clock Controller (RCC) unit is in charge of resetting the UCPD unit by asserting the NPReset signal.

It also provides the following reference clocks to the UCPD unit:

- PClk, which is the APB clock, used to access memorymapped registers

- UsbPdClk, which is the main functional clock.

UsbPdClk can be prescaled in order to obtain the half-bit clock required by the Bi Mark Phase coding.

Note that for the timings called tTransitionWindow and tInterFrameGap, the clock frequency uncertainty should be taken into account in order to respect the timings in all cases.

The UCPD module asserts ClkReq to the RCC in order to exit a clock-gating low-power state.

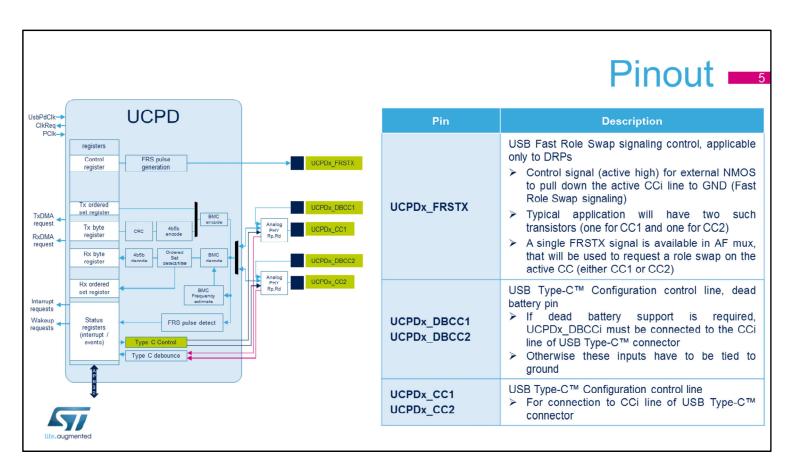

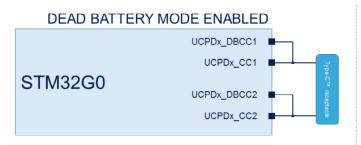

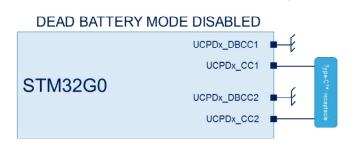

This slide describes the pinout of the UCPD units.

Pins UCPDx\_CC1 and UCPDx\_CC2 are the only signals to be routed to the USB Type-C receptacle. Note that the cable contains a unique CC signal, connected to either CC1 or CC2 in the receptacle because the cable can be flipped.

The UCPDx\_FRSTX pin is relevant when the Dual Role Port protocol is supported. It is used to control an external NMOS transistor that pulls down the CC1 or CC2 line respectively, which is the way to request a role swap.

Pins UCPDx\_DBCC1 and UCPDx\_DBCC2 are used when the STM32G0 USB Type-C port indicates to the peer port a dead battery condition, by connecting UCPDx\_DBCC1 to UCPDx\_CC1 and UCPDx\_DBCC2 to UCPDx\_CC2.

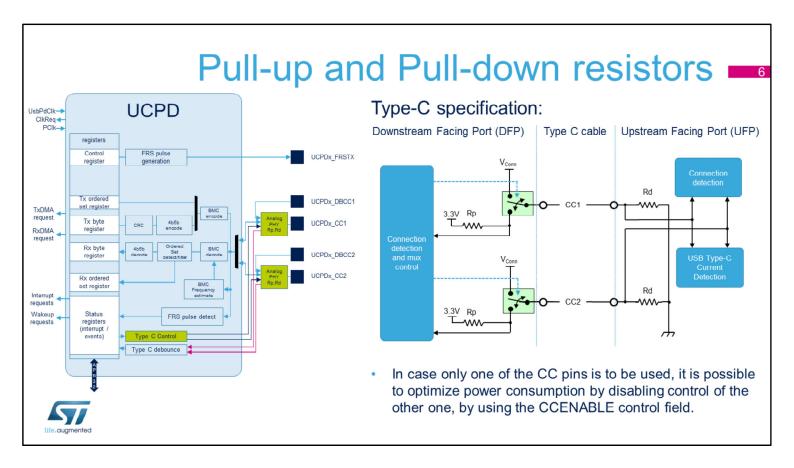

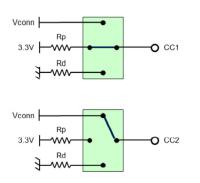

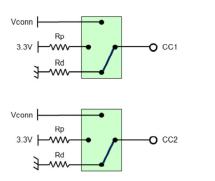

The STM32G0 implements internal Rp and Rd resistors connected to CC1 and CC2 pins required by the USB PD specification to:

- Detect a connection.

- Determine whether the cable is flipped.

- Determine the default available power as the currentcarrying capability depends on the values of Rp.

Finally, a unique CC pin, CC1 or CC2 according to cable flip, is used to transport PD messages.

The unused CC pin may become the VCONN pin, which supplies the power to integrated circuits present in active cables.

In order to conserve power, the unused CC pin can also be disabled by programming the CCENABLE field in the UCPD\_CR register.

#### PD and PU resistors

7

UCPD configured as Downstream Facing Port Assumption: cable is not flipped

UCPD configured as Upstream Facing Port Assumption: cable is not flipped

The UCPD is configured by software as either a Downstream Facing Port (DFP) or an Upstream Facing Port (UFP).

In DFP mode, assuming no cable flip, CC1 is connected to Rp. The value of Rp indicates the value of the default power that the DFP can source on Vbus.

In DFP mode, assuming no cable flip, CC2 is connected to Vconn. VCONN is a 5 Volt 1.0 Watt power supply used to power devices within the plug that are needed to implement electronically marked cables and VCONN-powered accessories.

In UFP mode, assuming no cable flip, CC1 and CC2 are connected to Rd, which is a 5.1 Kilo ohm resistor. Since the UCPD supports both DFP and UFP operation, the internal switches represented in the figure select the current configuration.

# PD and PU resistors, dead battery

When the MCU is unpowered, it will still present the "dead battery" Rd

When the MCU is unpowered, it will present an open circuit on CC1 and CC2

After power arrives and the MCU boots, the desired behavior (e.g. sink) should be programmed in the ANAMODE and ANASUBMODE fields of the UCPD\_CR register before writing SYS\_CONFIG[USBPDstrobe] to activate this behavior

When the UCPD is used as an upstream facing port, the dead battery feature enables the UCPD to indicate to the peer node that it needs to be powered. This analog setting is is functional even when the MCU power supply is switched off. This default behavior is configured by connecting the DBCC pins to the respective CC pins. After power arrives and the STM32G0 boots, the desired behavior (source of sink) should be programmed in the ANAMODE and ANASUBMODE fields of the UCPD\_CR register and then USB PD Strobe bit has to be set to one in a SYSCFG register called SYS\_CONFIG. Connecting DBCC pins to ground disables Dead Battery mode. In this case, the peer DFP is unable to distinguish a dead battery state from an unattached state.

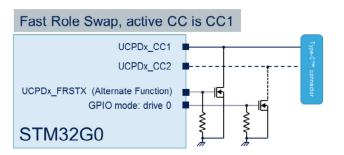

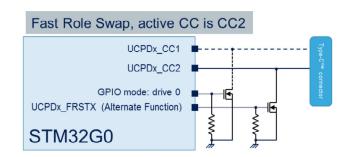

# Fast Role Swap (FRS) signaling and detection

- FRS signaling:

- External N-MOS transistors are required in order to get the low-resistance pull-down to GND on the appropriate CC line, the FRSTX control needs to be mapped to one or other N-MOS

- · A control signal (FRSTX) will pulse at high level for the correct duration

- FRS detection is controlled by FRSRXEN in UCPD\_CR register

The Fast Role Swap protocol swaps the roles of DFP and UFP. The default power source node becomes the sink node and the default sink node becomes the source node.

To request a FRS to the source node, the sink device temporarily connects the appropriate CC line to ground. This is achieved by external N-MOS transistors on both CC lines, however only one will receive the FRSTX pulse.

The N-MOS on the inactive CC line should be driven with a logic 0 level using GPIO mode.

The FRSRXEN bit in the UCPD\_CR register controls the FRS detection in the sink node. When this bit is set, the FRS detection is enabled.

####

UCPD Digital controller —10

- The digital controller handles notably

- USB Type-C<sup>™</sup> level detection with de-bounce, generating interrupts

- · FRS detection, generating an interrupt

- CRC generation/checking

- · 4b5b encode/decode

- Bi-Phase Mark encode/decode

- Ordered sets (with a programmable ordered set mask at receive)

- · Frequency recovery in receiver during preamble

- Byte-level interface for USB Power Delivery payload, generating interrupts (DMA compatible)

- USB Power Delivery timing dividers (including a clock pre-scaler)

The digital controller is in charge of:

- USB Type-C level detection with de-bounce

- Fast Role Swap (FRS) detection

- CRC generation and checking

- 4b5b encode/decode

- Bi-phased Mark (BMC) encode/decode

- Transmission and reception of ordered sets.

A clock data recovery unit in the receiver recovers the transmission clock from the received bitstream.

The digital controller offers a byte-level interface for USB Power Delivery payload, generating interrupts. A DMA channel can assist the transfer of message payloads, because the UCPD unit is able to request DMA transfers. The UCPD module implements two clock domains: APB register interface clocked by PCLK and PHY clocked by UsbPdClk.

UsbPdClk is divided by a programmable prescaler to

provide the CC clock, whose maximum frequency is 300 Kbps (kilobits per second). Due to the bi-phased mark coding, two transitions may occur per transmitted bit, therefore the actual maximum clock frequency is 600 kHz.

# Voltage monito Ucpd Ucpd It ordered set register TxDMA request RxDMA request Rx byte register Rx byte register Rx byte register Rx byte register Rx ordered set register Rx byte register Rx byte register Rx ordered set register Rx byte register Rx byte register Rx ordered set register Rx ordered set register Rx byte r

- Voltage monitoring and de-bouncing

- In order to keep the Type-C<sup>™</sup> state machine up to date, monitoring of significant voltage events on the CC1 and CC2 pins is available and can be done, either continuously or by polling

- In order to present only significant events to software, a de-bouncing is performed, also a co-ordination with power delivery Tx/Rx activity

The PHY monitors the state of CC1 and CC2, either continuously or by polling, to detect and signal events to the software by setting flags in the UCPD\_SR register. In order to optimize power consumption, it is recommended to use polling, because Type-C detectors are OFF between polls, rather than wakeup from STOP, which requires Type-C detectors permanently ON. The static level on the CC pins is determined via threshold detectors in the PHY to give a voltage range value in registers, facilitating the Type-C state machine implementation in software, and also allowing the cable orientation to be determined.

The Type C debounce subunit filters events to be reported to software. It is also in charge of ensuring the coordination between event signaling and power delivery Tx/Rx activity.

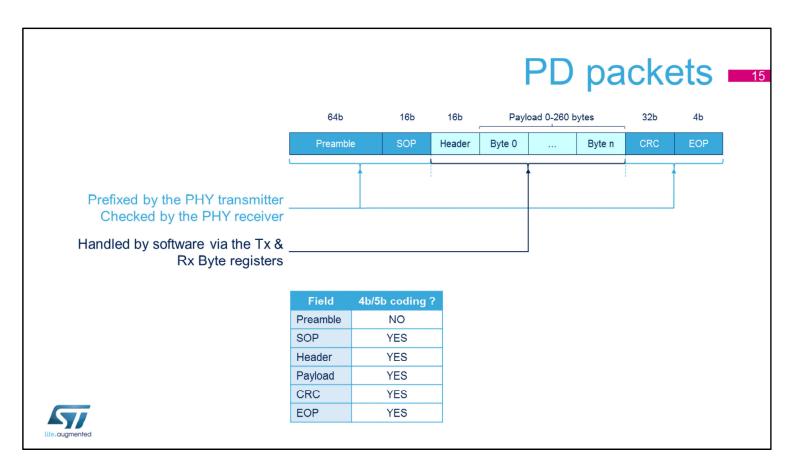

The PD software stack is executed by the Cortex-M0+core in the STM32G0.

It is based on messages and events. Events are reported to the Cortex-M0+ core through interrupts.

Regarding messages, only the payload is under software control. The digital controller performs message encapsulation with Preamble, Start of Packet, CRC and End of Packet.

The software stack includes the protocol layer, the policy engine, the device policy manager and the system policy manager. The system policy manager may control several PD ports, in order to implement platform level power management.

## PD protocol 13

| Protocol layer |                          | Purpose                                                                                                                                                                                                                                                                                                                                                          |  |  |

|----------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DPM            | Device Policy<br>Manager | <ul> <li>DPM is responsible of the overall system management and monitoring</li> <li>▶ It interacts with the policy engine, power supply, cable detect, and system policy manager</li> <li>▶ It determines the power plan and actions (contracts) required depending on current power state</li> </ul>                                                           |  |  |

| PE             | Policy Engine            | One instance per port, that determines the Local Policy to be enforced  > Message sequences are specified for various operations:  Request power resources for the port  Power source or sink transitions  This layer implements power negotiation and swapping  It handles message flow errors and resets                                                       |  |  |

| PL             | Protocol Layer           | On transmit, this layer builds the message and passes it to the Digital Controller On receipt, this layer gets the message from the Digital Controller, parses and deconstructs it  CRC generation/checking is performed by this layer, which automatically returns GoodCRC for correctly received messages  Communication errors are also handled by this layer |  |  |

Three software layers are defined in the PD specification:

- Device Policy Manager (DPM) is in charge of device level system management and monitoring. It determines the power plan and contracts depending on current power state.

- Policy Engine (PE) controls a single UCPD port.

Message sequences are defined to request power

resources, performing source or sink transitions. This

layer implements power negotiation, swapping and

handles message flow errors and reset.

- 3. Protocol Layer (PL) is in charge of constructing and deconstructing PD messages. This layer automatically returns GoodCRC when a message is correctly received and also handles transmission errors, such as timeout and retries.

#### Ordered sets -14

- An ordered set consists of 4 K-codes

- The receivers search for all four K-codes and when one of them finds either three out of four or all four in the correct place, it may interpret it as a valid ordered set

| Ordered sets defined in PD specification |                                                                                                 |  |  |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|

| Cable reset                              | Causes a cable reset                                                                            |  |  |  |

| Hard reset                               | Causes a hard reset                                                                             |  |  |  |

| SOP                                      | Start of Packets targeting the peer PD device or devices included in electrically marked cables |  |  |  |

| SOP'                                     |                                                                                                 |  |  |  |

| SOP'_Debug                               |                                                                                                 |  |  |  |

| SOP"                                     |                                                                                                 |  |  |  |

| SOP"_Debug                               |                                                                                                 |  |  |  |

In addition to transporting data digits, converted into 5-bit codes, the PD protocol also transports signaling patterns called ordered sets.

They are composed of four 5-bit K codes and are tolerant to transmission errors through a redundancy mechanism.

Ordered sets, such as Start of Packet (SOP) are necessarily present in packets. The digital controller automatically inserts them in the transmitter and strips them in the receiver after having checked their validity. The ordered sets defined in the PD specification are used to:

- Signal a cable or hard reset condition

- · Delimit the beginning of packets.

The PHY automatically inserts the preamble, the Start of Packet (SOP), the CRC and the End of Packet (EOP). The receiver PHY handles these fields and removes them. The header field and possibly the payload fields are entirely handled by software. The PHY does not interpret their contents.

The Preamble is not encoded. It is used by the receiver PHY to recover clock data. All the subsequent fields are encoded in the transmitter and decoded in the receiver.

## PD packets, resets

| 64b      | 4b    | 4b    | 4b    | 4b    |  |

|----------|-------|-------|-------|-------|--|

| Preamble | RST-1 | RST-1 | RST-1 | RST-2 |  |

- The Hard Reset packet directly interrupts an on-going transfer in a clean manner

- Cable Reset is similar in format to Hard Reset, but unlike Hard Reset it does not require a specific high-priority treatment

- Sequence

- Wait tInterFrameGap (25 µs)

- · If CC is not idle, wait for it to become idle

- Send the Preamble followed by the 4 K-codes for Hard Reset signaling

- Disable the channel (i.e. stop sending and receiving), reset the PHY Layer and inform the Protocol Layer that the PHY Layer has been reset

Re-enable the channel when requested by the Protocol Layer

The Type-C connector does not support a dedicated reset signal. Consequently, reset conditions are signaled by using specific PD packets transferred over the CC line. Two types of reset are defined: hard reset, which aborts the on-going transfers and the cable reset, which does not required a high-priority treatment. The sequence required to issue the reset packet is

described in this slide.

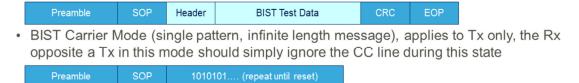

# PD packets, Built-In Self Test (BIST)

- Depending on the BIST action required by the Protocol Layer, either of the following can be run:

- A Tx BIST pattern test, achieved by writing to TXMODE and TXSEND in the UCPD\_CR register

- An Rx BIST pattern test, achieved by writing to RXMODE to the correct value for the RXBIST field in the UCPD CR register

- The two possible patterns supported in UCPD are:

- BIST Test Data (192-bit pattern), applies to Tx and Rx

Receiver acknowledged packet, but then discarded (not passed to the protocol layer)

The PD specification describes Built-In Self test (BIST) packets, used to test whether the CC line is functional. BISTs are sent on a software decision, based on fields in the UCPD\_CR register.

Software can enforce the transmission of a BIST packet and can also configure the receiver in test mode: received BIST packets are not submitted to software, however their CRC is checked.

Two formats of BIST packets are defined in the PD specification:

- BIST test data, which is a packet containing a payload, used to test the digital controller

- BIST carrier mode, which is a single pattern, infinite length message, used to the test the physical link by capturing the CC in an oscilloscope for example.

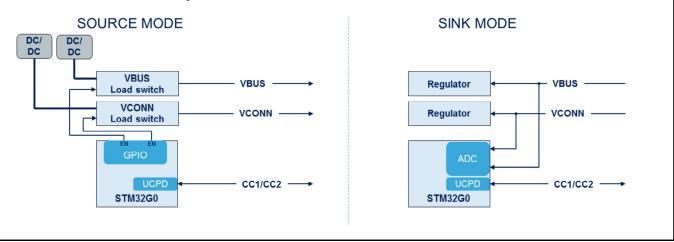

# Type-C™ state machine handling

- For the general application cases of source and sink (and also dualrole port which can switch between those two) the software must implement the relevant USB Type-C™ state machine

- · The UCPD module only controls the CC lines

The Type-C state machine is implemented in software. The Type-C state machine depends not only on CC pin levels, but also on the port role:

- In sink mode, it depends on the VBUS presence detection,

- In source mode, it depends on the VCONN generation and the VBUS state: ON, OFF, voltage level and discharge.

The UCPD module only controls the CC lines. Other modules are involved to control the VBUS and VCONN power supplies.

In Source mode, GPIOs are required to control the power delivery dynamically.

In Sink mode, ADC channels are used to monitor VBUS and VCONN supplies.

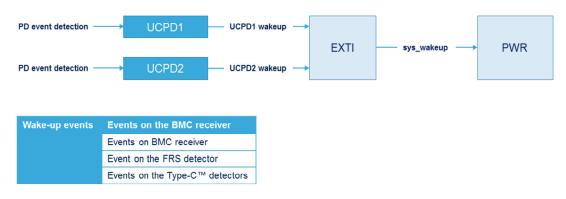

# Low power operation <a>—19</a>

- The interface offers low-power operation compatible with Stop mode, maintaining the capacity to detect incoming USB Power Delivery messages and FRS signaling when the MCU is in this low-power mode

- · The UCPD can be configured to wake up the MCU

The UCPD can be programmed to remain active in Stop 0 and Stop 1 modes. The detection of a PD event while the MCU is in Stop mode causes a wakeup condition, signaled to the EXTI unit and then to the PWR unit. The following events can be configured to cause a wake-up request:

- Events on the BMC receiver, such as message receipt

- Fast Role Swap request

- Events on the Type-C detector, such as attachment/detachment.

## Low power modes 20

| Mode      | Description                                                                                      |

|-----------|--------------------------------------------------------------------------------------------------|

| Run       | UCPD is active                                                                                   |

| Sleep     | UCPD is active                                                                                   |

| Stop 0/1  | Detection of events (Type-C™, BMC Rx, FRS detection) remains operational and can wake up the MCU |

| Standby   | UCPD is not operating, and cannot wake up the MCU ➤ Pull-downs will remain active if configured  |

| Unpowered | Dead battery pull-downs will remain active                                                       |

The UCPD is able to wakeup the MCU from Stop mode (if enabled by setting the WUPEN bit in the UCPD\_CFG2 register) when it recognizes one of the relevant events listed below:

- Type-C event relating to a change in the voltage range seen on either of the CC pins, visible in TYPEC\_VSTATE\_CCx

- Power delivery receive message with an ordered set matching those filtered according to RXORDSETEN[8:0], visible by reading RXORDSET.

At UCPD level, three types of events requiring kernel clock activity may occur during Stop mode: Type-C™, BMC Rx, and FRS detection.

In order to function correctly with the RCC, the clock request signal is activated (conditional on WUPEN) when the following events are detected:

Activity on the analog PHY voltage threshold

- detectors which could later be confirmed to be a stable change between voltage ranges defined in the Type-C specification

- Activity on Power Delivery BMC receiver (coming from the selected CC pin) which could potentially generate an Rx message event (RXORDSET) later

- Activity on Power Delivery FRS detector which could potentially generate an FRS signaling detection event (FRSEVT) later

- Type-C voltage threshold detectors (coming from either CC pin)

- The Power Delivery receiver signal (coming from the selected CC pin)

- The FRS detection signal (coming from the selected CC pin)

## Interrupts 21

| Interrupt event                               | Description                                                                                                                                       |  |  |  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Fast Role Swap detection event                | Set when a new FRS (Fast Role Swap) receive event has happened on the port                                                                        |  |  |  |

| Type C voltage level event (CC2)              | Set whenever TYPEC_VSTATE_CC2 value changes indicating a new stable voltage on that pin                                                           |  |  |  |

| Type C voltage level event (CC1)              | Set whenever TYPEC_VSTATE_CC1 value changes indicating a new stable voltage on that pin                                                           |  |  |  |

| Rx message received                           | Set when a new message has been received                                                                                                          |  |  |  |

| Rx data overflow interrupt                    | Set when the buffer of Rx bytes has overrun (not read in time to free space for the incoming byte)                                                |  |  |  |

| Rx Hard Reset detect interrupt                | Set when a Hard Reset message is received                                                                                                         |  |  |  |

| Rx ordered set (4 K-codes) detected interrupt | Set when a new ordered set is received                                                                                                            |  |  |  |

| Receive data register not empty interrupt     | Set when the UCPD_RXDR register is not empty                                                                                                      |  |  |  |

| Tx data underrun condition interrupt          | Set when an error condition whereby the Tx data register (TXDR) has under-run (i.e. data was not written in time for use in the Transmit message) |  |  |  |

| HRST sent interrupt                           | Set when the HRST message has been                                                                                                                |  |  |  |

| HRST discarded interrupt                      | Set when the HRST message has been discarded                                                                                                      |  |  |  |

| Transmit message abort interrupt              | Set when a Tx message has been aborted due to a subsequent HRST send request taking priority during transmit                                      |  |  |  |

| Transmit message sent interrupt               | Set at the completion of a packet transmission                                                                                                    |  |  |  |

| Transmit message discarded interrupt          | Set when the transmission of message was not possible due to a receive in progress (or noise on the line)                                         |  |  |  |

| Transmit interrupt status                     | Set when the UCPD_TXDR register is empty and it needs to be written                                                                               |  |  |  |

When an interrupt from the UCPD is received, then the software has to determine the source of the interrupt by reading the UCPD\_SR register.

Depending on which bit is set to "1", the interrupt service routine should handle that condition and clear the bit by writing to the appropriate bit in the UCPD\_ICR register. This slide summarizes all the events detected by the UCPD module that can cause interrupt requests.

### Related peripherals 22

- Refer to these trainings linked to this peripheral for more information:

- STM32G0 DMA controller (DMA)

- Reset and Clock Controller (RCC)

- Extended Interrupt and Event Controller (EXTI)

- System Configuration Controller (SYSCFG)

- Power Controller (PWR)

Please refer to the training linked to this peripheral for more information:

- STM32G0 DMA controller (DMA)

- Reset and Clock Controller (RCC)

- Extended Interrupts and Events Controller (EXTI)

- System Configuration Controller (SYSCFG)

- Power Controller (PWR)