Hello, and welcome to this presentation of the STM32MP1 series External Memories Overview.

This presentation quickly summarizes some key points for the selection of external memories and the related constrains for an application using STM32MP1 series devices.

Let's start to see which kind of Flash memories can be used with the STM32MP1 Series.

### Introduction 3

- Flash memories are non volatile memories used to store code and/or data

- In high speed system based on microprocessors, the external Flash technology and/or external interface are a bottleneck for performances.

- Need a working memory as intermediate workspace (usually a Dynamic RAM due to size required by Rich Operating Systems like Linux).

- In an Operating System environment (e.g. Linux), Flash memories are always used with a file system driver

- Support of new Flash devices could require SW/Ecosystem adaptation

- If needed, more than one Flash can be used in a system

- · To get advantage of each technology (e.g. NOR for reliability, NAND for price)

- To separate content types (e.g. One Flash for Linux kernel, One Flash for data

Filesystem)

Flash memories are used to store code and/or data. Due to high processing performance needed, accessing code and/or data become a bottleneck and an intermediate workspace like an external DDR is always required. In an Operating System environment, the Flash memory is managed as a file system, so execute in place (XIP) is not possible and the Flash memory always needs a specific driver tailored to each particular device. In most system, there is more than one Flash to cope with the strength or the weakness of each type of Flash technology or to separate storage to increase performance, security or user flexibility.

## Flash devices Vs Characteristics

| Flash Device     | Flash<br>Technology | PCB area | Cost Vs<br>Density | Reliability | Read<br>Perf. | Erase/Write<br>Perf. |  |

|------------------|---------------------|----------|--------------------|-------------|---------------|----------------------|--|

| Serial-NOR       | NOR                 | ****     | *                  | ****        | **            | *                    |  |

| Serial-NAND      | SLC-NAND            | ****     | **                 | ***         | **            | **                   |  |

| Raw-NAND         | SLC-NAND            | **       | ***                | ***         | ***           | ***                  |  |

| e•MMC            | SLC/MLC-NAND        | ***      | ****               | ***         | ****          | ****                 |  |

| Removable Device |                     |          |                    |             |               |                      |  |

| SD-Card          | MLC-NAND            | *        | ****               | **          | ***           | ***                  |  |

| USB Stick        | MLC-NAND            | *        | ****               | **          | ****          | ****                 |  |

SLC = Single Level Cell MLC = Multiple Level Cell

This table summarizes most of the differences between the various Flash technologies which can be used in a STM32MP1 microprocessor system.

Serial-NOR Flash technology has a very good PCB area (due to low pin count of serial devices) and a very good reliability. The cost of high density and the write performances are the bottleneck to use NOR Flash memories for large storage.

Serial-NAND Flash technology has a very good PCB area and a better cost and write performances than the Serial-NOR Flash technology. Reliability is often seen as lower than for Serial-NOR Flash technology, but error correction is embedded in the HW and transparent to the filesystem. Raw-NAND technology has a parallel interface which if not good for PCB area, but offer a good tradeoff between cost and performance. Most Raw-NAND memories do not have an embedded error correction and so, need additional HW and filesystem management for e.g. bad block management

and wear leveling.

eMMC devices are widely used in mobile phone market, and so, offer very good price and performance. eMMC memories embed error correction as well as fully automatic bad block management and wear leveling.

Removable devices such as SD-Card or USB stick are providing very good cost at large density, but at the expense of lower flexibility and reliability due to user access and mechanical constrains.

##

| Flash Device     | USBH           | SDMMC        | FMC                         | QUADSPI | Number<br>of wires        | Comments                                                                      |  |

|------------------|----------------|--------------|-----------------------------|---------|---------------------------|-------------------------------------------------------------------------------|--|

| Serial-NOR       |                |              |                             |         | 4 to 6                    | 1 to 4 bits                                                                   |  |

| Serial-NAND      |                |              |                             |         | 4 to 6                    | up 2x4 bits devices                                                           |  |

| Raw-NAND         |                |              | $   \overline{\checkmark} $ |         | 14 to 22                  | 8 or 16 bits, 8 bits ECC 2xCS for 8 bits devices                              |  |

| e•MMC            |                | $\checkmark$ |                             |         | 3 to 10                   | 1 to 8 bit width                                                              |  |

| Removable Device |                |              |                             |         |                           |                                                                               |  |

| SD-Card          |                |              |                             |         | 6<br>(10 wires for UHS-I) | 1 to 4 bit width                                                              |  |

| USB Stick        | (Not Bootable) |              |                             |         | 2                         | For information only as not bootable and cannot be used without another Flash |  |

STM32MP1 Series can interface Serial-NOR and Serial-NAND memory devices thru the QUADSPI interface which can support up to two 4-bit devices. STM32MP15 Series can only boot from the first QUADSPI device.

Raw-NAND memories can be connected to the Flexible Memory Controller (FMC). The possible configurations are either one 8-bit or 16-bit device or two 8-bit devices sharing the same data bus. Only SLC device requiring up to 8-bits ECC are supported. STM32MP1 Series can boot from Raw-NAND memory devices.

eMMC memories can be connected to any of the SDMMC interfaces (SDMMC3 has only 4-databits). eMMC devices support 1, 4 or 8-bit data width. STM32MP15 Series can boot from eMMC memory connected to the SDMMC2 interface.

SD-Card can be connected to any of the SDMMC interfaces. STM32MP15 Series provides optional control for external level shifter (mandatory for the support of UHS-I mode which

requires 3V then 1.8V signaling). STM32MP1 Series can boot from SD-Card connected to the SDMMC1 interface.

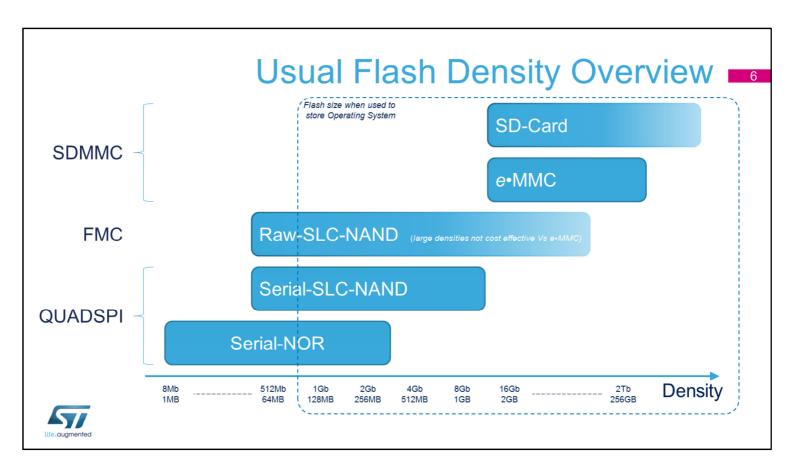

This slide shows the usual Flash density available by technology.

Note than a Flash memory with a size less than 1 Gbit (128 Mbyte) can not be used alone, as such size does not allow the storage of the operating system, but can anyway store data when used in conjunction with another larger Flash holding the operating system itself.

Let's continue with DRAM memories supported by the STM32MP1 Series.

### DDR fundamentals substituting statements substituting statements

- ١....

- DDR stands for Double Data Rate Synchronous Dynamic Random Access Memory

- DDR technology needs 'Refresh'

- Uses 'dynamic' memory cell (i.e. a small capacitor), data is lost after some tens of milliseconds if not 'refreshed'

- 'Refresh' is done automatically by the STM32MP1 Series DDR controller or generated inside the memory when the system is in low power mode (Self-Refresh mode)

- Data are accessed in burst (usually 4 or 8 data of 16 or 32-bits each)

- STM32MP1 Series DDR Controller has the duty to interleave and optimize controls, read/writes/refresh to get maximum performances

Here is some fundamentals about the DRAM technology. Despite their inherent complexity and constrains, dynamic RAMs are used in many devices as it is the only memory available with a very large density at an affordable price.

# DRAM devices Vs Characteristics

| DRAM<br>Device | Supply      | PCB area | Cost Vs<br>Density | Dynamic<br>Power | Standby<br>Power | Performance |

|----------------|-------------|----------|--------------------|------------------|------------------|-------------|

| DDR3           | 1.5V        | **       | ****               | *                | *                | ****        |

| DDR3L          | 1.35V       | **       | ****               | **               | *                | ****        |

| LPDDR2         | 1.2V & 1.8V | ****     | *                  | ****             | ****             | ***         |

| LPDDR3         | 1.2V & 1.8V | ****     | **                 | ****             | ****             | ***         |

DDR3 technology has been superseded by DDR3L technology which offers the same performance but consuming less power.

LPDDR2 technology offers smaller packages and less signals on PCB than the DDR3/DD3L one, a better power consumption, but has usually an higher price and needs two different supply voltages.

| DRAM<br>Device | Data<br>width | Max<br>Freq. | # of<br>CS | # of<br>ICs | # of<br>wires | Comments                          |

|----------------|---------------|--------------|------------|-------------|---------------|-----------------------------------|

| DDR3 /         | 16-bits       | 533 MHz      | 1          | 1           | 50            | DDD21 recommended for new designs |

| DDR3L          | 32-bits       | 533 MHz      | 1          | 2           | 72            | DDR3L recommended for new designs |

| LPDDR2 /       | 16-bits       | 533 MHz      | 1          | 1           | 36            | 16-bits less popular than 32-bits |

| LPDDR3         | 32-bits       | 533 MHz      | 1          | 1           | 58            |                                   |

- DDR interface uses dedicated pins which cannot be reused for other purposes

- 32-bit interface only available on LFBGA448 and TFBGA361 packages

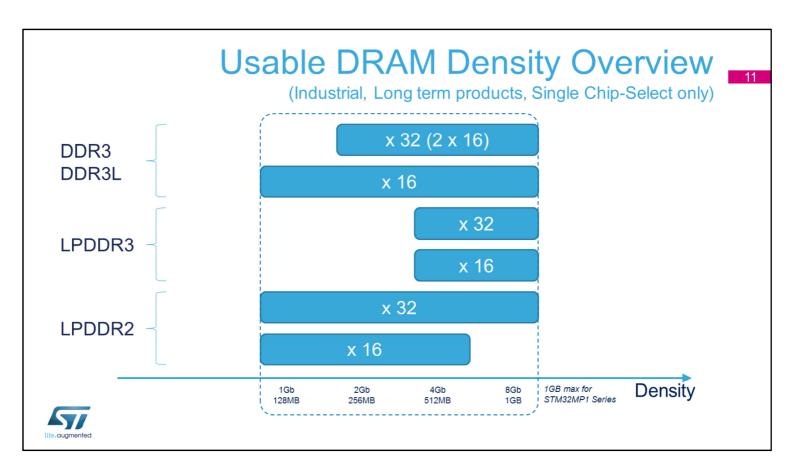

The STM32MP1 Series supports DDR3 or DDR3L memory devices in either 16-bit or 32-bit interface configuration (on some package only). As neither DDR3 nor DDR3L memory devices exist with a 32-bit interface, this configuration requires two devices which are using much PCB space. Package ball pitch is 0.8 mm which is adapted to industrial robustness.

LPDDR2 or LPDDR3 memory devices mostly exist in 32-bit versions and offer lower signal count than DDR3/DDR3L ones. The package is smaller, but the pitch can be 0.65mm, 0.5mm or below, requiring additional PCB cost.

STM32MP1 Series supports between 1 Gbit (128 Mbytes) and 8 Gbit (1 Gbyte) of DRAM memory.

# DDR interface PCB constrains (1/2)

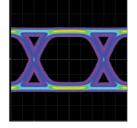

- All DDR DRAM uses rising & falling clock edge for data transmission

- 533MHz means one data sampled every 938 picoseconds

- DDR3 uses On Die Termination (ODT) to adapt impedance to the PCB connections (stripline)

- No ODT on LPDDR2 and LPDDR3 to save power, at the expense of additional signal integrity constrains

- DDR3 when used in x32-bits need two x16 devices, so Address/Command are routed to two packages

- Need termination resistors on Address/Command lines at mid-supply (VTT voltage)

- Both STM32MP15 and memory need a mid-supply reference (VREF)

- Very sensitive to noise, need to be carefully filtered

When designing a DDR system, DDR constrains must absolutely be taken into account. Refer to AN5031 and AN5122 for details.

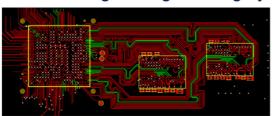

# DDR interface PCB constrains (2/2) 13

- Follow very carefully design guidelines, for example

- Constrained signals length (e.g. +/-500µm within all signals in a byte including DQS)

- Controlled impedance of PCB microstrips (e.g. 55  $\Omega$  single ended, 100  $\Omega$  differential)

- Differential routing of CLKP/CLKN, DQSP/DQSN

- · Low clock jitter

- Good supply decoupling and power planes

- STM32CubeMx provides a tool for tuning the DDR parameters as well as checking the signal integrity on the final target

STM32CubeMx provides a tool that helps tuning the DDR parameter sand checking the DDR signal integrity directly on the final target.

More details are provided in the ecosystem training part.

## Standards 14

- DRAM are specified by the following JEDEC standard

- · Standard interface and commands

- · Standard timings

- · Standard packages and ballout

- → JESD79-3F DDR3

- DDR3L → JESD79-3-1A (Addendum to DDR3)

- → JESD209-2B LPDDR2

- → JESD209-3C LPDDR3

All related DDR specifications are standardized thru JEDEC.

- Keys points

- External Flash are required in all SMT32MP1 Series systems

- DDR SDRAM are complex high speed devices and need careful PCB design

- DDR3L (1.35V) is recommended for cost and price sensitive solutions, while LPDDR2 or LPDDR3 are recommended when power is a concern

- LPDDR2 or LPDDR3 x32 are smaller than two DDR3L, but need higher cost PCB due to pitch 0.5mm

- STM32CubeMx will provide support for DDR parameter tuning on target

#### Recommended sizes

| Operating            |                     | Flash            | SDRAM              |            |  |

|----------------------|---------------------|------------------|--------------------|------------|--|

| system               | Minimun Recommended |                  | Minimun Recommende |            |  |

| Bare Linux           | 128 MBytes          | 2 GBytes or more | 128 MBytes         | 512 MBytes |  |

| Weston or<br>Android | 4 GBytes            | 8 GBytes or more | 512 MBytes         | 1 GByte    |  |

The keys points to remember from this presentations are:

- STM32MP1 Series always needs an external Flash memory device.

- External DRAMs such as DDR3/DDR3L or LPDDR2/LPDDR3 devices require a careful PCB design and signal integrity analysis

- STM32CubeMx helps to configure and validate the DDR memory on the final target

The recommended Flash or SDRAM size depends on the operating system configuration.

## Related documents 16

- Related documents

- AN5122 STM32MP1 Series DDR memory routing guidelines

- AN5031 Getting started with STM32MP1 Series hardware development

In addition to product Datasheet and Reference Manual, these two application notes are recommended before any design phase using the STM32MP1 microprocessor.