Hello, and welcome to this presentation of the STM32L5 comparators. It covers the main features of the ultra-low-power comparators and some application examples.

#### Overview

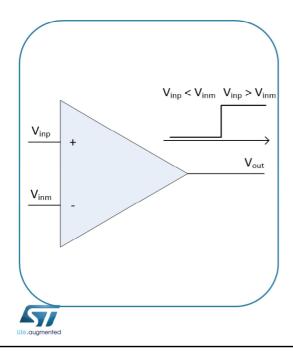

- Compares two analog signals and provides a digital output indicating which is larger

- Capability to wake up the CPU from LP modes

#### Application benefits

- Safety features such as the configuration lock or break event generator for timers

- Flexible I/O interconnections

- Hysteresis and speed vs. consumption configuration

The two comparators inside STM32 microcontroller provide a binary output which indicates if the analog voltage on the plus input is larger than the voltage on the negative input. It allows the MCU to react when the analog signal crosses a predefined threshold. The comparator continuously monitors voltage in contrast to an analog-to-digital converter which operates in sampled mode.

The comparator can be used to wake up devices from Sleep, Low-power sleep and Stop modes.

Applications can benefit from the flexible configuration of comparator properties which can be locked for safety reasons. Another safety feature of comparator is its ability to generate a break signal for timers allowing to safely stop the generation of PWM driving signals.

### Key features

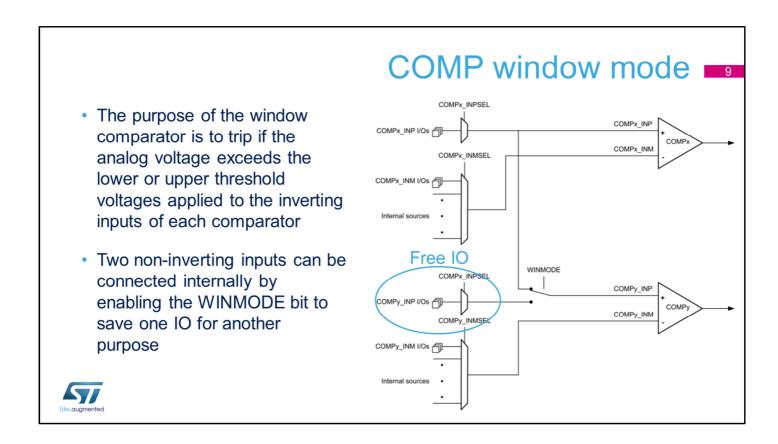

- Two independent comparators COMP1 and COMP2 can be combined to create one window comparator

- Programmable hysteresis and speed vs. consumption

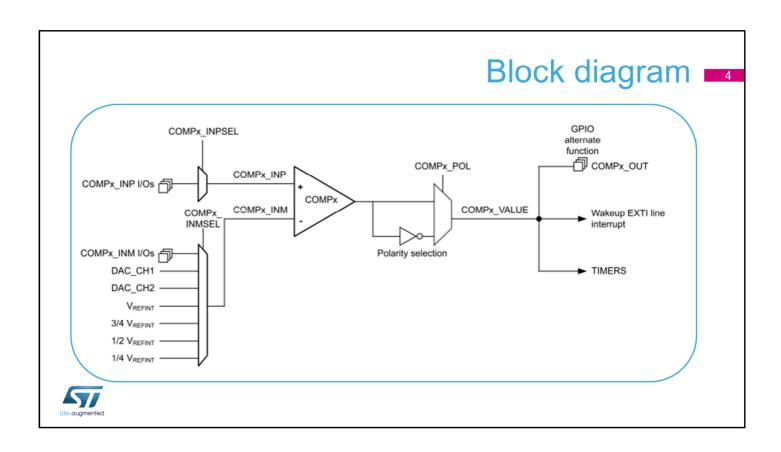

- Configurable plus and negative inputs

- Multiplexed I/O pins, DAC channels 1 and 2, internal reference voltage and its three submultiple values

- Output redirection

- · Configurable I/Os

- Timer break event for fast PWM shutdown, cycle-by-cycle current control, and input capture for timing measurements

- · Output blanking source

The two integrated comparators can be combined into a single window comparator.

The analog properties of the comparator include hysteresis or a trade-off between speed and power consumption are configurable.

It offers flexible inter-connections of inputs and outputs allowing a threshold selection of several external and internal inputs such as DAC outputs or internal reference voltage outputs.

The comparator output can be connected to I/Os using the alternate function channels or internally redirected to a variety of timer inputs such as enabling the break event for fast PWM shutdown. The user can create cycle-by-cycle current control or input captures for timing measurements.

This slide shows the general block diagram of the comparator integrated in the device.

### COMP low-power features in

- COMP1 and COMP2 power consumption versus propagation delay can be adjusted for the optimum trade-off for a given application

- There are three power modes available

- · HIGH SPEED and full power

- · MEDIUM SPEED and medium power

- · LOW SPEED and ultra-low power

The comparators' power consumption can be adjusted to have the optimum trade-off between the speed and energy efficiency for a given application.

There are three modes available: high speed, medium speed and ultra-low-power. The high speed mode would be preferred for power conversion applications - for example, a motor control design. While ultra-low power mode would be the right choice for battery-powered applications where reaction times are not critical - for example in PIR sensor monitoring.

The comparator can stay active even if the rest of the system is suspended and the clock is switched off.

# Interrupts i

| Interrupt event                | Description                                        |  |

|--------------------------------|----------------------------------------------------|--|

| Comparator output through EXTI | Configurable using rising or falling edges or both |  |

- · COMP output can trigger an interrupt through the EXTI line.

- COMP1 -> EXTI line 21

- COMP2 -> EXTI line 22

- EXTI lines can be configured to trigger on the rising, falling or both edges of the comparator output

The comparator can trigger an interrupt on the rising, falling or both edges of the comparator output through the EXTI line.

# Low-power modes

| Mode            | Description                                                                     |  |

|-----------------|---------------------------------------------------------------------------------|--|

| Run             | Active.                                                                         |  |

| Sleep           | Active. Peripheral interrupts cause the device to exit Sleep mode.              |  |

| Low-power run   | Active.                                                                         |  |

| Low-power sleep | Active. Peripheral interrupts cause the device to exit Low-power sleep mode.    |  |

| Stop 0/Stop 1   | Active. Peripheral interrupts cause the device to exit Stop0/Stop 1 mode.       |  |

| Stop 2          | Active. Peripheral interrupts cause the device to exit Stop 2 mode.             |  |

| Standby         | Powered-down. The peripheral must be reinitialized after exiting Standby mode.  |  |

| Shutdown        | Powered-down. The peripheral must be reinitialized after exiting Shutdown mode. |  |

The on-chip comparator remains active and can be used to wake up the device from all low-power modes except Standby and Shutdown.

### Performance & power consumption i

· Comparator consumption

| Conditions           | Static Typ.<br>(microamps) | Active <sup>(1)</sup> Typ.<br>(microamps) |

|----------------------|----------------------------|-------------------------------------------|

| Ultra-low-power mode | 0.35                       | 1.2                                       |

| Medium mode          | 5                          | 6                                         |

| High-speed mode      | 70                         | 75                                        |

(1) Propagation delay for step > 200 mV with 100 mV overdrive on positive inputs

Comparator propagation delay

| Conditions           | Typical<br>(microseconds) |  |

|----------------------|---------------------------|--|

| Ultra-low-power mode | 8                         |  |

| Medium mode          | 2                         |  |

| High-speed mode      | 0.1                       |  |

(1) Toggling with frequency of 50 kHz, ±100 mV overdrive square signal

The on-chip comparator configuration capability allows the user to select the best performance point for the targeted application. It replaces the external stand-alone comparator, thereby reducing the bill of materials.

The purpose of the window comparator is to trigger an interrupt if the analog voltage goes beyond the defined lower and upper voltage thresholds applied to the inverting inputs of each comparator. This event can generate an interrupt through the EXTI line. Two non-inverting inputs can be connected internally by enabling the WINMODE bit and therefore save one IO for another purpose.

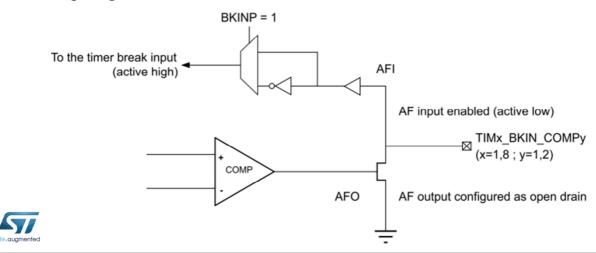

# COMP break signal generation in

Comparator (COMP1/COMP2) output values can generate break input signals for timers (TIM1 & TIM8) on input pins TIMx\_BKIN or TIMx\_BKIN2 by configuring the GPIO alternate function

Comparator output values can generate break input signals for the timers on input pins using GPIO alternate function selections incorporating the I/O open drain connection. The purpose of the break function is to protect power switches driven by PWM signals generated by timers. The two break inputs are usually connected to fault outputs of power stages and 3-phase inverters. When activated, the break circuitry shuts down the PWM outputs and forces them to a predefined safe state. Please see the timer training slides for more details.

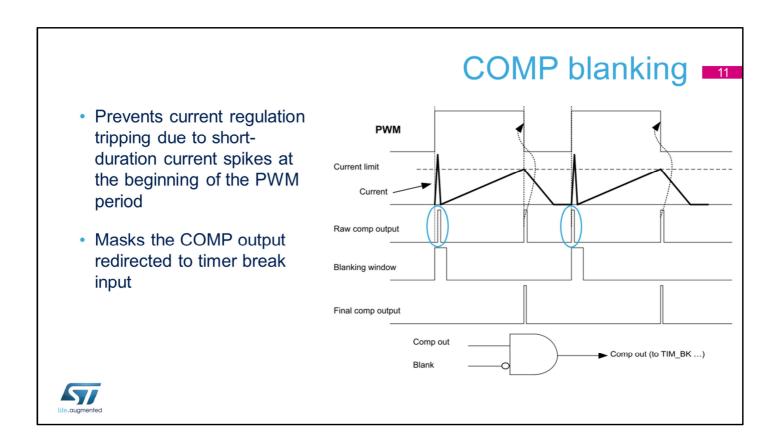

The comparator can be used in the cycle-by-cycle regulation loop for monitoring the peak value of the current flowing into the load. The purpose of the blanking function is to prevent incorrect current regulation tripping due to short duration current spikes at the beginning of the PWM period. Short current spikes caused by activating the power switches can produce false pulses on the comparator output – marked by the blue color on the diagram. These pulses need to be masked by a blanking window to avoid false fault detection. The blanking window waveform can be generated by one of the timer output channels.

### STM32L5 COMP differences 12

- · Both comparators have identical electrical parameters and configuration options.

- The only difference is the actual pin connections.

| External IO<br>assignment    | COMP1           | COMP2      |

|------------------------------|-----------------|------------|

| Input minus<br>IO assignment | PB1 or PC4      | PB3 or PB7 |

| Input plus<br>IO assignment  | PC5 or PB2, PA2 | PB4 or PB6 |

Both comparators have identical electrical parameters and configuration options. The difference in input interconnections are summarized in this table. For the difference in output redirections, please refer to product datasheet.

# Related peripherals 13

- Refer to these peripheral trainings linked to this peripheral

- Reset and clock control Reset and clock control (COMP clock control, COMP enable/reset)

- Interrupts (COMP interrupt mapping)

- Timers (COMP output redirection, break function)

- General-purpose inputs/outputs General-purpose inputs/outputs (COMP input/output pins)

- · Digital-to-analog converter

This is a list of peripherals related to the comparators. Please refer to these peripheral trainings for more information if needed.

Thank you.