Hello, and welcome to this presentation of the STM32 Display Serial Interface (DSI) Host. It covers the features of this interface, which is used for connecting graphical displays to the microcontroller.

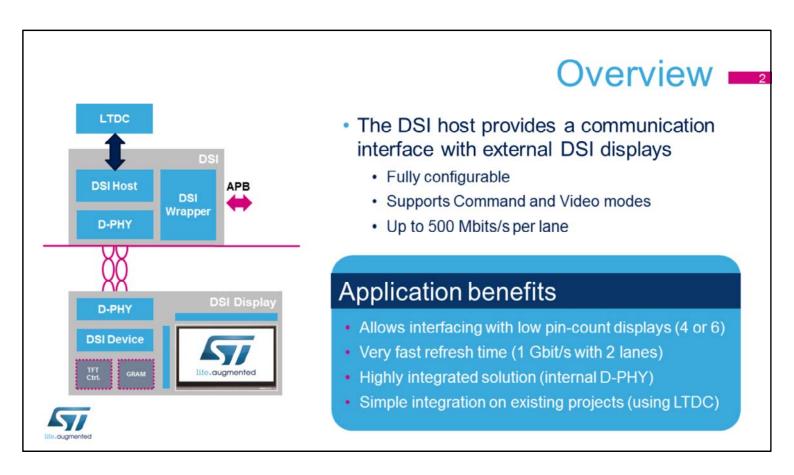

The DSI Host integrated inside STM32 microcontrollers provides a high-speed communication interface allowing the microcontroller to communicate with a display with a reduced pin count. This interface is fully configurable, making it easy to connect DSI displays available today on the market.

Applications benefit from the easy connection and reduced pin count.

### Flexible operating modes to efficiently support all display types

- Three operating modes

- · Video mode

- APB Command mode

- · Adapted Command mode

- Very fast transfers up to 1Gbit/s (500 Mbits/s per lane)

- User selects the number of data lanes (up to 2)

- · Number of pins fits exactly with the bandwidth requirement

- Deeply integrated with LTDC

LTDC remains the "streamer" and feeds the DSI Host

The DSI Host integrated inside STM32 microcontrollers offers three operating modes and is optimized for communication with graphical displays with a reduced pin count up to a 1Gbit/s. The number of data lanes is configurable to fit exactly with the application's needs. The DSI Host is deeply integrated with the LCD-TFT display controller (LTDC) to ease application development and porting.

## Operating modes

### Flexible operating modes to support efficiently all display types

- Video mode

- DSI Host sends LTDC output, including HSYNC and VSYNC signals over DSI (streaming)

- APB Command mode

- DSI Host sends DCS or custom commands over DSI (similar to serial LCDs with SPI or FMC interface)

- · Commands are launched using DSI Host APB interface

- Adapted Command mode

- DSI Host captures one full LTDC frame and transforms it automatically to a series of DCS commands to update the display's Graphics RAM (as previously done through SPI or FMC)

- · Most efficient way to manage Graphics RAM updates

Three operating mode are available to convey the graphical data to the display:

- Video mode streams over the high-speed link the RGB data and the associated synchronization signals directly generated by the LTDC. The streaming starts as soon as the DSI Host and the LTDC are enabled. This continuous refresh is the best way to interface with a display without Graphics RAM (GRAM ["G" "RAM"]).

- APB command mode sends commands over the highspeed link for configuration as it is done using a legacy serial interface (SPI, FMC). The commands are launched using the DSI Host APB interface.

- Adapted command mode is the best way to interface with a display having its own internal Graphics RAM.

The DSI Host captures only one full frame coming from the LTDC and transforms it into a series of write

commands to update the display Graphics RAM. This one-shot refresh automatically sets a control bit in the DSI Host.

#### Several video modes for efficient bus usage

- For Video mode, DSI supports the following operating modes:

- Non-Burst mode with sync pulses: Enables the peripheral to accurately reconstruct original video timing, including sync pulse widths

- · Non-Burst mode with sync event: Similar to above, but accurate reconstruction of sync pulse widths is not required, so a single sync event is substituted.

- · Burst mode: RGB pixel packets are time-compressed, leaving more time during a scan line for lowpower mode (saving power) or for multiplexing other transmissions onto the DSI link.

- A host supports all the 3 modes, but a display is only required to support at least one

The DSI Host's Video mode supports the three operating modes defined by the Mobile Industry Processor Interface (MIPI) DSI specification:

- Non-Burst with sync pulse: where the synchronization signal and the data are sent accurately enabling the target display to reconstruct the original video timings, including synchronization pulse widths without any buffering.

- Non-Burst with sync event mode is similar to the previous mode but for displays not requiring synchronization pulse width information.

- Burst mode is the most energy-efficient mode. RGB pixel packets are time-compressed, leaving time during a line transmission to go into low-power mode or to transmit other commands.

The DSI Host must support all three modes. A display is only required to support at least one of these three modes.

## APB Command mode —

### Sends commands through DSI Host APB registers

- APB interface for transfer operations

- · Sends DCS (Display Command Set) or generic commands

- · Used for display configurations and/or maintenance

- · Can be sent in High-Speed or Low-Power

- · Some displays only accept low-power during initialization phase

- · Each type of command packet can be configured in LP/HS

- Command can be sent during video transmission if the DSI host has time between two video packets

- · Scheduling is based on the timing programmed in the DSI Host registers.

- All commands are listed in the DCS specification (pure software)

- Generic commands (non-DCS) can be implemented (see the display specification)

APB Command mode is used to send commands through the DSI Host APB register interface.

Generic or Display Command Set (DCS) commands can be sent for display configuration at startup or for maintenance operations when the application is running.

All the commands can be sent either in high-speed or in lowpower modes as some displays only accept low-power communication at startup.

Commands can also be sent during video streaming: the DSI Host scheduler automatically evaluates if it has the sufficient time to insert a command during a video transmission according to the programmed timings.

All the commands are fully programmable by software, which means the DSI Host supports all the standard DCS commands and all the display-specific custom commands.

## Adapted Command mode —

## Automatic GRAM refresh mode with LTDC! No CPU nor DMA needed

- Graphics RAM refresh transfer operations

- · Used in conjunction with LTDC

- · The DSI Host controls the LTDC and enables it for 1 frame

- The RGB data from the LTDC are written within DCS long write command packet

- · Once refresh is done, the LTDC is stopped and the DSI link goes back to LP-Stop

- · Most efficient way to update Graphics RAM

- The user controls the refresh of the display by just setting one bit when the host-side frame buffer is ready

- The display can be refreshed at the maximum speed of the link

Take care of potential bandwidth limitations at the input of the LTDC

Adapted Command mode is a highly optimized operating mode to interface with displays having their own graphics RAM.

It automatically refreshes the display's Graphics RAM (GRAM) with the LTDC without any load on the CPU or DMA controller.

The Graphics RAM refresh operation works in conjunction with the LTDC:

- The DSI host controls the LTDC and enables it for 1 frame.

- The RGB data coming from the LTDC are captured and are sent into a series of DCS long write command packets to the display.

- Once the Graphics RAM is completely refreshed, the DSI Host automatically stops the LTDC and the DSI link goes into Low-power Stop mode.

The user controls the refresh operation of the display by

just setting one bit when the frame buffer is ready to be sent.

The display can be refreshed at the maximum speed of the link so special attention must be given on the bandwidth requirement on the LTDC side (e.g., memory bandwidth to read the frame buffer).

# Tearing effect management •

### Easy synchronization of GRAM refresh

- In Adapted Command mode, Tearing Effect signaling allows a perfect synchronization with the display for refresh operations

- TE over the link

- Once DCS SET\_TEAR\_ON command is issued through the APB Command mode interface, the DSI Host gives the bus control to the display

- Once the programmed scan line is reached, the display sends a Tearing Effect trigger and gives the bus control to the DSI Host

- · An interrupt is raised, and the user can launch a GRAM refresh

- TE over a pin

- The pin toggles when the programmed scan line is reached

- An interrupt is raised, and the user can launch a GRAM refresh

The tearing effect allows a perfect synchronization between the display and the DSI Host for refresh operations on displays having their own Graphics RAM.

The tearing effect can be signaled in two ways:

- Over the link without an additional pin,

- Or using an additional pin.

When the tearing effect is signaled over the link, the DSI host sends a SET\_TEAR\_ON command and gives the control of the bus to the display. Once the programmed scan line is reached by the display, it sends a trigger to the DSI Host and gives control of the bus back to the DSI Host.

An interrupt can be raised to launch the Graphics RAM refresh.

When the tearing effect is signaled over a pin, the

8

display toggles a dedicated GPIO to trigger the DSI Host when the programmed scan line is reached. Although an additional pin is required, this mechanism avoids having multiple exchanges over the link between the DSI Host and the display.

An interrupt can be raised on the pin toggling the launch the Graphics RAM refresh.

## Video mode vs Command mode -

### Adapted Command mode is preferred from an MCU standpoint

#### Video mode

- Lower cost display controller on display side

- But keeps the same constraints as today on LTDC

- · Image calculation in the same time as image streaming

- Usually need an external SRAM/SDRAM because of double buffering

- · High bandwidth on FMC

#### Adapted Command mode

- Slightly higher cost display controller on display side

- More integrated solution

- · Only one frame buffer needed on MCU side: frame buffer can often fit in the internal MCU

Image calculation and GRAM update are not occurring at the same time: no bottleneck

The choice between Video or Adapted Command mode has a big impact on the solution's architecture and cost.

From the MCU standpoint, Adapted Command mode is preferred for cost-optimized solutions.

As Video mode does not require Graphics RAM on the display side, this solution is often used for large displays which reduces cost. The constraints in term of bandwidth and memory usage on the MCU side remains the same as for today's LTDC-based solutions. Most of the time an external RAM is required for double-buffering of the frame buffer.

Adapted command mode requires a display with a Graphics RAM. The display may have a slightly higher cost, but most of the displays smaller than 480 by 480 pixels embed a Graphics RAM. As a consequence,

Adapted Command mode with a small display will not always require an external RAM as the frame buffer may fit in the internal MCU RAM. This highly reduces the bandwidth issues on the MCU and reduces the overall BOM cost and solution integration as no external RAM is required.

## Summary •••

#### Video and Command modes over DSI

- · Supports Video mode operating mode

- · Timing accurate streaming

- · Burst mode for consumption reduction

- All RGB color modes supported (RGB565/666/888)

- · Support classical commands with APB interface

- · Simple DCS or custom command issuing to the display

- · For display configuration at startup

- Support Adapted Command mode

- · Most efficient way to update a GRAM

- Only one bit to set to update a GRAM!

The DSI Host supports Video mode operation with:

- Timing accurate streaming

- Burst mode to reduce consumption during blanking periods

- Several RGB color encoding formats to optimize bandwidth usage

The DSI Host supports commands through its APB interface:

- DCS or generic commands can be issued to the display even when Video mode is working

- Commands are used for display configuration at startup and also for maintenance operations when the application is running

The DSI host can also use Adapted Command mode to update a display's Graphics RAM without having to use the CPU or DMA controller. This mode works using the LTDC to transmit write commands to the display.

## Performance ==

### **Equivalent Pixel Clock**

- Relationship between DSI bandwidth and LTDC Pixel clock

- · Depends on the color coding of the targeted display (bpp)

- Equivalent LTDC clock: 1 Gbit/s / 16 bpp = 62.5 MHz in 16 bpp

- Equivalent LTDC clock: 1 Gbit/s / 24 bpp = 41.5 MHz in 24 bpp

- Application example

- · 200 MHz DSI with 1 data lane ~200 Mbit/s bandwidth

- For a 16 bpp display, PCLK = 200/16 ~ 10 MHz (~400x400 / 60 Hz)

- 500 MHz DSI with 2 data lanes ~ 1 Gbit/s bandwidth

- For a 24 bpp display, PCLK = 1000/24 ~ 40 MHz (~800x600 / 60 Hz)

In terms of performance, there is a relationship between the equivalent pixel clock and the DSI Host configuration.

Depending on the color coding, the number of data lanes used and the speed of the data lanes, we can evaluate the equivalent pixel clock.

As an example, when using two lanes at 500 Mbits/s (pronounced Mega bit per second) for a total of 1 Gbit/s (pronounced Giga bit per second), we have a maximum equivalent pixel clock of 62.5 MHz (pronounced Megahertz) for a 16 bits per pixel coding and 41.5 MHz for a 24 bits per pixel coding.

In terms of the application, we can have, for example, a small 400 by 400 pixel display running on a single 200 Mbits/s lane at 16 bits per pixel or a large 800 by 600 pixel display at 24 bits per pixel running on both data lanes at 500 Mbits/s each.

#### **Equivalent Pixel Clock**

- The DSI Host has interrupt sources for all the events which could occur on the link in the controller

- Refer to the reference manual for a detailed description

- The DSI Host generates additional interrupts for

- Regulator events

- PLL events

- · Tearing Effect events

- No DMA request is necessary for the DSI Host as it works with the LTDC (which has its own DMA master)

The DSI Host has many interrupts to monitor all the timings and events of the communication. Please refer to the reference manual for a detailed description of all the interrupt sources.

In addition to protocol-related interrupts, the DSI Host also provides interrupts to manage:

- Regulator events,

- PLL events,

- Tearing effect events.

As the DSI Host uses the LTDC for data fetching, no DMA controller is necessary (the LTDC has its own DMA master).

# Low-power modes **13**

| Mode    | Description                                                                    |

|---------|--------------------------------------------------------------------------------|

| Run     | Active.                                                                        |

| Sleep   | Active. Peripheral interrupts cause the device to exit Sleep mode.             |

| Stop    | Frozen. Peripheral registers content is kept.                                  |

| Standby | Powered-down. The peripheral must be reinitialized after exiting Standby mode. |

The DSI Host is active in Run and Sleep modes. A DSI Host interrupt can cause the device to exit Sleep mode. In Stop mode, the DSI Host is frozen and its register content is kept. In Standby mode, the DSI Host is powered-down and it must be reinitialized afterwards.

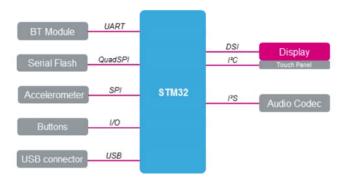

# Application examples -14

- · Applications including connectivity and user interface:

- 400x400 / 24 bpp display with embedded GRAM (no need for external RAM)

- · QSPI to store graphical primitives

Wearable applications require low-power management functions together with a high-quality user interface. This can be achieved using the DSI Host to interface with a display through only 4 or 6 pins. The low pin-count needed to drive such devices allows for a highly optimized system integration.

# Related peripherals ==15

- Refer to these peripheral training modules linked to this peripheral:

- · RCC (DSI clock control, DSI enable/reset)

- Interrupts (DSI interrupt mapping)

- · GPIOs (DSI input for tearing effect)

- LTDC (DSI pixel source, timing control)

You can refer to the training slides related to RCC, interrupts, LTDC, and GPIOs for additional information.