Hello and welcome to this presentation of the STM32G4 Analog-to-Digital Converter block. It will cover the main features of this block, which is used to convert analog voltages, like sensor outputs, to digital values for further processing in the digital domain.

### Overview 2

- Provides analog-to-digital conversion

- Five 12-bit ADCs with up to 42 input channels

- Oversampler

- 4 Msample/s maximum (12-bit resolution)

- Three analog watchdogs per ADC

- DMA request generation

- · Interrupt generation

### Application benefits

- Ultra Low power consumption

- Flexible trigger, data management to offload CPU

The analog-to-digital converter inside the STM32G4 microcontroller allows the microcontroller to accept an analog value like from a sensor output and convert the signal for use in the digital domain.

There are 42 analog inputs available across the five **ADCs**

The oversampling unit preprocesses the data to offload the main processor. It can handle multiple conversions and average them into a single data with an increased data width, up to 16 bits.

The ADC module itself is a 12-bit successive approximation converter with additional oversampling hardware.

The sampling speed is 4 mega sample per second for 12-bit resolution.

The data can be made available to the software either through DMA transfers or interrupts.

This ADC is designed for low power and high performance.

There are a number of triggering mechanisms and the data management can be configured to minimize the CPU workload.

The ADC module also integrates an analog watchdog.

### Key features

| Features           | Description                                                                                                                            |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ADC units          | 5 modules                                                                                                                              |  |  |

| hput channel       | Up to 42 external (GPIOs) single or differential and 3 internal channels                                                               |  |  |

| Type of conversion | 12-bit successive approximation                                                                                                        |  |  |

| Conversion time    | Min 15 ADC clock cycles  > 200 ns when f <sub>ACC_CLK</sub> = 60 MHz, 12-bit resolution > 4.0 Msamples/s                               |  |  |

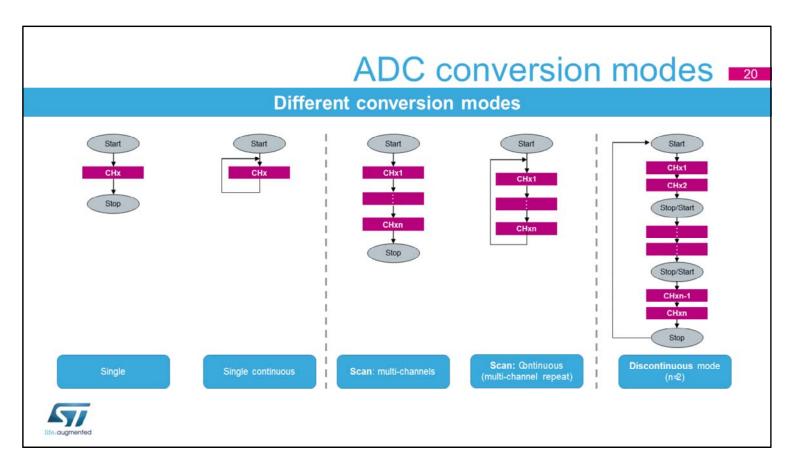

| Functional mode    | Single, continuous, scan, discontinuous or injected                                                                                    |  |  |

| Triggers           | Software or external trigger (Timers & Ds)                                                                                             |  |  |

| Special functions  | Hardware o versam bing, analog watchdogs (+ filter), data peconditioning (Offset and gain compensation), flexible sampling time        |  |  |

| Data processing    | hterrupt generation and DMA requests                                                                                                   |  |  |

| Low-power modes    | Deep power-down, auto-delayed conversion mode, speed adaptive low-power mode to reduce ADC consumption when operating at low frequency |  |  |

5 analog-to-digital converters are integrated inside STM32G4xx products.

The input channel is connected to up to 42 channels capable of converting signals in either Single-end or Differential mode.

The ADCs can convert signals at 4 mega sample per second in 12-bit mode when ADC clock frequency is 60 MHz.

There are several functional modes which will be explained later.

There are also several different triggering methods. In order to offload the CPU, the ADC has an analog watchdog for monitoring thresholds. The analog watchdog has new filtering features.

The ADC also offers oversampling to extend the number of bits presented in the final conversion value.

Also there is new flexible sampling time control and new

gain and offset compensation. For power-sensitive applications, the ADC offers a number of low-power features.

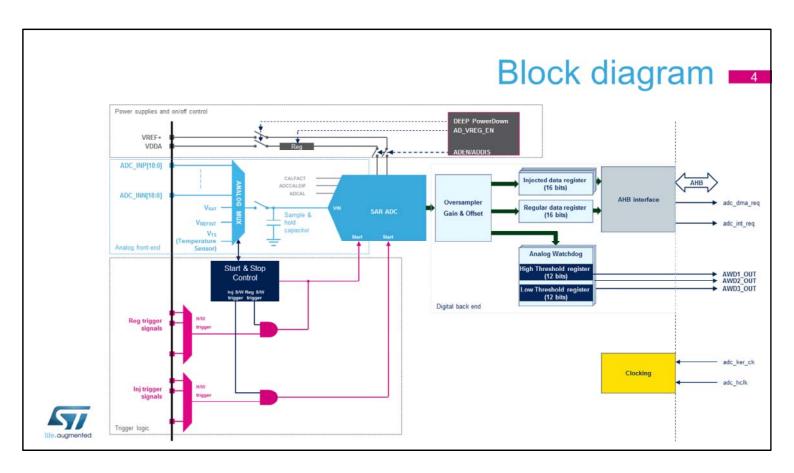

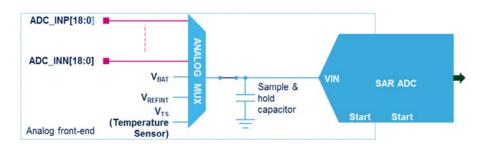

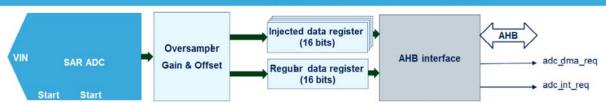

This slide shows the general block diagram of the ADC. The main important sub-units of the ADC are:

- The power supplies and on/off control

- · The analog front-end

- The trigger logic

- The digital back-end including the analog watchdogs and the AHB slave interface

- The clocking.

The next slides detail all these sub-units.

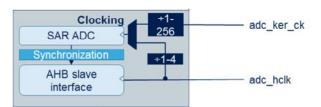

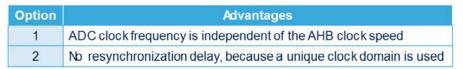

#### Clocking

- The ADC implements a dual clock domain architecture

- The user has to select the root clock used to obtain the ADC clock

- Option 1: adc\_ker\_ck, typically the P output of the PLL, divided by a programmable factor (1 to 256)

- Option 2: the AHB clock, divided by a programmable factor (1, 2 or 4)

The ADC has two clock inputs: adc\_ker\_ck and adc\_hclk.

The AHB interface belongs to the adc\_hclk clock domain. Regarding the digital part of the SAR ADC, there are two options:

- Either using adc\_hclk as the reference clock

- Or using adc\_ker\_ck, which is dedicated and independent of adc\_hclk.

With this second option, dynamic frequency scaling can be implemented in the AHB and CPU clock domain, while the sampling clock is fixed.

However samples acquired in the adc\_ker\_ck clock domain have to pass to the AHB clock domain to be read by CPU or DMA, which requires a synchronization delay. An uncertainty of the trigger instant is also added by the resynchronizations between the two clock domains.

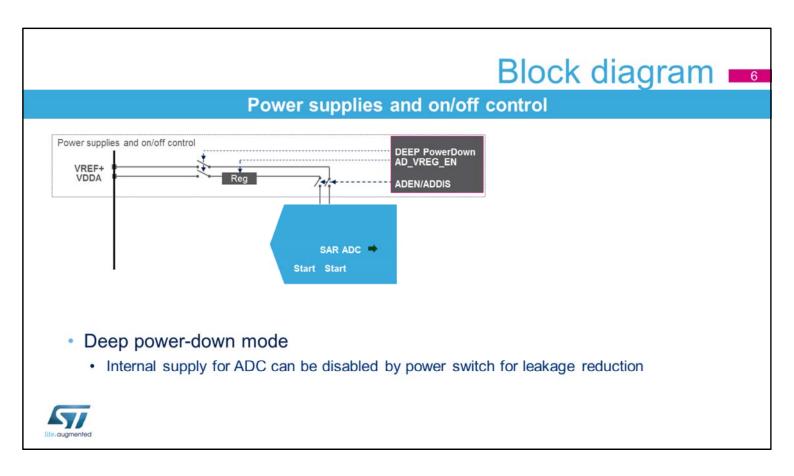

The analog part of the ADC needs two power supplies:

- VREF+ which is the positive analog reference

- And VDDA which is the analog power supply.

By default, the ADC is in deep-power-down mode, where its supply is internally switched off to reduce the leakage currents.

To start ADC operations, it is first needed to exit Deeppower-down mode by setting the DEEP PowerDown bit to zero.

It is possible to save power by also disabling the ADC voltage regulator. This is done by writing bit ADVREGEN to zero.

Setting ADDIS to one disables the ADC. ADEN and ADDIS are then automatically cleared by hardware as soon as the analog ADC is effectively disabled.

### Block diagram

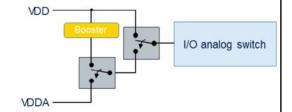

#### Power supplies and on/off control, IO voltage booster

- IO analog switch voltage booster

- Analog switch resistance increases when VDDA is decreasing

- For low VDDA, analog switch resistance can be minimized by enabling internal voltage booster to control the switch

- The recommended analog switch supply is as follows:

| VDD    | VDDA   | BOOSTEN | ANASWVDD | Analog switch supply |

|--------|--------|---------|----------|----------------------|

| -      | >2.4 v | 0       | 0        | VDDA (default)       |

| >2.4 v | <2.4 v | 0       | 1        | VDD                  |

| <2.4 v | <2.4 v | 1       | 0        | Voltage booster      |

- 1: I/O analog switches supplied by VDD

- 0: I/O analog switches supplied by VDDA or booster

BOOSTEN

1: I/O analog switches are supplied by voltage booster

0: I/O analog switches are supplied by VIDA

The analog switch inside the IO has a resistance which increases when the analog switch supply decreases. So for cases where VDDA and VDD are low, there is a possibility to enable a voltage booster which will supply the analog switch and guarantee low resistance.

The recommended supply for the analog switch is to use VDDA.

But when VDDA is lower than 2.4 Volt and VDD is larger than 2.4 Volt, the power supply can be switched to VDD. If both VDDA and VDD are lower than 2.4 Volt. the voltage booster should be enabled.

#### Power supplies and on/off control, Internal voltage reference VREFBUF

- Analog voltage reference Vref can be provided either externally or internally through the voltage reference VREFBUF

- · Three voltages are available: 2.048V, 2.5V, 2.9V

- Available only in packages with Vref+ pin available

- Even if VREFBUF is used, it is still needed to place decoupling capacitors to Vrefp pin

It is possible to provide the internal reference voltage Vref internally using the VREFBUF.

Three voltage levels are available.

This can be used only when there is a Vref pin in the package (all packages except 32-pin STM32G431 UFQFPN32 and LQFP32 packages)

Even when Vref is provided by internal VREFBUF, decoupling capacitors have to be connected externally to the Vref pin.

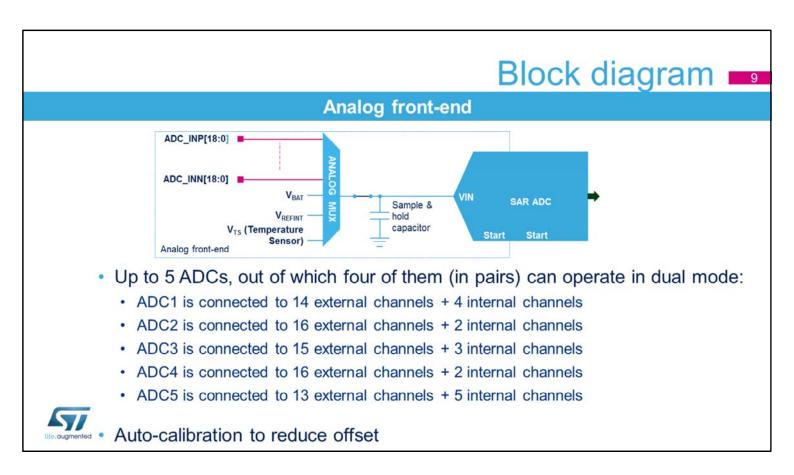

The STM32G4 supports up to 5 ADCs.

Each of them is connected to external analog channels and internal analog sources.

The internal channels are:

- The internal reference voltage (VREFINT)

- The internal temperature sensor (VSENSE)

- The VBAT monitoring channel (VBAT/3)

- OPAMP1,2,3,4,6 connected to various ADCs, which are not represented in the figure.

Note that analog inputs can be configured to be singleended or differential.

The ADC offers an auto calibration mechanism. Calibration is preliminary to any ADC operation. It removes the offset error which may vary from chip to chip due to process, supply voltage or temperature variation.

Single ended inputs and differential inputs are calibrated

separately according to the state of the ADCCALDIF bit value.

Software can request a calibration by setting the ADCAL bit to one.

The resulting calibration factor can be read from ADC\_CALFACT register.

It is recommended to run the calibration on the application if the reference voltage changes more than 10% so this would include emerging from RESET or from a low power state where the analog voltage supply has been removed and reestablished.

High temperature excursion may also require to run the offset calibration.

# ADC internal channels -

### **Analog front-end**

|                           | ADC1         | ADC2                       | ADC3         | ADC4         | ADC5                     |

|---------------------------|--------------|----------------------------|--------------|--------------|--------------------------|

| Temperature sensor        | IN16         | -                          | -            | -            | IN4                      |

| VBAT/3                    | IN17         | -                          | IN17         | -            | IN17                     |

| VREFINT                   | IN18         | -                          | IN18         | IN18         | IN18                     |

| OPAMPx internal output († | IN13 (x = 1) | IN16 (x = 2), IN18 (x = 3) | IN13 (x = 3) | IN17 (x = 6) | IN3 (x = 5), IN5 (x = 4) |

<sup>(\*)</sup> Internal OPAMP to ADC connection without external pin occupancy

This table indicates which are the internal analog channels for the five ADCs.

###

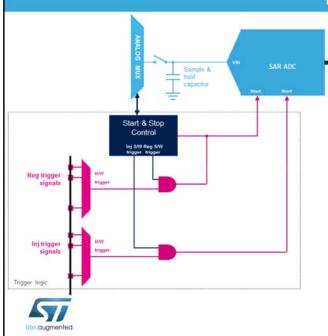

#### Trigger logic

- A flexible sequencer organizes the conversions in 2 groups: regular and injected

- · A group consists of a sequence of conversions that can be done on any channel and in any order

- · A regular group is composed of up to 16 conversions

- · The regular channels and their order in the conversion sequence must be selected in the ADC SQRy registers

- An injected group is composed of up to 4 conversions

- · The injected channels and their order in the conversion sequence must be selected in the ADC\_JSQR register

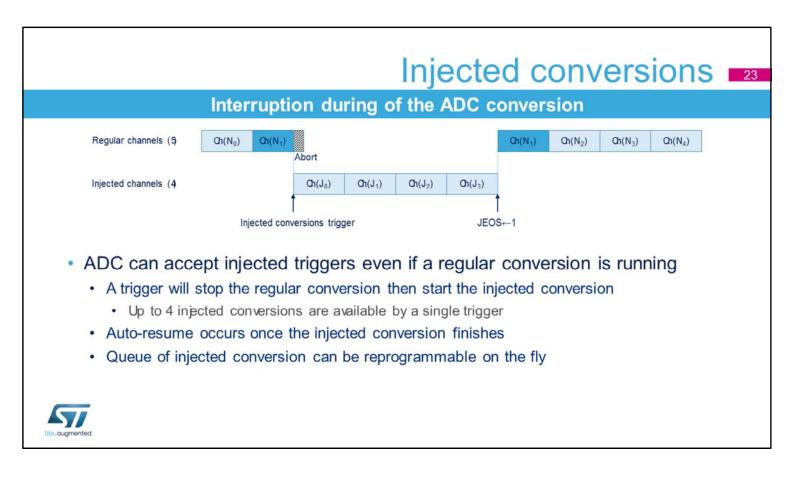

Conversions are organized in two groups: the regular group and the injected group.

The injected group can pre-empt the execution of the regular group sampling sequence.

The user is in charge of selecting the size of each group, maximum 16 acquisitions in the regular group and 4 in the injected group.

They also have to assign the analog channels for each sampling within the sequence.

Each group has its own trigger logic.

The trigger can be an external signal, coming from GPIOs or timer outputs.

A sequence of acquisition can also be triggered by software.

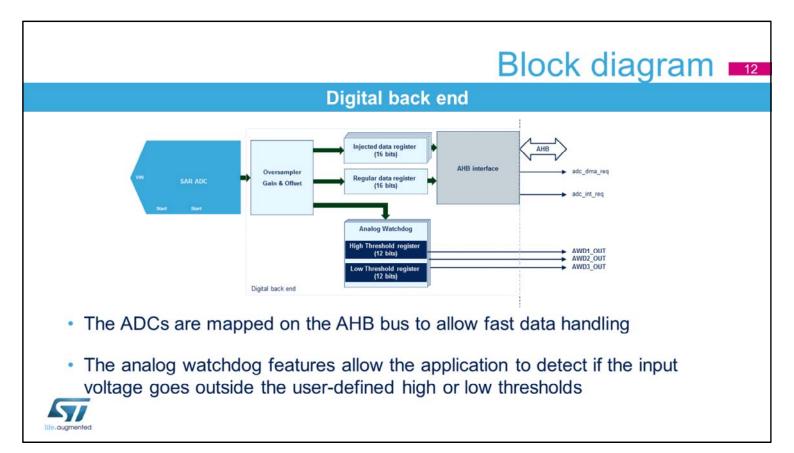

The digital back-end performs processing on the samples obtained in the SAR ADC in the over-sampler, gain & offset unit.

Raw samples maybe processed by the oversampler, gain and offset compensation units before being provided to the software.

The results are then stored into registers, that are accessible from the AHB slave interface.

AHB supports a higher bandwidth and minimizes latency, because the CPU and DMA are also connected to the AHB interconnect.

The ADC is able to assert a request to the DMA, so that samples coming from regular channels are automatically moved to memory.

Injected channels do not support DMA requests.

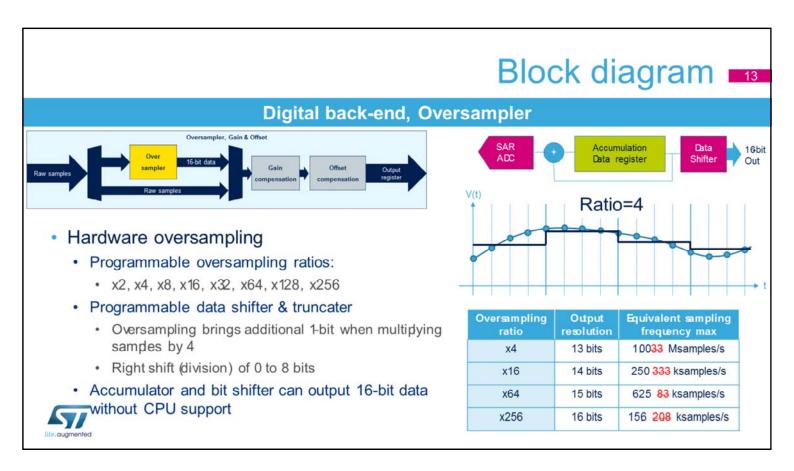

The ADC includes the oversampling hardware which accumulates data and then divides without CPU assistance.

The oversampler can accommodate from 2 to 256 time samples and right shift from one to eight binary digits. 12-bit data can be extended to be presented as 16-bit data.

This functionality can be used as an averaging function or for data rate reduction and signal-to-noise ratio improvement as well as for basic filtering.

## Block diagram 14

#### Digital back-end, Oversampler, Gain compensation

- Gain compensation

- · Improves the dynamic range of the ADC even when the input range is not aligned with the reference voltage

- Applying a gain factor helps extend the signal range to map it to the full ADC range

- · It is applied on all converted data (all channels) after oversampling shift

- Gain factor = (ADC GCOMP.GCOMPCOEFF[13:0]) /4096

- · The gain factor can range from 0 to 3999756

- · After each conversion Data is computed with following formula

DATA = DATA(adc result) x (GCOMPCOEFF[13:0]) /4096

A gain factor can be applied to the raw samples in order to improve the dynamic range.

The gain factor is performed after the oversampling. It is programmable in the range 0 to almost 4.

### Block diagram 15

#### Digital back-end, Offset saturation control

- Offset compensation

- Channel dependent offset compensation (up to 4 channels)

- Channel selection set in ADC\_OFRy.OFFSETy\_CH[4:0]

- Offset value is set by programming ADC OFRy.OFFSETy[11:0]

- Offset can be positive or negative (ADC\_OFRy.OFFSETPOS)

- Saturation control can be enabled by (ADC OFRy.SATEN) to prevent overflow

- · Data will be unsigned and saturate at 0x000 for negative offset and at 0xFFF for positive offset

- DATA = DATA(gain result) +/- OFFSETy[11:0]

Offset correction is not supported in oversampling mode

An offset y (y=1,2,3,4) can be applied to a channel by setting the bit OFFSETy\_EN=1 into ADC\_OFRy register. The channel to which the offset will be applied is programmed into the bits OFFSETy\_CH[4:0] of ADC OFRy register.

In this case, the converted value is decreased by the user-defined offset written in the bits OFFSETy[11:0]. The result may be a negative value so the read data is signed.

#### Several low-power features are implemented

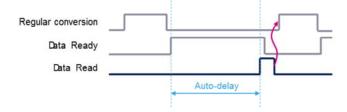

- Auto-delay mode

- A new conversion can start only if the previous data has been processed, once the ADC DR register has been read or if the EOC bit has been cleared for regular conversions

- · There is no delay inserted between each conversions of the injected sequence, except after the last one

- Power consumption from VDDA depends on sampling time

- 590 µA @ 4 Msample/s 16 µA @ 10 ksamples/s

When auto-delay mode is active, the ADCs wait until the last conversion data is read or the end-of-conversion flag is cleared before starting the next conversion.

This is a way to automatically adapt the speed of the ADC to the speed of the system which will read the data. This also avoids unnecessary conversions and thus reduces power consumption.

This Auto-delay mode does not apply to Injected conversions, except the last one when switching back to the regular conversions.

Power consumption from VDDA power supply depends on sampling time: from 16 µA at 10 Kilo samples per second to 590 µA at 4 mega samples per second. For low sampling rates, the current consumption is reduced almost proportionally.

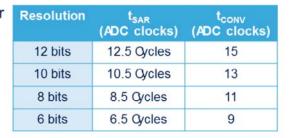

#### Conversion speed is resolution dependent

- t<sub>CONV</sub> = Sampling time + Conversion time

- ADC needs minimum 2.5<sub>ADC CLKs</sub> for sample period and 12.5<sub>ADC CLKs</sub> for conversion (12-bit resolution)

- 60 MHz maximum clock with 15-cycle results in 4.00 Msamples/s

- 7.0 Msamples/s in dual interleaved mode

- The maximum frequency is depends on the number of instance activated, please consult datasheet.

- Speed up by low resolution

- 12-bit: 12.5<sub>ADC CLKs</sub>(+2.5) => 4.00 Msamples/s

- 10-bit: 10.5<sub>ADC CLKs</sub> (+2.5) => 4.61 Msamples/s

| 8-bit: 8.5 <sub>ADC_CLKs</sub> | (+2.5) | => 5.45 | Msamples/s |

|--------------------------------|--------|---------|------------|

|--------------------------------|--------|---------|------------|

6-bit: 6.5<sub>ADC CLKs</sub> (+2.5) => 6.66 Msamples/s

The global conversion time is equal to the sampling time plus the conversion time.

The ADC needs a minimum of 2.5 clock cycles for the sampling and 12.5 clock cycles for conversion for 12-bit mode.

With a 60 MHz ADC clock, it can achieve 4 mega sample per second.

For a higher sampling speed, it is possible to reduce the resolution down to 10, 8 or 6 bits.

When associating a master and a slave ADC, the interleaved mode maximum performance is one sample every 8 clocks, so 7 Mega sample per second at 56 MHz.

### Sampling times <a>18</a>

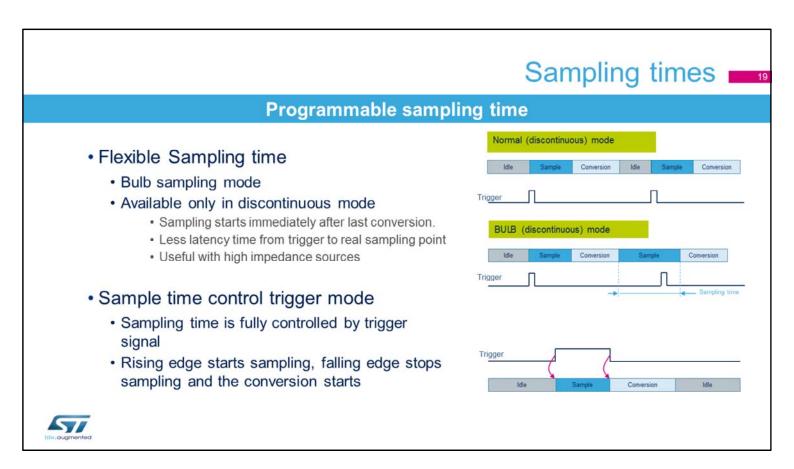

### Programmable sampling time

- Before starting a conversion, the ADC must establish a direct connection between the voltage source under measurement and the embedded sampling capacitor of the ADC

- · One ADC can scan the different input source with various source impedances

- · Each channel can be sampled with a different sampling time which is programmable

- · The following sampling times are supported:

2.5 cycles, 6.5 cycles, 12.5 cycles, 24.5 cycles, 47.5 cycles, 92.5 cycles, 247.5 cycles, 640.5 cycles

The first set of a conversion consists in loading the Sample & Hold capacitor with the voltage to be measured.

Longer sample times ensure that signals having a higher impedance are correctly converted.

The sampling times listed in this slide in ADC clock cycles are available.

The sampling time can be programmed individually for each input channel of the analog-to-digital converters.

Two new sampling mechanisms have been introduced. The first one is the bulb mode which works only in discontinuous mode.

In this mode, sampling starts immediately after last conversion finishes without going to idle state. This will provide less latency from the trigger signal to the start of conversion.

The very first ADC conversion, after the ADC is enabled, is performed with the sampling time programmed in SMP bits.

The Bulb mode is effective starting from the second conversion.

The second mechanism is the sampling mode based on trigger signal.

- Rising edge starts sampling.

- Falling edge stops sampling and the conversion starts.

#### The ADC supports several conversion modes:

- Single mode, which converts only one channel, in Single-shot or Continuous mode.

- Scan mode, which converts a complete set of predefined programmed input channels, in Single-shot or Continuous mode.

- Discontinuous mode, which converts a a short sequence (subgroup) of n conversions (n ≤ 8) that is part of the sequence of conversions. When an external trigger occurs, it starts the next n conversions selected in the ADC\_SQR registers until all the conversions in the sequence are done

#### Analog watchdog More robust (glitch free) analog watchdog High threshold Interrupt / The ADC has three Window watchdogs Signal **ADC** One Analog Watchdog can monitor one generator Low threshold selected channel or all enabled channels Window Two Analog Watchdogs can monitor Channel to monitor Watchdog several selected channels AWD1 1 (regular, injected, regular or injected) or all fegular, injected, regular or injected) Each watchdog continuously monitors an AWD2 All channels selected in ADC AWD2CR over- and/or under-threshold condition, then AWD3 All channels selected in ADC AWD3CR generates either an interrupt or an external signal Interrupt or timer trigger (no fiter) V(t) Analog watchdog filter (only with AWD1) hterrupt or signal generation only after High threshold programmable consecutive threshold detections Low threshold

Each ADC has 3 integrated 12-bit analog watchdogs with high and low threshold settings. The ADC conversion value is compared to this window threshold, if the result exceeds the threshold, an interrupt or timer trigger signal can be asserted without CPU intervention.

When converted data belongs to the interval defined, a DMA request is generated.

Otherwise, no DMA request is issued.

The Analog watchdog 1 has also a filtering capability. if data is out-of-range for a number of times higher than the value specified in AWDFILT in ADCx\_TR1 register, the AWDx flag is set and the corresponding interrupt is issued.

## Data transfers 22

- Regular conversion data is stored in a 16-bit data register

- In Dual mode regular conversions data are stored in a 32-bit data register ADCx CDR

- Software polling, interrupts or DMA requests can be used to move data

- The OVERRUN flag is set when previously converted data is overwritten by current data

- · For the analog watchdogs, it is not necessary to process each data: the OVERRUN flag can be disabled

- Injected conversion data is stored in four 16-bit data registers

- Injected conversion data is stored in dedicated registers

- The regular data sequence can be kept even if injected conversion occurs

The ADC conversion result is stored in a 16-bit data register.

In Dual mode, two samples are combined into a 32-bit register called ADCx\_CDR, thus minimizing the number of transactions on AHB.

The system can use CPU polling, interrupts or the DMA controller to make use of the conversion data.

An overrun flag can be generated if data is not read before the next conversion data is ready.

In case of overrun, either the new sample is dropped or the previous sample is overwritten.

For injected channel conversions, 4 dedicated data registers are available.

An injected conversion is used to interrupt the regular conversion, then insert up to 4 channel conversions. Once an injected conversion is finished, the regular conversion sequence can be resumed.

The injected conversion result is stored in dedicated data registers.

Flags and interrupts are available for the end of conversion and end of sequence.

The choices for an injected channel can be reprogrammed on the fly.

Even if a regular or injected conversion is in progress, you can add a different channel to the queue so that next injected channel can be different from the previous one.

### Features for each individual ADC 24

- Each ADC master shares the same input triggers with its ADC slave

- · ADC5 is controlled independently

| Four possible modes        |

|----------------------------|

| Injected simultaneous mode |

| Regular simultaneous mode  |

| Interleaved mode           |

| Alternate trigger mode     |

| Dual combined modes                                    |  |  |

|--------------------------------------------------------|--|--|

| Injected simultaneous mode + Regular simultaneous mode |  |  |

| Regular simultaneous mode + Aternate trigger mode      |  |  |

| Injected simultaneous mode + Interleaved mode          |  |  |

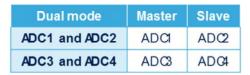

The STM32G4 embeds five ADCs.

ADC1 and ADC2 can be configured to work together in Dual mode, so that each analog-to-digital conversion can be synchronized between the two modules.

ADC3 and ADC4 can be also configured to work together in Dual mode

ADC5 works as a standalone converter.

Four possible Dual ADC modes are implemented:

- · Injected simultaneous mode

- Regular simultaneous mode

- Interleaved mode

- Alternate trigger mode

It is also possible to use these modes combined in the following ways:

- Injected simultaneous mode + Regular simultaneous mode

- Regular simultaneous mode + Alternate trigger mode

• Injected simultaneous mode + Interleaved mode.

In dual ADC mode, conversions can be started either simultaneously or alternately on ADC master and ADC slave.

The converted data of the master and slave ADC can be read in parallel, by reading the ADC common data register (ADCx\_CDR).

#### Do not convert the same channel on the two ADCs.

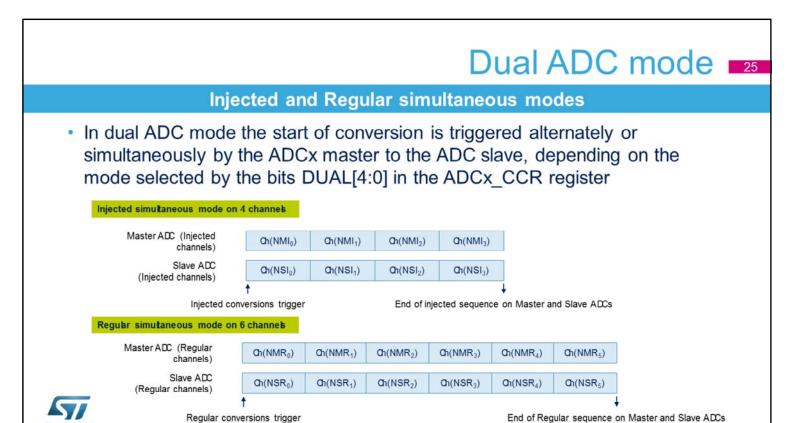

This slide describes the injected simultaneous mode and the regular simultaneous mode.

The trigger is used to simultaneously start the sequence of conversions on both Master and Slave ADC.

Conversion sequences must be equal on master and slave or must ensure that the interval between triggers is longer than both sequences.

In discontinuous mode, every simultaneous conversion requires an injected trigger.

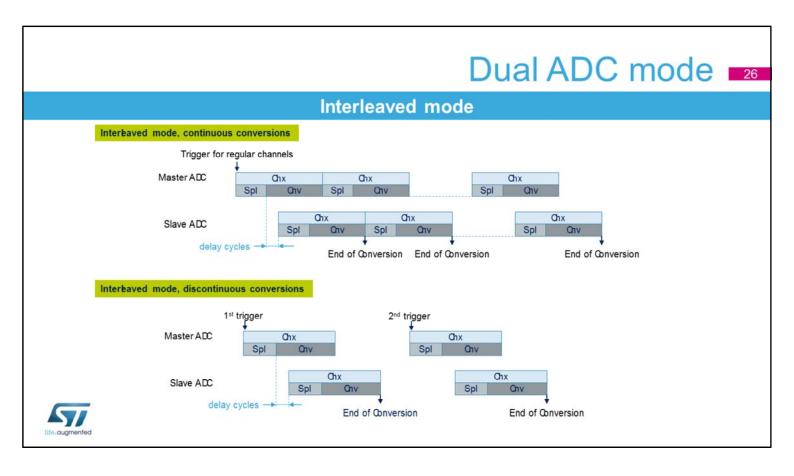

Interleaved mode converts a regular channel group (usually one channel).

The external trigger source which starts the conversion comes from ADC Master:

- ADC Master starts immediately

- ADC Slave starts after a configurable delay after the end of sampling of the master.

It prevents an ADC from starting a conversion while the complementary ADC is still sampling the input.

An EOC is generated at the end of each channel conversion.

In discontinuous mode, every simultaneous conversion requires a regular trigger.

### Dual ADC mode 27

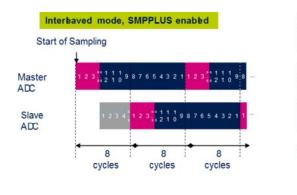

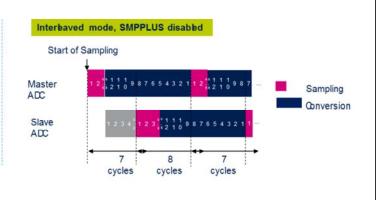

#### Interleaved mode, SMPPLUS

- The SMPPLUS in the ADC\_SMPR1 register can be set in dual interleaved mode to have equally spaced conversions between master and slave

- For 2.5 cycles sampling time, total conversion time is 15 cycles

- So 1 cycle is added to the sampling time to have total 16 cycles conversion thus making possible to interleave every 8 cycles

When a sampling time of 2.5 ADC clock cycles is selected, the total conversion time becomes 15 cycles in 12-bit mode.

If the dual interleaved mode is used, the sampling interval cannot be equal to 2.5 ADC clock cycles since an even number of cycles is required for the sampling time plus conversion time.

In the timing diagram on the right, the sampling time on the slave ADC has to be increased to 3.5 clock cycles, while the sampling time for the master ADC is 2.5 clock cycles.

The SMPPLUS bit can be used to change the sampling time 2.5 ADC clock cycles into 3.5 ADC clock cycles. In this way, the total conversion time becomes 16 clock cycles, thus making possible to interleave every 8 cycles. The maximum number of samples per second is equal to 56 MHz divided by 8 = 7 Mega samples per second.

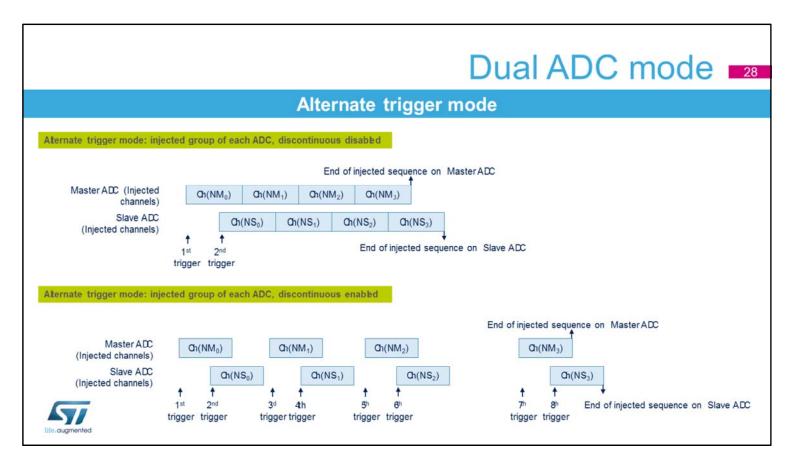

The Alternate Trigger mode converts an injected group of channels.

Conversions are started only by using hardware triggers.

The external trigger source comes from the injected group multiplexer of the master ADC.

When discontinuous mode is disabled and the 1st trigger occurs, all injected master ADC channels in the group are converted.

When the 2nd trigger occurs, all injected slave ADC channels in the group are converted.

When discontinuous mode is enabled and the 1st trigger occurs, the first injected channel of the master ADC is converted.

When the 2nd trigger occurs, the first injected channel of the slave ADC is converted.

# Interrupts and DMA

| 20 |  |

|----|--|

| 79 |  |

| Interrupt<br>event | Description                                      | Interrupt<br>event | Description                                       |

|--------------------|--------------------------------------------------|--------------------|---------------------------------------------------|

| ADRDY              | The ADC is ready to convert                      | AWD1-3             | Analog watchdog threshold breach detection occurs |

| EOC                | End of regular conversion                        | EOSMP              | End of a sampling phase                           |

| EOS                | End of sequence for regular conversion group     | OVR                | Data overrun occurs                               |

| JEOC               | End of injected conversion                       | JQOVF              | The injected sequence context queue overflows     |

| JEOS               | End of sequence for an injected conversion group |                    |                                                   |

DMA requests can be generated after each end of conversion of a regular channel

Each ADC can generate 9 different interrupts: ADC Ready, end of conversion, end of sequence, end of injected conversion, end of injected sequence, analog watchdog, end of sampling, data overrun and the overflow of the injected sequence context queue. DMA requests can be generated at each end of conversion when the ADC output data is ready.

### Low-power modes 30

| Mode           | Description                                                                     |  |

|----------------|---------------------------------------------------------------------------------|--|

| Run            | Active                                                                          |  |

| Seep           | Active  Peripheral interrupts cause the device to exit Sleep mode               |  |

| Low-power run  | Active                                                                          |  |

| Low-power seep | Active  Peripheral interrupts cause the device to exit low-power sleep mode     |  |

| Stop 0         | Not available  > Peripheral registers content is kept                           |  |

| Stop 1         | Not available  Peripheral registers content is kept                             |  |

| Standby        | Powered-down  > The peripheral must be reinitialized after exiting Standby mode |  |

| Shutdown       | Powered-down  The peripheral must be reinitialized after exiting Shutdown mode  |  |

In Deep power-down mode, the analog part of each ADC is switched off by an on-chip power switch

The ADCs are active in Run, Sleep, Low-power run and Low-power sleep modes.

In Stop 0 or Stop 1 mode, the ADCs are not available but the contents of their registers are kept.

In Standby or Shutdown mode, the ADCs are powereddown and must be reinitialized when returning to a higher power state.

There is a Deep power-down mode in each ADC itself which reduces leakage by turning off an on-chip power switch.

This is the recommended mode whenever an ADC is not used.

# Performance =

| 04  |  |

|-----|--|

| 3.1 |  |

|     |  |

|                                 | Condition     | Data (typ.) | Unit       |

|---------------------------------|---------------|-------------|------------|

|                                 | 12-bit mode   | 4.00        | Msamples/s |

| Samding rate                    | 10-bit mode   | 4.61        | Msamples/s |

| Sampling rate                   | 8-bit mode    | 5.45        | Msamples/s |

|                                 | 6-bit mode    | 6.66        | Msamples/s |

| Differential linearity error    |               | 1.4         | LSb        |

| htegral linearity error         | 12-bit mode   | 2.4         | LSb        |

| Effective Number Of Bits (ENOB) | 12-bit mode   | 10.6        | bit        |

| Consumerties A/DDA)             | 4 Msamples/s  | 590         | μΑ         |

| Consumption (VDDA)              | 10 Ksamples/s | 16          | μA         |

Note: This table shows the performance when only one ADC is activated. When multiple ADQs are activated, performance degradation is expected. Please see the datasheet for further detail

The following table shows performance parameters for the ADC.

# STM32G4 Vs STM32F3

| ADC features                  | STM32F3          | S1M32G4                  |

|-------------------------------|------------------|--------------------------|

| Number of ADCs                | 4                | 5                        |

| Conversion time               | 0.19 µs (51Msps) | 0.25 µs (4 Msps)         |

| External Triggers             | 16               | 32                       |

| HW Oversamping                | -                | yes                      |

| IO votage booster             | -                | yes                      |

| Gain compensation             | € 1              | yes                      |

| Offset compensation           | yes              | yes + Saturation control |

| Bub samping                   | -                | yes                      |

| Sampling time control trigger |                  | yes                      |

| Internal reference Vref       | Ē                | yes (2.048V, 2.5V, 2.9V) |

| Analog Watchdog               | yes              | yes + Filter             |

| Interbaved Mode SMPPLUS       | -                | yes                      |

This table highlights the new features implemented in the STM32G4's ADCs with regard to the STM32F3's ADCs.

# Related peripherals 33

- · Refer to these trainings linked to this peripheral, if needed:

- · DMA Direct memory access controller

- Interrupts Nested Vectored Interrupt Controller

- · GPIO General-purpose inputs and outputs

- · RCC Clock module

- DAC Digital-to-analog converter

- · TIM Timers for triggering interrupts and events

These peripherals may need to be specifically configured for correct use with the ADCs.

Please refer to the corresponding peripheral training modules for more information.

### References 34

- For more details, please refer to the following resources:

- · Application note AN2834: How to get the best ADC accuracy in STM32Fx Series and STM32L1 Series devices

- · Application note AN4073: How to improve ADC accuracy when using STM32F2xx and STM32F4xx microcontrollers

- Application note AN2668: Improving STM32F1x and STM32L1x ADC resolution by oversampling

- Application note AN4629: ADC hardware oversampling for microcontrollers of the STM32 L0 and L4 series

Several application notes dedicated to analog-to-digital converters are available.

To learn more about ADCs, you can visit a wide range of web pages discussing successive approximation analogto-digital converters.