How to Design a NFC Reader Application

A Step by Step Approach

Dan Merino

Technology Tour 2019

Dallas-Richardson, TX | March 7

# Agenda 2

# Defining Design Requirements

# Defining Design Requirements —4

### End Product

- Payment

- General Purpose

### Communication Protocol

- ISO 14443 A/B

- ISO 15693

- Felica

- AP2P.

## Defining Design Requirements 5

### System constraints

- Antenna Size

- Environmental Conditions

- Metal

- LCD screen

- Antenna placement

### Design Trade-offs

- Antenna size

- Read Range

- Current Consumption

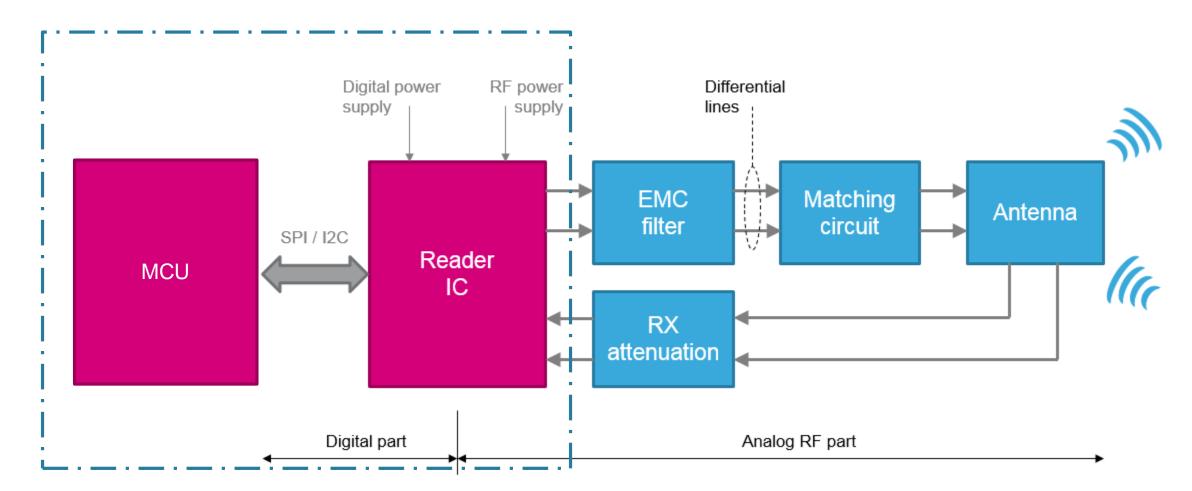

# System Block Diagram

# System Block Diagram -

### ST25R3911B Discovery

- Software GUI

- Source code downloadable

- Design files downloadable

### ST25R3911B Nucleo Shield

- Firmware available

- Design files downloadable

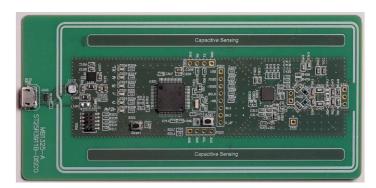

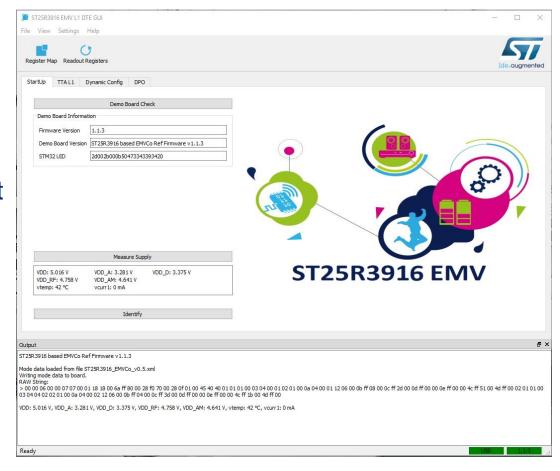

### ST25R3916 Discovery

- Software GUI

- Source code downloadable

- Design files downloadable

- EMVCo Reference design

- Hardware eval board

- Software GUI

- L1 Stack

- Available only by Request

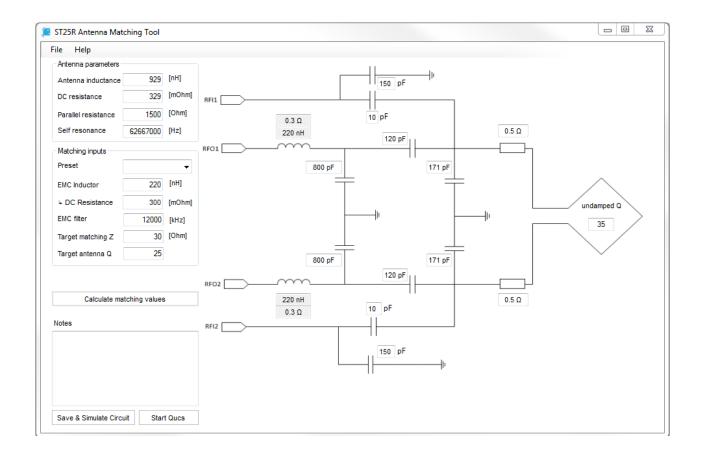

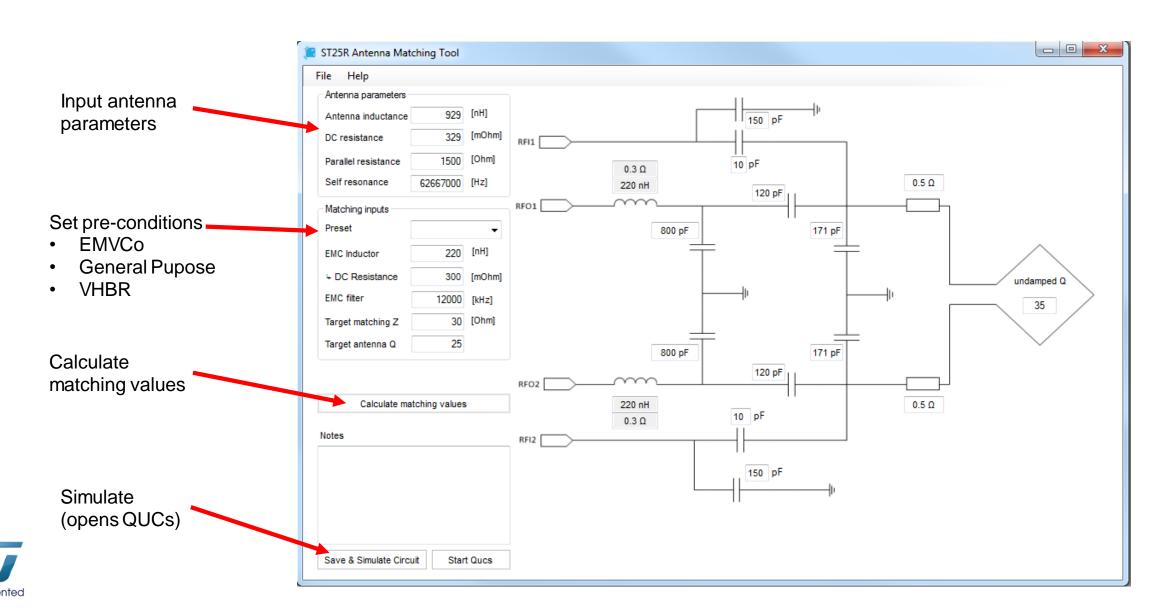

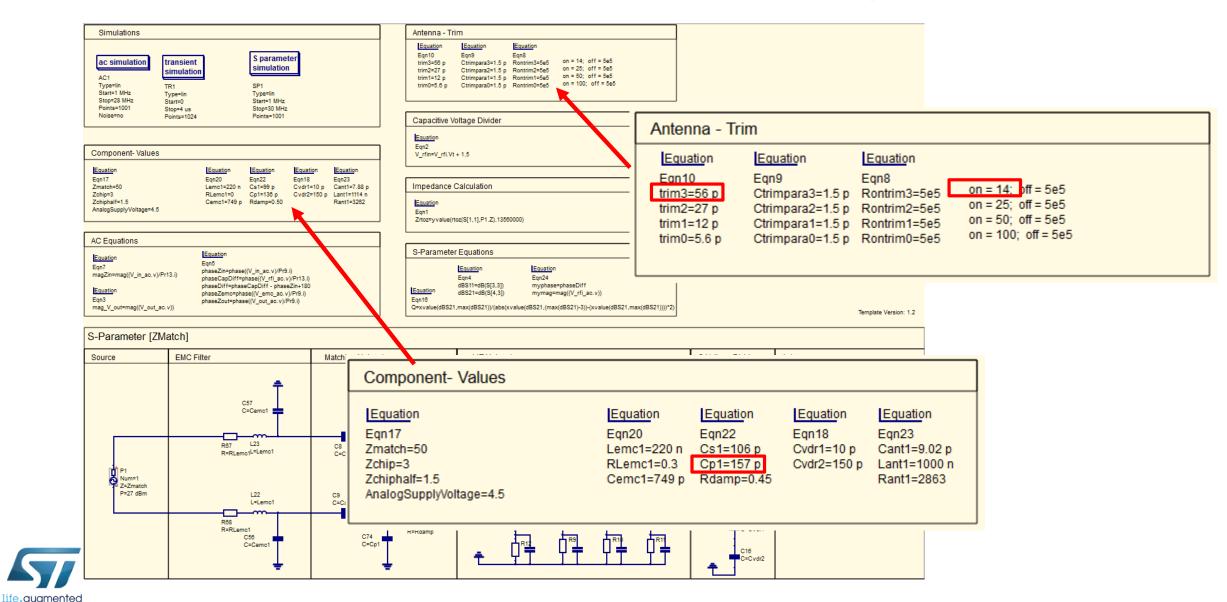

- Antenna Design Matching tool

- Calculates matching components

- Includes simulation program

- Available on ST25R3911B landing page

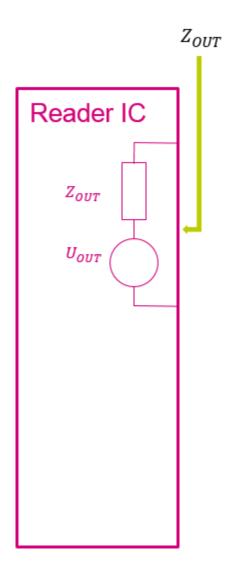

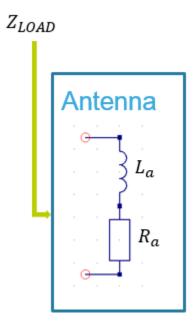

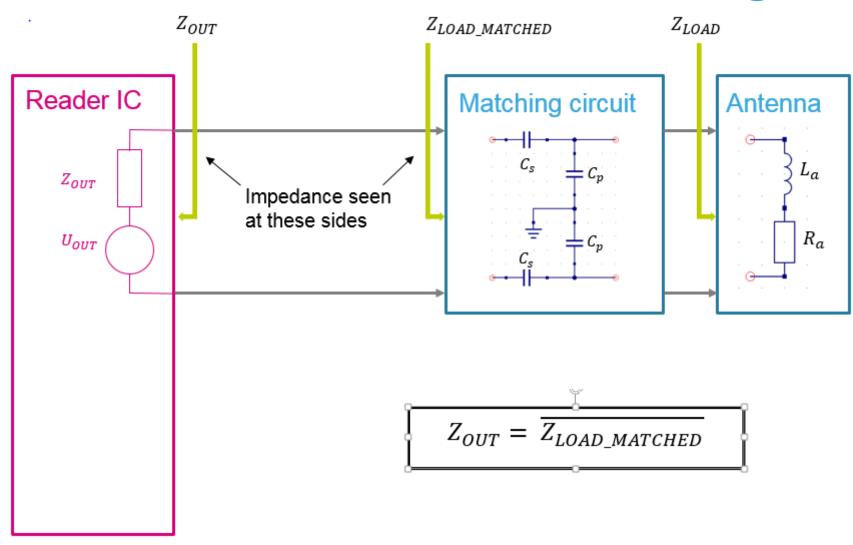

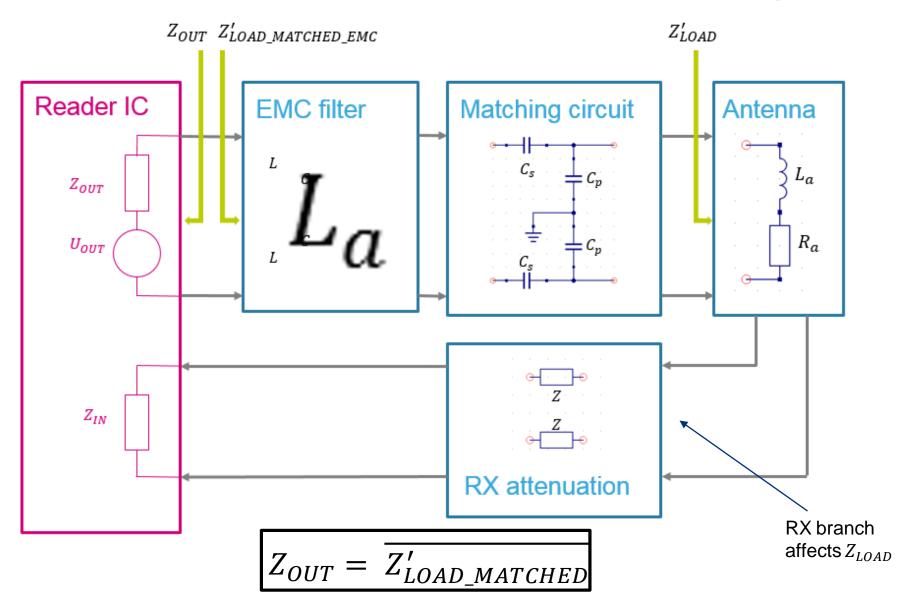

# Matching network

$$Z_{out} = \overline{Z_{LOAD}}$$

#### Antenna

- Two Turn

- Typical Inductance 200nH 2uH

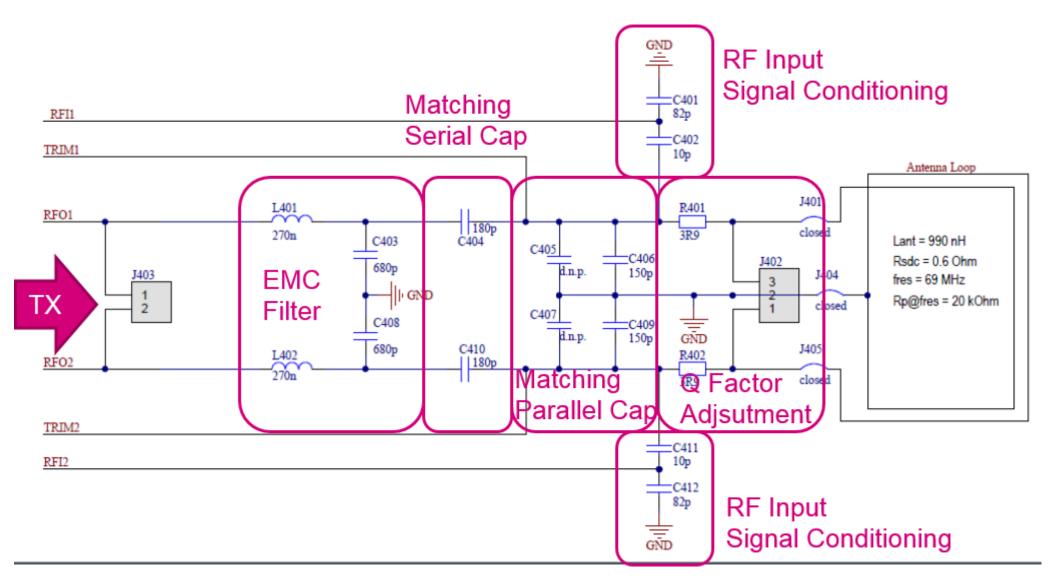

#### EMC Filter

- Reduces harmonics of the RFO output stage

- Target Cutoff Frequency about 13.56Mhz

### Matching Serial Cap

- Impedance match from EMC filter to antenna resonator circuit

- Cuts DC path from RFO1 to RFO2

### Q Factor adjustment

- Sets System Q (antenna Q should always be higher than System Q)

- Higher Q > More Field Strength > Lower Datarate

- Lower Q > Faster rise/fall times > Higher Datarate

- Target Values

- Up to 106kbps 25

- Up to 848kbps 12-16

- Up to 3.4Mbps 8

### RFI Input Conditioning

Reduces Antenna Voltage to < 3.0Vpp for RFI input</li>

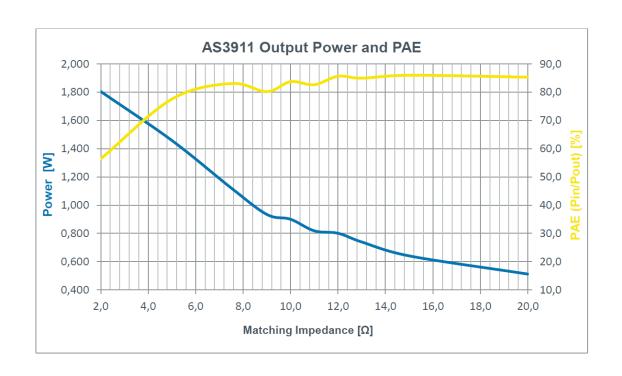

### Target Matching impedance

- Higher > less field strength > less power consumption > higher efficiency

- Lower > higher field strength > higher power consumption > less efficiency

- Range 8 120 ohms

- Typically between 10 30 ohms

### Antenna Parameters 21

| Parameter            | Action               | Effect on parameter | Q factor  |

|----------------------|----------------------|---------------------|-----------|

| Q factor             | Increase trace width | -                   | Increases |

|                      | Increase gap width   |                     |           |

| Inductance           | Larger antenna       | Increases           | Decreases |

|                      | Decrease trace width |                     |           |

|                      | Decrease gap width   |                     |           |

| Series DC resistance | Larger antenna       | Increases           | Decreases |

|                      | Decrease trace width |                     |           |

|                      | Decrease gap width   |                     |           |

| Parallel resistance  | Decrease trace width | Increases           | Increases |

|                      | Increase gap width   |                     |           |

| Resonance frequency  | Smaller antenna      | Increases           | Increases |

|                      | increase gap width   |                     |           |

# Antenna Matching

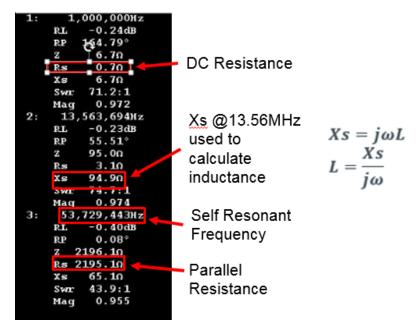

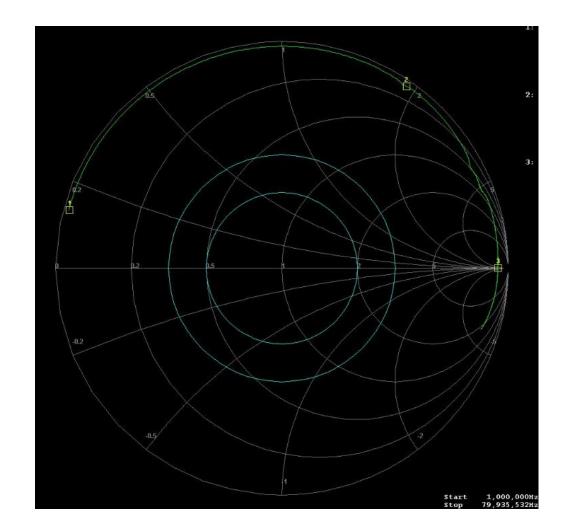

### Antenna Measurements 23

- Measure the following Parameters with a VNA

- DC resistance

- Inductance

- Self resonance frequency

- Parallel R @ FsR

### Antenna Measurements 24

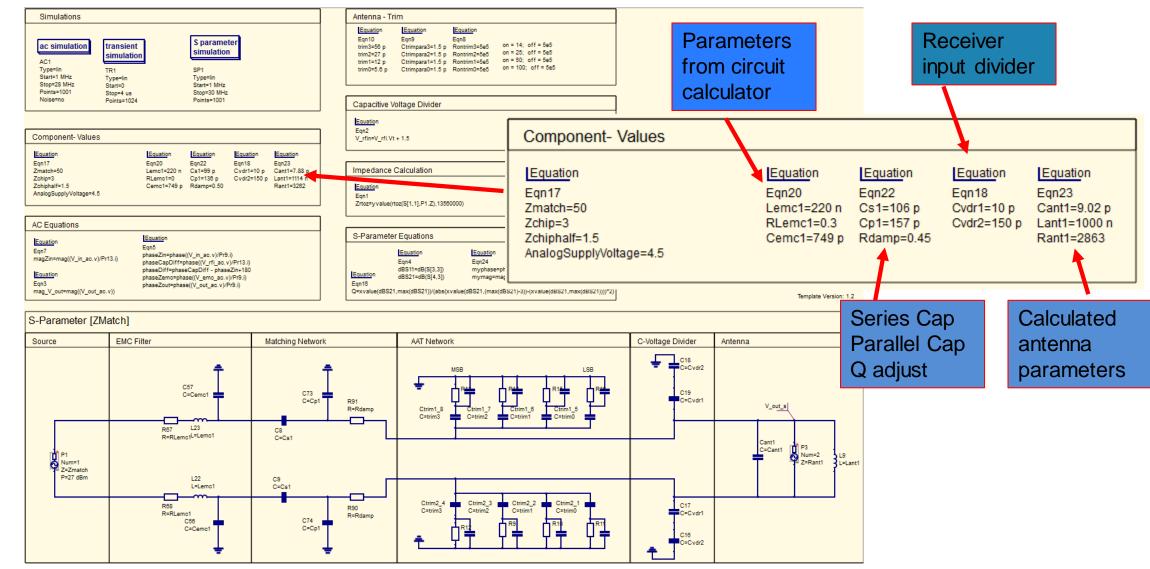

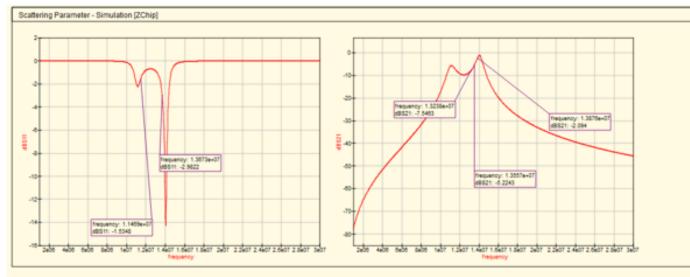

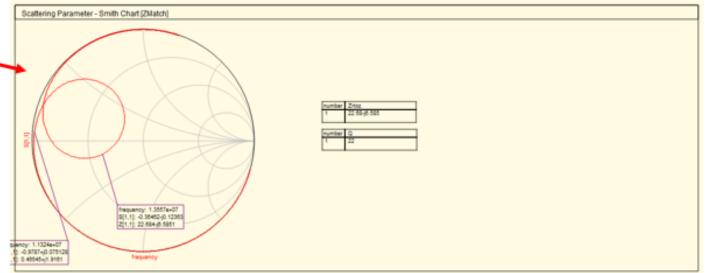

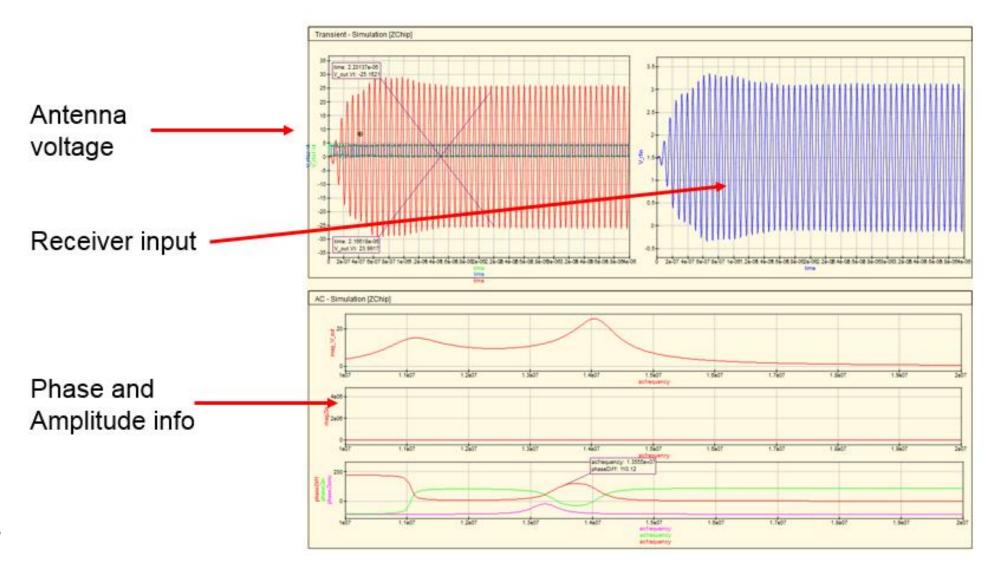

### Antenna Simulation 25

## Antenna Simulation 26

Impedance match info

### Antenna Simulation 27

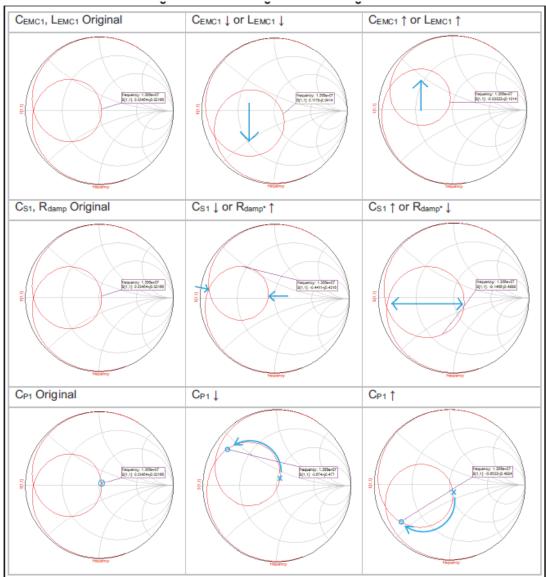

# Fine Tuning 28

**EMC** Components

- Serial Cap

- Damping Resistor

Parallel Cap

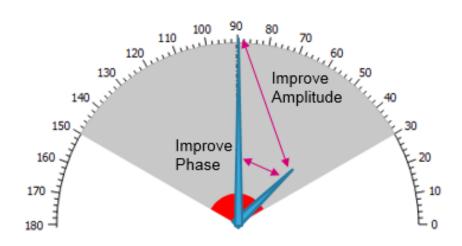

## Next Steps 29

- Populate values on circuit board

- Measure match on RFO pins with VNA

- Re-adjust values as required

- Test

- Optimize read range vs current consumption

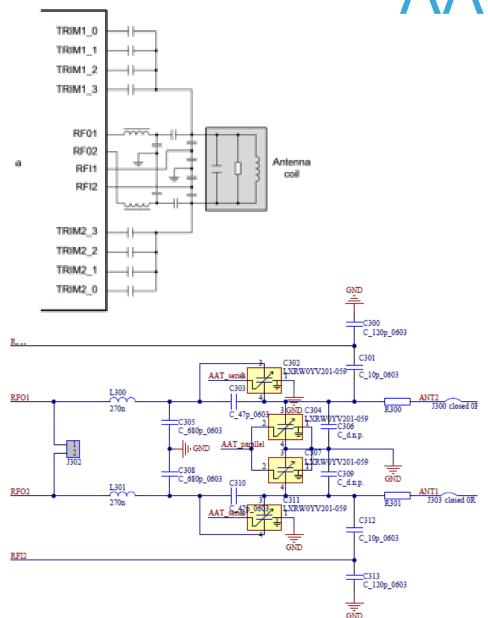

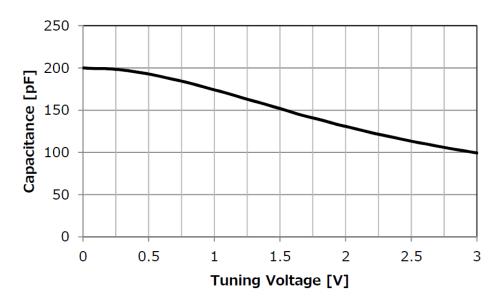

### Automatic Antenna Tuning

- Allows the matching circuit to be adjusted on the fly

- Adjustment range dependent on values used

- Larger Values > Larger range > less granularity

- Smaller Values > Smaller ranger > more granularity

- Must be compensated for in the matching circuit

### **AAT** 31

### • ST25R3911B

- 8 External Binary weighted capacitors (4 per RFO)

- Switches internal to reader

### • ST25R3916

- Uses variable capacitors

- Internal DAC's use to control variable capacitors

- Can be used to control both Serial and Parallel Caps

# AAT Compensation 32

- Match antenna as before

- Determine serial/parallel capacitors

- ST25R3916

- Subtract ¾ Variable cap value from Cp

- This becomes new parallel capacitor

- ST25R3911B

- Subtract Highest trim value cap from Cp

- This becomes new parallel capacitor

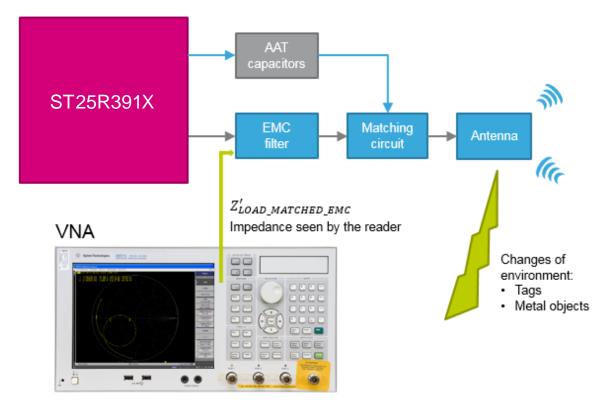

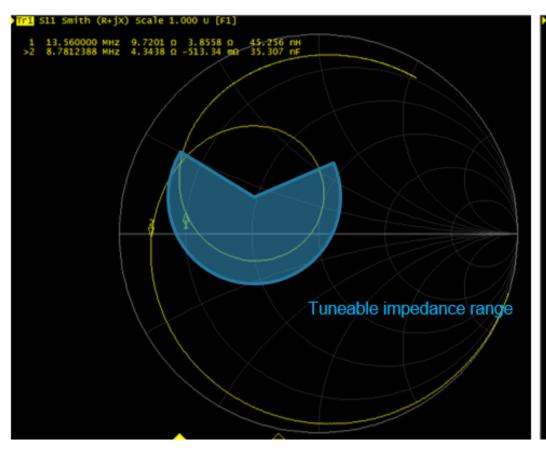

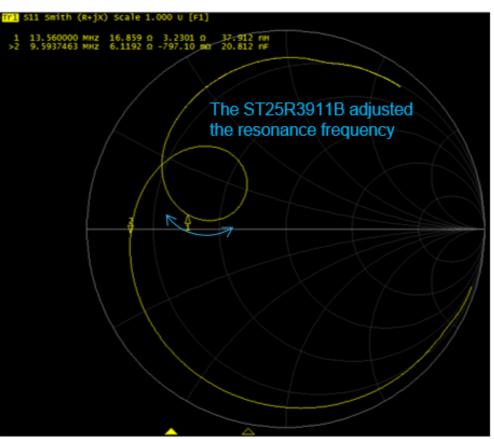

# Testing AAT 33

#### ST25R3911B

- Set reg 27 to 0xff (double check) that no field is being generated

- Adjust AAT trim to 8 (Antenna Tab in GUI)

- Match should be in center of range

### ST25R3916

- Set reg 28 to 0x7f (double check) that no field is being generated

- Adjust AAT trim mid (Antenna Tab in GUI)

- Match should be in center of range

### **Important to turn off output drivers**

Measurement of how AAT changes the impedance of the antenna seen by the reader

# AAT Range 34

ST25R3916

ST25R3911B

### AAT Simulation 35

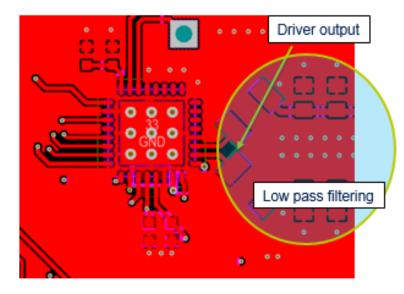

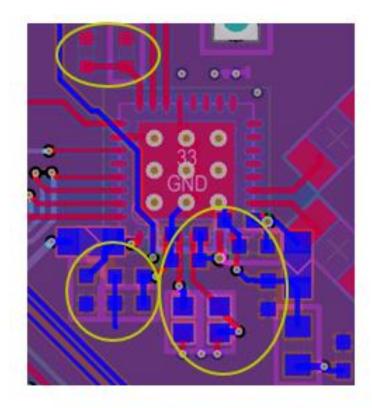

# Layout Suggestions 36

- 4 layer board if possible (Sig/GND/PWR/Sig)

- Make RFO paths symmetrical

- Keep traces short

- EMC filter as close as possible to RFO pins

- Layout extra pads for Cs and Cp for fine tuning

- Layout pads for AAT (just in case)

# Layout Suggestions 37

#### EMC filter

Filter must be positioned as close as possible to the output stages

#### RFO & RFI routing

- The inductors after the RFO are placed in 90 degree direction

- The RFI lines are routed symmetrically, but in a fair distance to the RFO lines

- No long signal traces between LC filter and the remaining matching components

- The vias in the RFI lines should be avoided in a final design

# Layout Suggestions 38

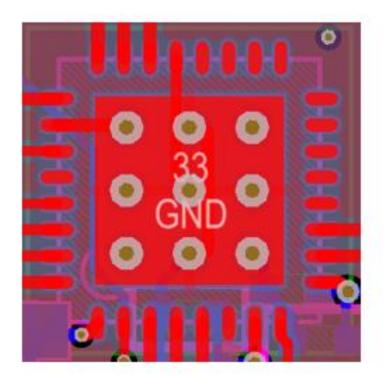

#### Decoupling

- Capacitors as close as possible to the chip

- Parallel capacitors 2.2 µF and 10 nF

### Thermal pad

- Ground plane & thermal heatsink

- Multiple through vias must be used

Questions?