# AN3090 Application note

# Power saving and LED status detection using the STP16DPPS05 device

### Introduction

Today, the use of LEDs is growing in many market segments, including portable applications, due to their improving performance and lower cost.

This new scenario requires that LED drivers be capable of providing good performance at low current, and include power saving capabilities. To address these requirements, STMicroelectronics has introduced the STP16xPPx05 family of LED drivers.

This application note describes the STP16DPPS05 low voltage 16-bit constant current LED sink driver, with particular focus on two important features: output error detection and auto power-saving.

December 2009 Doc ID 16496 Rev 1 1/19

Contents AN3090

## **Contents**

| 1 | Device description                               | . 5  |

|---|--------------------------------------------------|------|

| 2 | Normal mode functionality                        | . 6  |

| 3 | Error detection feature                          | . 8  |

| 4 | Error detection output test circuit              | . 13 |

| 5 | Auto power-saving feature                        | . 14 |

|   | 5.1 Value added by the auto power-saving feature | . 15 |

| 6 | Conclusion                                       | . 17 |

| 7 | Revision history                                 | 19   |

AN3090 List of tables

# List of tables

| Table 1. | Output error detection sequence after OE/DM2 acquisition | 10 |

|----------|----------------------------------------------------------|----|

| Table 2. | Error threshold test results                             | 13 |

| Table 3. | Document revision history                                | 18 |

List of figures AN3090

# **List of figures**

| Figure 1.  | STP16DPPS05 block diagram                                                  | 5    |

|------------|----------------------------------------------------------------------------|------|

| Figure 2.  | Typical data transfer from SDI to SDO                                      | 6    |

| Figure 3.  | Typical output_n functionality in normal mode                              | 7    |

| Figure 4.  | Typical application of the STP16DPPS05 device                              | 8    |

| Figure 5.  | Error detection sequence                                                   | 9    |

| Figure 6.  | Typical error detection results                                            | . 11 |

| Figure 7.  | Entering output error detection timing                                     | . 12 |

| Figure 8.  | Resuming normal mode timing                                                | . 12 |

| Figure 9.  | I <sub>DD</sub> consumption in normal mode and auto power-saving condition | . 14 |

| Figure 10. | First out "ON" after resuming normal mode                                  | 15   |

AN3090 **Device description**

#### **Device description** 1

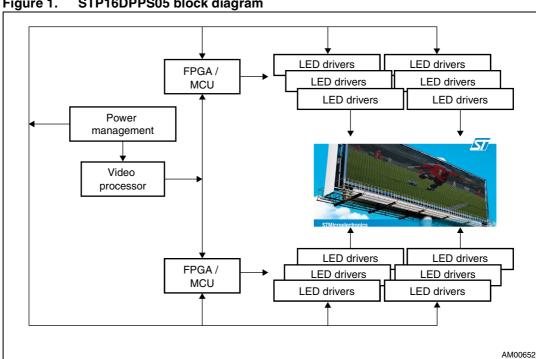

The STP16DPPS05 device is a monolithic, low voltage, low current power shift register. It contains a 16-bit serial IN, parallel OUT shift register that feeds a 16-bit D-type storage register. Sixteen regulated currents are present in the output stage, which is capable of providing 3-40 mA of constant current to drive the LEDs. Figure 1 shows the application block diagram of the STP16DPPS05 device.

STP16DPPS05 block diagram Figure 1.

Two important features of STP16DPPS05 are output status checking to detect LED errors during driving (error detection), and power saving when the device is not managing data (auto power safe).

## 2 Normal mode functionality

During normal operation, the serial data present on the SDI pin is transferred to the shift register in synchronization with the CLK rising edge. After 16 CLK pulses, the data loaded on the SDI pin is shifted to the SDO pin with a typical delay of 22 ns, as shown on the plot in *Figure 2*.

This delay guarantees the correct synchronization of the CLK and SDI signals if two or more STP16DPPS05 devices are cascaded.

Figure 2. Typical data transfer from SDI to SDO

The data present in any register is transferred to the respective latch when the latch-enable (LE/DM1) signal is high (serial-to-parallel conversion).

After this step, the data is transferred to the outputs via the output-enable pin  $(\overline{OE/DM2})$ , which turns on the LEDs at the current set by the external resistor.

By changing the  $\overline{\text{OE}/\text{DM2}}$  duty cycle, it is possible to set the output dimming if the application requires slow or fast frame visualization.

The plot in *Figure 3* shows typical output switching in normal mode at  $V_{DD} = 3.3 \text{ V}$ .

Figure 3. Typical output\_n functionality in normal mode

The following signals are shown on the plot above:

- Ch1 (yellow) = OE/DM2 signal

- Ch2 (blue) = SDI signal

- Ch3 (purple) = V<sub>OUT</sub>

- Ch4 (green) = OUPUT signal

It should be highlighted that the LE/DM1 and  $\overline{\text{OE}/\text{DM2}}$  signals are NOT synchronized with the rising or falling edges of the CLK signal. This mechanism is useful in all applications, especially where it is necessary to stop the CLK switching. For example, after the frame loading, it is necessary to stop the CLK switching to reduce noise between the lines.

**Error detection feature** AN3090

#### Error detection feature 3

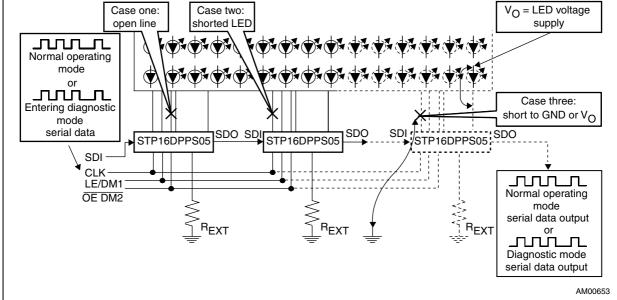

Figure 4.

The output error detection feature allows LED functionality checks by means of output status detection. This feature covers two types of detection: open-circuit and short-circuit detection.

The schematic in Figure 4 shows a typical application where multiple STP16DPPS05 devices are cascaded.

Typical application of the STP16DPPS05 device

From "normal mode", the device is switched to "error detection mode" (EDM) by a logic sequence on the LE/DM1 and OE/DM2 pins. In order to switch on all the outputs during the detection time, the sixteen data bits must be set to "1".

The data are latched by the LE/DM1, after which the outputs are ready for the detection process.

When the microcontroller switches the OE/DM2 to low, the device drives the LEDs to check if an open or short condition has occurred. The acquisition time (OE/DM2 to low) necessary to allow for correct LED feedback is typically 1 µs. Two CLK pulses must be sent after the minimum detection time (typical: 500-600 ns), in order to set the SDO pin to the correct output error detection value. In this way, the data loaded in the shift register is updated (rewritten) with the error detection data when the OE/DM2 signal goes high.

In synchronization with the rising edge of the CLK signal, the LED status is provided by the SDO pin: a "1" logic level signals a good output, while a "0" logic level signals an output fault condition (short or open condition).

AN3090 Error detection feature

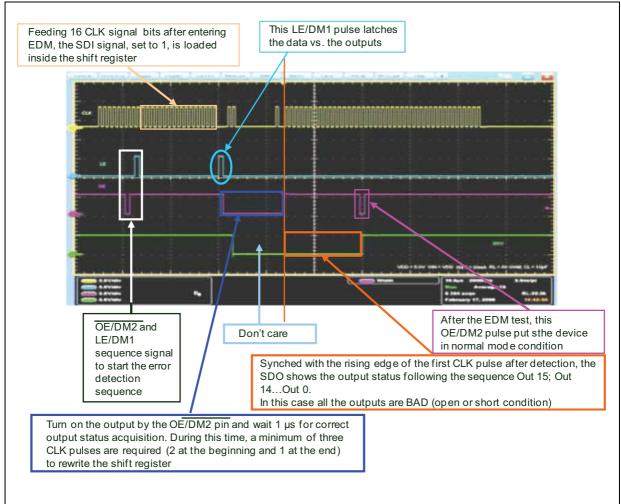

The plot in Figure 5 shows all the steps required to perform the EDM test.

Figure 5. Error detection sequence

As described above, the output status detection sequence is synchronized with the rising edge of the CLK signal after  $\overline{\text{OE}/\text{DM2}}$  changes to high. An overview of the output results is shown in *Table 1*.

Error detection feature AN3090

Table 1. Output error detection sequence after OE/DM2 acquisition

| CLK pulse after OE turns to high level | Output results |

|----------------------------------------|----------------|

| 1 <sup>st</sup> CLK rising edge        | Output 16      |

| 2 <sup>nd</sup> CLK rising edge        | Output 15      |

| 3 <sup>rd</sup> CLK rising edge        | Output 14      |

| 4 <sup>th</sup> CLK rising edge        | Output 13      |

| 5 <sup>th</sup> CLK rising edge        | Output 12      |

| 6 <sup>th</sup> CLK rising edge        | Output 11      |

| 7 <sup>th</sup> CLK rising edge        | Output 10      |

| 8 <sup>th</sup> CLK rising edge        | Output 9       |

| 9 <sup>th</sup> CLK rising edge        | Output 8       |

| 10 <sup>th</sup> CLK rising edge       | Output 7       |

| 11 <sup>th</sup> CLK rising edge       | Output 6       |

| 12 <sup>th</sup> CLK rising edge       | Output 5       |

| 13 <sup>th</sup> CLK rising edge       | Output 4       |

| 14 <sup>th</sup> CLK rising edge       | Output 3       |

| 15 <sup>th</sup> CLK rising edge       | Output 2       |

| 16 <sup>th</sup> CLK rising edge       | Output 1       |

To resume normal mode functionality, it is mandatory to apply another  $\overline{\text{OE}/\text{DM2}}$  pulse after 16 CLK pulses.

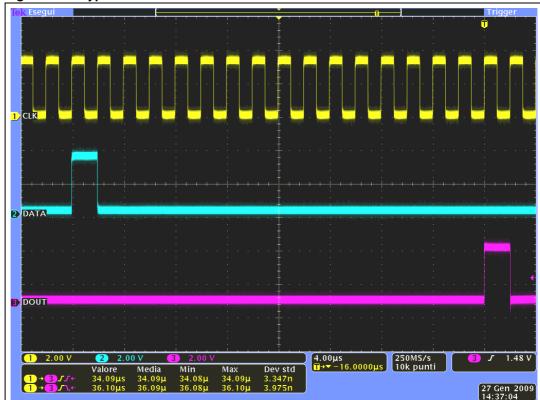

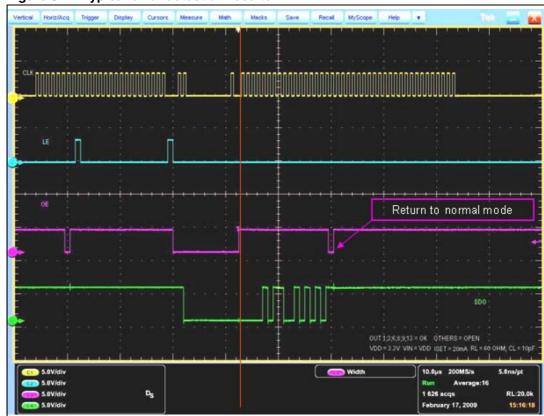

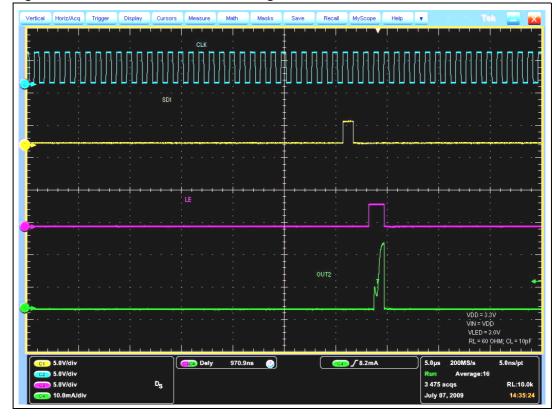

The plot in *Figure 6* shows a typical example of error detection feedback. Observing the SDO (green signal) and  $\overline{\text{OE/DM2}}$  (purple signal) it is possible to verify, respectively, the output status and how the device returns to normal mode.

AN3090 Error detection feature

Figure 6. Typical error detection results

The following signals are shown on the plot above:

- Ch1 (yellow) = CLK signal

- Ch2 (blue) = LE/DM1 signal

- ◆ Ch3 (purple) = OE/DM2 signal

- Ch4 (green) = SDO signal

Error detection feature AN3090

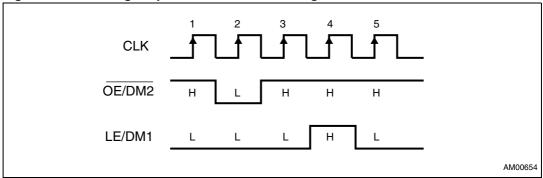

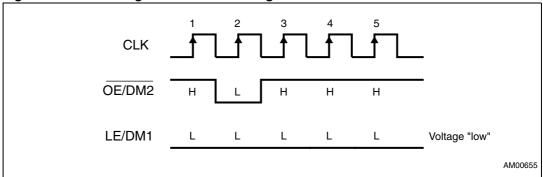

Figure 7 shows the OE/DM2 and LE/DM1 digital key combination necessary to start the EDM test. If this sequence is incorrect, the EDM test does not start.

Figure 7. Entering output error detection timing

*Figure 8* shows the timing sequence necessary to resume normal operation after the LED status acquisition is completed.

Figure 8. Resuming normal mode timing

### 4 Error detection output test circuit

During the error detection time, the internal structure of the device allows a single output current test. Specifically, the test is performed by comparing the current flowing from the output, to the current set by the  $R_{\mathsf{FXT}}$  programming resistor.

If the current detected is less than 50% (typ) of the current set by the  $R_{\text{EXT}}$  resistor, the device marks the output as malfunctioning, and converts the previous data loaded into the shift register from "1" to "0". Subsequently, these results are transferred as feedback by the SDO pin.

*Table 2* shows a typical example of the measured error detection threshold for several output current levels set by the R<sub>EXT</sub> resistor.

Table 2. Error threshold test results

| V <sub>DD</sub> (V) | I <sub>SET</sub> (mA) | Measured error threshold (mA) |

|---------------------|-----------------------|-------------------------------|

|                     | 1                     | 0.359                         |

|                     | 2                     | 0.841                         |

|                     | 3                     | 1.36                          |

| 3.3                 | 5                     | 2.10                          |

|                     | 10                    | 4.80                          |

|                     | 20                    | 10.2                          |

|                     | 40                    | 19.68                         |

|                     | 1                     | 0.355                         |

|                     | 2                     | 0.831                         |

|                     | 3                     | 1.21                          |

| 5.0                 | 5                     | 2.40                          |

|                     | 10                    | 5.00                          |

|                     | 20                    | 9.90                          |

|                     | 40                    | 19.55                         |

For output error detection to function correctly, all the signals must be synchronized with the falling edge of the CLK signal. This is necessary to avoid any setup\hold time violations.

In some cases, due to application conditions, this cannot be applied (i.e.: data generated by an MCU). To address this, it is possible to switch all of the other signals by applying a 15 ns delay after the rising edge of the CLK signal.

Only one error detection reading can be made within the acquisition time window. For this reason, if two or more readings are required it is necessary the complete the error detection sequence, then repeat each step again.

### 5 Auto power-saving feature

This section explains the benefits of the auto power-saving feature of the STP16DPPS05 device.

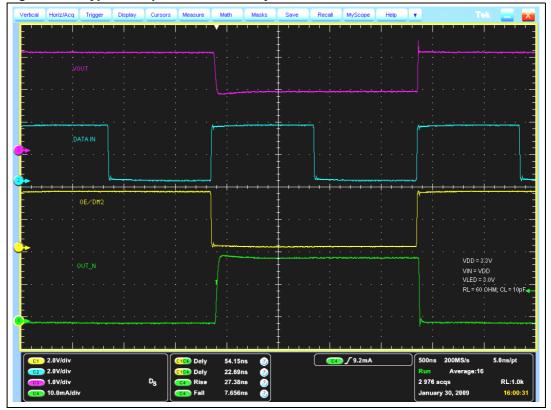

The plot in *Figure 9* shows the I<sub>DD</sub> supply voltage consumption during normal mode and in the auto power-saving condition.

Figure 9. I<sub>DD</sub> consumption in normal mode and auto power-saving condition

In the plot above,  $I_{DD}$  consumption (Ch4 green) falls after 16 CLK pulses (Ch2 blue) if no SDI data (Ch1 yellow) were latched by the LE/DM1 signal (Ch3 purple). When the first active data is available on the SDI pin (Ch1) and is latched by the LE/DM1 signal (Ch3), the device switches from auto power-saving mode to normal mode and  $I_{DD}$  consumption rises to typical values.

*Figure 10* shows the typical shape of the first output turn-on when the device switches from auto power-saving to normal mode.

Figure 10. First out "ON" after resuming normal mode

The following signals are shown on the plot above:

- Ch1 (yellow) = SDI signal

- Ch2 (blue) = CLK signal

- Ch3 (purple) = LE/DM1

- Ch4 (green) = first output switched on after return from auto power-saving to normal mode

### 5.1 Value added by the auto power-saving feature

To demonstrate the added benefits provided by the auto power-saving feature, consider a typical application, such as an LED display panel supplied by battery cell, where 100 STP16DPPS05 devices are used.

If the outputs of each device are driven with a 40 mA current capability ( $R_{EXT}$  = 497  $\Omega$ ), the  $I_{DD}$  supply current of each device is typically 8 mA.

The LED display supply current (I<sub>DD</sub>) is:

Total  $I_{DD} = I_{DD} \times n$

(Where *n* is the number of STP16DPPS05 devices used).

In this case:

Total  $I_{DD}$  (mA) = 0.008 x 100 = 800 mA

Using the power-saving feature, considering that the  $I_{DD}$  of one device in shutdown condition is typically 140  $\mu$ A, the LED display supply current ( $I_{DD}$ ) is:

Total  $I_{DD}$  (mA) = 0.00014 x 100 = 14 mA

As a result:

With all devices in auto-shutdown, the power supply consumption is 1.75% versus normal operating conditions, resulting in power savings of 98.25%.

Usually, when an LED panel is used in standard mode, it is common to have from 15% to 40% of the drivers with no active outputs. Also, in this condition the devices switching from auto power-up to auto-shutdown are able to save power to increase battery time span.

AN3090 Conclusion

### 6 Conclusion

The two highlighted features of the STP16DPPS05 generate benefits for a wide range of applications.

The device can provide the MCU with feedback of the overall LED system via the EDM test, which can be managed either locally or remotely through a network.

The STP16DPPS05 is suitable for all applications where power saving is important, such as in traffic panels or electronic advertising, where it is possible to switch off parts of the panels, when not necessary, to increase the battery time span.

Revision history AN3090

# 7 Revision history

Table 3. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 03-Dec-2009 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com