# AN3338 Application note

**SLLIMM**<sup>TM</sup>

## small low-loss intelligent molded module

By Carmelo Parisi and Giovanni Tomasello

#### Introduction

In recent years the variable speed motor control market has required high performance solutions able to satisfy the increasing energy saving requirements, compactness, reliability, and system costs in home appliances, such as washing machines, dish washers, refrigerators, air conditioning compressor drives, and in low power industrial applications, such as sewing machines, pumps, tools, etc. To meet these market needs, STMicroelectronics has developed a new family of compact, high efficiency, dual-in-line intelligent power modules, with optional extra features, called small low-loss intelligent molded module (SLLIMM<sup>TM</sup>).

The SLLIMM product family combines optimized silicon chips, integrated in three main inverter blocks:

- · power stage

- six short-circuit rugged IGBTs

- six freewheeling diodes

- driving network

- three high voltage gate drivers

- discrete gate resistors

- three bootstrap diodes

- · protection and optional features

- op amps for advanced current sensing

- comparators for fault protection against overcurrent and short-circuit

- NTC sensor for temperature control

- smart shutdown function

- dead time, interlocking function and undervoltage lockout.

Thanks to the state of art DBC mounting technology, the fully isolated SLLIMM package (SDIP) offers extremely low thermal resistance with optimum cost-effectiveness and quality level.

Compared to discrete-based inverters, including power devices, and driver and protection circuits, the SLLIMM family provides a high integrated level that means simplified circuit design, reduced component count, smaller weight, and high reliability.

The aim of this application note is to provide a detailed description of SLLIMM products, providing guidelines to motor drive designers for an efficient, reliable, and fast design when using the new ST SLLIMM family.

Contents AN3338

## **Contents**

| 1 | Inve | Inverter design concept and SLLIMM solution |                                                                       |    |  |  |

|---|------|---------------------------------------------|-----------------------------------------------------------------------|----|--|--|

|   | 1.1  | Produc                                      | et synopsis                                                           | 7  |  |  |

|   | 1.2  | Produc                                      | et line-up and nomenclature                                           | 9  |  |  |

|   | 1.3  | Interna                                     | ıl circuit                                                            | 11 |  |  |

|   | 1.4  | Absolu                                      | te maximum ratings                                                    | 3  |  |  |

| 2 | Elec | trical ch                                   | naracteristics and functions1                                         | 7  |  |  |

|   | 2.1  | IGBTs                                       |                                                                       | 17 |  |  |

|   | 2.2  | Freewh                                      | neeling diodes1                                                       | 17 |  |  |

|   | 2.3  | High vo                                     | oltage gate drivers                                                   | 17 |  |  |

|   |      | 2.3.1                                       | Logic inputs                                                          | 19 |  |  |

|   |      | 2.3.2                                       | High voltage level shift                                              | 21 |  |  |

|   |      | 2.3.3                                       | Undervoltage lockout                                                  | 21 |  |  |

|   |      | 2.3.4                                       | Dead time and interlocking function management                        | 22 |  |  |

|   |      | 2.3.5                                       | Comparators for fault sensing                                         | 24 |  |  |

|   |      | 2.3.6                                       | Short-circuit protection and smart shutdown function                  | 25 |  |  |

|   |      | 2.3.7                                       | Timing chart of short-circuit protection and smart shutdown function2 | 26 |  |  |

|   |      | 2.3.8                                       | Current sensing shunt resistor selection                              | 27 |  |  |

|   |      | 2.3.9                                       | RC filter network selection                                           | 29 |  |  |

|   |      | 2.3.10                                      | Overtemperature protection                                            | 30 |  |  |

|   |      | 2.3.11                                      | Op amps for advanced current sensing                                  |    |  |  |

|   |      | 2.3.12                                      | Bootstrap circuit                                                     |    |  |  |

|   |      | 2.3.13                                      | Bootstrap capacitor selection                                         |    |  |  |

|   |      | 2.3.14                                      | Initial bootstrap capacitor charging                                  | 37 |  |  |

| 3 | Pack | kage                                        |                                                                       | 19 |  |  |

|   | 3.1  | DBC s                                       | ubstrate 3                                                            | 39 |  |  |

|   | 3.2  | PCB .                                       |                                                                       | 10 |  |  |

|   | 3.3  | Packag                                      | ge structure                                                          | 10 |  |  |

|   | 3.4  | Packag                                      | ge outline and dimensions                                             | 13 |  |  |

|   | 3.5  | Input a                                     | nd output pins description                                            | 16 |  |  |

| 4 | Pow  | er losse                                    | es and dissipation5                                                   | 53 |  |  |

AN3338 Contents

| 7 | Revi | sion his | story                                           | 71 |

|---|------|----------|-------------------------------------------------|----|

| 6 | Refe | rences   |                                                 | 70 |

|   |      | 5.2.3    | General handling precaution and storage notices | 68 |

|   |      | 5.2.2    | Mounting torque                                 | 67 |

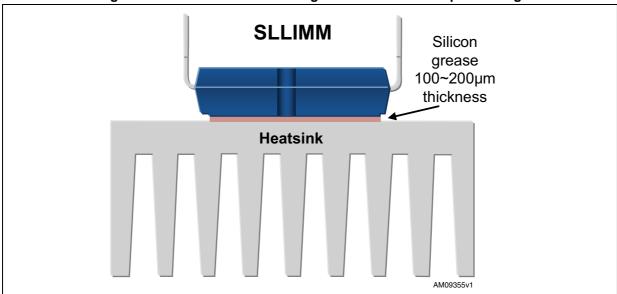

|   |      | 5.2.1    | Heatsink mounting                               | 66 |

|   | 5.2  | Mount    | ing instructions                                | 66 |

|   |      | 5.1.1    | General suggestions                             | 62 |

|   | 5.1  | Layout   | t suggestions                                   | 62 |

| 5 | Desi | gn and   | mounting guidelines                             | 62 |

|   | 4.4  | Power    | losses calculation example                      | 60 |

|   | 4.3  |          | al impedance overview                           |    |

|   |      |          |                                                 |    |

|   | 4.2  |          | ing power losses                                |    |

|   | 4.1  | Condu    | action power losses                             | 53 |

List of tables AN3338

# List of tables

| Table 1.  | SLLIMM line-up                                                              | 9       |

|-----------|-----------------------------------------------------------------------------|---------|

| Table 2.  | Inverter part of STGIPL14K60                                                | 14      |

| Table 3.  | Control part of STGIPL14K60                                                 | 16      |

| Table 4.  | Supply voltage and operation behavior                                       | 16      |

| Table 5.  | Total STGIPL14K60 system                                                    | 16      |

| Table 6.  | Integrated pull-up/down resistor values                                     | 20      |

| Table 7.  | Interlocking function truth table of STGIPS10K60A                           | 22      |

| Table 8.  | Interlocking function truth table of STGIPS14K60, STGIPL14K60, STGIPS20K60, | and ST- |

|           | GIPL20K6023                                                                 |         |

| Table 9.  | SDIP-25L mechanical data                                                    |         |

| Table 10. | SDIP-38L mechanical data                                                    | 46      |

| Table 11. | Input and output pins of SDIP-25L package                                   | 47      |

| Table 12. | Input and output pins of SDIP-38L package                                   | 48      |

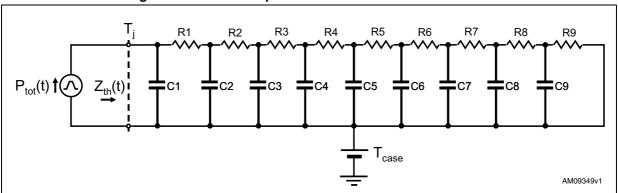

| Table 13. | RC Cauer thermal network elements by device                                 | 60      |

| Table 14. | Mounting torque and heatsink flatness                                       | 67      |

| Table 15. | Document revision history                                                   | 71      |

AN3338 List of figures

# List of figures

| Figure 1.    | Inverter motor drive block diagram                                           | 6    |

|--------------|------------------------------------------------------------------------------|------|

| Figure 2.    | Discrete-based inverter vs. SLLIMM solution comparison                       | 7    |

| Figure 3.    | SLLIMM block diagram                                                         |      |

| Figure 4.    | SLLIMM nomenclature                                                          | . 10 |

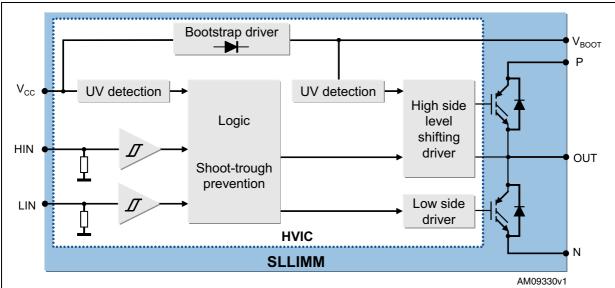

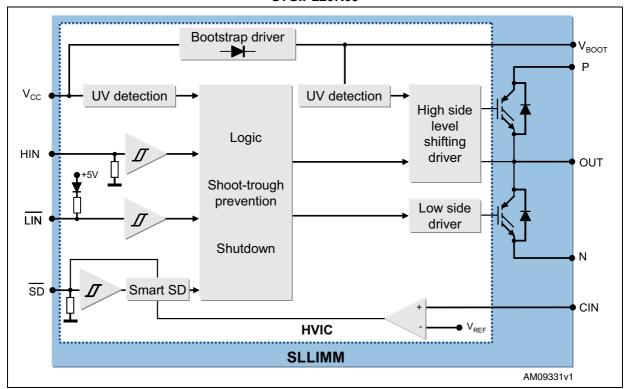

| Figure 5.    | Internal circuit of STGIPS10K60A                                             | . 11 |

| Figure 6.    | Internal circuit of STGIPS14K60 and STGIPS20K60                              | . 12 |

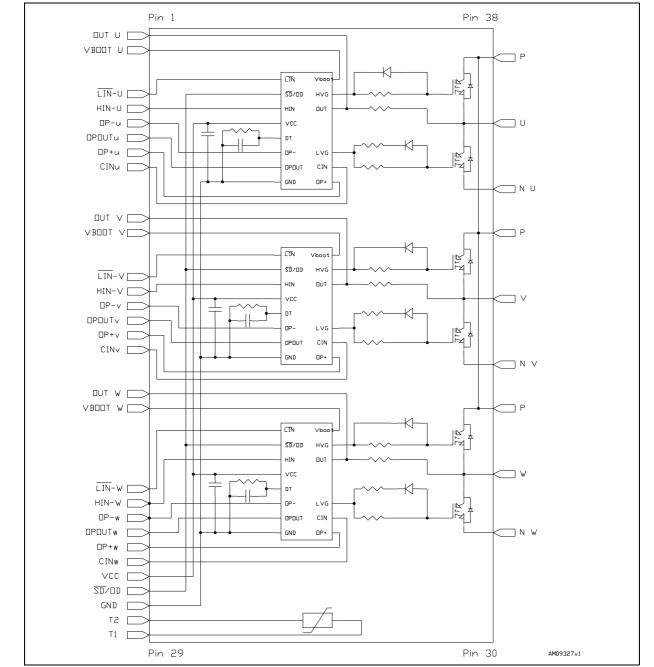

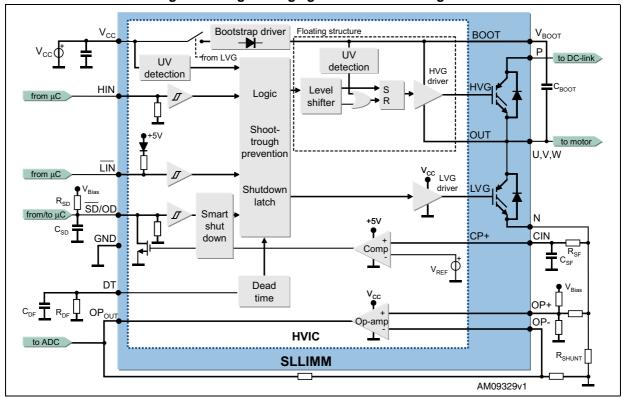

| Figure 7.    | Internal circuit of STGIPL14K60 and STGIPL20K60                              | . 13 |

| Figure 8.    | Stray inductance components of output stage                                  | . 15 |

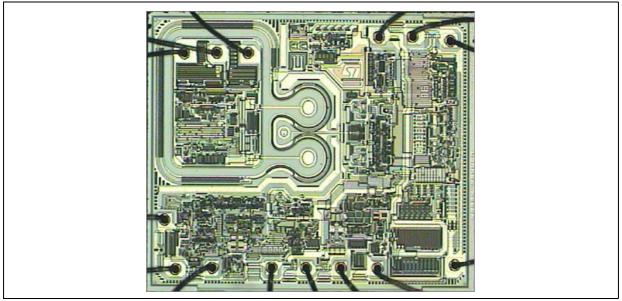

| Figure 9.    | High voltage gate drive die image                                            | . 18 |

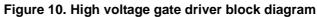

| Figure 10.   | High voltage gate driver block diagram                                       |      |

| Figure 11.   | Logic input configuration for STGIPS10K60A                                   |      |

| Figure 12.   | Logic input configuration for STGIPS14K60, STGIPL14K60, STGIPS20K60, and ST- |      |

| GIPL20K60    |                                                                              |      |

| Figure 13.   | Timing chart of undervoltage lockout function                                | . 22 |

| Figure 14.   | Timing chart of dead time function                                           |      |

| Figure 15.   | Smart shutdown equivalent circuitry                                          |      |

| Figure 16.   | Timing chart of smart shutdown function                                      |      |

| Figure 17.   | Examples of SC protection circuit                                            |      |

| Figure 18.   | Example of SC event                                                          |      |

| Figure 19.   | NTC resistance vs. temperature curve                                         |      |

| Figure 20.   | Example of overtemperature protection circuit                                |      |

| Figure 21.   | 3-phase system                                                               |      |

| Figure 22.   | General advanced current sense scheme and waveforms                          |      |

| Figure 23.   | Bootstrap circuit                                                            |      |

| Figure 24.   | Bootstrap capacitor vs. switching frequency                                  |      |

| Figure 25.   | Initial bootstrap charging time                                              |      |

| Figure 26.   | DCB structure                                                                |      |

| Figure 27.   | PCB structure                                                                |      |

| Figure 28.   | Images and internal view of SDIP-25L package                                 |      |

| Figure 29.   | Images and internal view of SDIP-38L package                                 |      |

| Figure 30.   | Outline drawing of SDIP-25L package                                          |      |

| Figure 31.   | Outline drawing of SDIP-38L package                                          |      |

| Figure 32.   | Pinout of SDIP-25L package (bottom view)                                     |      |

| Figure 33.   | Pinout of SDIP-38L package (bottom view)                                     |      |

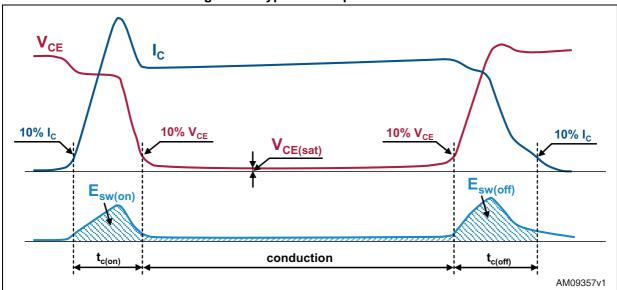

| Figure 34.   | Typical IGBT power losses                                                    |      |

| Figure 35.   | IGBT and diode approximation of the output characteristics                   |      |

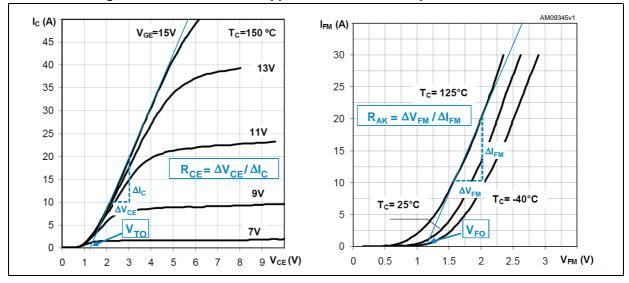

| Figure 36.   | Typical switching waveforms of STGIPL14K60                                   |      |

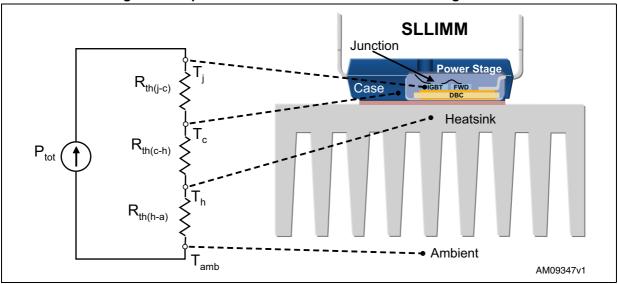

| Figure 37.   | Equivalent thermal circuit with heatsink single IGBT                         |      |

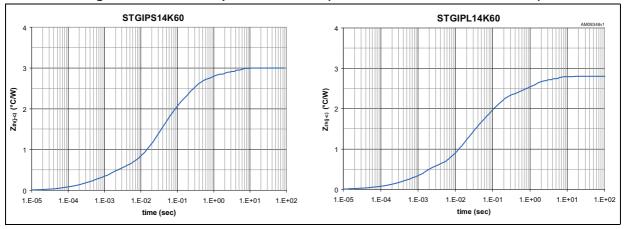

| Figure 38.   | Thermal impedance curves (STGIPS14K60 and STGIPL14K60)                       |      |

| Figure 39.   | Thermal impedance RC Cauer thermal network                                   | . 59 |

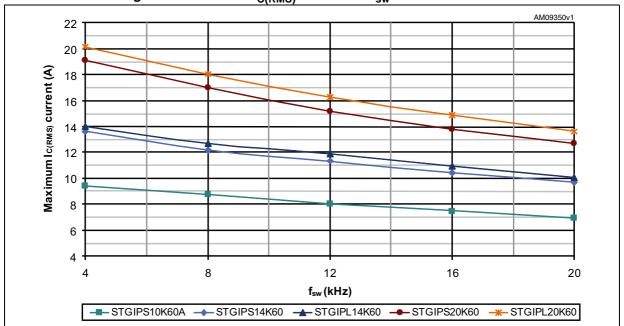

| Figure 40.   | Maximum IC(RMS) current vs. f <sub>sw</sub> simulated curves                 |      |

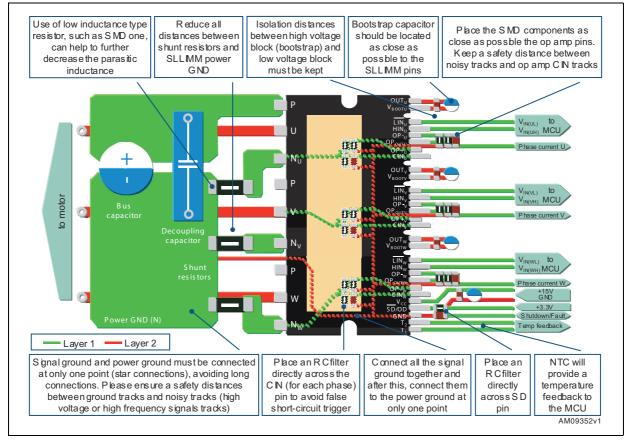

| Figure 41.   | General suggestions 1                                                        |      |

| Figure 42.   | General suggestions 2                                                        |      |

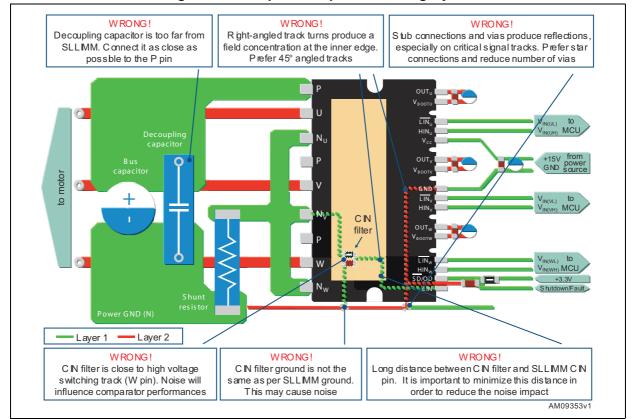

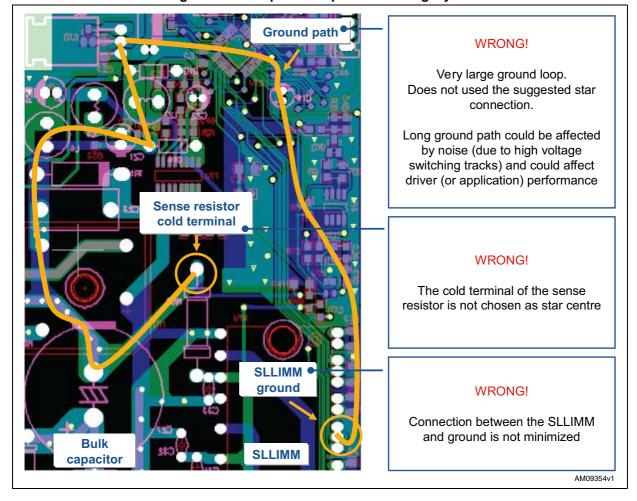

| Figure 43.   | Example 1 of a possible wrong layout                                         |      |

| Figure 44.   | Example 2 of a possible wrong layout                                         |      |

| Figure 45.   | Recommended silicon grease thickness and positioning                         |      |

| Figure 46.   | Measurement point of Cu heatsink flatness                                    |      |

| Figure 47.   | Recommended fastening order of mounting screws                               | . 68 |

| i igui G +1. | resonanciaca lasterning order of modifiing sofews                            | . 55 |

## 1 Inverter design concept and SLLIMM solution

Motor drive applications, ranging from a few tens of watts to mega watts, are mainly based on the inverter concept thanks to the fact that this solution can meet efficiency, reliability, size, and cost constraints required in a number of markets.

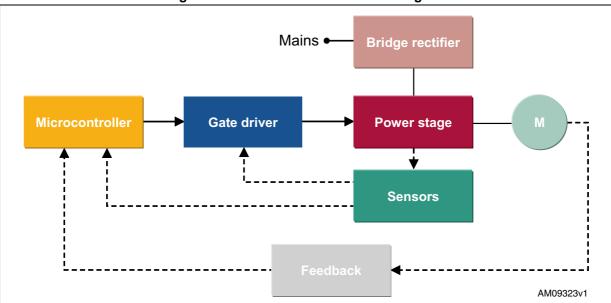

As shown in *Figure 1*, an inverter for motor drive applications is basically composed of a power stage, mainly based on IGBTs and freewheeling diodes; a driving stage, based on high voltage gate drivers; a control unit, based on microcontrollers or DSPs; some optional sensors for protections and feedback signals for controls.

The approach of this solution with discrete devices produces high manufacturing costs associated with high reliability risks, bigger size and higher weight, a considerable number of components and the significant stray inductances and dispersions in the board layout.

Figure 1. Inverter motor drive block diagram

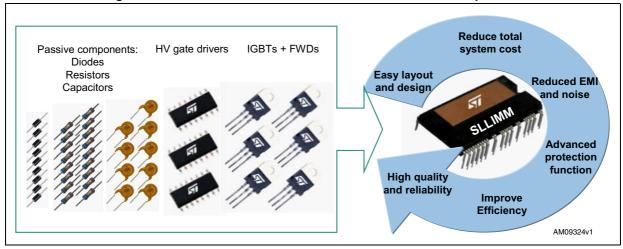

In recent years, the use of intelligent power modules has rapidly increased thanks to the benefits of greater integration levels. The new ST SLLIMM family is able to replace more than 30 discrete devices in a single package. *Figure 2* shows a comparison between a discrete-based inverter and the SLLIMM solution, the advantages of SLLIMM can be easily understood and can be summarized in a significantly improved design time, reduced manufacturing efforts, higher flexibility in a wide range of applications, and increased reliability and quality level.

In addition, the optimized silicon chips in both control and power stages and the optimized board layout provide maximized efficiency, reduced EMI and noise generation, higher levels of protection, and lower propagation delay time.

5//

Figure 2. Discrete-based inverter vs. SLLIMM solution comparison

## 1.1 Product synopsis

The SLLIMM family has been designed to satisfy the requirements of a wide range of final applications in the range of 300 W - 2.0 kW, such as:

- washing machines

- dish washers

- refrigerators

- air conditioning compressor drives

- sewing machines

- pumps

- tools

- low power industrial applications

The main features and integrated functions can be summarized as follows:

- 600 V, 10 30 A ratings

- 3-phase IGBT inverter bridge including:

- six low-loss and short-circuit protected IGBTs

- six low forward voltage drop and soft recovery freewheeling diodes

- three control ICs for gate driving and protection including:

- smart shutdown function

- comparator for fault protection against overcurrent and short-circuit

- op amps for advanced current sensing

- three integrated bootstrap diodes

- interlocking function

- undervoltage lockout

- NTC thermistor for temperature monitor

- open emitter configuration for individual phase current sensing

- DBC fully isolated package for enhanced thermal behavior

- isolation voltage rating of 2500 V<sub>RMS</sub>

- several passive components for IGBT switching speed optimum setting

- gate driver proper biasing and noise filtering.

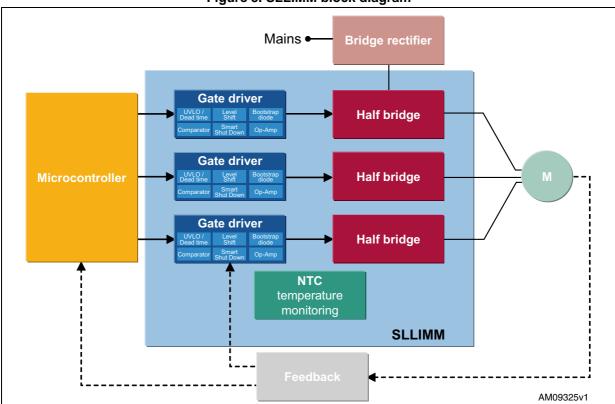

Figure 3 shows the block diagram of SLLIMM included in the inverter solution

Figure 3. SLLIMM block diagram

The power devices (IGBTs and freewheeling diodes), incorporated in the half bridge block, are tailored for a motor drive application delivering the greatest overall efficiency, thanks to the optimized trade-off between conduction and switching power losses and very low EMI generation, as a result of reduced dV/dt and di/dt.

The IC gate drivers have been selected in order to meet two levels of functionality giving the designers more freedom to choose: a basic version which includes the essential features for a cost-effective solution and a fully featured version which provides advanced options for a sophisticated control method.

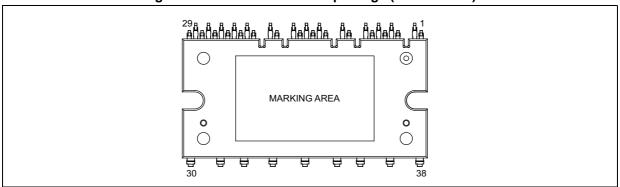

The fully isolated SDIP package is available in a 25-lead version (SDIP-25L) and 38-lead version (SDIP-38L) and offers excellent heat dissipation characteristics, thanks to the state of the art DBC mounting technology, ensuring at the same time, very high voltage isolation rating (2500  $V_{RMS}$ ), compact size and high reliability.

8/72 DocID018441 Rev 5

# 1.2 Product line-up and nomenclature

Table 1. SLLIMM line-up<sup>(1)</sup>

| Footures                                  | Basic version | Fully featured version |               |               |               |  |  |

|-------------------------------------------|---------------|------------------------|---------------|---------------|---------------|--|--|

| Features                                  | STGIPS10K60A  | STGIPS14K60            | STGIPL14K60   | STGIPS20K60   | STGIPL20K60   |  |  |

| Voltage (V)                               | 600           | 600                    | 600           | 600           | 600           |  |  |

| Current @ T <sub>C</sub> =25 °C (A)       | 10            | 14                     | 15            | 18            | 20            |  |  |

| R <sub>thJC</sub> max. single IGBT (°C/W) | 3.8           | 3                      | 2.8           | 2.4           | 2.2           |  |  |

| Package type                              | SDIP-25L      | SDIP-25L               | SDIP-38L      | SDIP-25L      | SDIP-38L      |  |  |

| Package size<br>(mm) X, Y, Z              | 44.4x22.0x5.4 | 44.4x22.0x5.4          | 49.6x24.5x5.4 | 44.4x22.0x5.4 | 49.6x24.5x5.4 |  |  |

| DBC substrate                             | Yes           | Yes                    | Yes           | Yes           | Yes           |  |  |

| NTC                                       | Yes           | No                     | Yes           | No            | Yes           |  |  |

| Integrated bootstrap diode                | Yes           | Yes                    | Yes           | Yes           | Yes           |  |  |

| SD function                               | No            | Yes                    | Yes           | Yes           | Yes           |  |  |

| Comparator for fault protection           | No            | Yes (1 pin)            | Yes (3 pins)  | Yes (1 pin)   | Yes (3 pins)  |  |  |

| Smart shutdown function                   | No            | Yes                    | Yes           | Yes           | Yes           |  |  |

| Op amps for advanced current sensing      | No            | No                     | Yes           | No            | Yes           |  |  |

| Interlocking function                     | Yes           | Yes                    | Yes           | Yes           | Yes           |  |  |

| Undervoltage lockout                      | Yes           | Yes                    | Yes           | Yes           | Yes           |  |  |

| Open emitter configuration                | Yes (3 pins)  | Yes (3 pins)           | Yes (3 pins)  | Yes (3 pins)  | Yes (3 pins)  |  |  |

| 3.3 / 5 V input interface compatibility   | Yes           | Yes                    | Yes           | Yes           | Yes           |  |  |

| High side IGBT input signal               | Active High   | Active High            | Active High   | Active High   | Active High   |  |  |

| Low side IGBT input signal                | Active High   | Active Low             | Active Low    | Active Low    | Active Low    |  |  |

<sup>1.</sup> For additional information and the complete product portfolio, refer to www.st.com/modules.

**Nominal current**

$I_{C}$  current at  $T_{C}\text{=}25~^{\circ}\text{C}$

**W** = Very High frequency (15÷50 kHz) **C** = Medium frequency (4÷20 kHz)

60 X **Special features A** = Basic version **T** = NTC option **-H** = Both active high **G** = 3Φ IGBT + Diode input signal L1 = Single phase SLLIMM™ (IPM) **V**<sub>CES</sub> voltage divided by 10 **Package** L = SDIP-38L **Technology** S = SDIP-25L **K**, **H** = High frequency (8÷20 kHz)

Figure 4. SLLIMM nomenclature

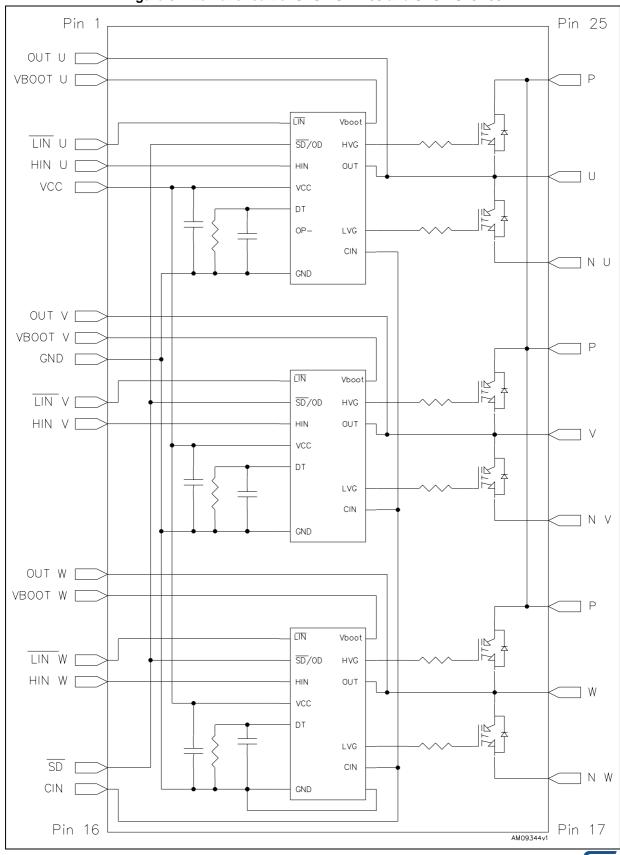

## 1.3 Internal circuit

T1 T2

Pin 16

Pin 1 Pin 25 DUT U ∨B□□T U □ LIN U [ ∨B□□T HIN VCC HIN U [ HVG ACC [ □UT L∨G GND ¬ N U DUT V ∨B□□T ∨ [ GND LIN ∨B□□T H∨G LIN V [ HIN V  $\supset$  N  $\vee$ DUT W [ VBOOT W LIN ∨B□□T HIN VCC H∨G LIN W [ □UT HIN W [ LVG GND

Figure 5. Internal circuit of STGIPS10K60A

\_\_\_ N W

Pin 17

AM09326v1

12/72

DocID018441 Rev 5

Figure 6. Internal circuit of STGIPS14K60 and STGIPS20K60

Figure 7. Internal circuit of STGIPL14K60 and STGIPL20K60

## 1.4 Absolute maximum ratings

The absolute maximum ratings represent the extreme capability of the device and they can be normally used as a worst limit design condition. It is important to note that the absolute maximum value is given according to a set of testing conditions such us temperature, frequency, voltage, and so on. The device performances can change according to the applied condition.

The SLLIMM specifications are described below by using the STGIPL14K60 datasheet as an example. Please refer to the respective product datasheets for a detailed description of other types.

**Symbol** Value Unit **Parameter**  $V_{PN}$ Supply voltage applied between P-N<sub>IJ</sub>, N<sub>V</sub>, N<sub>W</sub> 450 ٧ Supply voltage (surge) applied between P-N<sub>U</sub>, N<sub>V</sub>, N<sub>W</sub> V V<sub>PN(surge)</sub> 500 Collector emitter voltage (V<sub>IN</sub><sup>(1)</sup>=0) ٧ 600  $V_{CES}$  $\pm I_{C}^{(2)}$ Each IGBT continuous collector current at T<sub>C</sub>=25 °C Α 15  $\pm I_{C}^{(3)}$ Each IGBT pulsed collector current 30 Α Each IGBT total dissipation at  $T_C=25~^{\circ}C$ 44 W P<sub>TOT</sub> Short-circuit withstand time, V<sub>CE</sub>=0.5· V<sub>(BR)CES</sub>, T<sub>j</sub>=125 °C, V<sub>CC</sub>=V<sub>boot</sub>=15 V, V<sub>IN</sub> $^{(1)}$ =0÷5 V t<sub>SCW</sub> 5 μs

Table 2. Inverter part of STGIPL14K60

- 1. Applied between  $HIN_U$ ,  $HIN_V$ ,  $HIN_W$ ,  $\overline{LIN}_U$ ,  $\overline{LIN}_V$ ,  $\overline{LIN}_W$  and GND.

- 2. Calculated according to the iterative Equation 1.

- 3. Pulse width limited by max. junction temperature.

#### **Equation 1**

$$I_{C}(T_{C}) = \frac{T_{jmax} - T_{C}}{R_{th(j-c)} \cdot V_{CE(sat)(max)}(@T_{jmax},I_{C}(T_{C}))}$$

- V<sub>PN</sub>: supply voltage applied between P-N<sub>U</sub>, N<sub>V</sub>, N<sub>W</sub>

- V<sub>PN(surge)</sub>: supply voltage (surge) applied between P-N<sub>U</sub>, N<sub>V</sub>, N<sub>W</sub>

- V<sub>CES</sub>: collector emitter voltage

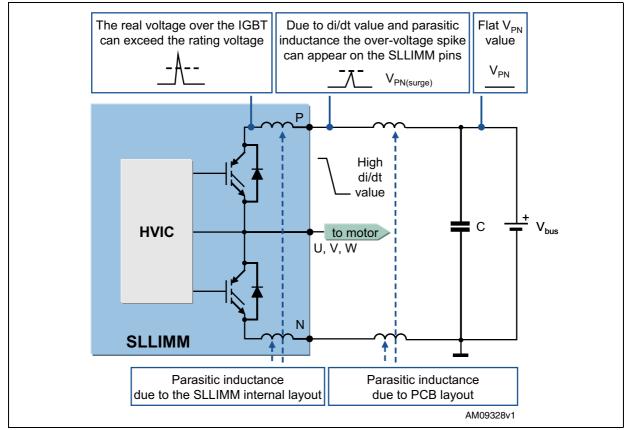

The power stage of SLLIMM is based on IGBTs (and freewheeling diodes) having 600 V V<sub>CES</sub> rating. Considering the SLLIMM internal stray inductances during the commutations, which can generate up to 100 V of surge voltage, the maximum surge voltage between P-N (V<sub>PN(surge)</sub>) allowed is 500 V. At the same time, the maximum supply voltage (in steady-state) applied between P-N (V<sub>PN</sub>) allowed is 450 V because of an additional 50 V of surge voltage generated by the stray inductance between the SLLIMM and the DC-link capacitor.

*Figure 8* shows the parasitic inductances of the output stage. It is possible to note that there are two major components, the first is due to the internal layout of SLLIMM, while the second is due to the layout of the board.

Figure 8. Stray inductance components of output stage

±I<sub>C</sub>: each IGBT continuous collector current

The allowable DC current continuously flowing at collector electrode ( $T_C = 25$  °C). The  $I_C$  parameter is calculated according to *Equation 1*.

• t<sub>SCW</sub>: short-circuit withstand time

The IGBTs incorporated inside the SLLIMM are tailored for a motor control application, therefore, short-circuit self-protection is one of the main module features.

$t_{SCW}$  represents the short-circuit, non-repetitive, withstand time. If the short-circuit conditions exceed the above specifications, the lifetime of the device is drastically shortened. It is strongly recommended that the SLLIMM should not be operated under these conditions.

Table 3. Control part of STGIPL14K60

| Symbol                | Parameter                                                                                                                                                                                 | Value                                           | Unit |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------|

| V <sub>OUT</sub>      | Output voltage applied between $\mathrm{OUT}_{\mathrm{U}},\mathrm{OUT}_{\mathrm{V}},\mathrm{OUT}_{\mathrm{W}},\mathrm{and}$ $\mathrm{GND}(\mathrm{V}_{\mathrm{CC}}\text{=}15~\mathrm{V})$ | V <sub>boot</sub> -21 to V <sub>boot</sub> +0.3 | V    |

| V <sub>CC</sub>       | Low voltage power supply                                                                                                                                                                  | -0.3 to 21                                      | V    |

| V <sub>CIN</sub>      | Comparator input voltage                                                                                                                                                                  | -0.3 to V <sub>CC</sub> +0.3                    | V    |

| V <sub>boot</sub>     | Bootstrap voltage                                                                                                                                                                         | -0.3 to 620                                     | V    |

| V <sub>IN</sub>       | Logic input voltage applied between HIN, $\overline{\text{LIN}}$ and GND                                                                                                                  | -0.3 to 15                                      | V    |

| V <sub>SD/OD</sub>    | Open drain voltage                                                                                                                                                                        | -0.3 to 15                                      | V    |

| dV <sub>OUT</sub> /dt | Allowed output slew rate                                                                                                                                                                  | 50                                              | V/ns |

#### V<sub>CC</sub>: low voltage power supply

V<sub>CC</sub> represents the supply voltage of the control part. A local filtering is recommended to enhance the SLLIMM noise immunity. Generally, the use of one electrolytic capacitor (with a greater value but not negligible ESR) and a good quality (low ESR, low ESL) filter capacitor (hundreds of nF), faster than the electrolytic one to provide current, is suggested. Small filter capacitors are already connected inside the SLLIMM, directly on the involved pins (see internal circuits *Figure 5*, *6*, and *7*).

Please refer to *Table 4* in order to properly drive the SLLIMM.

Table 4. Supply voltage and operation behavior

| V <sub>CC</sub> voltage (typ. value) <sup>(1)</sup> | Operating behavior                                                                                                                        |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| < 12 V                                              | As the voltage is lower than the UVLO threshold the control circuit is not fully turned on. A perfect functionality cannot be guaranteed. |

| 12 V – 13.5 V                                       | IGBTs can work, however conduction and switching losses increase due to low voltage gate signal.                                          |

| 13.5 V – 18 V                                       | Recommended value (see relevant datasheets).                                                                                              |

| 18 V – 21 V                                         | IGBTs can work. Switching speed is faster and saturation current higher, increasing short-circuit broken risk and EMI issues.             |

| > 21 V                                              | Control circuit is destroyed. Absolute max. rating is 21 V.                                                                               |

<sup>1.</sup> Except for STGIPS10K60A. For further information please refer to the relevant datasheet.

Table 5. Total STGIPL14K60 system

| Symbol           | Parameter                                                                                          | Value      | Unit |

|------------------|----------------------------------------------------------------------------------------------------|------------|------|

| V <sub>ISO</sub> | Isolation withstands voltage applied between each pin and heatsink plate (AC voltage, t = 60 sec.) | 2500       | V    |

| T <sub>j</sub>   | Operating junction temperature                                                                     | -40 to 150 | °C   |

| T <sub>C</sub>   | Module case operation temperature                                                                  | -40 to 125 | °C   |

16/72 DocID018441 Rev 5

#### 2 Electrical characteristics and functions

In this section the main electrical characteristics of the power stage are discussed, together with a detailed description of all the SLLIMM functions.

#### 2.1 IGBTs

The SLLIMM achieves power savings in the inverter stage thanks to the use of IGBTs manufactured with the proprietary advanced PowerMESH™ process.

These power devices, optimized for the typical motor control switching frequency, offer an excellent trade-off between voltage drop ( $V_{CE(sat)}$ ) and switching speed ( $t_{fall}$ ), and therefore minimize the two major sources of energy loss, conduction and switching, reducing the environmental impact of daily-use equipment. A full analysis on the power losses of the complete system is reported in *Section 4: Power losses and dissipation*.

This IGBT family is capable of surviving short-circuits lasting up to 5 microseconds, as expected by targeted applications.

## 2.2 Freewheeling diodes

The Turbo 2 ultrafast high voltage diodes have been adequately selected for the SLLIMM family and carefully tuned to achieve the best  $t_{rr}/V_F$  trade-off and softness as freewheeling diodes in order to further improve the total performance of the inverter and significantly reduce the electromagnetic interference (EMI) in motor control applications which are quite sensitive to this phenomena.

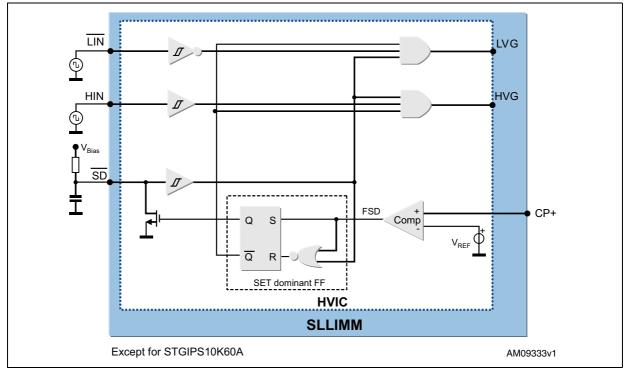

## 2.3 High voltage gate drivers

The SLLIMM is equipped with a versatile high voltage gate driver IC (HVIC), designed using BCD offline (Bipolar, CMOS, and DMOS) technology (see *Figure 9*) and particularly suited to field oriented control (FOC) motor driving applications, able to provide all the functions and current capability necessary for high side and low side IGBT driving. This driver can be used in all applications where high voltage shifted control is necessary and it includes a patented internal circuitry which replaces the external bootstrap diode.

Each high voltage gate driver chip controls two IGBTs in half bridge topology, offering the basic functions such as dead time, interlocking, integrated bootstrap diode, and also the advanced features such as smart shutdown (patented), fault comparator, and a dedicated high performance op amp for advanced current sensing. A schematic summary of the features by device are listed in *Table 1*.

In this application note the main characteristics of a high voltage gate drive related to the SLLIMM are discussed. For a greater understanding, please refer to the AN2738 application note.

Figure 9. High voltage gate drive die image

57/

#### 2.3.1 Logic inputs

The high voltage gate driver IC has two logic inputs, HIN and LIN, to separately control the high side and low side outputs, HVG and LVG. Please refer to *Table 1* for the input signal logics by device.

In order to prevent any cross conduction between high side and low side IGBT a safety time (dead time) is introduced (see Section 2.3.4: Dead time and interlocking function management for further details).

All the logic inputs are provided with hysteresis (~1 V) for low noise sensitivity and are TTL/CMOS 3.3 V compatible. Thanks to this low voltage interface logic compatibility, the SLLIMM can be used with any kind of high performance controller, such as microcontrollers, DSPs or FPGAs.

As shown in the block diagrams of *Figure 11* and *Figure 12*, the logic inputs have internal pull-down (or pull-up) resistors in order to set a proper logic level in case of interruption in the logic lines. If logic inputs are left floating, the gate driver outputs LVG and HVG are set to low level. This simplifies the interface circuit by eliminating the six external resistors and, therefore saving cost, board space and number of components.

Figure 11. Logic input configuration for STGIPS10K60A

Figure 12. Logic input configuration for STGIPS14K60, STGIPL14K60, STGIPS20K60, and STGIPL20K60

The typical values of the integrated pull-up/down resistors are shown in *Table 6*:

Table 6. Integrated pull-up/down resistor values

| Input pin                                                                                                                    | PN                                                       | Input pin logic | Internal pull-up | Internal pull-down |

|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------|------------------|--------------------|

| High side gate driving HIN <sub>U</sub> , HIN <sub>V</sub> , HIN <sub>W</sub>                                                | STGIPS10K60A                                             | Active high     |                  | 500 kΩ             |

| Low side gate driving LIN <sub>U</sub> , LIN <sub>V</sub> , LIN <sub>W</sub>                                                 | STGIPS10K60A                                             | Active high     |                  | 500 kΩ             |

| High side gate driving HIN <sub>U</sub> , HIN <sub>V</sub> , HIN <sub>W</sub>                                                | STGIPS14K60<br>STGIPL14K60<br>STGIPS20K60<br>STGIPL20K60 | Active high     |                  | 85 kΩ              |

| Low side gate driving $\overline{\text{LIN}}_{\text{U}}, \overline{\text{LIN}}_{\text{V}}, \overline{\text{LIN}}_{\text{W}}$ | STGIPS14K60<br>STGIPL14K60<br>STGIPS20K60<br>STGIPL20K60 | Active low      | 720 kΩ           |                    |

| SD / OD shutdown                                                                                                             | STGIPS14K60<br>STGIPL14K60<br>STGIPS20K60<br>STGIPL20K60 | Active low      |                  | 125 kΩ             |

577

20/72 DocID018441 Rev 5

#### 2.3.2 High voltage level shift

The built-in high voltage level shift allows direct connection between the low voltage control inputs and the high voltage power half bridge in any power application up to 600 V. It is obtained thanks to the BCD offline technology which integrates, in the same die bipolar devices, low and medium voltage CMOS for analog and logic circuitry and high voltage DMOS transistors with a breakdown voltage in excess of 600 V. This key feature eliminates the need for external optocouplers, resulting in significant savings regarding component count and power losses. Other advantages are high-frequency operation and short input-to-output delays.

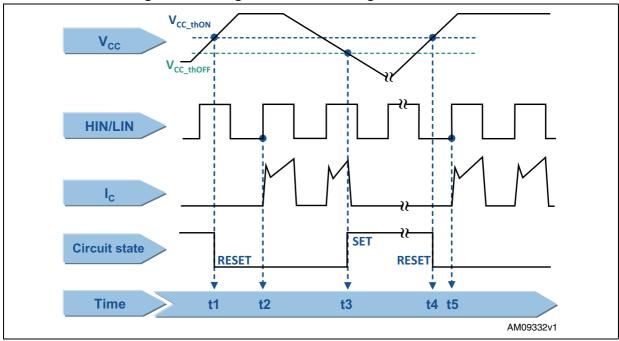

#### 2.3.3 Undervoltage lockout

The SLLIMM supply voltage  $V_{CC}$  is continuously monitored by an undervoltage lockout (UVLO) circuitry which turns off the gate driver outputs when the supply voltage goes below the  $V_{CC\_thOFF}$  threshold specified on the datasheet and turns on the IC when the supply voltage goes above the  $V_{CC\_thON}$  voltage. A hysteresis of about 1.5 V is provided for noise rejection purposes. The high voltage floating supply  $V_{boot}$  is also provided with a similar undervoltage lockout circuitry. When the driver is in UVLO condition, both gate driver outputs are set to low level, setting the half bridge power stage output to high impedance.

The timing chart of undervoltage lockout, plotted in *Figure 13*, is based on the following steps:

- t1: when the V<sub>CC</sub> supply voltage raises the V<sub>CC\_thON</sub> threshold, the gate driver starts to work after the next input signal HIN/LIN is on. The circuit state becomes RESET.

- t2: input signal HIN/LIN is on and the IGBT is turned on.

- t3: when the V<sub>CC</sub> supply voltage goes below the V<sub>CC\_thOFF</sub> threshold, the UVLO event is detected. The IGBT is turned off in spite of input signal HIN/LIN. The state of the circuit is now SET.

- t4: the gate driver re-starts once the V<sub>CC</sub> supply voltage again raises the V<sub>CC\_thON</sub> threshold.

- t5: input signal HIN/LIN is on and the IGBT is turned on again.

Figure 13. Timing chart of undervoltage lockout function

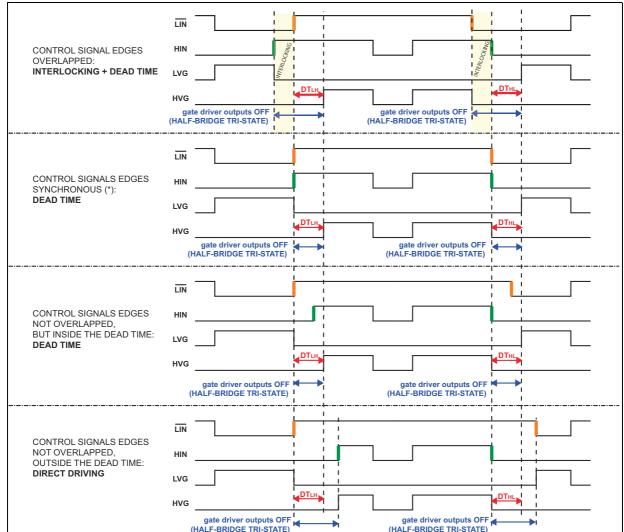

#### 2.3.4 Dead time and interlocking function management

In order to prevent any possible cross-conduction between high side and low side IGBTs, the SLLIMM provides both the dead time and the interlocking functions. The interlocking function is a logic operation which sets both the outputs to low level when the inputs are simultaneously active. The dead time function is a safety time introduced by the device between the falling edge transition of one driver output and the rising edge of the other output. If the rising edge set externally by the user occurs before the end of this dead time, it is ignored and results as delayed until the end of the dead time.

|                                             | Logic i | nput (V <sub>I</sub> ) | Outputs |     |  |

|---------------------------------------------|---------|------------------------|---------|-----|--|

| Condition                                   | LIN     | HIN                    | LVG     | HVG |  |

| Interlocking<br>half bridge tri-state       | Н       | Н                      | L       | L   |  |

| 0 "logic state"<br>half bridge tri-state    | L       | L                      | L       | L   |  |

| 1 "logic state" low side direct driving     | Н       | L                      | Н       | L   |  |

| 1 "logic state"<br>high side direct driving | L       | Н                      | L       | Н   |  |

Table 7. Interlocking function truth table of STGIPS10K60A

The dead time is internally set at 320 ns as the typical value of STGIPS10K60A.

22/72 DocID018441 Rev 5

Table 8. Interlocking function truth table of STGIPS14K60, STGIPL14K60, STGIPS20K60, and STGIPL20K60

| Condition                                   | Logic input (V <sub>I</sub> ) |     |     | Outputs |     |

|---------------------------------------------|-------------------------------|-----|-----|---------|-----|

| Condition                                   | SD                            | LIN | HIN | LVG     | HVG |

| Shutdown enable<br>half bridge tri-state    | L                             | Х   | Х   | L       | L   |

| Interlocking<br>half bridge tri-state       | Н                             | L   | Н   | L       | L   |

| 0 "logic state"<br>half bridge tri-state    | Н                             | Н   | L   | L       | L   |

| 1 "logic state"<br>low side direct driving  | Н                             | L   | L   | Н       | L   |

| 1 "logic state"<br>high side direct driving | Н                             | Н   | Н   | L       | Н   |

Note: X: not important.

The dead time is internally set at 600 ns as typical value. In *Figure 14* the details of dead time and interlocking function management of the STGIPS14K60, STGIPL14K60, STGIPS20K60, and STGIPL20K60 products are described.

Figure 14. Timing chart of dead time function

#### 2.3.5 Comparators for fault sensing

The SLLIMM family integrates up to three comparators (with reference to the product line-up in *Table 1*) intended for advanced fault protection, such as overcurrent, overtemperature or any other type of fault measurable via a voltage signal. Each comparator has an internal reference voltage  $V_{REF}$ , specified in the datasheet, on its inverting input (see *Figure 10*), while the non-inverting input is available on  $C_{IN}$  pins (one per half bridge). The comparators input can be connected to an external shunt resistor, in order to implement a simple overcurrent or short-circuit detection function, as discussed in detail in *Section 2.3.6*: *Short-circuit protection and smart shutdown function*. Nevertheless, in the case of three internal comparators, they can be separately used in order to implement three independent controls.

24/72 DocID018441 Rev 5

#### 2.3.6 Short-circuit protection and smart shutdown function

The SLLIMM is able to monitor the output current and provide protection against overcurrent and short-circuit conditions in a very short time (comparator triggering to high/low side driver turn-off propagation delay  $t_{isd}$  = 200 ns), thanks to the smart shutdown function. This feature is based on an innovative patented circuitry which provides an intelligent fault management operation and greatly reduces the protection intervention delay independently on the protection time duration which can be set as desired by the device user.

As already mentioned in Section 2.3.5: Comparators for fault sensing and shown in Figure 10, each comparator input can be connected to an external shunt resistor,  $R_{SHUNT}$ , in order to implement a simple overcurrent detection function. An RC filter network ( $R_{SF}$  and  $C_{SF}$ ) is necessary to prevent erroneous operation of the protection. The output signal of the comparators is fed to an integrated MOSFET with the open drain available on the  $\overline{SD}/OD$  pin, shared with the  $\overline{SD}$  input. When the comparator triggers, the device is set in shutdown state and all its outputs are set to low level, leaving the half bridge in tri-state. In common overcurrent protection architectures, usually the comparator output is connected to the SD input and an external RC network ( $R_{SD}$  and  $C_{SD}$ ) is connected to this  $\overline{SD}/OD$  line in order to provide a mono-stable circuit which implements a protection time when a fault condition occurs.

Contrary to common fault detection systems, the new smart shutdown structure allows to immediately turn off the output gate driver in the case of fault, without waiting for the external capacitor to be discharged. This strategy minimizes the propagation delay between the fault detection event and the actual outputs switch off. In fact, the time delay between the fault and outputs disabling is not dependent on the RC value of the external SD circuitry but, thanks to the new architecture, has a preferential path internally in the driver. Then the device immediately turns off the driver outputs and latches the turn-on of the open drain switch, until the SD signal has reached its lower threshold. After the SD signal goes below the lower threshold, the open drain is switched off (see *Figure 16*).

The smart shutdown system provides the possibility to increase the value of the external RC network across the SD pin (sized to fix the disable time generated after the fault event) as much as desired by the user without compromising the intervention time delay of the SLLIMM protection.

A block diagram of the smart shutdown architecture is depicted in Figure 15.

Figure 15. Smart shutdown equivalent circuitry

In normal operation the outputs follow the commands received from the respective input signals.

When a fault detection event occurs, the fault signal (FSD) is set to high by the fault detection circuit output and the FF receives a SET input signal. Consequently, the FF outputs set the SLLIMM output signals to low level and, at the same time, turn on the open drain MOSFET which works as active pull-down for the  $\overline{SD}$  signal. Note that the gate driver outputs stay at low level until the  $\overline{SD}$  pin has experienced both a falling edge and a rising edge, although the fault signal could be returned to low level immediately after the fault sensing. In fact, even if the FF is reset by the falling edge of the  $\overline{SD}$  input, the  $\overline{SD}$  signal also works as enable for the outputs, thanks to the two AND ports. Moreover, once the internal open drain transistor has been activated, due to the latch, it cannot be turned off until the  $\overline{SD}$  pin voltage reaches the low logic level. Note that, since the FF is SET dominant, oscillations of the  $\overline{SD}$  pin are avoided if the fault signal remains steady at high level.

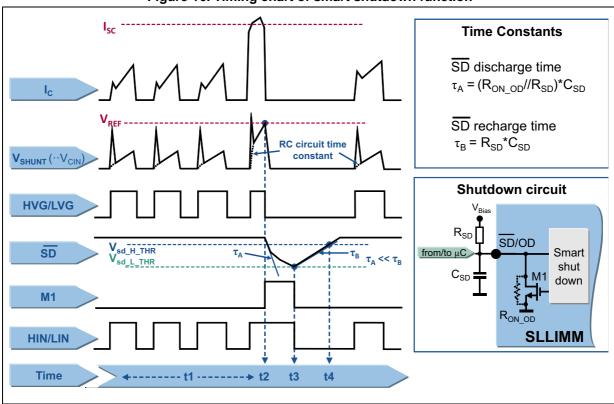

#### 2.3.7 Timing chart of short-circuit protection and smart shutdown function

With reference to *Figure 16*, the short-circuit protection is based on the following steps:

- t1: when the output current is lower than the max. allowed level, the SLLIMM is working in normal operation.

- t2: when the output current reaches the max. allowed level (I<sub>SC</sub>), the overcurrent/short-circuit event is detected and the protection is activated. The voltage across the shunt resistor, and then on the C<sub>IN</sub> pin, exceeds the V<sub>REF</sub> value, the comparator triggers, setting the device in shutdown state and both its outputs are set to low level leading the half bridge to tri-state. The smart shutdown switches off the IGBT gate (HVG, LVG) through a preferential path (200 ns as typical internal delay time) and, at the same time, it switches on the M1 internal MOSFET. The SD signal starts the discharge phase and its value drops with a time constant τ<sub>A</sub>. The time constant τ<sub>A</sub> value is given by:

26/72 DocID018441 Rev 5

#### **Equation 2**

$$\tau_{A} = (R_{ON} - OD / R_{SD}) \cdot C_{SD}$$

• t3: the SD signal reaches the lower threshold  $V_{sd\_L\_THR}$  and the control unit switches off the input HIN and LIN. The smart shutdown is disabled (M1 off) and SD can rise up with a time constant  $\tau_B$ , given by:

#### **Equation 3**

$$\tau_B = R_{SD} \cdot C_{SD}$$

t4: when the SD signal reaches the upper threshold V<sub>sd\_H\_THR</sub>, the system is reenabled.

Figure 16. Timing chart of smart shutdown function

### 2.3.8 Current sensing shunt resistor selection

As previously discussed, the shunt resistors  $R_{SHUNT}$  externally connected between the N pin and ground (see *Figure 10*) are used to realize the overcurrent detection.

When the output current exceeds the short-circuit reference level ( $I_{SC}$ ), the  $C_{IN}$  signal overtakes the  $V_{REF}$  value and the short-circuit protection is active. For a reliable and stable operation the current sensing resistor should be a high quality, low tolerance non-inductive type. In fact, stray inductance in the circuit, which includes the layout, the RC filter, and also the shunt resistor, must be minimized in order to avoid undesired short-circuit detection.

For these reasons, the shunt resistor and the filtering components must be placed as close as possible to the SLLIMM pins, for additional suggestions refer to Section 5.1: Layout suggestions.

The value of the current sense resistor can be calculated by following different guidelines, functions of the design specifications, or requirements. A common criterion is presented here based on the following steps:

- Defining of the overcurrent threshold value (I<sub>OC\_th</sub>). For example, it can be fixed

considering the IGBT typical working current in the application and adding 20-30% as

overcurrent.

- Calculation of the shunt resistor value according to the conditioning network. An

example of the conditioning network is shown in *Figure 22*. Further details can be

found in the user manuals listed (see References 7, References 8, and References 9).

- Selection of the closest shunt resistor commercial value.

- Calculation of the power rating of the shunt resistor, taking into account that this

parameter is strongly temperature dependent. Therefore, the power derating ratio of

the shunt resistor, ΔP(T)%, shown in the manufacturer's datasheet, must be considered

in the calculation as follows:

#### **Equation 4**

$$P_{SHUNT}(T) = \frac{R_{SHUNT} \cdot I_{RMS}^2}{\Delta P(T)\%}$$

where I<sub>RMS</sub> is the IGBT RMS working current.

For a proper selection of the shunt resistor, a safety margin of at least 30% is recommended on the calculated power rating.

#### 2.3.9 RC filter network selection

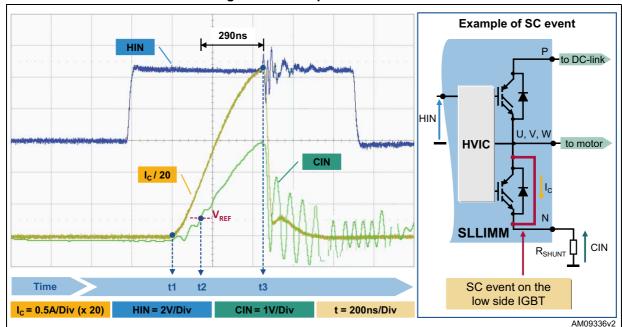

Two options of shunt (1- or 3-shunt) resistor circuit can be adopted in order to implement different control technique and short-circuit protection, as shown in *Figure 17*.

1-shunt resistor circuit

AM09335v1

Figure 17. Examples of SC protection circuit

A RC filter network is required to prevent undesired short-circuit operation due to the noise on the shunt resistor.

Both solutions allow to detect the total current in all three phases of the inverter. The filter is based on the  $R_{SF}$  and  $C_{SF}$  network and its time constant is given by:

#### **Equation 5**

$$t_{SF} = R_{SF} \cdot C_{SF}$$

In addition to the RC time constant, the turn-off propagation delay of the gate driver,  $t_{isd}$  (specified in the datasheet) and the IGBT turn-off time (in the range of tens of ns), must be considered in the total delay time ( $t_{Total}$ ), which is the time necessary to completely switch off the IGBT once the short-circuit event is detected. Therefore, the  $t_{Total}$  is calculated as follows:

#### **Equation 6**

$$t_{Total} = t_{SF} + t_{isd} + t_{off}$$

also considering that the IGBT short-circuit withstand time ( $t_{SC}$ ) is 5  $\mu$ s, the  $t_{SF}$  is recommended to be set in the range of 1~2  $\mu$ s.

In the case of a 3-shunt resistors circuit, a specific control technique can be implemented by using the three shunt resistors ( $R_{SHUNT\_U}$ ,  $R_{SHUNT\_V}$  and  $R_{SHUNT\_W}$ ) able to monitor each phase current.

An example of a short-circuit event is shown in *Figure 18*, where it is possible to note the very fast protection, thanks to the smart shutdown function, against fault events. The main steps are:

- t1: collector current I<sub>C</sub> starts to rise. SC event is not detected yet due to the RC network on the C<sub>IN</sub> pin

- t2: voltage on V<sub>CIN</sub> reaches the V<sub>REF</sub>. SC event is detected and the smart shutdown starts to turn off the SLLIMM.

- t3: the SLLIMM is definitively turned off in less than 300 ns (including the td(off) time of IGBT) from SC detection.

Finally, the total disable time is t3-t2 and the total SC action time is t3-t1.

Figure 18. Example of SC event

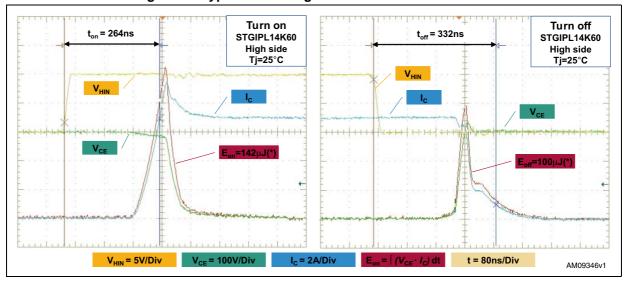

#### 2.3.10 Overtemperature protection

STGIPS10K60A, STGIPL14K60, and STGIPL20K60 are equipped with a negative temperature coefficient (NTC) thermistor for an easy overtemperature protection, in the case of slow case temperature drift or just for the temperature measurements, sending this information to the microcontroller in real-time. Due to the thermal impedance of SLLIMM and its own time constant, the NTC thermistor is not suited to detect rapid junction temperature rise of the power devices directly. Therefore, it cannot be used for short-circuit or overcurrent protection, but only for slow changes in temperature monitoring.

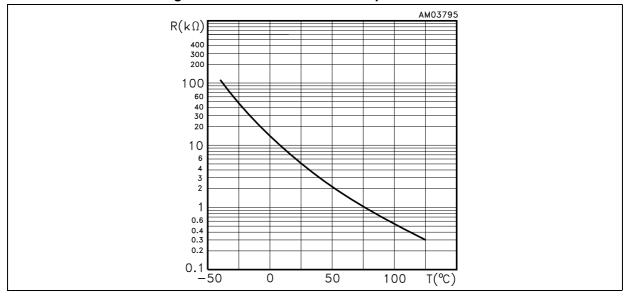

The resistance versus temperature characteristic of NTC thermistor, represented in *Figure 19*, is non-linear and is described by the following expression:

#### **Equation 7**

$$R(T) = R_{25} \cdot e^{B\left(\frac{1}{T} - \frac{1}{298}\right)}$$

**57**

30/72 DocID018441 Rev 5

where T is the temperature in Kelvin, B and  $R_{25}$ , respectively, are a constant value in the SLLIMM working range and the resistance value at 25 °C, both parameters are shown in the datasheet.

Figure 19. NTC resistance vs. temperature curve

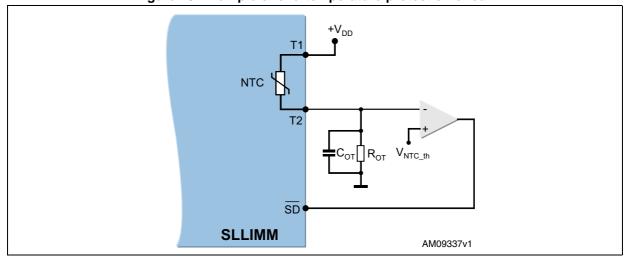

An easy circuit, using a voltage divider, for both overtemperature protection and temperature monitoring, is shown in *Figure 20*:

Figure 20. Example of overtemperature protection circuit

The external comparator is used to send a shutdown signal to the SLLIMM in case of overtemperature. The  $V_{NTC\_th}$  is a threshold voltage, fixed by design, and connected on the non inverting input, whilst the inverting input is connected on a voltage divider based on the NTC and  $R_{OT}$  resistors. When voltage on the inverting input exceeds the  $V_{NTC\_th}$  value the comparator triggers, pulling down the  $\overline{SD}$  and, consequently, switching off the IGBTs.

For a proper sizing of the voltage divider, first of all the maximum allowed temperature level  $(T_{OT\_Max})$  must be fixed, consequently the thermistor resistance is given by *Equation 7*, as well as by *Figure 19*. The value of  $R_{OT}$  resistance can be calculated by using the voltage divider formula:

#### **Equation 8**

$$V^{-}(T) = \frac{R_{OT}}{R_{NTC}(T) + R_{OT}} \cdot V_{DD}$$

taking into account that, if  $T = T_{OT\ Max}$  then  $V^{-}(T_{OT\ Max}) = V_{NTC\ th}$

The maximum allowed power on the thermistor should not exceed 50 mW in all the operating range, in order to guarantee a safe working condition and avoid power consumption affecting the temperature measurement through self-heating. Therefore, considering (T =  $T_{OT\ Max}$ ), it must be:

#### **Equation 9**

$$R_{NTC} \cdot I^2 = R_{NTC} \cdot \left(\frac{V_{DD}}{R_{NTC} + R_{OT}}\right)^2 \le 50 \text{mW}$$

Finally, to increase the noise immunity of the NTC thermistor, it is recommended to parallel a decoupling capacitor ( $C_{OT}$ ), whose value must be between 10 to 100 nF.

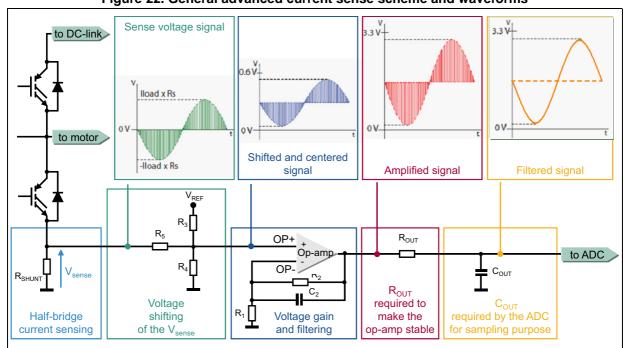

#### 2.3.11 Op amps for advanced current sensing

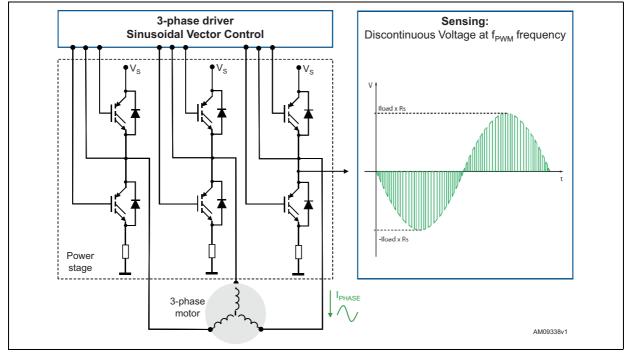

The SLLIMM devices, in the SDIP-38L package, integrate also three operational amplifiers optimized for field oriented control (FOC) applications. In a typical FOC application the currents in the three half bridges are sensed using a shunt resistor. The analog current information is transformed into a discontinuous sense voltage signal, having the same frequency as the PWM signal driving the bridge. The sense voltage is a bipolar analog signal, whose sign depends on the direction of the current (see *Figure 21*):

Figure 21. 3-phase system

The sense voltage signals must be provided to an A/D converter. They are usually shifted and amplified by dedicated op amps in order to exploit the full range of the A/D converter. The typical scheme and principle waveforms are shown in *Figure 22*:

Figure 22. General advanced current sense scheme and waveforms

5

ADCs used in vector control applications have a typical full scale range (FSR) of about 3.3 V. The sense signals must be shifted and centered on FSR/2 voltage (about 1.65 V) and amplified with a gain which provides the matching between the maximum value of the sensed signal and the FSR of the ADC. Some typical examples of sense network sizing can be found in the user manuals listed (see References 7, References 8, and References 9).

#### 2.3.12 Bootstrap circuit

In the 3-phase inverter the emitters of the low side IGBTs are connected to the negative DC bus ( $V_{DC}$ -) as common reference ground, which allows all low side gate drivers to share the same power supply, while, the emitter of high side IGBTs is alternately connected to the positive ( $V_{DC}$ -) and negative ( $V_{DC}$ -) DC bus during the running conditions.

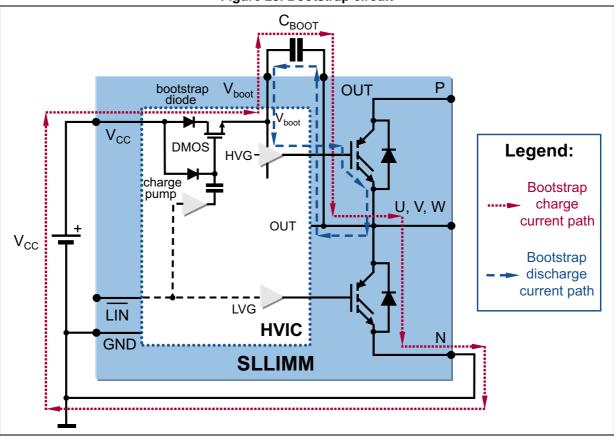

A bootstrap method is a simple and cheap solution to supply the high voltage section. This function is normally accomplished by a high voltage fast recovery diode. The SLLIMM family includes a patented integrated structure that replaces the external diode. It is realized with a high voltage DMOS driven synchronously with the low side driver (LVG) and a diode in series. An internal charge pump provides the DMOS driving voltage.

The operation of the bootstrap circuit is shown in *Figure 23*. The floating supply capacitor  $C_{BOOT}$  is charged, from the  $V_{CC}$  supply, when the  $V_{OUT}$  voltage is lower than the  $V_{CC}$  voltage (e.g. low side IGBT is on), through the bootstrap diode and the DMOS path with reference to the "bootstrap charge current path". During the high side IGBT on phase, the bootstrap circuit provides the right gate voltage to properly drive the IGBT (see "bootstrap discharge current path"). This circuit is iterated for all three half bridges.

Figure 23. Bootstrap circuit

The value of the  $C_{BOOT}$  capacitor should be calculated according to the application condition and must take the following into account:

- voltage across C<sub>BOOT</sub> must be maintained at a value higher than the undervoltage lockout level for the IC driver. This enables the high side IGBT to work with a correct gate voltage (lower dissipation and better overall performances). Bear in mind that if a voltage below the UVLO threshold is applied on the bootstrap channel, the IC disables itself (no output) without any fault signal.

- the voltage across C<sub>BOOT</sub> is affected by different components such as drop across the integrated bootstrap structure, drop across the low side IGBT, and others.

- when the high side IGBT is on, the C<sub>BOOT</sub> capacitor discharges mainly to provide the right IGBT gate charge but other phenomena must be considered such as leakage currents, quiescent current, etc.

#### 2.3.13 Bootstrap capacitor selection

A simple method to properly size the bootstrap capacitor considers only the amount of charge that is needed when the high voltage side of the driver is floating and IGBT gate is driven once. This approach does not take into account either the duty cycle of the PWM, or the fundamental frequency of the current.

During the bootstrap capacitor charging phase, the low side IGBT is on and the voltage across  $C_{BOOT}$  ( $V_{CBOOT}$ ) can be calculated as follows:

#### **Equation 10**

$$V_{CBOOT} = V_{CC} - V_F - V_{RDS(on)} - V_{CE(sat)max}$$

where:

V<sub>CC</sub>: supply voltage of gate driver

V<sub>F</sub>: bootstrap diode forward voltage drop

V<sub>CE(sat)max</sub>: maximum emitter collector voltage drop of low side IGBT

V<sub>RDS(on)</sub>: DMOS voltage drop

The dimension of the bootstrap capacitance  $C_{BOOT}$  value is based on the minimum voltage drop ( $\Delta V_{CBOOT}$ ) to guarantee when the high side IGBT is on, and must be:

#### **Equation 11**

$$\Delta V_{CBOOT} = V_{CC} - V_F - V_{RDS(on)} - V_{GE(min)} - V_{CE(sat)max}$$

under the condition:

#### **Equation 12**

$$V_{CBOOT(min)} > V_{BS\_thON}$$

where:

V<sub>GF(min)</sub>: minimum gate emitter voltage of high side IGBT

V<sub>BS\_thON</sub>: bootstrap turn-on undervoltage threshold (maximum value, see datasheet)

Considering the factors contributing to V<sub>CBOOT</sub> decreasing, the total charge supplied by the bootstrap capacitor (during high side on phase) is:

#### **Equation 13**

where:

Q<sub>GATE</sub>: total IGBT gate charge

$I_{LKGE}$ : IGBT gate emitter leakage current  $I_{QBO}$ : bootstrap circuit quiescent current  $I_{LK}$ : bootstrap circuit leakage current

I<sub>LKDiode</sub>: bootstrap diode leakage current

I<sub>LKCap</sub>: bootstrap capacitor leakage current (relevant when using an electrolytic capacitor but can be ignored if other types of capacitors are used)

t<sub>Hon</sub>: high side on time

Q<sub>LS</sub>: charge required by the internal level shifters

Finally, the minimum size of the bootstrap capacitor is:

#### **Equation 14**

$$C_{BOOT} = \frac{Q_{TOT}}{\Delta V_{CBOOT}}$$

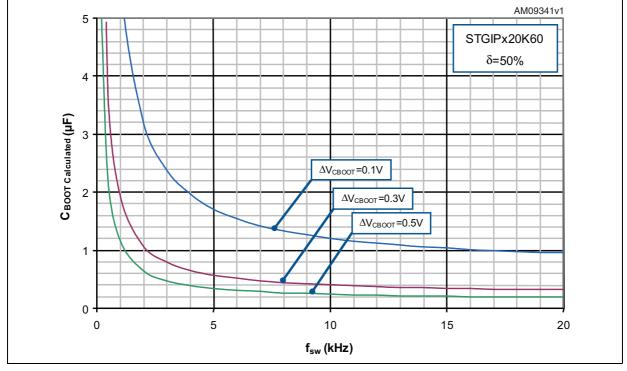

For an easier selection of bootstrap capacitor, *Figure 24* shows the behavior of  $C_{BOOT}$  (calculated) versus switching frequency ( $f_{sw}$ ), with different values of  $\Delta V_{CBOOT}$ , corresponding to *Equation 14* for a continuous sinusoidal modulation and for STGIPS20K60 and STGIPL20K60 (worst case) and a duty cycle  $\delta$  = 50%. For all the other devices the bootstrap capacitor can be calculated using the same curve.

Figure 24. Bootstrap capacitor vs. switching frequency

Considering the limit cases during the PWM control and further leakages and dispersions in the board layout, the capacitance value to use in the bootstrap circuit must be selected two or three times higher than the  $C_{BOOT}$  calculated in the graph of *Figure 24*. The bootstrap capacitor should be with a low ESR value for a good local decoupling, therefore, in case an electrolytic capacitor is used, a good quality (low ESR, low ESL) filter capacitor placed directly on the SLLIMM pins is strictly recommended.

### 2.3.14 Initial bootstrap capacitor charging

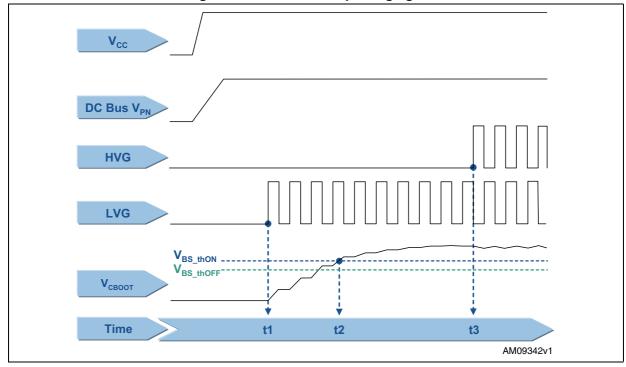

During the startup phase, the bootstrap capacitor must be charged for a suitable time to complete the initial charging time ( $t_{CHARGE}$ ), which is, at least, the time  $V_{CBOOT}$  needs to exceed the turn-on undervoltage threshold  $V_{BS\_thON}$ , as already stated in *Equation 12*. For a normal operation, the voltage across the bootstrap capacitor must never drop down to the turn-off undervoltage threshold  $V_{BS\_thOFF}$  throughout the working conditions. For the period of startup, only the low side IGBT is switched on and, just after this phase, the PWM is run, as shown in the following steps of *Figure 25*:

- t1: the bootstrap capacitor starts to charge through the low side IGBT (LVG)

- t2: the voltage across the bootstrap capacitor ( $V_{CBOOT}$ ) reaches its turn-on undervoltage threshold  $V_{BS\ thON}$ .

- t3: the bootstrap capacitor is fully charged, this enables the high side IGBT and the C<sub>BOOT</sub> capacitor starts to discharge in order to provide the right IGBT gate charge. The bootstrap capacitor recharges during the on state of low side IGBT (LVG).

Figure 25. Initial bootstrap charging time

The initial charging time is given by *Equation 15* and must be, for safety reasons, at least three times longer than the calculated value.

#### **Equation 15**

$$t_{CHARGE} \ge \frac{C_{BOOT} \cdot R_{DS(on)}}{\delta} * In \left(\frac{V_{CC}}{\Delta V_{CBOOT}}\right)$$

where  $\delta$  is the duty cycle of the PWM signal and R<sub>DS(on)</sub> is 120  $\Omega$  typical value, as shown in the datasheet.

A practical example can be done by considering a motor drive application where the PWM switching frequency is 12.5 kHz, with a duty cycle of 50%, and  $\Delta V_{CBOOT} = 0.1 \text{ V}$  (that means, a gate driver supply voltage  $V_{CC} = 17.6 \text{ V}$ ). From the graph in *Figure 24* the bootstrap capacitance is 1.5  $\mu\text{F}$ , therefore, the  $C_{BOOT}$  can be selected by using a value between 3.0 and 4.5  $\mu\text{F}$ . According to the commercial value the bootstrap capacitor can be 3.3  $\mu\text{F}$ . From *Equation 15*, the initial charging time is:

#### **Equation 16**

$$t_{CHARGE} \ge \frac{3.3 \cdot 10^{-6} \cdot 120}{0.5} \cdot ln \left(\frac{17.6}{0.1}\right) = 4ms$$

For safety reasons, the initial charging time must be at least 12 ms.

57/

## 3 Package

The SLLIMM benefits from a compact package while providing high power density, the best thermal performance, and great electrical isolation (> 2500 V<sub>RMS</sub>).

The SDIP is a dual-in-line transfer mold package, available in 25-lead version (SDIP-25L) and 38-lead version (SDIP-38L) and based on the state of the art DBC mounting technology for the power stage, whilst the control stage is assembled on a PCB layer. A vacuum soldering process is used to avoid any gas inclusion (voids) during the soldering process that could cause potential hot spots. It results in a further increase in the reliability of the SLLIMM family due to the improved thermal and electrical conductivity.

This technology makes it possible to achieve extremely low thermal resistance values, high stability in thermal cycling, small size with optimum cost-effectiveness, and quality level.

### 3.1 DBC substrate

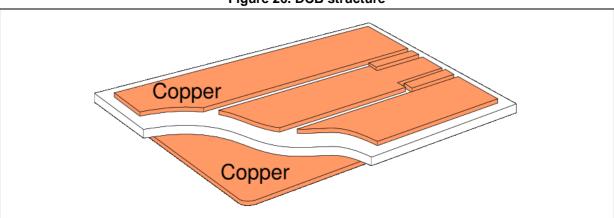

DBC means direct bonded copper and denotes a process in which copper and a ceramic material are directly bonded, as shown in *Figure 26*. Direct bonded copper substrates have been proven for many years to be an excellent solution for electrical isolation and thermal management of high power semiconductor modules.

Figure 26. DCB structure

The advantages of DBC substrates are, firstly, high current-carrying capability, due to thick copper metallization, and secondly, a thermal expansion coefficient close to the silicon one at the copper surface.

DBC has two layers of copper that are directly bonded onto an aluminum-oxide ( $Al_2O_3$ ) ceramic base. The DBC process yields a super-thin base and eliminates the need for thick, heavy copper bases that were used prior to this process. Because SLLIMM with DBC bases has fewer layers, it has much lower thermal resistance values than those based on different materials.

### The main properties of DBC ceramic substrates

The main properties of DBC include good mechanical strength, mechanically stable shape, good adhesion and corrosion resistance, and also offer:

- Excellent electrical isolation

- Very good thermal conductivity

- The thermal expansion coefficient is close to that of silicon, so no interface layers are required

- Good heat spreading

- May be structured just like printed circuit boards or "IMS substrates"

- Environmentally clean

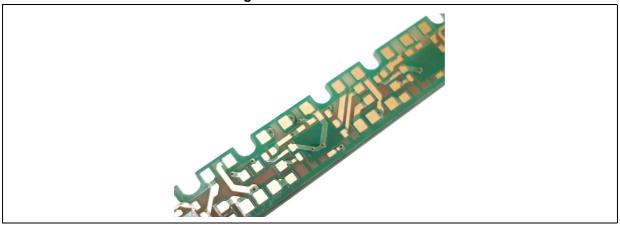

### 3.2 PCB

A PCB (printed circuit board) is used to mechanically support the gate driver ICs and to electrically connect those using conductive pathways.

Thanks to the internal PCB it is possible to realize various electric configurations, necessary to add advanced features, and to insert several passive components, such as resistors or capacitors, to properly bias the gate drivers. The insertion of filter capacitors, directly across the gate driver pins, improves the SLLIMM noise immunity and helps users to work in a safer condition. *Figure 27* shows the internal PCB detail.

Figure 27. PCB structure

## 3.3 Package structure

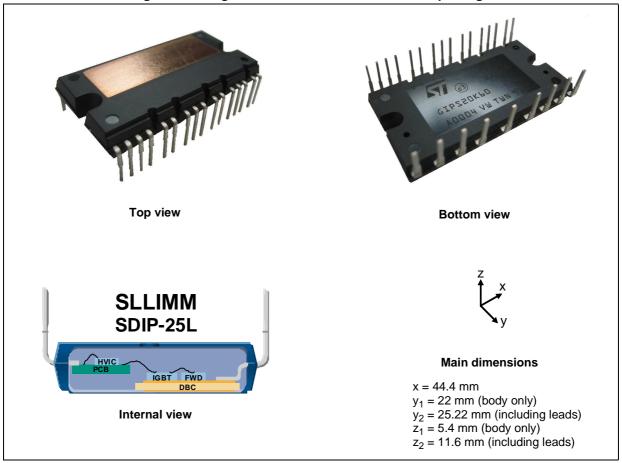

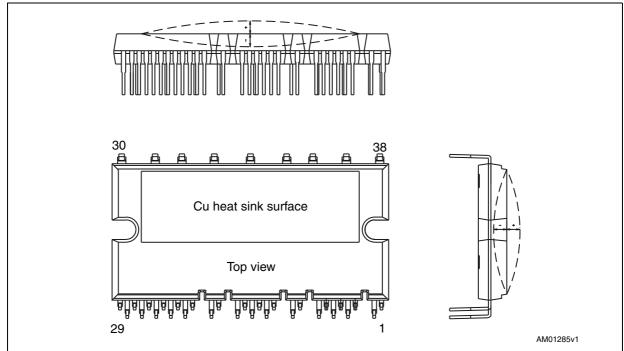

Figure 28 and Figure 29 contain images and an internal structure illustration of the SDIP-25L and SDIP-38L package.

577

Figure 28. Images and internal view of SDIP-25L package

Top view

Bottom view

SLLIMM

SDIP-38L

Main dimensions

x = 49.6 mm

y<sub>1</sub> = 24.5 mm (body only)

y<sub>2</sub> = 29.1 mm (including leads)

z<sub>1</sub> = 5.4 mm (body only)

z<sub>2</sub> = 10.91 mm (including leads)

Figure 29. Images and internal view of SDIP-38L package

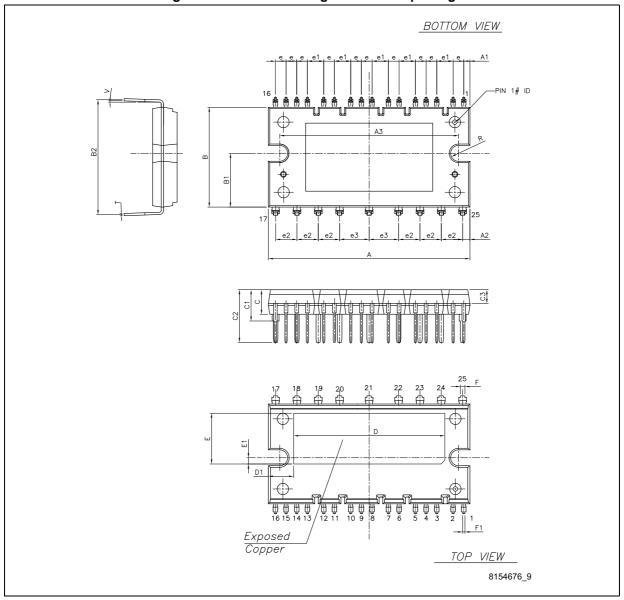

## 3.4 Package outline and dimensions

Figure 30. Outline drawing of SDIP-25L package

Table 9. SDIP-25L mechanical data

| Dim. | mm    |       |       |  |  |  |

|------|-------|-------|-------|--|--|--|

| Dim. | Min.  | Тур.  | Max.  |  |  |  |

| А    | 43.90 | 44.40 | 44.90 |  |  |  |

| A1   | 1.15  | 1.35  | 1.55  |  |  |  |

| A2   | 1.40  | 1.60  | 1.80  |  |  |  |

| А3   | 38.90 | 39.40 | 39.90 |  |  |  |

| В    | 21.50 | 22.00 | 22.50 |  |  |  |

| B1   | 11.25 | 11.85 | 12.45 |  |  |  |

| B2   | 24.83 | 25.23 | 25.63 |  |  |  |

| С    | 5.00  | 5.40  | 6.00  |  |  |  |

| C1   | 6.50  | 7.00  | 7.50  |  |  |  |

| C2   | 11.20 | 11.70 | 12.20 |  |  |  |

| C3   | 2.90  | 3.00  | 3.10  |  |  |  |

| е    | 2.15  | 2.35  | 2.55  |  |  |  |

| e1   | 3.40  | 3.60  | 3.80  |  |  |  |

| e2   | 4.50  | 4.70  | 4.90  |  |  |  |

| e3   | 6.30  | 6.50  | 6.70  |  |  |  |

| D    |       | 33.30 |       |  |  |  |

| D1   |       | 5.55  |       |  |  |  |

| Е    |       | 11.20 |       |  |  |  |

| E1   |       | 1.40  |       |  |  |  |

| F    | 0.85  | 1.00  | 1.15  |  |  |  |

| F1   | 0.35  | 0.50  | 0.65  |  |  |  |

| R    | 1.55  | 1.75  | 1.95  |  |  |  |

| Т    | 0.45  | 0.55  | 0.65  |  |  |  |

| V    | 0°    |       | 6°    |  |  |  |

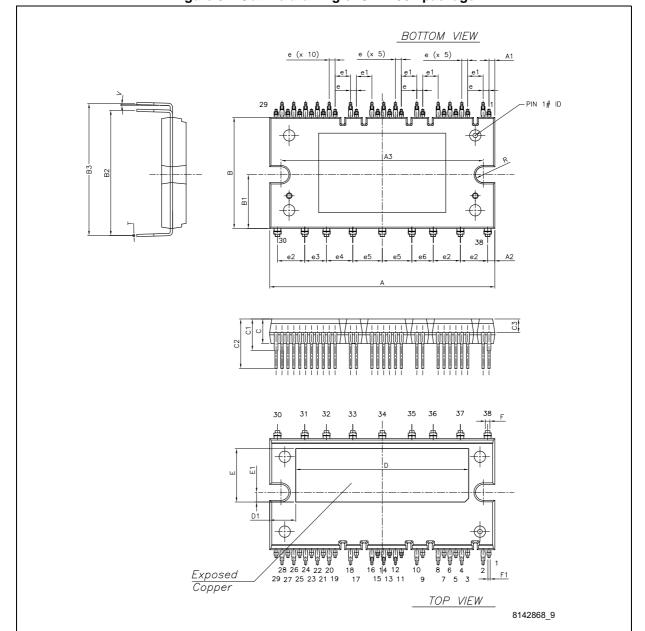

Figure 31. Outline drawing of SDIP-38L package

Table 10. SDIP-38L mechanical data

| mm    |                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Min.  | Тур.                                                                                                                       | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 49.10 | 49.60                                                                                                                      | 50.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 1.10  | 1.30                                                                                                                       | 1.50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 1.40  | 1.60                                                                                                                       | 1.80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

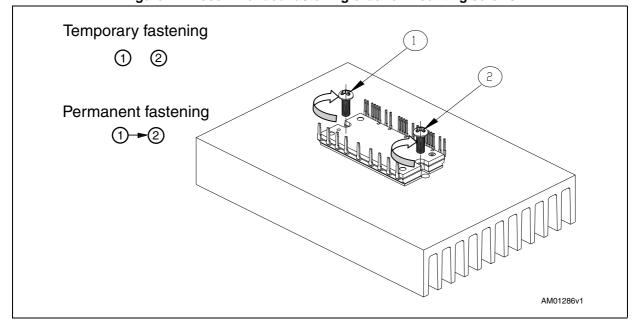

| 44.10 | 44.60                                                                                                                      | 45.10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |