# Use STM32F3/STM32G4 CCM SRAM with IAR Embedded Workbench®, Keil® MDK-ARM, STMicroelectronics STM32CubeIDE, and other GNU-based toolchains

#### Introduction

This document gives a presentation of the core-coupled memory (CCM) SRAM available on STM32F3/STM32G4 microcontrollers and describes what is required to execute part of the application code from this memory region using different toolchains.

The first section provides an overview of the CCM SRAM, while the next sections describe the steps required to execute part of the application code from CCM SRAM using the following toolchains:

- IAR Systems<sup>®</sup> IAR Embedded Workbench<sup>®</sup>

- Keil<sup>®</sup> MDK-ARM

- STMicroelectronics STM32CubeIDE and other GNU-based toolchains

The procedures described throughout the document are applicable to other SRAM regions such as the CCM data RAM of some STM32F4 devices, or external SRAM.

Table 1 lists the STM32 microcontrollers used as examples for CCM SRAM.

**Table 1. Applicable products**

| Refer           | ence    | Products                              |

|-----------------|---------|---------------------------------------|

| STM32F3/STM32G4 | STM32F3 | STM32F303 line, STM32F334 line        |

|                 |         | STM32F328C8                           |

|                 |         | STM32F358CC, STM32F358RC, STM32F358VC |

|                 |         | STM32F398VE                           |

|                 | STM32G4 | STM32G4 Series                        |

#### 1 Overview of STM32F3/STM32G4 CCM SRAM

This document applies to STM32F3/STM32G4 microcontrollers based on the Arm® Cortex®-M core.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

#### 1.1 Purpose

The CCM SRAM is tightly coupled with the Arm<sup>®</sup> Cortex<sup>®</sup> core, to execute the code at the maximum system clock frequency without any wait-state penalty. This also brings a significant decrease of the critical task execution time, compared to code execution from flash memory.

The CCM SRAM is typically used for real-time and computation intensive routines, like the following:

- Digital power conversion control loops (switch-mode power supplies, lighting)

- Field-oriented 3-phase motor control

- Real-time DSP (digital signal processing) tasks

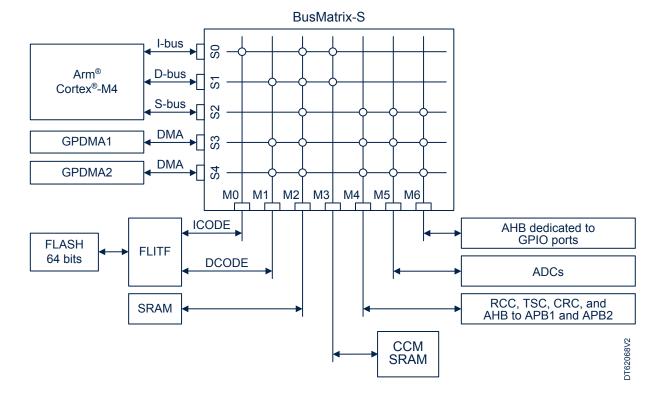

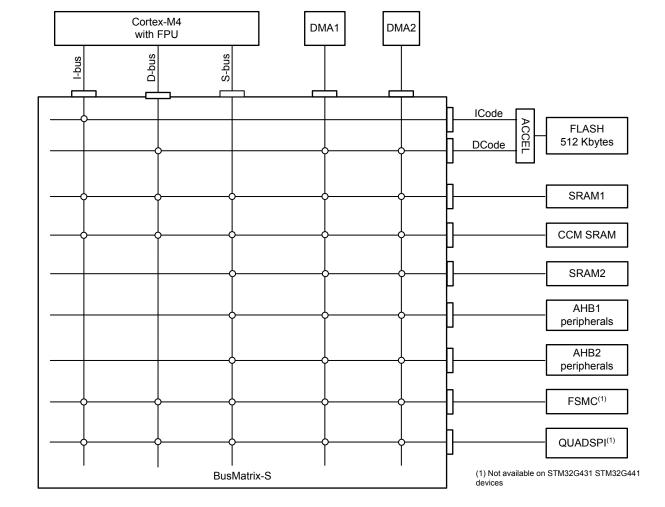

When the code is located in CCM SRAM and data stored in the regular SRAM, the Cortex<sup>®</sup>-M4 core is in the optimum Harvard configuration. A dedicated zero-wait-state memory is connected to each of its I-bus and D-bus (see the figures below) and can thus perform at 1.25 DMIPS/MHz, with a deterministic performance of 90 DMIPS in STM32F3 and 213 DMIPS in STM32G4. This also guarantees a minimal latency if the interrupt service routines are placed in the CCM SRAM.

Figure 1. STM32F3 device system architecture

AN4296 - Rev 6 page 2/23

Figure 2. STM32G4 device system architecture

#### Example

A benchmark between the STM32F103 and STM32F303 microcontrollers using the STMicroelectronics MC library V3.4 shows that, in case of single motor control using three-shunt algorithm, the field-oriented control (FOC) total execution time for STM32F303 is 16.97 µs compared to 21.3 µs for the STM32F103 (see the note below), with FOC core and sensorless core loops running from CCM SRAM for STM32F303. This means that the STM32F303 is 20.33% faster than the STM32F103 thanks to the CCM SRAM.

Note:

FOC routines are programmed in structured C, so the values provided above do not represent the fastest possible execution for both STM32F103 and STM32F303. In addition, the execution time is also a function of the compiler used and of its version.

When the CCM SRAM is not used for code, it can hold data like an extra SRAM memory. It is not recommended to place both code and data together in the CCM, since the Cortex® core must then fetch code and data from the same memory with the risk of collisions. The core is then in the Von Neumann configuration and its performance drops from 1.25 DMIPS/MHz to below 1 DMIPS/MHz.

AN4296 - Rev 6 page 3/23

0x2000 5800

#### 1.2 CCM SRAM features

The table below summarizes the CCM SRAM features on various STM32 products. More details are provided in the next sections.

STM32F303x6/8 STM32F303xB/C STM32F303xD/F STM32G47xx STM32G431x Feature/ STM32F334xx products STM32F358xx STM32F398xx STM32G48xx STM32G441x STM32F328xx Size (Kbytes) 8 16 32 10 0x1000 0000 and can be 0x1000 0000 and can be 0x1000 0000 Mapping aliased at 0x2001 8000 aliased at 0x2000 5800 Parity check Write protection Yes, with 1-Kbyte page granularity Read protection Nο Yes Erase No Yes No if mapped at No if mapped at 0x1000 0000 0x1000 0000 DMA access No Yes if mapped at Yes if mapped at

Table 2. CCM SRAM main features

#### 1.2.1 CCM SRAM mapping

The CCM SRAM is mapped at address 0x1000 0000.

On the STM32G4 devices, the CCM SRAM is aliased at the address following the end of SRAM2 offering a continuous address space with the SRAM1 and SRAM2.

0x2001 8000

#### 1.2.2 CCM SRAM remapping

Unlike regular SRAM, the CCM SRAM cannot be remapped at address 0x0000 0000.

#### 1.2.3 CCM SRAM write protection

The CCM SRAM can be protected against unwanted write operations with a page granularity of 1 Kbyte.

The write protection is enabled through the SYSCFG CCM SRAM protection register. This is a write-1-once mechanism: once the write protection is enabled on a given CCM SRAM page by programming the corresponding bit to 1, it can be cleared only through a system reset. For more details refer to the product reference manual.

#### 1.2.4 CCM SRAM parity check

The implemented parity check is disabled by default and can be enabled by the user when needed through an option bit (SRAM\_PE bit). When this option bit is cleared, the parity check is enabled.

#### 1.2.5 CCM SRAM read protection (only on STM32G4 devices)

The CCM SRAM can also be readout-protected via the RDP option byte. When protected, the CCM SRAM cannot be read or written by the JTAG or serial-wire debug port, and when the boot in the system flash memory or the boot in the SRAM is selected.

The CCM SRAM is erased when the readout protection is changed from Level 1 to Level 0.

#### 1.2.6 CCM SRAM erase (only on STM32G4 devices)

The CCM SRAM can be erased by software by setting the CCMER bit in the CCM SRAM system configuration control and status register.

The CCM SRAM can also be erased with the system reset depending on the option bit CCMSRAM\_RST in the user option bytes.

AN4296 - Rev 6 page 4/23

# Execute application code from CCM SRAM using the IAR Systems<sup>®</sup> IAR Embedded Workbench<sup>®</sup> toolchain

#### 2.1 Execute a simple code from CCM SRAM (except for interrupt handler)

A simple code can be composed of one or more functions that are not referenced from an interrupt handler. If the code is referenced from an interrupt handler, follow the steps described in Section 2.2.

IAR Embedded Workbench<sup>®</sup> provides the possibility to place one or more functions or a whole source file in CCM SRAM. This operation requires a new section to be defined in the linker file (.icf) to host the code to be placed in CCM SRAM. This section is copied to CCM SRAM at startup. The required steps are listed below:

- 1. Define the address area for the CCM SRAM by indicating the start and end addresses.

- 2. Tell the linker to copy at startup the section named .ccmram from the flash memory to the CCM SRAM.

- 3. Indicate to the linker that the code section .ccmram must be placed in the CCM SRAM region.

The figure below shows an example of code implementing these operations.

Figure 3. IAR Embedded Workbench® linker update

```

/*###ICF### Section handled by ICF editor, don't touch! ****/

/*-Editor annotation file-*/

/* IcfEditorFile="$TOOLKIT_DIR$\config\ide\IcfEditor\cortex_v1_0.xml" */

/*-Specials-*/

define symbol __ICFEDIT_intvec_start__ = 0x08000000;

/*-Memory Regions-*/

/*-Memory Regions-*/

define symbol __ICFEDIT_region_ROM_start __ = 0x08000000;

define symbol __ICFEDIT_region_ROM_end __ = 0x0803FFFF;

define symbol __ICFEDIT_region_RAM_start __ = 0x20000000;

define symbol __ICFEDIT_region_RAM_end __ = 0x20009FFFF;

/*-Sizes-*/

define symbol __ICFEDIT_size_cstack__ = 0x400;

define symbol __ICFEDIT_size_heap__ = 0x200;

define symbol __ICFEDIT_size_heap_ = 0x20

/**** End of ICF editor section. ###ICF###*/

define memory mem with size = 4G;

Defines the address zone for

define region CCMRAM_region = mem:[from 0x10000000 to 0x10001FFF];

CCM SRAM.

define block CSTACK

with alignment = 8, size =

with alignment = 8, size = __ICFEDIT_size_cstack__

with alignment = 8, size = __ICFEDIT_size_heap__

define block HEAP

'Initialize by copy ' tells the linker to copy

initialize by copy { readwrite, section .ccmram };

this section at startup time.

do not initialize { section .noinit };

place at address mem:__ICFEDIT_intvec_start__ { readonly section .intvec };

place in ROM region { readonly };

Places .ccmram section at CCM SRAM

place in CCMRAM region {section .ccmram};

defined above.

place in RAM region { readwrite,

block CSTACK, block HEAP };

```

Note: This procedure is not valid for interrupt handlers.

#### 2.1.1 Execute a source file from CCM SRAM

Execute a source file from CCM SRAM means that all functions declared in this file are executed from this memory area.

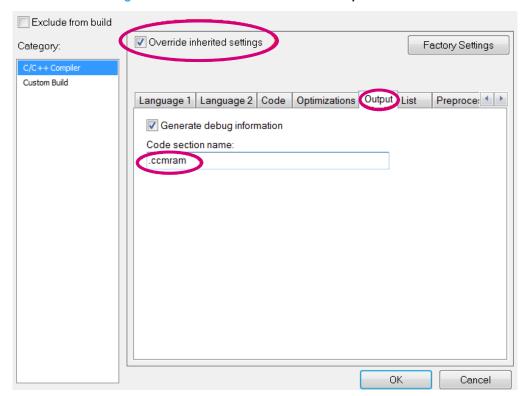

To place and execute a source file from CCM SRAM, use the IAR Embedded Workbench® file *Options* window as follows:

- 1. Add the section .ccmram (for example) in the linker file as defined in Section 2.1.

- 2. Right click on the file name from the workspace window.

- 3. Select [Options] from the displayed menu.

- 4. Check [Override inherited settings] from the displayed window.

AN4296 - Rev 6 page 5/23

5. Select the *Output* tab and type the name of the section already defined in the linker file (.ccmram in this example) in the [**Code section name**] field (see the figure below).

Figure 4. IAR Embedded Workbench® file placement

#### 2.1.2 Executing one or more functions from CCM SRAM

The steps required to execute a function from CCM SRAM are the following:

- 1. Add the section .ccmram in the linker file as described in Section 2.1.

- Using keyword pragma location, specify the function to be executed from CCM SRAM (see the figure below).

Figure 5. IAR Embedded Workbench® function placement

```

/**

* @brief Inserts a delay time.

* @param nTime: specifies the delay time length, in milliseconds.

* @retval None

*/

*pragma location = ".ccmram"

Pragma key word to precise the function placement

void Delay(_IO uint32_t nTime)

{

TimingDelay = nTime;

while(TimingDelay != 0);

}

```

Note:

To execute more than one function from CCM SRAM, the pragma location keyword must be placed above each function declaration.

AN4296 - Rev 6 page 6/23

#### 2.2 Execute an interrupt handler from CCM SRAM

The vector table is implemented as an array named \_\_vector\_table and referenced in the startup code.

The IAR Embedded Workbench® linker protects the sections that are referenced from the startup code from being affected by an 'initialize by copy' directive. The symbol \_\_vector\_table must not be used to allow copying interrupt handler sections via the 'initialize by copy' directive. A second vector table must be created and placed in CCM SRAM.

The steps required to execute an interrupt handler from CCM SRAM are listed below and described in the next sub-sections:

- 1. Update the linker file (.icf).

- 2. Update the startup file.

- 3. Place the interrupt handler in CCM SRAM.

- 4. Remap the vector table to CCM SRAM.

#### 2.2.1 Updating the linker file (.icf)

The following steps are needed to update the linker file .icf (see the figure below):

- 1. Define the address where the second vector table is located: 0x1000 0000.

- 2. Define the memory address area for the CCM SRAM by specifying the start and end addresses.

- 3. Tell the linker to copy at startup the section named .ccmram and the second vector table section .intvec\_CCMRAM from flash memory to CCM SRAM.

- 4. Tell the linker that the second vector table must be placed in the .intvec CCMRAM section.

- 5. Indicate that the .ccmram code section must be placed in CCM SRAM.

Figure 6. IAR Embedded Workbench® linker update for interrupt handler

```

/*###ICF### Section handled by ICF editor, don't touch! ****/

/*-Editor annotation file-*

/* IcfEditorFile="$TOOLKIT_DIR$\config\ide\IcfEditor\cortex_v1_0.xml" */

/*-Specials-*/

define symbol __ICFEDIT_intvec_start__ = 0x080000000;

/*-Memory Regions-*/

define symbol __ICFEDIT_region_RAM_end__

/*-Sizes-*/

define symbol __ICFEDIT_size_cstack__ = 0x1000;

define symbol __ICFEDIT_size_heap__ = 0x0000;

/**** End of ICF editor section. ###ICF###*/

define symbol CCMRAM_intvec_start = 0x10000000;

define memory mem with size = 4G;

define region ROM_region = mem:[from _ICFEDIT_region_ROM_start_ to _ICFEDIT_region_ROM_end_];

define region RAM region = mem:[from _ICFEDIT_region_RAM_end_];

define region CCMRAM_region

= mem: [from 0x10000000 to 0x10001FFF]

define block CSTACK with alignment = 8, size = __ICFEDIT_size_cstack_

define block HEAP with alignment = 8, size = __ICFEDIT_size_heap

define block HEAP

3 initialize by copy { readwrite, section .intvec_CCMRAM, section .ccmram, ro object stm32f30_it.o };

do not initialize { section .noinit };

place at address mem; ICFEDIT intvec start { readonly section .intvec };

4 place at address mem: CCMRAM_intvec_start { section .intvec_CCMRAM };

place in CCMRAM_region { section .ccmram };

place in ROM_region { readonly };

place in RAM_region

block CSTACK, block HEAP 1:

```

AN4296 - Rev 6 page 7/23

#### 2.2.2 Updating the startup file

The following steps are needed to update the startup file:

- 1. Make a second vector table to be stored in CCM SRAM. For example, the <code>startup\_stm32f30x.s</code> file must be modified by removing all entries except <code>sfe(CSTACK)</code> and <code>Reset\_Handler</code> from the original vector table <code>\_\_vector\_table</code>.

- 2. Add a second vector table to be placed in CCM SRAM. It must contain all entries. As an example this table can be called \_\_vector\_table\_CCMRAM. This vector table must be placed in the .intvec\_CCMRAM section defined in the linker file.

Figure 7. IAR Embedded Workbench® startup file update for interrupt handler

```

;; Forward declaration of sections.

SECTION CSTACK: DATA: NOROOT (3)

SECTION .intvec:CODE:NOROOT(2)

EXTERN

__iar_program_start

EXTERN SystemInit

PUBLIC __vector_table

DATA

_vector_table

DCD

sfe(CSTACK)

DCD

Reset Handler

; Reset Handler

SECTION .intvec_CCMRAM:CODE:ROOT(2)

PUBLIC __vector_table_CCMRAM

DATA

_vector_table_CCMRAM

sfe(CSTACK)

DCD

DCD

Reset_Handler

; Reset Handler

DCD

NMI_Handler

; NMI Handler

DCD

HardFault_Handler

; Hard Fault Handler

DCD

MemManage_Handler

; MPU Fault Handler

DCD

BusFault Handler

; Bus Fault Handler

UsageFault_Handler

DCD

; Usage Fault Handler

DCD

0

: Reserved

```

#### 2.2.3 Place the interrupt handler in CCM SRAM

Place the interrupt handler to be executed in CCM SRAM as described in Executing one or more functions from CCM SRAM or the whole stm32f it.c file as described in Execute a source file from CCM SRAM.

; Reserved

; Reserved

#### 2.2.4 Remap the vector table to CCM SRAM

In the SystemInit function, remap the vector table to CCM SRAM by modifying the VTOR register as follows:

```

SCB->VTOR = 0x10000000 | VECT_TAB_OFFSET;

```

DCD

DCD

0

AN4296 - Rev 6 page 8/23

#### 2.3 Execute a library (.a) from CCM SRAM

IAR Embedded Workbench® allows the execution of a library or a library module from CCM SRAM. The required steps are listed below:

1. Define the memory address area corresponding to the CCM SRAM by specifying the start and end addresses.

#### Figure 8. CCM SRAM area definition

```

define memory mem with size = 4G;

define region ROM_region = mem:[from _ICFEDIT_region_ROM_start__ to _ICFEDIT_region_ROM_end_];

define region RAM_region = mem:[from _ICFEDIT_region_RAM_start_ to _ICFEDIT_region_RAM_end_];

define region CCMRAM_region = mem:[from 0x10000000 to 0x10001FFF];

Defines the address zone for CCM SRAM.

define block CSTACK with alignment = 8, size = _ICFEDIT_size_cstack_ { };

define block HEAP with alignment = 8, size = _ICFEDIT_size_heap_ { };

```

2. Update the linker to copy at startup the library or the library module in CCM SRAM using the 'initialize by copy' directive.

#### Figure 9. IAR Embedded Workbench® section initialization

```

initialize by copy { readwrite,ro object iar_cortexM41f_math.a };

do not initialize { section .noinit };

```

3. Indicate to the linker that the library must be placed in CCM SRAM.

#### Figure 10. IAR Embedded Workbench® library placement

```

place in ROM_region { readonly };

place in CCMRAM_region { section .text object iar_cortexM4lf_math.a};

```

To execute a library module from CCM SRAM, follow steps 1, 2 and 3 using the library module name.

AN4296 - Rev 6 page 9/23

The example in the figure below shows how to place <code>arm\_abs\_f32.o</code> (a module of <code>iar\_cortexM4l\_math.a</code> library) in CCM SRAM.

#### Figure 11. IAR Embedded Workbench® library module placement

```

/*###ICF### Section handled by ICF editor, don't touch! ****/

/*-Editor annotation file-*,

/* IcfEditorFile="$T00LKIT_DIR$\config\ide\IcfEditor\cortex_v1_0.xml" */

/*-Specials-*/

define symbol

_ICFEDIT_intvec_start__ = 0x08000000;

/*-Memory Regions-*/

define symbol _ICFEDIT_region_ROM_start _ = 0x08000000;

define symbol _ICFEDIT_region_ROM_end _ = 0x0803FFFF;

define symbol _ICFEDIT_region_RAM_start = 0x20000000;

define symbol _ICFEDIT_region_RAM_end _ = 0x20009FFF;

/*-Sizes-*/

define symbol __ICFEDIT_size_cstack__ = 0x400;

define symbol __ICFEDIT_size_heap__ = 0x200;

/**** End of ICF editor section. ###ICF###*/

define memory mem with size = 4G;

define region ROM_region = mem:[from _ICFEDIT_region_ROM_start_ to _ICFEDIT_region_ROM_end_];

define region RAM_region = mem:[from _ICFEDIT_region_RAM_start_ to _ICFEDIT_region_RAM_end_];

define region CCMRAM_region = mem:[from 0x10000000 to 0x10001FFF];

with alignment = 8, size = __ICFEDIT_size_cstack_

with alignment = 8, size = ICFEDIT size heap

define block CSTACK

define block HEAP

initialize by copy { readwrite, ro object arm_abs_f32.0 };

do not initialize { section .noinit };

place at address mem:__ICFEDIT_intvec_start__ { readonly section .intvec };

place in ROM region _ { readonly };

place in CCMRAM region {section .text object arm abs f32.0 };

place in RAM_region { readwrite,

block CSTACK, block HEAP };

```

AN4296 - Rev 6 page 10/23

# Execute application code from CCM SRAM using the Keil<sup>®</sup> MDK-ARM toolchain

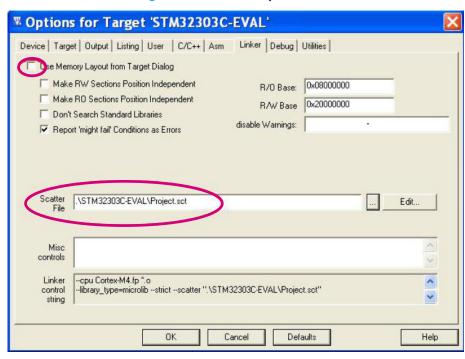

MDK-ARM features make it possible to execute simple functions or interrupt handlers from CCM SRAM. The following sections explain how to use these features to execute code from CCM SRAM.

#### 3.1 Execute a function or an interrupt handler from CCM SRAM

The steps required to execute a function or an interrupt handler from CCM SRAM are listed below:

- 1. Define a new region (comram) in the scatter file by indicating the start and end addresses of CCM SRAM.

- 2. Indicate to the linker that the sections with the comram attribute must be placed in the CCM SRAM region.

Figure 12. MDK-ARM scatter file

```

Project.sct system_stm32f30x.c

main.c

stm32f30x_it.c

startup_stm32f30x.s

: **********************

: *** Scatter-Loading Description File generated by uVision ***

3

4

LR_IROM1 0x08000000 0x00040000 {

; load region size_region

6

ER IROM1 0x08000000 0x00040000 { ; load address = execution address

7

*.o (RESET, +First)

8

*(InRoot$$Sections)

9

.ANY (+RO)

10

RW IRAM1 0x20000000 0x00000A000 { ; RW data

11

12

.ANY (+RW +ZI)

Defines CCM SRAM as

13

execution region

RW IRAM2 0x10002000 0x00001000 {

14

15

.ANY (+RW +ZI)

16

17

ER 0x10000000 0x00002000 { ; load address = execution address

18 1

15

20 2

.ANY (ccmram)

- Places code in ccmram section.

21

22

```

AN4296 - Rev 6 page 11/23

3. Refer to the modified scatter file for the project options.

4. Place the part of code to be executed from CCM SRAM in the comman section defined above. This is done by adding the attribute key word above the function declaration.

Figure 14. MDK-ARM function placement

```

#*

* @brief This function handles SysTick Handler.

* @param None

* @retval None

*/

attribute__((section ("ccmram"))

void SysTick_Handler(void)

{

TimingDelay_Decrement();

}

```

Note: To execute more than one function from CCM SRAM, the attribute keyword must be placed above each function declaration.

AN4296 - Rev 6 page 12/23

#### 3.2 Execute a source file from CCM SRAM

Executing a source file from CCM SRAM means that all functions declared in this file are executed from the CCM SRAM region.

Follow the steps below to execute a file from CCM SRAM:

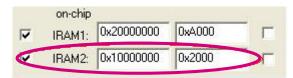

1. Define the CCM SRAM as a memory area in the project option window ([Project]>[option]>[target]).

Figure 15. MDK-ARM target memory

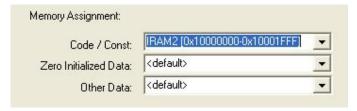

- 2. Right click on the file to place it in CCM SRAM and select [Options].

- 3. Select the CCM SRAM region in the [Memory assignment] menu.

Figure 16. MDK-ARM file placement

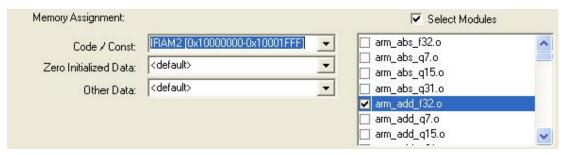

#### 3.3 Execute a library or a library module from CCM SRAM

Follow the steps below to execute a library or a library module from CCM SRAM:

- 1. Define CCM SRAM as a memory area as shown in the figure below.

- 2. Right click on the library from the workspace and select [Options].

- 3. Place the complete library or a module from a library in CCM SRAM.

Figure 17. MDK-ARM library placement

AN4296 - Rev 6 page 13/23

# Execute application code from CCM SRAM using STM32CubeIDE with GNU-based toolchain

STM32CubeIDE and GNU-based toolchains allow executing simple functions or interrupt handlers from CCM SRAM. The following sections explain how to use these features to execute code from CCM SRAM.

#### 4.1 Execute a function or an interrupt handler from CCM SRAM

The steps required to execute a function or an interrupt handler from CCM SRAM are listed below:

1. Define a new region (ccmram) in the linker file (.ld) by defining the start address and the size of the CCM SRAM region.

```

/* Entry Point */

ENTRY(Reset_Handler)

/* Highest address of the user mode stack */

_estack = ORIGIN(RAM) + LENGTH(RAM); /* end of "RAM" Ram type memory */

_Min_Heap_Size = 0x200; /* required amount of heap */

_Min_Stack_Size = 0x400; /* required amount of stack */

/* Memories definition */

MEMORY

{

RAM (xrw) : ORIGIN = 0x20000000, LENGTH = 112K

FLASH (rx) : ORIGIN = 0x8000000, LENGTH = 512K

CCMRAM (xrw) : ORIGIN = 0x10000000, LENGTH = 8K

}

```

AN4296 - Rev 6 page 14/23

2. Instruct the linker that code sections with the commam attribute must be placed in CCM SRAM. Insert the following code into the linker script. It is important to insert it before .text in the script.

```

/* The startup code into "FLASH" Rom type memory */

.isr_vector :

. = ALIGN(4);

KEEP(*(.isr_vector)) /* Startup code */

\cdot = ALIGN(4);

} >FLASH

/*--- New CCMRAM linker section definition ---*/

_siccmram = LOADADDR(.ccmram);

/* CCMRAM section */

.ccmram :

. = ALIGN(4);

sccmram = .;

/* define a global symbols at ccmram start */

*(.ccmram)

*(.ccmram*)

. = ALIGN(4);

/* define a global symbols at ccmram end */

_eccmram = .;

} >CCMRAM AT> FLASH

/*--- End of CCMRAM linker section definition ---*/

/* The program code and other data into "FLASH" Rom type memory */

. = ALIGN(4);

*(.text)

/* .text sections (code) */

/* .text* sections (code) */

*(.text*)

/* glue arm to thumb code */

*(.glue 7)

*(.glue 7t)

/* glue thumb to arm code */

*(.eh_frame)

KEEP (*(.init))

KEEP (*(.fini))

. = ALIGN(4);

etext = .;

/* define a global symbols at end of code */

} >FLASH

```

AN4296 - Rev 6 page 15/23

3. Modify the startup file to initialize data and code to place in CCM SRAM at startup time.

```

^{\prime \star} Copy the data segment initializers from flash to SRAM ^{\star \prime}

ldr r0, = \_sdata

ldr r1, = _edata

ldr r2, = sidata

movs r3, \frac{1}{40}

b LoopCopyDataInit

CopyDataInit:

ldr r4, [r2, r3]

str r4, [r0, r3]

adds r3, r3, #4

LoopCopyDataInit:

adds r4, r0, r3

cmp r4, r1

bcc CopyDataInit

/* Copy from flash to CCMRAM */

ldr r0, =_sccmram

ldr r1, =_eccmram

ldr r2, = siccmram

movs r3, #0

b LoopCopyCcmInit

CopyCcmInit:

ldr r4, [r2, r3]

str r4, [r0, r3]

adds r3, r3, #4

LoopCopyCcmInit:

adds r4, r0, r3

cmp r4, r1

bcc CopyCcmInit

/* End of copy to CCMRAM */

/* Zero fill the bss segment. */

ldr r2, =_sbss

ldr r4, =_ebss

movs r3, \frac{1}{4}0

b LoopFillZerobss

FillZerobss:

str r3, [r2]

adds r2, r2, #4

LoopFillZerobss:

cmp r2, r4

bcc FillZerobss

/* Call the clock system initialization function.*/

bl SystemInit

/* Call static constructors */

bl __libc_init_array

/* Call the application's entry point.*/

bl main

LoopForever:

b LoopForever

```

AN4296 - Rev 6 page 16/23

4. Place the part of code to be executed from CCM SRAM in the .ccmram section by adding the attribute key word in the function prototype.

```

void NMI_Handler(void);

void HardFault_Handler(void);

void MemManage_Handler(void);

void BusFault_Handler(void);

void UsageFault_Handler(void);

void SVC_Handler(void);

void DebugMon_Handler(void);

void PendSV_Handler(void);

void SysTick_Handler(void) __attribute__((section (".ccmram")));

```

AN4296 - Rev 6 page 17/23

#### 4.2 Execute a file from CCM SRAM

Executing a source file from CCM SRAM means that all functions declared in this file are executed from CCM SRAM.

To execute a file from CCM SRAM, follow the steps listed below:

- Add the .ccmram section in the linker file as defined in Execute a function or an interrupt handler from CCM SRAM.

- 2. Place the file in CCM SRAM as shown below. The startup file also needs to be updated to copy code from the flash memory to CCM SRAM as described in Execute a function or an interrupt handler from CCM SRAM. This example shows how to execute file myTestCCM.o from CCM SRAM:

#### 4.3 Execute a library from CCM SRAM

Follow the steps below to execute a library from CCM SRAM:

- Add the .ccmram section in the linker file as defined in Execute a function or an interrupt handler from CCM SRAM.

- 2. Place the library in CCM SRAM as shown below. The startup file also needs to be updated to copy code from the flash memory to CCM SRAM as described in Execute a function or an interrupt handler from CCM SRAM. This example shows how to execute library myLib.a from CCM SRAM:

AN4296 - Rev 6 page 18/23

### **Revision history**

**Table 3. Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23-Jul-2013 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 2        | Changed STM32F313xC into STM32F358xC.                                                                                                                                                                                                                                                                                                                                                                      |

| 25-Mar-2014 |          | Reworked Section 1: Overview of STM32F303xB/C and STM32F358xC CCM RAM.                                                                                                                                                                                                                                                                                                                                     |

|             |          | Added STM32F303x6/x8, STM32F328x8, STM32F334x4/x6/x8 in <i>Table 1: Applicable products.</i>                                                                                                                                                                                                                                                                                                               |

| 02-Sep-2014 | 3        | Updated step 2 in Section 2.1: Executing a simple code from CCM RAM (except for interrupt handler), step 3 in Section 2.2.1: Updating the linker file (.icf) and updated Figure 5: EWARM linker update for interrupt handler.                                                                                                                                                                              |

|             |          | Updated Figure 11: MDK-ARM scatter file.                                                                                                                                                                                                                                                                                                                                                                   |

| 16-Apr-2019 | 4        | Updated:  Title of the document  Introduction  CCM RAM replaced by CCM SRAM in the whole document  Figure 1. STM32F3 devices system architecture  Added:  Figure 2. STM32G4 devices system architecture  Table 2. CCM SRAM main features  Section 1.2.5 CCM SRAM read protection (only on STM32G4 devices)  Section 1.2.6 CCM SRAM erase (only on STM32G4 devices)  Removed Table 2. CCM RAM organization. |

| 08-Feb-2021 | 5        | Updated: Title of the document Section 4 description and code examples to authorize code execution in CCM SRAM when using a GNU-based toolchain such as STM32CubeIDE                                                                                                                                                                                                                                       |

| 16-Apr-2025 | 6        | Updated:  Device reference in Table 2. CCM SRAM main features  Figure 1. STM32F3 device system architecture  Removed STM32F328K8, STM32F328R8, STM32F398RE, and STM32F398ZE from Table 1. Applicable products.                                                                                                                                                                                             |

AN4296 - Rev 6 page 19/23

### **Contents**

| 1   | Ove   | rview o | f STM32F3/STM32G4 CCM SRAM                                                                            | 2  |

|-----|-------|---------|-------------------------------------------------------------------------------------------------------|----|

|     | 1.1   | Purpo   | se                                                                                                    | 2  |

|     | 1.2   | CCM :   | SRAM features                                                                                         | 4  |

|     |       | 1.2.1   | CCM SRAM mapping                                                                                      | 4  |

|     |       | 1.2.2   | CCM SRAM remapping                                                                                    | 4  |

|     |       | 1.2.3   | CCM SRAM write protection                                                                             | 4  |

|     |       | 1.2.4   | CCM SRAM parity check                                                                                 | 4  |

|     |       | 1.2.5   | CCM SRAM read protection (only on STM32G4 devices)                                                    | 4  |

|     |       | 1.2.6   | CCM SRAM erase (only on STM32G4 devices)                                                              | 4  |

| 2   |       |         | oplication code from CCM SRAM using the IAR Systems <sup>®</sup> IAR Workbench <sup>®</sup> toolchain | 5  |

|     | 2.1   | Execu   | ite a simple code from CCM SRAM (except for interrupt handler)                                        | 5  |

|     |       | 2.1.1   | Execute a source file from CCM SRAM                                                                   |    |

|     |       | 2.1.2   | Executing one or more functions from CCM SRAM                                                         | 6  |

|     | 2.2   | Execu   | ite an interrupt handler from CCM SRAM                                                                | 7  |

|     |       | 2.2.1   | Updating the linker file (.icf)                                                                       | 7  |

|     |       | 2.2.2   | Updating the startup file                                                                             | 8  |

|     |       | 2.2.3   | Place the interrupt handler in CCM SRAM                                                               | 8  |

|     |       | 2.2.4   | Remap the vector table to CCM SRAM                                                                    | 8  |

|     | 2.3   | Execu   | ite a library (.a) from CCM SRAM                                                                      | 9  |

| 3   | Exe   | cute ap | plication code from CCM SRAM using the Keil <sup>®</sup> MDK-ARM toolchain .                          | 11 |

|     | 3.1   | Execu   | ite a function or an interrupt handler from CCM SRAM                                                  | 11 |

|     | 3.2   | Execu   | Ite a source file from CCM SRAM                                                                       | 13 |

|     | 3.3   | Execu   | ite a library or a library module from CCM SRAM                                                       | 13 |

| 4   |       |         | pplication code from CCM SRAM using STM32CubeIDE with GNU-                                            |    |

|     | 4.1   | Execu   | ite a function or an interrupt handler from CCM SRAM                                                  | 14 |

|     | 4.2   | Execu   | ite a file from CCM SRAM                                                                              | 18 |

|     | 4.3   |         | ite a library from CCM SRAM                                                                           |    |

| Rev | ision |         | ·<br>/                                                                                                |    |

|     |       | •       |                                                                                                       |    |

|     |       | ures    |                                                                                                       | 22 |

### **List of tables**

| Table 1. | Applicable products       | •  |

|----------|---------------------------|----|

| Table 2. | CCM SRAM main features    | 4  |

| Table 3. | Document revision history | 19 |

AN4296 - Rev 6 page 21/23

## **List of figures**

| Figure 1.  | STM32F3 device system architecture                                | . 2 |

|------------|-------------------------------------------------------------------|-----|

| Figure 2.  | STM32G4 device system architecture                                | . 3 |

| Figure 3.  | IAR Embedded Workbench® linker update                             | . 5 |

| Figure 4.  | IAR Embedded Workbench® file placement                            | . 6 |

| Figure 5.  | IAR Embedded Workbench® function placement                        | . 6 |

| Figure 6.  | IAR Embedded Workbench® linker update for interrupt handler       | . 7 |

| Figure 7.  | IAR Embedded Workbench® startup file update for interrupt handler | . 8 |

| Figure 8.  | CCM SRAM area definition                                          | . 9 |

| Figure 9.  | IAR Embedded Workbench® section initialization                    | . 9 |

| Figure 10. | IAR Embedded Workbench® library placement                         | . 9 |

| Figure 11. | IAR Embedded Workbench® library module placement                  |     |

| Figure 12. | MDK-ARM scatter file                                              | 11  |

| Figure 13. | MDK-ARM Options menu.                                             |     |

| Figure 14. | MDK-ARM function placement                                        |     |

| Figure 15. | MDK-ARM target memory                                             |     |

| Figure 16. | MDK-ARM file placement                                            |     |

| Figure 17. | MDK-ARM library placement                                         | 13  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

AN4296 - Rev 6 page 23/23