# AN4344 Application note

# Software routine for safe usage the interrupt controller SPC57EM80x/SPC574K72x according to ISO26262

### Introduction

Aim of this document is to give some examples on implementing the needed software mechanisms to verify the integrity of the interrupt controller embedded in SPC57EM80x/SPC574K72x.

These safety mechanisms are listed in the Safety Manual and FMEDA of SPC57EM80x/SPC574K72x.

This document does not provide a list of all possible implementations of these safety mechanisms because the implementation of some of them is application dependent. The document helps the user to choose the methodology which better fits user's needs.

September 2013 DocID025067 Rev 2 1/28

AN4344

# **Contents**

Contents

| 1       | Overview |                                           |      |

|---------|----------|-------------------------------------------|------|

|         | 1.1      | Safety Mechanisms implemented by software |      |

|         | 1.2      | Use case example                          | 6    |

| 2       | Initia   | alization                                 | 8    |

|         | 2.1      | INTC_UNUSED_ILLEGAL                       | 8    |

| 3       | Run      | -time checks                              | . 10 |

|         | 3.1      | INT_CHECK_TRIGGER_SET                     | . 10 |

|         | 3.2      | ISR_CHECK_PRIORITY                        | 11   |

|         | 3.3      | ISR_CHECK_CORE                            | . 13 |

|         | 3.4      | ISR_CHECK_TRIGGER_CLEAR                   | . 15 |

|         | 3.5      | ISR_DOUBLE_ASSIGNMENT                     | . 17 |

|         | 3.6      | ISR_CHECK_EFFECT                          | . 21 |

| 4       | Sum      | nmary                                     | . 24 |

| Append  | dix A I  | Reference documents                       | . 25 |

| Append  | dix B    | Acronyms                                  | . 26 |

| Revisio | n histo  | NEV.                                      | 27   |

AN4344 List of figures

# List of figures

| Figure 1.  | Simplified working schema of the INTC                                                 | 4    |

|------------|---------------------------------------------------------------------------------------|------|

| Figure 2.  | Hardware resources and interrupts used by the safety function                         |      |

| Figure 3.  | Hardware resources and interrupt used by the safety function and its monitors         | 7    |

| Figure 4.  | Example of INTC_UNUSED_ILLEGAL implementation                                         | 9    |

| Figure 5.  | A bit flip in the INTC can cause a spurious interrupt request                         | 10   |

| Figure 6.  | INT_CHECK_TRIGGER_SET implementation schema                                           | 11   |

| Figure 7.  | Faulty INTC can request interrupt with wrong priority                                 | 11   |

| Figure 8.  | Core read the INTC.CPR register and compare it with the expected value                | 12   |

| Figure 9.  | INTC can request an interrupt to one or more cores                                    | 13   |

| Figure 10. | Due to a failure the ISR is serviced by the wrong core                                |      |

| Figure 11. | CoreO_ISR verifies it's executed on the exepected core by reading the processor ID (F | PIR) |

| _          |                                                                                       | 14   |

| Figure 12. | Interrupt status flag is set the by a peripheral and clear by the ISR                 | 16   |

| Figure 13. | Generic implementation of the ISR_DOUBLE_ASSIGNMENT mechanism                         | 18   |

| Figure 14. | Schema of the example of the implementation of ISR_DOUBLE_ASSIGNMENT                  | 19   |

| Figure 15. | Periodic interrupt can measure its period                                             | 22   |

Overview AN4344

### 1 Overview

SPC57EM80x/SPC574K72x is a multicore device which embeds a single instantiation of the Interrupt Controller (INTC).

The function of the INTC is to forward correctly and timely<sup>(a)</sup> interrupt events triggered by peripherals to the one or more cores.

peripheral event INTC interrupt core

The core executes the specific ISR associated with the event

Figure 1. Simplified working schema of the INTC

Interrupt controller is prone to different failure modes, for example:

- spurious interrupt

- lost interrupt

- interrupt serviced with wrong priority

- interrupt request forwarded to the wrong core

- interrupt latency higher than expected

- and so on

These failure modes can be detected by some software mechanisms. In case the software detects an unexpected situation a fault management routine shall be called. The reaction of this routine is application dependent and it's out of the scope of the document.

The above failure modes can be caused, for instance, by a permanent damage in the silicon substrate (hard error according to the ISO26262) or by a particle strike due to an electromagnetic wave (soft error according to the ISO26262) which causes a temporal change of the MCU state.

To guarantee an acceptable risk according to the ISO26262, some mechanisms must be introduced to detect, and then react, to these failure modes. These mechanisms can be implemented either by software or hardware.

The full list of the considered failure modes, the mechanisms to detect them and their estimated diagnostic coverage can be found in the SPC57EM80x/SPC574K72x FMEDA.

SPC57EM80x/SPC574K72x is not the first MCU which has been thought to meet the ISO26262 requirements. The SPC56EL60 is the first MCU developed by

57/

a. Timely means with the expected latency; correctly means with proper computation parameters as priority and location of the ISR.

AN4344 Overview

STMicroelectronics which has been certified to meet requirements providing "Systematic Integrity: ASIL D".

SPC56EL60 implements most of safety mechanisms for the INTC by hardware. It exploits the hardware redundancy to guarantee the integrity of the INTC. Two INTCs are embedded and, simplifying the real implementation, the output of the INTC\_0 is compared with the output of INTC\_1.

Such a solution still requires some software safety mechanisms to detect:

- spurious interrupt signaled to both INTCs for example due to a glitches on the line source of the interrupt, or

- lost interrupt due to an unwanted masking to both INTCs.

As drawback this hardware redundancy requires a larger silicon area and a higher consumption.

This solution has been optimized on SPC57EM80x/SPC574K72x which embeds a single INTC and bases the verification of the INTC integrity mainly on a software implementation.

In addition to the software mechanisms there is a hardware mechanism, i.e. LBIST, to detect latent failures affecting the INTC.

Solution showed in the document shall be considered not as mandatory, but recommended and taken as an example on the implementation of the safety mechanisms.

This document focuses on the detection of the occurrence of a failure. Since the best reaction is application dependent, it's out of the scope of this document.

In the described examples, each time a failure is detected the function *error\_handling\_ISR* is called. This function shall implement the error management.

# 1.1 Safety Mechanisms implemented by software

According to the Safety Manual (and then to the safety concept and FMEDA) the software mechanisms required to guarantee the integrity of the INTC are:

- INTC\_UNUSED\_ILLEGAL Unused interrupt vectors shall point, or jump, to an address which is illegal to execute, contains an illegal instruction, or in some other way causes detection of their execution;

- ISR\_CHECK\_TRIGGER\_SET The ISR will check that the triggering module actually shows a requested interrupt (for example, reading the interrupt request or status register in the peripheral);

- ISR\_CHECK\_PRIORITY The ISR shall check that it was called with the correct priority;

- ISR\_CHECK\_CORE The ISR checks that it is executed on the expected core using the relevant core register;

- ISR\_CHECK\_TRIGGER\_CLEAR Periodically check that interrupt flags in peripherals are cleared;

- ISR\_DOUBLE\_ASSIGNMENT Interrupts where a short latency is safety-relevant are

assigned to two (or more) cores and one of those cores checks (for example, using a

shared variable) that the other core actually executes the ISR within the expected

latency after the IRQ occurred;

- ISR\_CHECK\_EFFECT Periodically check for effects of lost interrupts (for example, buffer overflow or underflow).

Overview AN4344

These safety mechanisms shall run online while the safety application runs. Only exception is the INTC UNUSED ILLEGAL which is related the INTC initialization.

The user has the responsibility to choose the implementation which better fits his or her needs.

# 1.2 Use case example

To describe the software which shall be implemented, a use case example has been assumed. All described concepts can be reused for other use cases.

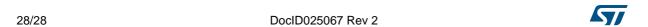

Let's assume 2 periodic interrupts are needed for functional purpose. These interrupts are serviced by the CORE0 and are implemented via 2 hardware interrupt sources, i.e. STM0 CH0 and STM0 CH1. A block schema of this simple example without any safety mechanism is shown on *Figure 2*.

STM0

—STM0 CH0

—STM0 CH1

—INTC

STM0 CH1

—STM0 CH1

—STM

Figure 2. Hardware resources and interrupts used by the safety function

For safety purpose

- these 2 interrupts are serviced also by the CORE2 which can be considered the monitor of the correct execution in terms of timing of the interrupt service routine executed by CORE0;

- an additional interrupt is implemented, i.e. PIT0\_CH0, to monitor the correct number of triggered functional interrupts;

- a free running timer, implemented by STM2, is used to check execution time of the interrupt service routine.

*Figure 3* shows a block scheme of the hardware resources and interrupts to implement the safety function and its monitors.

57/

AN4344 Overview

Figure 3. Hardware resources and interrupt used by the safety function and its monitors

Next sections give details and hints about the implementation of these software mechanisms.

Initialization AN4344

### 2 Initialization

This section describes mechanisms which must be applied during the initialization of the INTC, usually before the INTC is enabled.

Safety analysis assumes these mechanisms are applied before the safety application starts.

# 2.1 INTC\_UNUSED\_ILLEGAL

A faulty INTC can trigger unused ISRs. These ISR can have an impact on the safety function by executing an unexpected code.

To detect such a failure mode the INTC\_UNUSED\_ILLEGAL mechanism shall be implemented. Quoting the SM:

Unused interrupt vectors shall point, or jump, to an address which is illegal to execute, contains an illegal instruction, or in some other way causes detection of their execution.

To implement this mechanism all unused functions in the vector table shall not point to any unexpected location, but to a defined function, i.e. *dummy* in the *Example 1*.

#### Example 1: Unused interrupts point to a defined function

```

const uint32_t IntcIsrVectorTable[] = {

...

(unsigned int)&dummy, (unsigned int)&STM0_CH0_ISR, (unsigned int)&STM0_CH1_ISR, ... /* ISRs 35 - 39 */

...

}

```

If executed, this function shall trigger an alarm to the application. This alarm can be a core exception or other means.

In the *Example 2* a core exception is triggered by writing to an illegal address.

#### Example 2: Unused interrupts shall trigger an exception if executed

```

void dummy (void) {

tU32 *pointTest = 0x34567890;

*pointTest = 40;

}

```

This software mechanism is executed only in case of failure. Until the INTC works properly, the *dummy* function is never executed.

5/

AN4344 Initialization

Unused interrupt

Calls to unused interrupt

triggers a Core0 exception

Figure 4. Example of INTC\_UNUSED\_ILLEGAL implementation

# 3 Run-time checks

This section describes the software mechanisms to be executed in run-time, i.e. while the safety application runs. Most of these mechanisms are triggered either by the application which calls them periodically or by interrupts.

It is assumed that the INTC, and the whole device, has been "properly" configured before the safety application starts. "Properly" configured means accordingly to the functional and safety requirements.

### 3.1 INT\_CHECK\_TRIGGER\_SET

The INTC requests the core to execute the ISR if an event is triggered by a peripheral, see *Figure 1*.

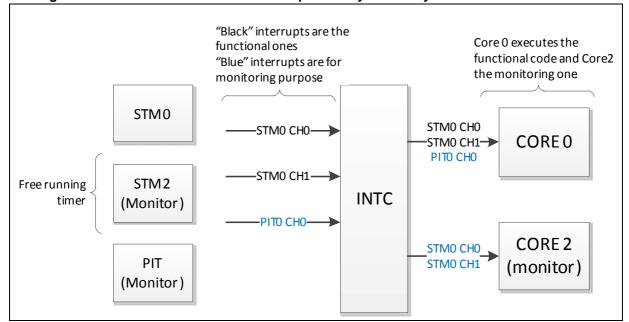

Due to a fault (e.g. an internal bit flip), the INTC could request the execution of an ISR even without any event by a peripheral, see *Figure 5*.

Figure 5. A bit flip in the INTC can cause a spurious interrupt request

To detect such a spurious interrupt, the INT\_CHECK\_TRIGGER\_SET mechanism shall be implemented. Quoting the SM:

The ISR will check that the triggering module actually shows a requested interrupt (for example, reading the interrupt request or status register in the peripheral).

Each peripheral, which can request interrupts, embeds a means to verify whether the interrupt has been requested or not. In most cases this mechanism is a status flag or register, e.g.:

- Channel Interrupt Flag (CIF) implemented by the STM,

- Transmit FIFO Fill Flag (TFFF) implemented by the DSPI.

To implement this safety mechanism the core, each time is requested to execute an ISR, shall verify the status flag of the peripheral triggering the event. A failure is detected if the peripheral status flag shows that not all requests have been sent to the INTC.

Note:

This check must be done before the ISR executes any instruction which can have an impact on the safety goal, for example before sending any safety related messages or before calling any safety related routines.

peripheral INTC interrupt core

Figure 6. INT CHECK TRIGGER SET implementation schema

*Example 3* shows how this software mechanism can be implemented by software in case the requesting peripherals is the STM0.

Example 3: Interrupt service routine checks the status flash of the requesting module

```

void STM0_CH1_ISR_COREO(void) {

...

if (STM_0.Channel[1].CIR.B.CIF != 0x1) {

error_handling_ISR(); //error handling

}

...

}

```

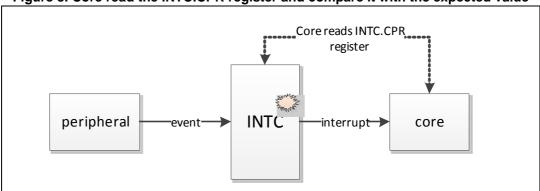

# 3.2 ISR\_CHECK\_PRIORITY

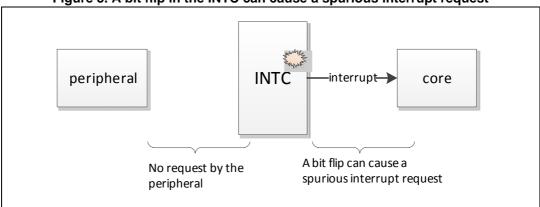

INTC provides priority-based preemptive scheduling of interrupt requests. A higher priority interrupt preempts a lower priority one.

Due to a failure in the INTC, e.g. a bit flip, an interrupt can be serviced with a priority which is higher or lower than the configured one. In such a case the preemption mechanism doesn't work as configured.

This failure has an impact on the safety function because the execution flow of interrupt service routines can be different than the expected one.

Figure 7. Faulty INTC can request interrupt with wrong priority

For example, let's assume 2 ISRs configured to have different priorities (63 is the highest priority):

- ISR\_A with priority 5 (lower priority)

- ISR\_B with priority 6 (higher priority)

Safety function expects that ISR\_A is preempted by ISR\_B, but due to a failure in the INTC ISR\_A is executed with the highest priority, i.e. 63. In such a case the ISR\_B can't preempt the ISR\_A and the safety function is impacted.

To detect such failure mode, the ISR\_CHECK\_PRIORITY mechanism shall be implemented. Quoting the SM:

The ISR shall check that it was called with the correct priority.

The INTC contains a register showing the priority with which an ISR is executing, i.e. current priority register.

To implement this safety mechanism the core, each time is requested to execute an ISR, shall read the current priority in the INTC and compare it with the expected one.

Note:

This check must be done before the ISR executes any instruction which can have an impact on the safety goal, for example before sending any safety related messages or before calling any safety related routines.

Figure 8. Core read the INTC.CPR register and compare it with the expected value

Example 4: Interrupt service routine verifies the current priority

```

void STM0_CH1_ISR_CORE0(void) {

...

u32_CurrentPriority = INTC.CPR[0].B.PRI;

if (u32_CurrentPriority!=PRIORITY_INT_STM_CH1) {

error_handling_ISR(); //error handling

}

...

}

```

It's recommended to implement this safety mechanism not only inside safety related ISRs, but inside every ISR routine. Because if this failure mode affects a non safety related ISR, an impact to the safety related ones can appear. For example:

- ISR\_A is NOT safety related with priority 5 (lower priority)

- ISR\_B is safety related with priority 6 (higher priority)

5

If a failure in the INTC causes the execution of ISR\_A with the highest priority, ISR\_B can't preempt the ISR\_A. As a result the ISR\_B suffers for "late ISR" failure mode. This failure mode is detected by the ISR\_CHECK\_PRIORITY execute inside the ISR\_A.

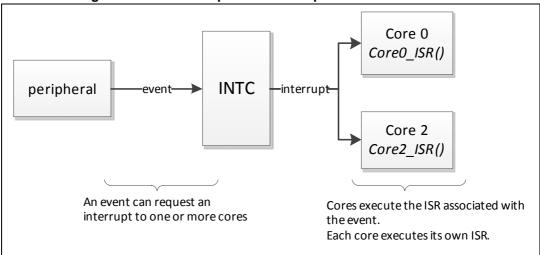

### 3.3 ISR\_CHECK\_CORE

In a multi core MCU as SPC57EM80x/SPC574K72x, the INTC can request an interrupt to one or more cores (see *Figure 9*). Usually the executed interrupt service routine is different core by core<sup>(b)</sup>.

Figure 9 shows a peripheral which triggers an event to the INTC which as a result requests an interrupt to both cores:

- Core 0 executes the Core0\_ISR(), and

- Core 1 executes the Core1\_ISR().

Figure 9. INTC can request an interrupt to one or more cores

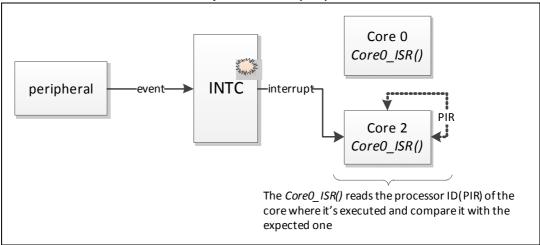

Due to a fault, e.g. a bit flip, the INTC can request a core to execute an interrupt service routine which should be executed by the other core. For example in *Figure 10* the INTC requests Core 2 to execute the *CoreO\_ISR* which is supposed to be executed by Core 0.

This failure mode can have an impact on the safety function because it may generate unexpected situations, for example Core2 tries to access resources reserved to Core 0.

b. If properly designed the same interrupt service routine can be executed by both cores.

DocID025067 Rev 2

Core 0

CoreO\_ISR()

INTC

Interrupt is supposed to be serviced by the CoreO\_executed by CoreO, but due to a failure the CoreO\_ISR() is executed by Core2

Figure 10. Due to a failure the ISR is serviced by the wrong core

To detect such failure mode, the ISR\_CHECK\_CORE mechanism shall be implemented. Quoting the SM:

The ISR checks that it is executed on the expected core using the relevant core register.

To implement this safety mechanism the ISR, each time is requested to be executed, shall read processor ID and compare it with the expected one, see *Figure 11*.

Note:

This check must be done before the ISR executes any instruction which can have an impact on the safety goal, for example before sending any safety related messages or before calling any safety related routines.

The processor ID (PIR) is a special purpose register of the core<sup>(c)</sup>.

Figure 11. Core0\_ISR verifies it's executed on the exepected core by reading the processor ID (PIR)

Example 5 shows how this software mechanism can be implemented.

c. PIR register can be accessed in supervisor mode only.

#### Example 5: Example of implementation of the ISR CHECK CORE mechanism

```

void STM0_CH0_ISR_COREO(void) {

...

u32_CoreId = ProcessorID_GET();//the id of the core executing the ISR is read

if (u32_CoreId != EXPECTED_EXECUTION_CORE_0) {

error_handling_ISR(); //error handling

}

...

}

tU32_ProcessorID_GET(void) {

asm("mfspr r3, 286");

return;

}

```

This mechanism is assumed to be done for all ISRs and not only for the safety-relevant ones. The execution of an ISR on the wrong core has an impact on the safety function because not only it slows down the ISR (due to code and/or data not being in local memory) but also increases load on the wrong core potentially delaying the execution of safety-relevant functions.

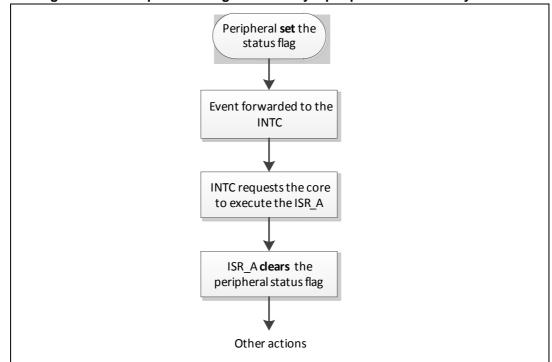

## 3.4 ISR\_CHECK\_TRIGGER\_CLEAR

As described in Section 3.1: INT\_CHECK\_TRIGGER\_SET, each peripheral embeds a means to verify whether an interrupt request is pending or not. In most cases this mechanism is a status flag or a register.

This status flag:

- is set by the peripheral when it triggers an event to the INTC, and

- is reset by software inside the ISR (e.g. ISR\_A in Figure 12).

Assuming there is a periodic ISR, i.e. ISR\_B<sup>(d)</sup>, which has a lower priority than ISR\_A. The ISR\_A, triggered by the STM, can preempt the ISR\_B execution.

With such assumptions and if everything works fine, the ISR\_B never sees the STM status flag set to one. The ISR\_B is never executing while the STM status flag set to one.

d. ISR\_A and ISR\_B are triggered by different interrupt sources.

Figure 12. Interrupt status flag is set the by a peripheral and clear by the ISR

This is not true if there is a failure in the INTC. For example the STM set the flags<sup>(e)</sup> and forward the event to the INTC, but the INTC doesn't request the execution of ISR\_A (i.e. missing interrupt failure mode). In this case the status flag is kept asserted to 1.

This is the idea behind the ISR\_CHECK\_TRIGGER\_CLEAR. Quoting the SM:

Periodically check that interrupt flags in peripherals are cleared.

To implement such a mechanism, a periodic interrupt for monitoring purpose shall be added. The period of such an interrupt shall be smaller than the assumed FTTI and its priority shall be lower than other monitored safety relevant interrupts.

This periodic interrupt must check the interrupt flags of safety relevant interrupts. If at least one of this flag is set 1, a failure has been detected.

**Example 6** shows how the ISR\_CHECK\_TRIGGER\_CLEAR is implemented in the example. The periodic monitor interrupt is generated by the PIT. It monitors 2 safety relevant interrupts coming from channel 0 and 1 of STM 0.

Status flag to be verified by the PITO ISR are:

- STM\_0.Channel[0].CIR.B.CIF and

- STM\_0.Channel[1].CIR.B.CIF.

If one of these status flags is set to 1, the mechanism has potentially detected a missing interrupt. In such a case the error handling function should be called.

e. ISR\_A of the example.

Since there is certain latency between an IRQ flag switching to 1 and the INTC activating the ISR in the core, a not reset flag needs to be validated by re-checking it after the known INTC latency<sup>(f)</sup>.

#### **Example 6**: Implementation of the ISR\_CHECK\_TRIGGER\_CLEAR mechanism

```

void PIT0_Isr(void) {

...

if ((1==STM_0.Channel[0].CIR.B.CIF) ||

(1==STM_0.Channel[1].CIR.B.CIF)) {

DELAY(50); //due to the latency, flags are verified again

if ((1==STM_0.Channel[0].CIR.B.CIF) ||

(1==STM_0.Channel[1].CIR.B.CIF))

error_handling_ISR();

}

...

}

```

# 3.5 ISR\_DOUBLE\_ASSIGNMENT

In a multicore environment as SPC57EM80x/SPC574K72x, an interrupt can be forwarded to two cores (see *Figure 9*). One core executes the safety relevant ISR and the other one verifies its expected execution in terms of time, and eventually of result.

This mechanism is effective in case a safety function requires a short latency and execution time of an ISR. Other mechanisms described in this document can detect different failure modes (e.g. missing interrupt, wrong priority), but not the timely execution of an ISR.

#### Quoting the SM:

Interrupts where a short latency is safety-relevant are assigned to two (or more) cores and one of those cores checks (for example, using a shared variable) that the other core actually executes the ISR within the expected latency after the IRQ occurred.

The core0, executing the functional ISR, can use a shared resource, e.g. a flag saved in RAM, to indicate the status of the execution of the ISR to the other core. The shared flag is set when the functional ISR starts and is reset when it ends.

The monitoring ISR is triggered by the same interrupt event. It must monitor if the shared flag is set/reset in the appropriate time frame.

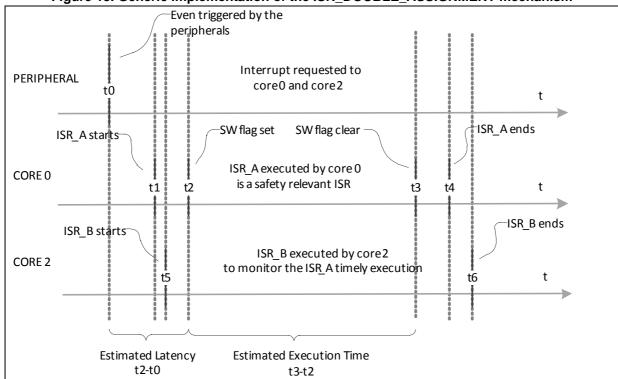

The implementation of this mechanism depends on the application and on the peripherals triggering the interrupts. A generic implementation is shown in *Figure 13*:

- Interrupt is triggered by a peripheral at time t<sub>0</sub>

- At time t₁ the safety relevant ISR, i.e. ISR\_A starts (it ends at time t₂)

- It's executed by core 0

- At time t<sub>5</sub> the monitoring ISR, i.e. ISR\_B starts<sup>(g)</sup> (it ends at time t<sub>6</sub>)

g. ISR\_B may start before than ISR\_A; all comments are still valid.

f. To have all details about the interrupt latency checks the section "Interrupt Latency" of the Reference Manual (see *Appendix A: Reference documents*).

- It's executed by core 2

- At time  $t_2$ , core 0 sets a shared flag to communicate to core 2 that ISR\_A is starting executing the safety relevant actions

- Core 2 waits for the clearing of the shared flag, which is de-asserted at time  $t_3$  by core 0 after the execution of the safety relevant actions

- ISR\_B can verify the ISR\_A timing (e.g. latency and execution time) based on an independent timer.

Figure 13. Generic implementation of the ISR\_DOUBLE\_ASSIGNMENT mechanism

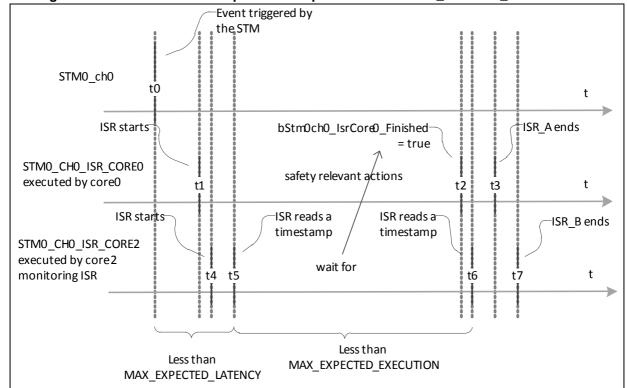

Figure 13 shows a generic example about how to implement the ISR\_DOUBLE\_ASSIGNMENT mechanism. Details about the implemented reference code are given hereafter (Figure 14).

Reference code considers an interrupt sources, i.e. channel #0 of STM0, which triggers interrupt to core 0 and core 2:

- STM0 CH0 ISR CORE0 executed by core 0 executes the safety relevant actions

- STM0\_CH0\_ISR\_CORE2 monitors the timely execution of STM0\_CH0\_ISR\_CORE0.

The monitoring ISR verifies that the total execution time (including latency) of STM0\_CH0\_ISR\_CORE0 is below a certain threshold. To do this check, core 2 reads some timestamps using an independent free-running timer, i.e. STM2<sup>(h)</sup>.

DocID025067 Rev 2

18/28

h. STM2 does not trigger any interrupt, but it is only used at free running timer. STM belongs to a different lake respect STM0 to decrease the probability of CCF.

Figure 14. Schema of the example of the implementation of ISR DOUBLE ASSIGNMENT

The STM0\_CH0\_ISR\_CORE0 executes the safety relevant actions and, at time  $t_2$ , sets a shared variable, i.e. bStm0ch0\_IsrCore0\_Finished, to communicate to core 2 the ISR ends.

#### **Example 7**: Functional ISR sets a shared variable

```

void STM0_CH0_ISR_COREO(void) {

...

/* execute its safety relevant actions*/

...

/* This flag indicates that the ISR is ended.*/

bStm0ch0_IsrCore0_Finished=true;

}

```

The STM0\_CH0\_ISR\_CORE2 executes multiple actions.

At time  $t_5$ , it reads a timestamp from the STM2 counter (see *Example 8*) and it verifies that latency is below an expected threshold (see *Example 9*).

#### **Example 8**: Monitoring ISR reads a timestamp from an independent timer, i.e. STM2

```

void STM0_CH0_ISR_CORE2(void) {

...

/* a first timestamp is read from the free running timer STM2 */

u32InitTimerCounter = STM_2.CNT.R;

...

}

```

#### **Example 9**: Monitoring ISR verifies that latency is below an expected threshold

```

void STM0_CH0_ISR_CORE2(void) {

...

/* interrupt is expected when the STM0 counter reaches the value

STM_0_CH0_TIMEOUT_INIT. latency is estimated by reading the STM0_CH0

counter and subtracting the STM_0_CH0_TIMEOUT_INIT.*/

u32latency =

CounterSubWithOverflow<sup>(i)</sup>(STM_0.CNT.R,STM_0_CH0_TIMEOUT_INIT);

if (u32latency>MAX_EXPECTED_LATENCY) {

error_handling_ISR(); //error handling

}

...

}

```

Then it waits for the  $bStm0ch0\_IsrCore0\_Finished$  set to true by the functional ISR, i.e. time  $t_2$ .

At this point it can read another timestamp from the STM2, i.e. time  $t_6$ . Subtracting the 2 read timestamps, it can verify the execution time of STM0\_CH0\_ISR\_CORE0 is below a threshold, i.e. MAX\_EXPECTED\_EXECUTION.

The reference code implements a software timeout to detect not expected situation as for example the *bStm0ch0\_IsrCore0\_Finished* never set to true (see *Example 10*).

#### Example 10: Execution time of functional ISR is estimated by monitoring one

```

void STM0_CH0_ISR_CORE2(void) {

. . .

/* passed time considering the overflow is measured using the the free

running timer STM2. A second time stamp is read */

u32WaitingTime = CounterSubWithOverflow(i) (STM 2.CNT.R,

u32InitTimerCounter);

/* loop exits if:

a) interrupt is serviced by Core 0, or

b) time-out expires */

while( (bStm0ch0 IsrCore0 Finished==false) &&

(u32WaitingTime<MAX EXPECTED EXECUTION));

/* check if Core 0 executed the ISR in time */

if (bStm0ch0 IsrCore0 Finished==false) {

error_handling_ISR();

} else {

/* flag is reset for the next cycle */

bStm0ch0_IsrCore0_Finished=false;

}

}

```

i. This function subtracts 2 values taking into account the counter overflow situation.

### 3.6 ISR\_CHECK\_EFFECT

Instead of checking event status flags, priorities and core ID, a different way to detect failures in the INTC is to verify directly the functional effect of a wrong interrupt service routing execution.

This generic mechanism includes checking any functional parameter related to the application to detect failure in the INTC, for example:

- DSPI buffer over-run event in the receiving FIFO may indicate that ISR used to retrieve data out from the receiving FIFO has not been executed as expected, or

- If the application expects a fixed number of interrupt in a FTTI, it is possible to count them and compare it with the expected number, or

- In case of interrupts with a known period it's possible to measure the elapsed time between 2 consecutive interrupts and compare it with the expected period.

#### Quoting the SM:

Periodically check for effects of lost interrupts (for example, buffer overflow or underflow).

It is possible to use such kind of methodologies to detect different failures modes, e.g. missing/spurious interrupt and late interrupts.

Note:

Implementation of this safety mechanism is strictly application dependent. Aim of this section is not to describe all possible implementations, but describes some common ones.

The reference code considers 2 safety relevant periodic ISRs

- STM0\_CH0\_ISR\_CORE0 triggered by STM0 ch0

- STM0\_CH1\_ISR\_CORE0 triggered by STM0 ch1

and a monitor one

• PIT0\_Isr triggered by PIT0.

Each time the STM0\_CH0\_ISR\_CORE0 (or STM0\_CH1\_ISR\_CORE0) is executed a software counter is incremented (see *Example 11*).

#### Example 11: Safety relevant ISR increases a software counter when executed

```

void STM0_CH0_ISR_CORE0(void) {

...

/* this global variable is used to count the number of interrupt in a

certain period. It is used to implement the ISR_CHECK_EFFECT safety

mechanism */

u32NumOf_Stm0ch0core0_ISR++;

...

}

void STM0_CH1_ISR_CORE0(void) {

...

u32NumOf_Stm0ch1core0_ISR++;

...

}

```

*PITO\_Isr* is called every FTTI. It reads the software counters to verify how many times, safety relevant ISRs have been executed.

```

void PIT0_Isr(void) {

...

/* Considering application expects a certain number of STM interrupts in

a certain period. Missing interrupt can detected by reading, each

period, the number of executed STM interrupt

and compare it with the expected one. */

if (

EXPECTED_NUMOF_STMOCHOCOREO_ISR != u32NumOf_StmOchOcoreO_ISR ||

EXPECTED_NUMOF_STMOCHICOREO_ISR != u32NumOf_StmOchIcoreO_ISR ) {

error_handling_ISR(); //error handling

}

...

/* Counters are re-initialized to 0 */

u32NumOf_StmOchIcoreO_ISR = 0;

u32NumOf_StmOchOcoreO_ISR = 0;

...

}

```

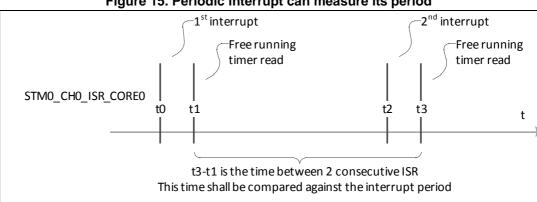

Since the 2 safety relevant interrupts are periodic additional checks can be implemented. Two timestamps read from a free running timer can be used to verify the period (see *Figure 15*).

Figure 15. Periodic interrupt can measure its period

In our example the free-running timer is provided by the STM2.

Each time the STM0\_CH0\_ISR\_CORE0<sup>(j)</sup> is called, it reads a timestamp from a freerunning counter. It uses this timestamp with the one from the last ISR invocation to measure the execution period and compares it with the expected one, see *Example 12*.

5

j. Same mechanism is applied also on the STM0\_CH1\_ISR\_CORE0.

# **Example 12**: Period of safety relevant ISR is measured via a 2 consecutive read of free running counter

```

void STM0_CH0_ISR_COREO(void) {

...

/* In case the interrupt to be monitored is periodic its possible measure

its frequency via a free running timer every time the ISR is called:

-store the current value of the timer and

-compare it against the stored value from the last ISR invocation.

This can detect the spurious/late/missing ISR execution. */

...

u32CurrentTimeStamp = STM_2.CNT.R;

u32_MeasuredPeriod = CounterSubWithOverflow<sup>(k)</sup> (u32CurrentTimeStamp,

u32PreviousTimeStamp);

if ((u32_MeasuredPeriod < EXPECTED_STM0_CH0_PERIOD_LOW) ||

(u32_MeasuredPeriod > EXPECTED_STM0_CH0_PERIOD_HIGH)) {

/* measured period not compliant with the expected time */

error_handling_ISR();

}

...

}

```

5

k. This function subtracts 2 values taking into account the counter overflow situation.

Summary AN4344

# 4 Summary

This document based on an example describes the recommended software mechanisms to grant the correct execution of the interrupt service routines.

The document cannot describe all possible solutions to implement these software mechanisms because some of them are application dependent. Aim of this AN is to make the user aware of what needs to be implemented in software.

These software mechanisms are not strictly mandatory, but they have been assumed to be implemented by the safety analysis done for SPC57EM80x/SPC574K72x. User may not implement them, but it's up to him to provide other methods to cover the respective failure modes.

AN4344 Reference documents

# Appendix A Reference documents

SPC57EM80xx - 32-bit Power Architecture<sup>®</sup> based MCU with up to 4 Mbyte Flash and 304 Kbyte RAM memories (RM0314, DocID022530)

- 2. SPC574Kxx 32-bit Power Architecture® based MCU for automotive applications (RM0334, DocID023671)

- 3. 32-bit Power Architecture<sup>®</sup> based MCU for automotive applications (SPC57EM80E7, SPC57EM80C3, DocID022502)

- 4. 32-bit Power Architecture<sup>®</sup> based MCU for automotive applications (SPC574K72E5, SPC574K72E7, DocID023601)

- 5. Safety application guide for SPC57EM80x family (AN4252, DocID024256)

- 6. Road vehicles Functional safety, ISO/FDIS 26262:2011

Acronyms AN4344

# Appendix B Acronyms

Table 1. Acronyms

| Acronym | Name                                             |

|---------|--------------------------------------------------|

| SoC     | System on Chip                                   |

| FMEDA   | Failure Modes, Effects, and Diagnostics Analysis |

| ASIL    | Automotive Safety Integrity Level                |

| SM      | Safety Manual                                    |

| RM      | Reference Manual                                 |

| INTC    | Interrupt controller                             |

| MCU     | Microcontroller                                  |

| ISR     | Interrupt service routine                        |

| STM     | System Timer Module                              |

| DSPI    | Deserial Serial Peripheral Interface             |

| PIT     | Periodic Interrupt Timer                         |

| FTTI    | Fault Tolerant Time Interval                     |

| CCF     | Common Cause Failure                             |

AN4344 Revision history

# **Revision history**

**Table 2. Document revision history**

| Date        | Revision | Changes             |

|-------------|----------|---------------------|

| 05-Aug-2013 | 1        | Initial release.    |

| 17-Sep-2013 | 2        | Updated Disclaimer. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com