# AN4646 Application note

# Peripheral interconnections on STM32F401 and STM32F411 lines

#### Introduction

On top of the highest performance and the lowest power consumption of the STM32F4 family, STM32F401/411 peripherals can communicate autonomously, without any intervention from the CPU, via a network known as peripheral interconnect matrix.

This STM32F401/411 feature enhances CPU real-time performance while substantially reducing its energy consumption.

The present document first describes the peripheral interconnect matrix features and then provides an overview on the peripheral interconnections and on how to configure them depending on your application. This description is completed by a detailed application example.

This application note must be read in conjunction with STM32F401 line reference manual (RM0383) and STM32F411 line reference manual (RM0368). Both documents are available from http://www.st.com/stm32.

Table 1. Applicable products

| Туре             | Product lines |

|------------------|---------------|

| Microcontrollers | STM32F401     |

|                  | STM32F411     |

March 2015 DocID027369 Rev 1 1/17

### **Contents**

| 1 | Mod  | dule ove  | erview 5                             |

|---|------|-----------|--------------------------------------|

| 2 | Peri | pheral i  | nterconnect matrix                   |

|   | 2.1  | Timers    | s block                              |

|   |      | 2.1.1     | From TIM to TIM                      |

|   |      | 2.1.2     | From TIM to ADC                      |

|   |      | 2.1.3     | From TIM to DMA                      |

|   | 2.2  | Analo     | og block                             |

|   |      | 2.2.1     | From temperature sensor to ADC1      |

|   |      | 2.2.2     | From Analog block to DMA10           |

|   | 2.3  | Clocks    | s block                              |

|   |      | 2.3.1     | From CSS to TIM                      |

|   |      | 2.3.2     | From LSE, LSI, RTC to TIM            |

|   | 2.4  | Syster    | m block                              |

|   |      | 2.4.1     | From VBAT, VREFINT to ADC            |

|   |      | 2.4.2     | From EXTI to analog block11          |

|   | 2.5  | Comm      | nunication interfaces11              |

|   |      | 2.5.1     | From USB block to TIM11              |

|   |      | 2.5.2     | From Communication interfaces to DMA |

|   | 2.6  | DMA l     | olock 12                             |

| 3 | Арр  | lication  | example 13                           |

|   | 3.1  | Hardw     | vare description                     |

|   | 3.2  | Softwa    | are description                      |

| 4 | Con  | clusion   |                                      |

| 5 | Revi | ision his | story                                |

AN4646 List of tables

# List of tables

| Table 1. | Applicable products                          | 1  |

|----------|----------------------------------------------|----|

| Table 2. | STM32F401/411 peripheral interconnect matrix | 7  |

| Table 3. | Peripheral interconnect configuration detail | 14 |

| Table 4. | Document revision history                    | 16 |

List of figures AN4646

# List of figures

| Figure 1. | STM32F401/411 peripheral interconnection overview | 6 |

|-----------|---------------------------------------------------|---|

| Figure 2. | Master/Slave timer overview                       | S |

| Figure 3. | Master TIM/Slave ADC overview                     | S |

| Figure 4. | SOF connectivity                                  | 1 |

| Figure 5. | Application overview                              | 3 |

AN4646 Module overview

### 1 Module overview

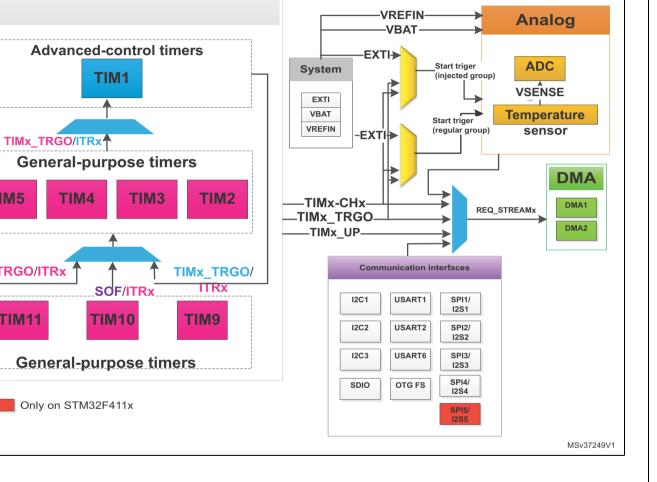

Several peripherals can be directly interconnected and configured to send/respond to event signals that can be internally routed to/from other peripherals in the device.

The STM32F401/411 autonomous peripherals include:

- Timers that can either be internally connected to each other or connected to the DMA or to the analog block.

- Analog block that can receive events from a timer or send events to the DMA.

- Clocks block that can send events to timers.

- System block that can send events to the analog block.

- Communication interfaces that can send events to the timers or to the DMA.

An overview of STM32F401/411 peripheral interconnections is given in *Figure 1: STM32F401/411 peripheral interconnection overview*.

**Timers**

TIMX BKIN

TIM11\_CH1

TIM5

TIMx\_TRGO/ITRx

Clocks

CSS LSE

LSI

**RTC**

## 2 Peripheral interconnect matrix

STM32F401/411 peripherals are interconnected through the peripheral interconnect matrix that allows to directly connect one peripheral to another without waking up the CPU.

These interconnections can operate in Run, Sleep or Stop modes, depending on peripherals.

Peripherals that respond to events are referred to as **users** while peripherals that send events are referred to as **generators**.

Table 2. STM32F401/411 peripheral interconnect matrix<sup>(1)</sup>

|            |        | Users  |       |       |       |       |        |      |      |      |

|------------|--------|--------|-------|-------|-------|-------|--------|------|------|------|

| Generators |        | Timers |       |       |       |       |        |      | DMA  |      |

|            |        | TIM 1  | TIM 2 | TIM 3 | TIM 4 | TIM 5 | TIM 11 | DMA1 | DMA2 | ADC1 |

| Timers     | TIM1   | -      | Х     | Х     | Х     | -     | -      | -    | Х    | Х    |

|            | TIM2   | Х      | -     | Х     | Х     | Х     | -      | Х    | -    | Х    |

|            | TIM3   | Х      | Х     | -     | Х     | Х     | -      | Х    | -    | Х    |

|            | TIM4   | Х      | Х     | Х     | -     | Х     | -      | Х    | -    | Х    |

|            | TIM5   | Х      | -     | Х     | -     | -     | -      | Х    | -    | Х    |

| Analog     | ADC1   | -      | -     | -     | -     | -     | -      | -    | Х    | -    |

|            | VSENSE | -      | -     | -     | -     | -     | -      | -    | -    | Х    |

| Clocks     | LSI    | -      | -     | -     | -     | Х     | -      | -    | -    | -    |

|            | LSE    | -      | -     | -     | -     | Х     | -      |      | -    | -    |

|            | RTC    | -      | -     | -     | -     | Х     | Х      |      | -    | -    |

|            | css    | Х      | -     | -     | -     | -     | -      | -    | -    | -    |

Χ

Users **Timers DMA** Analog Generators DMA1 DMA2 TIM 1 TIM 2 TIM 3 TIM 4 TIM 5 **TIM 11** ADC1 **OTG FS** Χ SPI1/I2S1 Х SPI2/I2S2 Χ -\_ -SPI3/I2S3 Χ SPI4/I2S4 Χ SPI5/I2S5 Х Communication **I2C1** Χ interfaces **I2C2** Χ **I2C3** Χ **USART1** Х **USART2** Χ \_ \_ **USART6** Χ **SDIO** Χ **VBAT** Χ **System VREFINT** Χ

Table 2. STM32F401/411 peripheral interconnect matrix<sup>(1)</sup> (continued)

**EXTI**

#### 2.1 Timers block

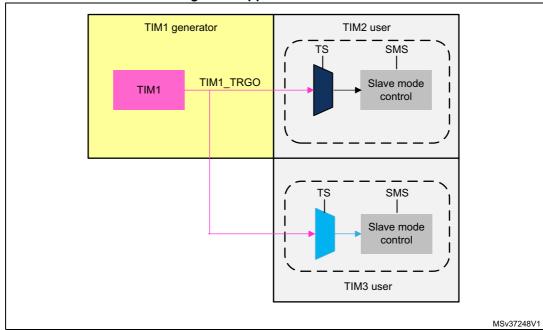

#### 2.1.1 From TIM to TIM

Some timers are linked together internally for timer synchronization or chaining. When one timer (TIMx) is configured in Master mode, it can reset, start, stop or clock the counter of any other timer configured in Slave mode (TIMy).

The master output is TIMx\_TRGO signal. This output is configured as a timer event through TIMx\_CR2 register. It is sent to TIMy\_ITR0/ITR1/ITR2/ITR3 inputs.

Figure 2: Master/Slave timer overview gives an overview of the trigger selection and the master mode selection blocks.

8/17 DocID027369 Rev 1

<sup>1.</sup> In gray, the peripherals that are available only on STM32F411 line.

Master TIM Slave TIM Clock MMS SMS TS UEV Master Slave TRGO **ITR** Counter Prescaler Prescaler mode mode Counter control control MS35838V1

Figure 2. Master/Slave timer overview

A description of this feature is provided in the *Timer synchronization* section on RM0368 and RM0383 reference manuals, while all the possible master/slave connections are described in the *TIMx internal trigger connection* tables.

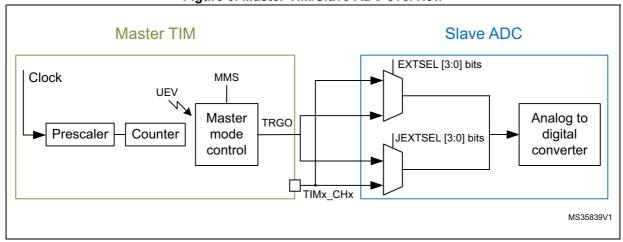

#### 2.1.2 From TIM to ADC

Some timers can be used to generate an ADC trigger event.

The timer output can be either TIMx\_TRGO signal or TIMx\_CHx event. It is input to ADC EXTSEL[3:0] and JEXTSEL [3:0] signals.

Figure 3: Master TIM/Slave ADC overview gives an overview of the trigger selection and master mode selection blocks.

Figure 3. Master TIM/Slave ADC overview

ADC synchronization is described in the *Conversion on external trigger and trigger polarity* section of RM0368 and RM0383 reference manuals. The connection between timers and ADCs regular and injected channels is described in *External trigger for regular channels* and *External trigger for injected channels* tables.

#### 2.1.3 From TIM to DMA

Refer to Section 2.6: DMA block.

### 2.2 Analog block

The analog block includes:

- the ADC block (ADC1)

- the temperature sensor block.

#### 2.2.1 From temperature sensor to ADC1

On STM32F401/411 devices, the temperature sensor is internally connected to ADC1\_IN18 input channel. It is used to convert the sensor output voltage into a digital value.

The *Temperature sensor* reference manual section describes the connection between sensor and ADC as well as the procedure to read the converted value.

#### 2.2.2 From Analog block to DMA

Refer to Section 2.6: DMA block.

#### 2.3 Clocks block

The clock block includes:

- the LSE clock

- the LSI clock

- the clock security system (CSS)

- the real-time clock (RTC)

#### 2.3.1 From CSS to TIM

The CSS can generate system errors. In this case a clock failure event is sent to TIM1 break inputs.

The purpose of the break function is to protect the power switches driven by PWM signals generated by the timer.

The list of possible break sources is given in the *Using the break function (TIM1)* reference manual section.

#### 2.3.2 From LSE, LSI, RTC to TIM

External clock (LSE), internal clock (LSI) and RTC wakeup interrupt can be input to general-purpose timer (TIM5 channel 4/TIM11 channel 1).

This feature is described in the following sections of RM0368 and RM0383 reference manuals:

- Internal/external clock measurement using TIM5/TIM11

- TIM5 option register (TIM5\_OR)

- TIM11 option register 1 (TIM11\_OR).

#### System block 2.4

The system blocks include:

- Internal reference voltage (V<sub>REFINT</sub>)

- V<sub>BAT</sub> supply voltage

- External interrupt/event controller (EXTI).

#### 2.4.1 From VBAT, VREFINT to ADC

The V<sub>BAT</sub> channel is connected to ADC1\_IN18 channel. It can be converted either as an injected or as a regular channel.

V<sub>REFINT</sub> is connected to ADC1\_IN17.

Refer to the following reference manual sections for a description of the interconnection between V<sub>BAT</sub>, V<sub>REFINT</sub> and ADC:

- Channel selection

- Battery charge monitoring.

#### 2.4.2 From EXTI to analog block

An external interrupt/event (EXTI) can be used to generate an ADC trigger event or to start DAC conversion.

ADC synchronization is described in the Conversion on external trigger and trigger polarity section of the reference manuals.

#### **Communication interfaces** 2.5

#### 2.5.1 From USB block to TIM

The USB OTG FS SOF pulse signal can trigger TIM2 general-purpose timer.

STM32 SOF pulse output to external audio control SOF pulse ITR1 TIM2 SOFgen TIM2 Slave **USB** Master MS35807V1

Figure 4. SOF connectivity

The interconnection between USB and TIM2 is described in the *SOF trigger* section of RM0368 and RM0383 reference manuals.

#### 2.5.2 From Communication interfaces to DMA

Refer to Section 2.6: DMA block.

#### 2.6 DMA block

Each stream is associated with a DMA request that can be selected out of 8 possible channel requests. This selection is controlled by the CHSEL [2:0] bits of the DMA\_SxCR register. The 8 requests from the peripherals (TIM, ADC, SPI, I2C, etc.) are independently connected to each channel and their connection depends on the product implementation.

This interconnection is explained in the following tables of RM0368 and RM0383 reference manuals:

- DMA1 request mapping

- DMA2 request mapping.

### 3 Application example

This application example demonstrate how to use the peripheral interconnect matrix on STM32F401/411 lines and shows how to synchronize TIM peripherals in parallel mode.

This firmware is based on STM32F4xx HAL drivers which is part of STM32CubeF4.

### 3.1 Hardware description

Three timers are used in this example:

- TIM1 is configured as master timer:

- PWM mode is enabled

- TIM2 update event is used as trigger output.

- TIM2 and TIM3 are slaves for TIM1

- PWM mode is enabled

- ITR0(TIM1) is used as trigger input for both slave timers.

Figure 5. Application overview

1. The generator (TIM1) is shown in yellow, while the user blocks (TIM2 and TIM3) are highlighted in gray.

### 3.2 Software description

TIM1 counter clock is 84 MHz.

TIM1 master timer is running at TIM1 frequency:

- TIM1 frequency = TIM1 counter clock/ (TIM1 period + 1) = 328.125 KHz

- The duty cycle is equal to TIM2\_CCR1/ (TIM2\_ARR + 1) = 25%.

Application example AN4646

TIM2 slave timer is running at:

- (TIM1 frequency)/ (TIM2 period + 1) = 32.815 KHz

- The duty cycle is equal to TIM2\_CCR1/ (TIM2\_ARR + 1) = 30%

TIM3 slave timer is running at:

- (TIM1 frequency)/ (TIM3 period + 1) = 65.630 KHz

- The duty cycle is equal to: TIM3\_CCR1/ (TIM3\_ARR + 1) = 60%

*Table 3: Peripheral interconnect configuration detail* gives code examples to configure TIM1, TIM2 and TIM3 as described above.

Table 3. Peripheral interconnect configuration detail

| Interconnect        | Example                                                                                                                                                                                                                                                                                                                                                     | Comments                                                                                                                                                                            |  |  |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TIM1 master timer   | <pre>sMasterConfig.MasterOutputTrigger = TIM_TRGO_UPDATE sMasterConfig.MasterSlaveMode = TIM_MASTERSLAVEMODE_ENABLE; HAL_TIMEx_MasterConfigSynchronization(&amp;htim1, &amp;sMasterConfig);</pre>                                                                                                                                                           | Configures TIM2<br>Update event as<br>Trigger Output                                                                                                                                |  |  |

| TIM2 slave<br>timer | <pre>sSlaveConfig.SlaveMode = TIM_SLAVEMODE_GATED; sSlaveConfig.InputTrigger = TIM_TS_ITR0; HAL_TIM_SlaveConfigSynchronization(&amp;htim2, &amp;sSlaveConfig); sMasterConfig.MasterOutputTrigger = TIM_TRGO_RESET; sMasterConfig.MasterSlaveMode=TIM_MASTERSLAVEMODE_DIS ABLE; HAL_TIMEx_MasterConfigSynchronization(&amp;htim2, &amp;sMasterConfig);</pre> | Configures ITR0 as trigger input for both slaves. Enables the Gated mode so that the start/stop of slave counters is controlled by the master trigger output signal (update event). |  |  |

| TIM3 slave<br>timer | <pre>sSlaveConfig.SlaveMode = TIM_SLAVEMODE_GATED; sSlaveConfig.InputTrigger = TIM_TS_ITR0; HAL_TIM_SlaveConfigSynchronization(&amp;htim3, &amp;sSlaveConfig); sMasterConfig.MasterOutputTrigger = TIM_TRGO_RESET; sMasterConfig.MasterSlaveMode=TIM_MASTERSLAVEMODE_DIS ABLE; HAL_TIMEx_MasterConfigSynchronization(&amp;htim2, &amp;sMasterConfig);</pre> |                                                                                                                                                                                     |  |  |

AN4646 Conclusion

### 4 Conclusion

This application note complements STM32F401/411 datasheets and reference manuals by introducing the Peripheral interconnect matrix.

It also gives a detailed description of a basic example that can be a used as a starting point to develop your own application.

Revision history AN4646

# 5 Revision history

Table 4. Document revision history

| Date            | Revision | Changes          |  |  |

|-----------------|----------|------------------|--|--|

| 19-Mar-2015 1 I |          | Initial release. |  |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics - All rights reserved