# AN4658 Application note

# Migration of applications from STM32F429/439 lines to STM32F446 line

#### Introduction

For more and more applications using STM32 products, it is important to easily migrate a project to a different microcontroller in the same product family.

Migrating an application to a different microcontroller is needed, for instance, when product requirements grow, putting extra demands on memory size, or requiring an increase in the number of I/Os. On the other hand, cost reduction objectives may force to switch to cheaper components and towards shrinking the PCB area.

This application note is intended to help the user to analyze the steps needed to migrate from existing designs based on STM32F429xx and STM32F439xx products to STM32F446xx devices. It groups together all the most important information and lists the key items to address.

In this document the comparisons are carried out for "fully featured" microcontrollers of the STM32F429/439 and STM32F446 lines, user must consider that some products may have less features (depending on actual part number).

Migrating between two devices within the same family can require in some cases hardware and/or software changes: the required ones are described in this document.

To benefit fully from the information in this application note, the user should be familiar with the STM32 microcontroller family.

This application note has to be read in conjunction with STM32F429xx/STM32F439xx and STM32F446xx reference manuals (RM0090 and RM0390, respectively) and datasheets available at <a href="https://www.st.com">www.st.com</a>.

**Table 1. Applicable products**

| Product type     | Product lines              |

|------------------|----------------------------|

| Microcontrollers | STM32F429/439<br>STM32F446 |

March 2015 DocID027496 Rev 1 1/24

AN4658

## **Contents**

Contents

| 1 | Hard  | Hardware migration guide                     |  |  |  |

|---|-------|----------------------------------------------|--|--|--|

|   | 1.1   | Recommendations for board migration 5        |  |  |  |

| 2 | Perip | oheral migration guide                       |  |  |  |

|   | 2.1   | STM32 product cross-compatibility            |  |  |  |

|   | 2.2   | Memory mapping 9                             |  |  |  |

|   | 2.3   | Flash memory                                 |  |  |  |

|   | 2.4   | Flexible memory controller (FMC)11           |  |  |  |

|   | 2.5   | Interrupts                                   |  |  |  |

|   | 2.6   | RCC 13                                       |  |  |  |

|   | 2.7   | RTC 14                                       |  |  |  |

|   | 2.8   | PWR 15                                       |  |  |  |

|   | 2.9   | U(S)ART                                      |  |  |  |

|   | 2.10  | I2C 16                                       |  |  |  |

|   | 2.11  | Audio interfaces                             |  |  |  |

|   | 2.12  | CRC 17                                       |  |  |  |

|   | 2.13  | USB OTG 18                                   |  |  |  |

|   | 2.14  | Digital camera interface (DCMI)              |  |  |  |

|   | 2.15  | Secure digital input/output interface (SDIO) |  |  |  |

|   | 2.16  | ADC/DAC                                      |  |  |  |

| 3 | Cond  | clusion                                      |  |  |  |

| 4 | Revi  | sion history                                 |  |  |  |

AN4658 List of tables

# List of tables

| Table 1.  | Applicable products                                | . 1  |

|-----------|----------------------------------------------------|------|

| Table 2.  | Pinout comparison (LQFP packages)                  | . 5  |

| Table 3.  | Peripheral compatibility analysis                  | . 7  |

| Table 4.  | Peripheral bus mapping comparison                  | . 9  |

| Table 5.  | Flash memory comparison                            | 10   |

| Table 6.  | FMC comparison                                     | . 11 |

| Table 7.  | Interrupt vector comparison                        | . 12 |

| Table 8.  | Reset and Clock Controller comparison              | . 13 |

| Table 9.  | RTC comparison                                     | 14   |

| Table 10. | PWR comparison                                     | . 15 |

| Table 11. | PWR_CR register for STM32F446xx products           | . 16 |

| Table 12. | PWR_CSR register for STM32F446xx products          | 16   |

| Table 13. | USART comparison                                   | 16   |

| Table 14. | Audio interfaces comparison                        | . 17 |

| Table 15. | SPI_I2SCFGR register for STM32F446xx products      |      |

| Table 16. | CRC features for STM32F429xx/439xx and STM32F446xx | . 17 |

| Table 17. | USB comparison                                     | 18   |

| Table 18. | DCMI comparison                                    | 19   |

| Table 19. | DCMI_CR register for STM32F446xx products          |      |

| Table 20. | SDIO comparison                                    |      |

| Table 21. | SDIO_STA register for STM32F446xx products         | 20   |

| Table 22. | SDIO_ICR register for STM32F446xx products         | 20   |

| Table 23. | SDIO_CMD register for STM32F446xx products         | 20   |

| Table 24. | Document revision history                          | 23   |

List of figures AN4658

# List of figures

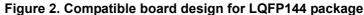

| Figure 1. | Compatible board design for LQFP100 package | 6 |

|-----------|---------------------------------------------|---|

| Figure 2. | Compatible board design for LQFP144 package | 6 |

## 1 Hardware migration guide

Except for the LQFP100 and LQFP144 packages, the STM32F446xx devices are fully pin-to-pin compatible with the STM32F429xx/439xx devices, allowing the user to try different peripherals, and reaching higher performance (higher frequency) for a greater degree of freedom during the development cycle.

The transition from the STM32F429/439 lines to the STM32F446 line is simple since only a few pins are impacted, as summarized in *Table 2*.

| idale 211 medit companies (2411 packages) |                   |                       |             |                   |                      |  |

|-------------------------------------------|-------------------|-----------------------|-------------|-------------------|----------------------|--|

| STM32F429xx/439xx                         |                   |                       | STM32F446xx |                   |                      |  |

| QFP100                                    | QFP144            | Pinout                | QFP100      | QFP144            | Pinout               |  |

| 48                                        | -                 | PB11                  | 48          | -                 | VCAP1                |  |

| 49                                        | -                 | VCAP1                 | 49          | -                 | VSS                  |  |

| -                                         | 70 <sup>(1)</sup> | PB11 (OTG_HS_ULPI_D4) | -           | 70 <sup>(1)</sup> | PB11                 |  |

| -                                         | 48 <sup>(1)</sup> | PB2                   | -           | 48 <sup>(1)</sup> | PB2 (OTG_HS_ULPI_D4) |  |

| -                                         | 95                | VDD                   | -           | 95                | VDDUSB               |  |

Table 2. Pinout comparison (LQFP packages)

#### 1.1 Recommendations for board migration

For the LQFP100 package PB11 is not available anymore and it is replaced by VCAP1.

For the LQFP144 the PCB change is mandatory only when an external ULPI PHY is used in USB HS mode, otherwise no PCB update is needed.

A dedicated VDDUSB supply is used on STM32F446 and it is available only on LQFP144, UFBGA144 and WLCSP81 packages.

The pin PDR\_ON used on STM32F429 to enable power supervisor is now managed in static way.

*Figure 1* and *Figure 2* show two examples of board designs migrating from STM32F429 to STM32F446.

For the LQFP144 the PCB change is mandatory only when an external ULPI PHY is used in USB HS mode, otherwise no PCB update is needed.

0  $\Omega$  resistor or soldering bridge present for the STM32F446 configuration, not present in other STM32F4xx configurations 75 76 49 48 PB11 not available Not populated when 0  $\Omega$  resistor for the STM32F446 or soldering bridge is present Populated when  $0 \Omega$  resistor 100 0 or soldering bridge is present 25 MS37366V1

Figure 1. Compatible board design for LQFP100 package

## 2 Peripheral migration guide

#### 2.1 STM32 product cross-compatibility

The STM32 microcontrollers embed a set of peripherals that can be classed in three categories:

- 1. Peripherals which are by definition common to all products. Those peripherals are identical, so they have the same structure, registers and control bits. There is no need to perform any firmware change to keep the same functionality at the application level after migration. All the features and behavior remain the same.

- 2. Peripherals which are shared by all products but have only minor differences (in general to support new features), so migration from one product to another is very easy and does not need any significant new development effort.

- 3. Peripherals which have been considerably changed from one product to another (new architecture, new features...). For this category of peripherals, migration will require new development at application level.

*Table 3* summarizes the available peripherals and their compatibility between the STM32F429/439 and the STM32F446 lines.

Compatibility **Peripherals** STM32F429xx/439xx STM32F446xx **SW** Comments 512K Flash memory (in Bytes) 2M 256 128 System **SRAM** (112+16+64+64)(112+16)(in KBytes) 4 4 Backup General Purpose 10 10 \_ Advanced control **Timers** 2 2 2 Basic 2

Table 3. Peripheral compatibility analysis

Table 3. Peripheral compatibility analysis (continued)

| Peripherals              |                       | STM32F429xx/439xx | OTMOOF 440        | Compatibility                                         |                                                          |

|--------------------------|-----------------------|-------------------|-------------------|-------------------------------------------------------|----------------------------------------------------------|

| Perip                    | renpherais            |                   | S1M32F446XX       | SW                                                    | Comments                                                 |

|                          | SPI / I2S             | 6/2               | 4/3               | API enhancement<br>to handle new I2S<br>clock sources | New clock source<br>for I2S<br>on APB2                   |

|                          | FMPI2C                | No                | 1                 | -                                                     | New peripheral<br>(new IOs to<br>support FM+)            |

|                          | USART / UART          | 4 / 4             | 4 /2              | -                                                     | -                                                        |

| Communication interfaces | USB OTG FS USB OTG HS | Yes               | Yes               | -                                                     | Dedicated V <sub>DDUSB</sub> More endpoints on STM32F446 |

|                          | CAN                   | 2                 | 2                 | -                                                     | -                                                        |

|                          | SAI                   | 1                 | 2                 | API enhancement<br>to handle new SAI<br>clock sources | New clock source added                                   |

|                          | SDIO/SDMMC            | Yes               | Yes               | -                                                     | New clock source is SYSCLK                               |

|                          | SPDIF-RX              | No                | 4 parallel inputs | -                                                     | New peripheral                                           |

| RNG                      |                       | Yes               | No                | -                                                     | -                                                        |

| QuadSPI                  |                       | No                | Yes               | -                                                     | New peripheral                                           |

| FMC (memory controller)  |                       | Yes               | Yes               | -                                                     | -                                                        |

| Ethernet                 |                       | Yes               | No                | -                                                     | -                                                        |

| HDMI-CEC                 |                       | No                | Yes               | -                                                     | -                                                        |

| DCMI                     |                       | Yes               | Yes               | -                                                     | -                                                        |

| WWDG                     |                       | Yes               | Yes               | -                                                     | -                                                        |

| IWDG                     |                       | Yes               | Yes               | -                                                     | -                                                        |

| CRC                      |                       | Yes               | Yes               | -                                                     | -                                                        |

| LCD-TFT                  |                       | Yes               | No                | -                                                     | -                                                        |

| DMA                      |                       | DMA1-DMA2 (8 st   | reams each)       | -                                                     | Enhanced<br>dynamic power<br>consumption                 |

| Chrom-Art-Acce           | lerator™ DMA2D        | Yes               | No                | -                                                     | -                                                        |

| Crypto                   |                       | Yes               | No                | -                                                     | -                                                        |

| Hash                     |                       | Yes               | No                | -                                                     | -                                                        |

| GPIOs                    |                       | Up to 168         | Up to 114         | -                                                     | -                                                        |

Table 3. Peripheral compatibility analysis (continued)

| Peripherals   |                    | STM32F429xx/439xx    | STM22E446vv | Compatibility |                                                                                                                                                |

|---------------|--------------------|----------------------|-------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Peli          | prierais           | 5 I WI32F429XX/439XX | 31W32F446XX | sw            | Comments                                                                                                                                       |

|               | Count              | 3                    | 3           | -             | -                                                                                                                                              |

| ADC (12 bits) | Number of channels | 16 / 24              | 16 / 24     | -             | -                                                                                                                                              |

|               | Count              | 1                    | 1           | -             | -                                                                                                                                              |

| DAC (12 bits) | Number of channels | 2                    | 2           | -             | -                                                                                                                                              |

| RCC           |                    | Yes                  | Yes         | -             | More flexibility, with additional clock sources to AHB, USB and audio peripherals. Dedicated input clock divider input for PLL.  New LSE mode. |

The Cube Hardware Abstraction Layer (HAL) is compatible between the STM32F429/F439 and STM32F446 lines.

## 2.2 Memory mapping

Address mapping has been slightly changed in the STM32F446xx vs. STM32F429xx/439xx, the differences are shown in *Table 4*, where a gray cell indicates that the feature is not available (NA).

Table 4. Peripheral bus mapping comparison

| Peripheral       | Bus  | STM32F429xx/439xx<br>Base address | STM32F446xx<br>Base address |

|------------------|------|-----------------------------------|-----------------------------|

| QuadSPI Register | AHB3 | NA                                | 0xA000 1000                 |

| RNG              |      | 0x5006 0800                       | NA                          |

| HASH             | AHB2 | 0x5006 0400                       | NA                          |

| CRYP             |      | 0x5006 0000                       | NA                          |

| DMA2D            |      | 0x4002 B000                       | NA                          |

| ETHERNET MAC     |      | 0x40029000                        | NA                          |

| CPIOK            | AHB1 | 0x4002 2800                       | NA                          |

| GPIOJ            |      | 0x4002 2400                       | NA                          |

| GPIOI            |      | 0x4002 2000                       | NA                          |

| Peripheral | Bus  | STM32F429xx/439xx<br>Base address | STM32F446xx<br>Base address |

|------------|------|-----------------------------------|-----------------------------|

| LCD-TFT    |      | 0x4001 6800                       | NA                          |

| SPI6       | APB2 | 0x4001 5400                       | NA                          |

| SPI5       | AFDZ | 0x4001 5000                       | NA                          |

| SAI2       |      | NA                                | 0x4001 5C00                 |

| UART8      |      | 0x4000 7C00                       | NA                          |

| UART7      |      | 0x4000 7800                       | NA                          |

| HDMI-CEC   | APB1 | NA                                | 0x4000 6C00                 |

| I2S3ext    | APB1 | 0x4000 4000                       | NA                          |

| SPDIFRX    |      | NA                                | 0x4000 4000                 |

| I2S2ext    |      | 0x4000 3400                       | NA                          |

Table 4. Peripheral bus mapping comparison (continued)

## 2.3 Flash memory

Peripheral migration guide

The differences between the Flash interface of STM32F446 products vs. those of the STM32F429/439 lines are indicated in *Table 5* (a gray cell indicates that the feature is not available). For more information on programming, erasing and protection of STM32F446xx, please refer to the RM0390 reference manual.

Flash STM32F429xx/439xx STM32F446xx 0x0800 0000 - (up to) 0x081F FFFF 0x0800 0000 - up to 0x0807 FFFF Up to 2 Mbytes (split in 2 banks) Up to 512 Kbytes Main / Program memory 4 sectors of 16 Kbytes 4 sectors of 16 Kbytes 1 sector of 64 Kbytes 1 sector of 64 Kbytes 3 sectors of 128 Kbytes 6 sectors of 128 Kbytes Read while Write (RWW) **Features** NA **Dual Bank Boot** Wait states Up to 8 (depending on the supply voltage and frequency) One Time Programmable 512 bytes (OTP) memory 0x1FFF C000 - 0x1FFF C00F Option bytes 0x1FFF C000 - 0x1FFF C00F 0x1FFE C000 - 0x1FFE C00F 0x4002 3C00 Interface

Table 5. Flash memory comparison

| , company (community |                   |              |  |

|----------------------|-------------------|--------------|--|

| Flash                | STM32F429xx/439xx | STM32F446xx  |  |

|                      | nRST_STOP         | nRST_STOP    |  |

|                      | nRST_STDBY        | nRST_STDBY   |  |

|                      | WDG_SW            | IWDG_SW      |  |

| Lloor option bytos   | BOR_LEV[1:0]      | BOR_LEV[2:0] |  |

| User option bytes    | BFB2              | NA           |  |

|                      | SPRMOD            | SPRMOD       |  |

|                      | DB1M              | NA           |  |

|                      | nWRP              | nWRP         |  |

Table 5. Flash memory comparison (continued)

## 2.4 Flexible memory controller (FMC)

*Table 6* presents the differences between the FMC features of STM32F429/439 and STM32F446 lines.

STM32F446xx **FMC** STM32F429xx/439xx SRAM SRAM NOR/NAND memories NOR/NAND memories PSRAM (4 memory banks) PSRAM (4 memory banks) External memory interface - One bank of NAND Flash Two banks of NAND Flash memory with ECC hardware memory with ECC hardware 16-bit PC Card compatible devices Data bus width 8, 16 or 32 bits 8 or 16 bits Bank1 NOR/PSRAM/SRAM NOR/PSRAM/SRAM 4x64MB Bank2 NAND Flash Reserved 4x64MB Bank3 NAND Flash NAND Flash 4x64MB **FMC Bank** memory mapping Bank4 PC card Reserved 4x64MB

Table 6. FMC comparison

**SDRAM**

SDRAM Bank1 4x64MB

SDRAM Bank2 4x64MB **SDRAM**

**FMC** STM32F429xx/439xx STM32F446xx 0xD000 0000 to PC card 256 MB Reserved 0xDFFF FFFF 0xC000 0000 to NAND Bank2 256 MB NOR/RAM 256 MB 0xCFFF FFFF 0xA000 0000 to Registers Registers 0xAFFF FFFF Memory 0x9000 0000 to mapping swap SDRAM Bank2 256 MB QuadSPI 256 MB 0x9FFF FFFF (SWP\_FMC=01b) 0x8000 0000 to SDRAM Bank1 256 MB NAND Bank3 256 MB 0x8FFF FFFF 0x7000 0000 to NAND Bank1 256 MB SDRAM Bank2 256 MB 0x7FFF FFFF 0x6000 0000 to NOR/RAM 256 MB SDRAM Bank1 256 MB 0x6FFF FFFF

Table 6. FMC comparison (continued)

### 2.5 Interrupts

*Table 7* presents the interrupt vectors in the STM32F429/439 vs. the STM32F446 lines. Again, a gray cell indicates that the feature is not available.

| Position | STM32F429xx/439xx | STM32F446xx |

|----------|-------------------|-------------|

| 61       | ETH               | NA          |

| 62       | ETH_WKUP          | NA          |

| 79       | CRYP              | NA          |

| 80       | HASH_RNG          | NA          |

| 82       | UART7             | NA          |

| 83       | UART8             | NA          |

| 85       | SPI5              | NA          |

| 86       | SPI6              | NA          |

| 88       | LCD-TFT           | NA          |

| 89       | LCD-TFT           | NA          |

| 90       | DMA2D             | NA          |

| 91       | NA                | SAI2        |

| 92       | NA                | QUADSPI     |

| 93       | NA                | HDMI-CEC    |

| 94       | NA                | SPDIF-RX    |

Table 7. Interrupt vector comparison

Table 7. Interrupt vector comparison (continued)

| Position | STM32F429xx/439xx | STM32F446xx   |

|----------|-------------------|---------------|

| 95       | NA                | FMP2C1        |

| 96       | NA                | FMPI2C1 error |

## 2.6 RCC

The main differences related to Reset and Clock Controller in the STM32F446 line vs. the STM32F429/439 lines are presented in *Table 8*, where a gray cell indicates that the feature is not available.

Table 8. Reset and Clock Controller comparison

| RCC                   | STM32F429xx/439xx                               | STM32F446xx                                                                                                                                                      |  |  |

|-----------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AHB                   | 180 MHz                                         | 180 MHz                                                                                                                                                          |  |  |

| APB2                  | 84 MHz                                          | 84 MHz                                                                                                                                                           |  |  |

| APB1                  | 42 MHz                                          | 42 MHz                                                                                                                                                           |  |  |

| PLL                   | One clock input divider for all PLLs (M factor) | <ul> <li>New dedicated clock input divider for each PLL</li> <li>One input clock divider per PLL that needs to be configured before enabling the PLL</li> </ul>  |  |  |

|                       | HSI/HSE                                         | HSI/HSE                                                                                                                                                          |  |  |

| System clock (SYSCLK) | PLL P                                           | PLL_P                                                                                                                                                            |  |  |

|                       | FLL_F                                           | PLL_R                                                                                                                                                            |  |  |

| LSE modes             | One LSE mode is available: low power.           | <ul> <li>New LSE modes are available in STM32446: low power and high drive.</li> <li>User can select the LSE mode by configuring RCC_BDCR[LSEMOD] bit</li> </ul> |  |  |

|                       | Peripherals clock sources                       |                                                                                                                                                                  |  |  |

| USB OTG FS / SDIO     | 48 MHz from main PLL<br>(PLLQ clock output)     | 48 MHz from main PLL<br>(PLLQ clock output)                                                                                                                      |  |  |

| (PLL48CLK)            | -                                               | 48 MHz from PLLSAI<br>(PLLSAIP clock output)                                                                                                                     |  |  |

| SDIO                  | PLL48CLK                                        | PLL48CLK                                                                                                                                                         |  |  |

|                       | I LL40OLIX                                      | System clock (SYSCLK)                                                                                                                                            |  |  |

|                       |                                                 | System clock (SYSCLK)                                                                                                                                            |  |  |

| FMPI2C                | NA                                              | HSI clock                                                                                                                                                        |  |  |

|                       |                                                 | APB1 clock (PCLK1)                                                                                                                                               |  |  |

**RCC** STM32F429xx/439xx STM32F446xx PLLI2SCLK PLLI2SCLK I2S\_CKIN Clock source for I2S on APB1 HSE/HSI I2S\_CKIN Main PLL (PLLR output clock) I2S PLLI2SCLK PLLI2SCLK I2S\_CKIN Clock source for I2S on APB2 HSE/HSI NA Main PLL (PLLR output clock) PLLI2SQ(2) PLLI2SQ<sup>(1)</sup> PLLSAIQ(2) PLLSAIQ<sup>(1)</sup> SAI1 I2S CKIN<sup>(1)</sup> I2S CKIN<sup>(2)</sup> NA Main PLL (PLLR output clock)(2) PLLI2SQ(2) PLLSAIQ(2) SAI2 NA I2S CKIN(2) Main PLL (PLLR output clock)<sup>(2)</sup> Main PLL (PLLR output clock) SPDIF-RX NA LSE clock **HDMI-CEC** NA HSI clock divided by 488

Table 8. Reset and Clock Controller comparison (continued)

## 2.7 RTC

The STM32F446 and STM32F429/439 lines implement the same features on the RTC, as shown in *Table 9*.

Table 9. RTC comparison

| RTC                                 | STM32F429xx/439xx        | STM32F446xx                                                 |  |  |

|-------------------------------------|--------------------------|-------------------------------------------------------------|--|--|

| Calendar in BCD                     | Yes                      | Yes                                                         |  |  |

| Calendar Sub seconds access         | Yes                      | Yes                                                         |  |  |

| Calendar synchronization on the fly | Yes                      | Yes                                                         |  |  |

| Alarm on calendar                   | 2 with subseconds        |                                                             |  |  |

| Calendar Calibration                | Calibration step: 3.81pp | ow: 8s / 16s / 32s<br>m / 1.91ppm / 0.95 ppm<br>pm +480ppm] |  |  |

| Synchronization on mains            | Yes                      | Yes                                                         |  |  |

14/24 DocID027496 Rev 1

<sup>1.</sup> Configurable clock per SAI sub-block.

<sup>2.</sup> Configurable clock per SAI block.

Table 9. RTC comparison

| RTC                         | STM32F429xx/439xx                        | STM32F446xx   |  |  |  |

|-----------------------------|------------------------------------------|---------------|--|--|--|

| Periodic wakeup             | Yes Yes                                  |               |  |  |  |

| Timestamp                   | Yes<br>Sec, Min, Hour, Date, Sub-seconds |               |  |  |  |

| RTC alternate functions pin | RTC_AF0                                  | ) → PC13      |  |  |  |

| KTC alternate functions pin | RTC_AF1 → PI8                            | RTC_AF1 → PA0 |  |  |  |

| RTC in Vbat                 | Yes                                      | Yes           |  |  |  |

## 2.8 PWR

In STM32F446 lines the PWR controller presents some differences vs. STM32F429/439 lines, as highlighted in *Table 10*, where a gray cell indicates that the feature is not available.

Table 10. PWR comparison

| PWR                     |                        | STM32F429xx/439xx             | STM32F446xx                                                                                                                                                                                                                                                                                              |

|-------------------------|------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supplies          |                        | NA                            | Independent USB transceivers supply ( $V_{DDUSB}$ ). $V_{DDUSB}$ supplies USB DP/DM pins. When internal USB PHY is used, $V_{DDUSB}$ range is from 3.0 to 3.6 V, and is completely independent from $V_{DD}$ or $V_{DDA}$ . When internal USB PHY is not used $V_{DDUSB}$ can be connected to $V_{DD}$ . |

| Power control registers | PWR_CR <sup>(1)</sup>  | NA                            | Added bits:  - PWR_CR[FMSSR]: used to Stop the Flash Interface while System is in Run mode  - PWR_CR[FMSSR]: used to force Flash into STOP or Deep Power Down mode while System is in Run mode                                                                                                           |

|                         | PWR_CSR <sup>(2)</sup> | Only one wakeup pin available | Added / modified bits:  - PWR_CSR [EWUP1] and PWR_CSR [EWUP2]: Wakeup Pin 1 and Wakeup Pin 2 Enable/Disable bits.                                                                                                                                                                                        |

- 1. See *Table 11*

- 2. See *Table 12*

The added bits in PWR\_CR and PWR\_CSR registers are shown in *Table 11* and *Table 12*, respectively: the new features are highlighted in red, while blue indicates same feature with specification change or enhancement. Reserved bits are in light gray.

Table 11. PWR\_CR register for STM32F446xx products

| 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21    | 20    | 19  | 18     | 17     | 16   |

|------|------|------|------|------|------|------|------|------|------|-------|-------|-----|--------|--------|------|

| Res. | FISSR | FMSSR | UDE | N[1:0] | ODSWEN | ODEN |

|      | •    |      |      |      |      |      |      |      |      |       |       |     |        |        |      |

| 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5     | 4     | 3   | 2      | 1      | 0    |

#### Table 12. PWR\_CSR register for STM32F446xx products

| 31   | 30     | 29   | 28   | 27   | 26   | 25   | 24    | 23    | 22   | 21   | 20   | 19   | 18     | 17      | 16    |

|------|--------|------|------|------|------|------|-------|-------|------|------|------|------|--------|---------|-------|

| Res. | Res.   | Res. | Res. | Res. | Res. | Res. | Res.  | Res.  | Res. | Res. | Res. | UDRE | Y[1:0] | ODSWRDY | ODRDY |

| 15   | 14     | 13   | 12   | 11   | 10   | 9    | 8     | 7     | 6    | 5    | 4    | 3    | 2      | 1       | 0     |

| Res. | VOSRDY | Res. | Res. | Res. | Res. | BRE  | EWUP1 | EWUP2 | Res. | Res. | Res. | BRR  | PVDO   | SBF     | WUF   |

## 2.9 U(S)ART

The STM32F446 includes the Same USART interface used in the STM32F429/439, as indicated in *Table 13*.

Table 13. USART comparison

| U(S)ART    | STM32F429xx/439xx                                                                                                                                                    | STM32F446xx          |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| UART/USART | 4 / 4                                                                                                                                                                | 4/2                  |  |  |  |

| Baudrate   | up to 4x11                                                                                                                                                           | .25 Mbit/s           |  |  |  |

| Clock      | Single clo                                                                                                                                                           | ck domain            |  |  |  |

| Data       | Word length: progra                                                                                                                                                  | mmable (8 or 9 bits) |  |  |  |

| Interrupt  | 10 interrupt sources with flags                                                                                                                                      |                      |  |  |  |

| Features   | LIN mode SPI Master IrDA SIR ENDEC block Hardware flow control (CTS/RTS Continuous communication using Multiprocessor communication Single-wire half-duplex communic | DMA                  |  |  |  |

#### 2.10 I2C

The STM32F446xx implements exactly the same features on the I2C interface (I2C1, I2C2 and I2C3) as the STM32F429xx/439xx.

#### 2.11 Audio interfaces

The STM32F429/439 and STM32F446 lines implement the same features on the SPI, apart from I2S. This is clear from *Table 14*, where a gray cell indicates that the feature is not available. The added bit in SPI\_I2SCFGR register is shown in *Table 15*, where the new feature is highlighted in red, and reserved bits are in light gray.

| Audio<br>interfaces | Description   | STM32F429xx/439xx                                                                                     | STM32F446xx                                                                                                                                                  |  |  |

|---------------------|---------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                     | Instances     | x6   x2 (SPI/I2S)                                                                                     | x4   x3 (SPI/I2S)                                                                                                                                            |  |  |

| SPI/I2S             | Features      | <ul><li>I<sup>2</sup>S Full duplex</li><li>SPI TI mode support</li><li>SPI Motorola support</li></ul> | <ul> <li>3 I²S Half duplex</li> <li>SPI TI mode support</li> <li>SPI Motorola support</li> <li>Enhanced clock source for I2S on<br/>APB1 and APB2</li> </ul> |  |  |

|                     | Modifications | NA                                                                                                    | Added bit SPI_I2SCFGR <sup>(1)</sup> [ASTREN]: allows to configure the I2S peripheral in asynchronous start mode.                                            |  |  |

|                     | Instances     | x1 (SAI)                                                                                              | x2 (SAI)                                                                                                                                                     |  |  |

| SAIs                | Features      | Clock source for each<br>SAI sub-block to target<br>independent audio<br>frequency sampling           | Internal synchronization between the two SAIs. Clock source for each SAI block to target independent audio frequency sampling.                               |  |  |

| SPDIFRx             | Instances     | NA                                                                                                    | x1 (SPIDIFRx)                                                                                                                                                |  |  |

Table 14. Audio interfaces comparison

#### Table 15. SPI\_I2SCFGR register for STM32F446xx products

| 15   | 14   | 13   | 12     | 11     | 10   | 9    | 8   | 7       | 6    | 5    | 4   | 3     | 2   | 1   | 0     |

|------|------|------|--------|--------|------|------|-----|---------|------|------|-----|-------|-----|-----|-------|

| Res. | Res. | Res. | ASTREN | I2SMOD | I2SE | 1280 | CFG | PCMSYNC | Res. | 1288 | STD | CKPOL | DAT | LEN | CHLEN |

#### 2.12 CRC

The STM32F446xx implements CRC (Cyclic redundancy check) unit calculation similarly to STM32F429xx/439xx, the main features are listed in *Table 16*.

Table 16. CRC features for STM32F429xx/439xx and STM32F446xx

| CRC      | STM32F429xx/439xx and STM32F446xx                                                                                                                                                                                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Features | Single input/output 32-bit data register CRC computation done in 4 AHB clock cycles (HCLK) for the 32-bit data size General-purpose 8-bit register (can be used for temporary storage) Uses CRC-32 (Ethernet) polynomial: 0x4C11DB7 Handles 32-bit data size |

<sup>1.</sup> See *Table 15*

## 2.13 **USB OTG**

The STM32F446xx and STM32F429xx/439xx implement similar USB peripherals, as shown in *Table 17*, where a gray cell indicates a not available feature.

Table 17. USB comparison

|               | 14516 17. 005 001                                                                                                                                           | T                                                                                                                               |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| USB           | STM32F429xx/439xx                                                                                                                                           | STM32F446xx                                                                                                                     |

|               | Universal Serial Bus Revision 2.0 Full support for the USB On-The-Go (USB OTG) USB internal connect/disconnect feature with an internal connect/disconnect. | ernal pull-up resistor on the USB D + (USB_DP) line                                                                             |

|               | NA                                                                                                                                                          | Independent $V_{DDUSB}$ power supply allowing lower $V_{DD}$ (down to 1.8 V) while using USB                                    |

|               | FS n                                                                                                                                                        | node                                                                                                                            |

| Features      | bidirectional control endpoint     IN endpoints (Bulk, Interrupt, Isochronous)     OUT endpoints (Bulk, Interrupt, Isochronous)                             | bidirectional control endpoint     IN endpoints (Bulk, Interrupt, Isochronous)     OUT endpoints (Bulk, Interrupt, Isochronous) |

|               | HS r                                                                                                                                                        | node                                                                                                                            |

|               | 6 bidirectional endpoints (including EP0) 12 Host mode channels                                                                                             |                                                                                                                                 |

|               | FS n                                                                                                                                                        | node                                                                                                                            |

| Buffer        | Management of up to 4 Tx FIFOs (1 for each IN end point) + 1 Rx FIFO                                                                                        | Management of up to 6 Tx FIFOs (1 for each IN end point) + 1 Rx FIFO                                                            |

| memory        | HS r                                                                                                                                                        | node                                                                                                                            |

|               | 4 KB to                                                                                                                                                     | tal RAM                                                                                                                         |

|               | FS n                                                                                                                                                        | node                                                                                                                            |

| Low-<br>power | USB suspend and resume                                                                                                                                      | USB suspend and resume<br>Link Power Management (LPM) support                                                                   |

| modes         | HS r                                                                                                                                                        | node                                                                                                                            |

|               | LPM not supported                                                                                                                                           | LPM supported                                                                                                                   |

|               |                                                                                                                                                             |                                                                                                                                 |

# 2.14 Digital camera interface (DCMI)

The STM32F429xx/439xx and STM32F446xx products have similar DCMI peripherals, as can be seen in *Table 18*, where a gray cell indicates that the feature is not available.

Table 18. DCMI comparison

| DCMI                                    | STM32F429xx/439xx                                             | STM32F446xx                                                                                                                                                                               |  |  |  |  |  |

|-----------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Parallel interface                      | 8-, 10-, 12-                                                  | and 14-bits                                                                                                                                                                               |  |  |  |  |  |

| Embedded synchronization                | Yes                                                           | Yes                                                                                                                                                                                       |  |  |  |  |  |

| External line and frame synchronization | Yes                                                           | Yes                                                                                                                                                                                       |  |  |  |  |  |

| Crop feature                            | Yes                                                           | Yes                                                                                                                                                                                       |  |  |  |  |  |

|                                         | 8/10, 12, 14 bits progressive vid                             | deo (monochrome or raw bayer)                                                                                                                                                             |  |  |  |  |  |

|                                         | RGB565 progressive video                                      |                                                                                                                                                                                           |  |  |  |  |  |

|                                         | YCbCr4:2:2                                                    |                                                                                                                                                                                           |  |  |  |  |  |

| Supported data formats                  | 8/10, 12, 14 bits progressive video (monochrome or raw bayer) |                                                                                                                                                                                           |  |  |  |  |  |

|                                         | NA                                                            | YCbCr – Y only (Black and White)                                                                                                                                                          |  |  |  |  |  |

|                                         | NA                                                            | Half resolution image extraction                                                                                                                                                          |  |  |  |  |  |

|                                         | Compressed JPEG                                               |                                                                                                                                                                                           |  |  |  |  |  |

| DCMI control register <sup>(1)</sup>    | NA                                                            | Added bits:  - DCMI_CR [BSM] and DCMI_CR [OEBS]: allows configuring the byte selection for capture  - DCMI_CR [LSM] and DCMI_CR [OELS]: allows configuring the line selection for capture |  |  |  |  |  |

<sup>1.</sup> See *Table 19*

The added bits in DCMI registers are shown in *Table 19*, the new features are highlighted in red, and reserved bits are in light gray.

Table 19. DCMI\_CR register for STM32F446xx products

| 31   | 30     | 29   | 28   | 27   | 26   | 25   | 24   | 23    | 22    | 21     | 20   | 19   | 18   | 17 | 16      |

|------|--------|------|------|------|------|------|------|-------|-------|--------|------|------|------|----|---------|

| Res. | Res.   | Res. | Res. | Res. | Res. | Res. | Res. | Res.  | Res.  | Res.   | OELS | LSM  | OEBS | ı  | BSM     |

| 15   | 14     | 13   | 12   | 11   | 10   | 9    | 8    | . 7   | 6     | 5      | 4    | 3    | 2    | 1  | 0       |

| Res. | ENABLE | Res. | Res. | E    | OM   | FCRC |      | VSPOL | HSPOL | PCKPOL | ESS  | JPEG | CROP | CM | CAPTURE |

## 2.15 Secure digital input/output interface (SDIO)

The STM32F429xx and STM32F446xx products implement very similar SDIO module. The key differences are listed in *Table 20*, where a gray cell indicates that the feature is not available.

Table 20. SDIO comparison

| SDIO                           | STM32F429xx/439xx                                                                                                                                                                              | STM32F446xx                                                                                                     |  |  |  |  |  |  |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Features                       | Full compliance with MultiMediaCard System Specification Version 4.2 Full compliance with SD Memory Card Specifications Version 2.0 Full compliance with SD I/O Card Specification Version 2.0 |                                                                                                                 |  |  |  |  |  |  |  |

|                                | Full support of the CE-ATA features                                                                                                                                                            | NA                                                                                                              |  |  |  |  |  |  |  |

| SDMMC registers <sup>(1)</sup> | -                                                                                                                                                                                              | CE-ATA protocol related features removed from specification (updated SDIO_STA, SDIO_ICR and SDIO_CMD registers) |  |  |  |  |  |  |  |

<sup>1.</sup> See Table 21, Table 22 and Table 23.

The added bits in DCMI registers are shown in *Table 21*, *Table 22* and *Table 23*, where the changes are highlighted in red, and reserved bits are in light gray.

Table 21. SDIO\_STA register for STM32F446xx products

| 31               | 30               | 29    | 28    | 27         | 26          | 25   | 24          | 23          | 22          | 21          | 20           | 19           | 18           | 17           | 16           |

|------------------|------------------|-------|-------|------------|-------------|------|-------------|-------------|-------------|-------------|--------------|--------------|--------------|--------------|--------------|

| Res.             | Res.             | Res.  | Res.  | Res.       | Res.        | Res. | Res.        | Res.        | SDIOIT      | RXD<br>AVL  | TXD<br>AVL   | RX<br>FIFOE  | TX<br>FIFOE  | RX<br>FIFOF  | TX<br>FIFOF  |

| 15               | 14               | 13    | 12    | 11         | 10          | 9    | 8           | 7           | 6           | 5           | 4            | 3            | 2            | 1            | 0            |

| RX<br>FIFO<br>HF | TX<br>FIFO<br>HE | RXACT | TXACT | CMD<br>ACT | DBCK<br>END | Res. | DATA<br>END | CMDS<br>ENT | CMDR<br>END | RX<br>OVERR | TXUND<br>ERR | DTIME<br>OUT | CTIME<br>OUT | DCRC<br>FAIL | CCRC<br>FAIL |

#### Table 22. SDIO\_ICR register for STM32F446xx products

| 31   | 30   | 29   | 28   | 27   | 26           | 25   | 24   | 23           | 22           | 21   | 20            | 19            | 18    | 17            | 16            |

|------|------|------|------|------|--------------|------|------|--------------|--------------|------|---------------|---------------|-------|---------------|---------------|

| Res. | Res. | Res. | Res. | Res. | Res.         | Res. | Res. | Res.         | SDIO<br>ITC  | Res. | Res.          | Res.          | Res.  | Res.          | Res.          |

| 15   | 14   | 13   | 12   | 11   | 10           | 9    | 8    | 7            | 6            | 5    | 4             | 3             | 2     | 1             | 0             |

| Res. | Res. | Res. | Res. | Res. | DBCK<br>ENDC | Res. | DATA | CMD<br>SENTC | CMD<br>RENDC | RX   | TX<br>UNDERRC | DTIME<br>OUTC | CTIME | DCRC<br>FAILC | CCRC<br>FAILC |

#### Table 23. SDIO\_CMD register for STM32F446xx products

| 31   | 30   | 29   | 28   | 27              | 26         | 25           | 24          | 23   | 22   | 21       | 20   | 19   | 18   | 17   | 16   |

|------|------|------|------|-----------------|------------|--------------|-------------|------|------|----------|------|------|------|------|------|

| Res. | Res. | Res. | Res. | Res.            | Res.       | Res.         | Res.        | Res. | Res. | Res.     | Res. | Res. | Res. | Res. | Res. |

| 15   | 14   | 13   | 12   | 11              | 10         | 9            | 8           | 7    | 6    | 5        | 4    | 3    | 2    | 1    | 0    |

| Res. | Res. | Res. | Res. | SDIO<br>Suspend | CPSM<br>EN | WAIT<br>PEND | WAIT<br>INT | WAIT | RESP | CMDINDEX |      |      |      |      |      |

20/24 DocID027496 Rev 1

## 2.16 ADC/DAC

The STM32F446 and the STM32F429/439 lines implement the very same features on the ADC and DAC peripherals.

Conclusion AN4658

# 3 Conclusion

This application note is a useful complement to datasheets and reference manuals as it provides a simple guide to migrate from an existing design based on STM32F429xx/439xx devices to one using STM32F446xx products.

AN4658 Revision history

# 4 Revision history

Table 24. Document revision history

| Date        | Revision | Changes         |

|-------------|----------|-----------------|

| 18-Mar-2015 | 1        | Initial release |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics - All rights reserved