# AN4807 Application note

# Migrating between STM32F303 and STM32F302 line products

#### Introduction

For the designers of the STM32 microcontroller applications, being able to replace easily one microcontroller type by another in the same product family is an important asset. Migrating an application between the STM32F303 and STM32F302 line products is often needed, when the product requirements grow, putting extra demands on the memory size or increasing the number of I/Os. The cost reduction objectives may also be an argument to switch to another product with less memory and peripherals.

This application note analyzes the steps required to migrate from an existing STM32F302 or STM32F303 based design to any other STM32 device in the same line. It compares the STM32F302 and STM32F303 line products and highlights the differences between all the devices within the same line (STM32F303 or STM32F302).

The STM32F302 and STM32F303 line products are compatible, but few differences exist that could have an impact on the migration. All the most important information is in this application note.

To fully benefit from this application note, the user should be familiar with the STM32F3 microcontroller documentation available on <a href="https://www.st.com">www.st.com</a>:

- STM32F302 reference manual (RM0365)

- STM32F303 reference manual (RM0316)

- STM32F302x6/8 datasheet

- STM32F302xB/C datasheet

- STM32F302xD/E datasheet

- STM32F303x6/8 datasheet

- STM32F303xB/C datasheet

- STM32F303xD/E datasheet

October 2016 DocID028820 Rev 2 1/27

AN4807 Contents

# **Contents**

| 1 | STM  | 32F302   | line product differences          | 5  |

|---|------|----------|-----------------------------------|----|

|   | 1.1  | STM32    | 2F302 line product overview       | 5  |

|   | 1.2  | STM32    | 2F302 line product differences    | 7  |

|   |      | 1.2.1    | Clock tree                        | 7  |

|   |      | 1.2.2    | Clock out capability              | 8  |

|   |      | 1.2.3    | Embedded SRAM                     | 8  |

|   |      | 1.2.4    | SYSCFG                            | 8  |

|   |      | 1.2.5    | I/O and pinout                    | 9  |

|   |      | 1.2.6    | Analog to Digital Converter (ADC) | 10 |

|   |      | 1.2.7    | Digital to Analog Converter (DAC) | 11 |

|   |      | 1.2.8    | Comparators                       | 11 |

|   |      | 1.2.9    | Operational amplifier             | 12 |

|   |      | 1.2.10   | Timer                             | 12 |

|   |      | 1.2.11   | USART/UART                        | 13 |

|   |      | 1.2.12   | USB                               | 14 |

| 2 | STM  | 32F303   | line product differences          | 15 |

|   | 2.1  | STM32    | 2F303 line product overview       | 15 |

|   | 2.2  | STM32    | 2F303 line product differences    | 18 |

|   |      | 2.2.1    | Clock tree                        | 18 |

|   |      | 2.2.2    | Clock out capability              | 18 |

|   |      | 2.2.3    | Embedded SRAM                     | 19 |

|   |      | 2.2.4    | SYSCFG                            | 19 |

|   |      | 2.2.5    | I/O and pinout                    | 20 |

|   |      | 2.2.6    | Analog to Digital Converter (ADC) | 21 |

|   |      | 2.2.7    | Digital to Analog Converter (DAC) | 22 |

|   |      | 2.2.8    | Comparators                       | 22 |

|   |      | 2.2.9    | Operational amplifier             | 23 |

|   |      | 2.2.10   | Timer                             | 23 |

|   |      | 2.2.11   | USART/UART                        | 24 |

|   |      | 2.2.12   | USB                               | 25 |

| 3 | Revi | sion his | story                             | 26 |

|   |      |          |                                   |    |

List of tables AN4807

# List of tables

| Table 1.  | STM32F302x6/8/B/C/D/E peripherals     | 5  |

|-----------|---------------------------------------|----|

| Table 2.  | PLL clock source selection            | 7  |

| Table 3.  | Alternate functions added             | 10 |

| Table 4.  | ADC channel mapping differences       | 10 |

| Table 5.  | DAC external triggers                 | 11 |

| Table 6.  | Timers available for STM32F302 line   | 12 |

| Table 7.  | Interconnection of timer triggers     | 12 |

| Table 8.  | USART/UART discrepancies              | 13 |

| Table 9.  | STM32F302 line USB Implementation     | 14 |

| Table 10. | Peripheral overview                   | 15 |

| Table 11. | PLL clock source selection            | 18 |

| Table 12. | Embedded SRAM for the STM32F303 line  | 19 |

| Table 13. | Alternate functions added             | 21 |

| Table 14. | ADC channel mapping differences       | 21 |

| Table 15. | DAC external triggers                 | 22 |

| Table 16. | Timers that can be clocked at 144 MHz | 23 |

| Table 17. | Interconnection of timer triggers     | 23 |

| Table 18. | USART/UART discrepancies              | 24 |

| Table 19. | USB RAM management                    | 25 |

| Table 20  | Document revision history             | 26 |

AN4807 List of figures

# List of figures

| Figure 1. | STM32F302xB/C clock out capability       | . 8 |

|-----------|------------------------------------------|-----|

|           | STM32F302x6/8/D/E clock out capability   |     |

|           | STM32F302xx LQFP64 pinout discrepancies  |     |

|           | STM32F302xx LQFP100 pinout discrepancies |     |

| Figure 5. | STM32F303xB/C clock out capability       | 19  |

| Figure 6. | STM32F303x6/8/D/E clock out capability   | 19  |

| Figure 7. | STM32F303xx LQFP64 pinout discrepancies  | 20  |

| Figure 8. | STM32F303xx LQFP100 pinout discrepancies | 20  |

# 1 STM32F302 line product differences

# 1.1 STM32F302 line product overview

*Table 1* provides an overview of the STM32F302x6/8/B/C/D/E peripherals.

Table 1. STM32F302x6/8/B/C/D/E peripherals<sup>(1)</sup>

| STM32F302 device                         |                    | STM32F302x6/8              | STM32F302xB/C                           | STM32F302xD/E                           |

|------------------------------------------|--------------------|----------------------------|-----------------------------------------|-----------------------------------------|

|                                          |                    | System                     |                                         |                                         |

| Embedded SR/                             | AM size            | Up to 16 Kbytes            | Up to 40 Kbytes                         | Up to 64 Kbytes                         |

| SRAM parity                              | check              | N/A                        | Implemented only on the first 16 Kbytes | Implemented only on the first 32 Kbytes |

| MPU                                      |                    | N/A                        | ✓                                       | ✓                                       |

| Flash memor                              | y size             | Up to 64 Kbytes            | Up to 256 Kbytes                        | Up to 512 Kbytes                        |

| Direct memory access                     | -                  | 7-channel DMA controller   | 12-channel DMA controller               | 12-channel DMA controller               |

| Direct memory access (DMA)               | GP-DMA1            | ✓                          | ✓                                       | ✓                                       |

|                                          | GP-DMA2            | N/A                        | ✓                                       | <b>√</b>                                |

| FMC                                      |                    | N/A                        | N/A                                     | ✓                                       |

| GPIO                                     |                    | Up to 51 fast I/Os         | Up to 87 fast I/Os                      | Up to 115 fast I/Os                     |

|                                          |                    | Analog                     |                                         |                                         |

|                                          | -                  | 1                          | 2                                       | 2                                       |

| Analog to digital converter (ADC)        | Number of channels | Up to 15 channels          | Up to 17 channels                       | Up to 18 channels                       |

| 5MSPS                                    | ADC1               | ✓                          | ✓                                       | ✓                                       |

|                                          | ADC2               | -                          | ✓                                       | ✓                                       |

|                                          | -                  | 1                          | 2                                       | 2                                       |

| Available operational amplifiers (OPAMP) | OPAMP1             | -                          | ✓                                       | ✓                                       |

| (0.7)                                    | OPAMP2             | ✓                          | ✓                                       | ✓                                       |

| Digital to analog converter (DAC)        | -                  | 1 x 12-bit DAC channel     | 1 x 12-bit DAC<br>channel               | 1 x 12-bit DAC<br>channel               |

|                                          | -                  | 3 x ultra-fast comparators | 4 x fast comparators                    | 4 x ultra-fast comparators              |

|                                          | COMP1              | -                          | ✓                                       | ✓                                       |

| Comparators (COMP)                       | COMP2              | ✓                          | ✓                                       | ✓                                       |

|                                          | COMP4              | ✓                          | ✓                                       | ✓                                       |

|                                          | COMP6              | ✓                          | ✓                                       | ✓                                       |

Table 1. STM32F302x6/8/B/C/D/E peripherals<sup>(1)</sup> (continued)

| STM32F302 c                               |             | STM32F302x6/8                                                                        | STM32F302xB/C                                                                              | STM32F302xD/E                                                                              |

|-------------------------------------------|-------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Touch Sens                                | sing        | Up to 18 capacitive sensing channels supporting touch key, linear and rotary sensors | Up to 24 capacitive sensing channels supporting touch key, linear and rotary touch sensors | Up to 24 capacitive sensing channels supporting touch key, linear and rotary touch sensors |

|                                           |             | Communication                                                                        | ,                                                                                          |                                                                                            |

|                                           | -           | 3 x I <sup>2</sup> Cs                                                                | 2 x I <sup>2</sup> Cs                                                                      | 3 x I <sup>2</sup> Cs                                                                      |

| IOC Aveilable                             | I2C1        | ✓                                                                                    | ✓                                                                                          | ✓                                                                                          |

| I2C Available                             | 12C2        | ✓                                                                                    | ✓                                                                                          | ✓                                                                                          |

|                                           | I2C3        | ✓                                                                                    | -                                                                                          | ✓                                                                                          |

|                                           | -           | 3 x U(S)ARTs                                                                         | 5 x U(S)ARTs                                                                               | 5 x U(S)ARTs                                                                               |

|                                           | USART1      | ✓                                                                                    | ✓                                                                                          | ✓                                                                                          |

| USART/UART                                | USART2      | ✓                                                                                    | ✓                                                                                          | ✓                                                                                          |

| Available                                 | USART3      | ✓                                                                                    | ✓                                                                                          | ✓                                                                                          |

|                                           | UART4       | -                                                                                    | ✓                                                                                          | ✓                                                                                          |

|                                           | UART5       | -                                                                                    | ✓                                                                                          | ✓                                                                                          |

|                                           | -           | 2 x SPIs/2 x I2Ss                                                                    | 3 x SPIs/2 x I2Ss                                                                          | 4 x SPIs/2 x I2Ss                                                                          |

|                                           | SPI1        | -                                                                                    | ✓                                                                                          | ✓                                                                                          |

| SPI Available                             | SPI2/I2S2   | ✓                                                                                    | ✓                                                                                          | ✓                                                                                          |

|                                           | SPI3/I2S3   | ✓                                                                                    | ✓                                                                                          | ✓                                                                                          |

|                                           | SPI4        | -                                                                                    | -                                                                                          | ✓                                                                                          |

| USB 2.0 full-speed                        | d interface | ✓ with LPM support                                                                   | ✓                                                                                          | ✓with LPM support                                                                          |

| CAN 2.0I                                  | В           | ✓                                                                                    | ✓                                                                                          | ✓                                                                                          |

| Infrared trans                            | mitter      | ✓                                                                                    | ✓                                                                                          | ✓                                                                                          |

|                                           |             | Timers                                                                               | ,                                                                                          |                                                                                            |

|                                           | -           | Up to 9 timers                                                                       | Up to 11 timers                                                                            | Up to 11 timers                                                                            |

|                                           | TIMER1      | ✓                                                                                    | ✓                                                                                          | ✓                                                                                          |

|                                           | TIMER2      | ✓                                                                                    | ✓                                                                                          | ✓                                                                                          |

| General purpose/motor control/basic timer | TIMER3      | -                                                                                    | ✓                                                                                          | ✓                                                                                          |

| Some of basic time!                       | TIMER4      | -                                                                                    | ✓                                                                                          | <b>✓</b>                                                                                   |

|                                           | TIMER6      | ✓                                                                                    | ✓                                                                                          | <b>✓</b>                                                                                   |

|                                           | TIMER15     | ✓                                                                                    | <b>✓</b>                                                                                   | ✓                                                                                          |

| STM32F302 device                          |                                                    | STM32F302x6/8                     | STM32F302xB/C                                   | STM32F302xD/E                                   |  |  |

|-------------------------------------------|----------------------------------------------------|-----------------------------------|-------------------------------------------------|-------------------------------------------------|--|--|

|                                           | TIMER16                                            | ✓                                 | ✓                                               | ✓                                               |  |  |

|                                           | TIMER17                                            | ✓                                 | ✓                                               | ✓                                               |  |  |

| General purpose/motor control/basic timer | SysTick timer<br>24-bit down-<br>counter           | <b>√</b>                          | ✓                                               | <b>✓</b>                                        |  |  |

|                                           | Watchdog 2 x watchdog timers (independent, window) |                                   | 2 x watchdog timers<br>(independent,<br>window) | 2 x watchdog timers<br>(independent,<br>window) |  |  |

| RTC -                                     |                                                    | ✓                                 | ✓                                               | ✓                                               |  |  |

| Packages                                  |                                                    |                                   |                                                 |                                                 |  |  |

| Available pac                             | kages                                              | WLCSP49<br>UFQFPN32<br>LQFP 64/48 | LQFP 100/64/48<br>WLCSP100                      | LQFP 144/100/64<br>UFBGA100<br>WLCSP100         |  |  |

Table 1. STM32F302x6/8/B/C/D/E peripherals<sup>(1)</sup> (continued)

### 1.2 STM32F302 line product differences

#### 1.2.1 Clock tree

When the HSI is selected as the PLL clock source, the maximum CPU clock can be reached:

- On the STM32F302x6/8/B/C devices, there is one bit PLLSRC (bit 16 in the RCC\_CFGR register) dedicated to select the PLL clock source; and when the HSI is selected as the PLL clock source, the maximum CPU frequency that can be reached is 64 MHz.

- On the STM32F302xD/E devices, two bits (bit 15 and 16 in the RCC\_CFGR register)

are used in order to select the PLL clock source. The purpose is to add a configuration

where the HSI is selected as the PLL clock source and 72 MHz CPU clock is reached.

Bit 15

Bit 16

Description

0

0

HSI/2 used as PREDIV1 entry and PREDIV1 forced to div by 2

0

1

HSI used as PREDIV1 entry (only on STM32F302xD/E)

1

0

HSE used as PREDIV1 entry

1

1

Reserved

Table 2. PLL clock source selection

<sup>✓ =</sup> supported.

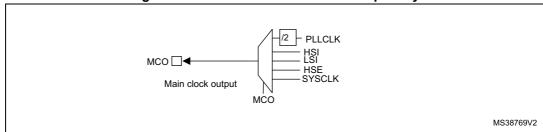

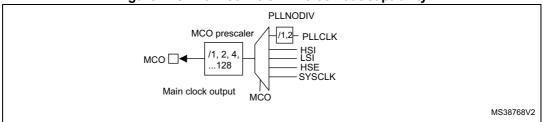

#### 1.2.2 Clock out capability

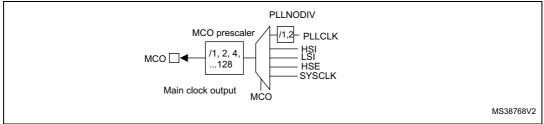

Compared to the STM32F302xB/C devices, on the STM32F302x6/8/D/E devices:

- One PLLNODIV bit in the RCC\_CFGR register is added, its purpose is to control the divider bypass for a PLL clock input to the MCO.

- The MCO frequency can be reduced by a configurable divider, controlled by the MCOPRE [2..0] bits in the RCC CFGR register.

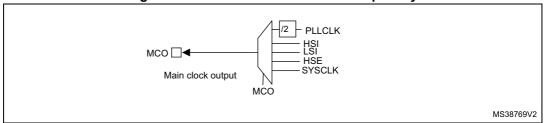

Figure 1. STM32F302xB/C clock out capability

Figure 2. STM32F302x6/8/D/E clock out capability

#### 1.2.3 Embedded SRAM

The SRAM in the STM32F302x6/8 devices does not support the hardware parity check; however the SRAM in the STM32F302xB/C/D/E devices supports the hardware parity check which is implemented on the first 16 Kbytes in the STM32F302xB/C devices and implemented on the first 32 Kbytes on the STM32F302xD/E devices.

#### 1.2.4 SYSCFG

In the SYSCFG configuration register2 (SYSCFG\_CFGR2): PVD\_LOCK, SRAM\_PARITY\_LOCK and LOCKUP\_LOCK bits are reset only by system reset on the STM32F302x6/8/D/E devices.

However on the STM32F302xB/C devices, these bits can be reset also by a reset coming from RCC (using the SYSCFGRST bit).

#### 1.2.5 I/O and pinout

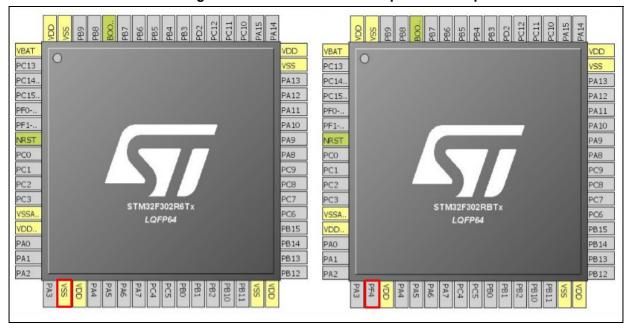

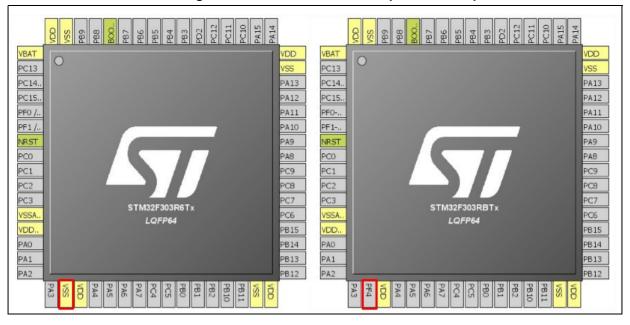

The STM32F302x6/8/B/C/D/E devices are pinout compatible except for the fact that PF4 in the STM32F302xB/C devices, is VSS in the STM32F302x6/8/D/E devices. Refer to *Figure 3* and *Figure 4*:

Figure 3. STM32F302xx LQFP64 pinout discrepancies

The GPIO LOCK feature is only available on Port A, B and D for the STM32F302xB/C devices. This feature is implemented for all GPIOs on the STM32F302x6/8/D/E devices.

*Table 3* summarizes all added alternate functions in the STM32F302x6/8/D/E devices compared to the STM32F302xB/C devices.

Table 3. Alternate functions added

| I/O and alternate function | Added function       |

|----------------------------|----------------------|

| PB8 (AF7)                  | USART3_Rx            |

| PB9 (AF7)                  | USART3_Tx            |

| PC0 (AF2)                  | TIM1_CH1             |

| PC1 (AF2)                  | TIM1_CH2             |

| PC2 (AF2)                  | TIM1_CH3             |

| PC3 (AF2)                  | TIM1_CH4             |

| PC4 (AF2)                  | TIM1_ETR             |

| PC5 (AF2)                  | TIM15_BKIN           |

| PA12 (AF5)                 | I2S_CKIN             |

| PF0 (AF5)                  | SPI2_NSS/I2S2_WS     |

| PF1 (AF5)                  | SPI2_SCK/I2S2_CK     |

| PA10 (AF5)                 | SPI2_MISO/I2S2ext_SD |

| PA11 (AF5)                 | SPI2_MOSI/I2S2_SD    |

| PB5 (AF8)                  | I2C3_SDA             |

| PA8 (AF3)                  | I2C3_SCL             |

| PC9 (AF3)                  | I2C3_SDA             |

| PA9 (AF2)                  | I2C3_SMBAL           |

Note: The FMC is available only on the STM32F302xD/E devices. The corresponding alternate functions are not mentioned in Table 3.

#### 1.2.6 Analog to Digital Converter (ADC)

Table 4 shows the mapping differences of ADC channels on the STM32F302 line products.

Table 4. ADC channel mapping differences

| I/O | STM32F302x6/8 | STM32F302xB/C | STM32F302xD/E |

|-----|---------------|---------------|---------------|

| PA4 | ADC1_IN5      | ADC2_IN1      | ADC2_IN1      |

| PA5 | -             | ADC2_IN2      | ADC2_IN2      |

| PC4 | -             | ADC2_IN5      | ADC2_IN5      |

| PC5 | -             | ADC2_IN11     | ADC2_IN11     |

| PA6 | ADC1_IN10     | ADC2_IN3      | ADC2_IN3      |

| PB0 | ADC1_IN11     | -             | -             |

| PB1 | ADC1_IN12     | -             | -             |

| PB2 | -             | ADC2_IN12     | ADC2_IN12     |

Table 4. ADC channel mapping differences (continued)

| 11 0 , , |               |               |               |  |  |  |  |  |

|----------|---------------|---------------|---------------|--|--|--|--|--|

| I/O      | STM32F302x6/8 | STM32F302xB/C | STM32F302xD/E |  |  |  |  |  |

| PB11     | ADC1_IN14     | -             | ADC12_IN14    |  |  |  |  |  |

| PB13     | ADC1_IN13     | -             | -             |  |  |  |  |  |

| PA7      | ADC1_IN15     | ADC2_IN4      | ADC2_IN4      |  |  |  |  |  |

#### 1.2.7 Digital to Analog Converter (DAC)

Table 5 lists the DAC external triggers.

Table 5. DAC external triggers

| TSEL control bits |       |   | Devices            |               |  |  |

|-------------------|-------|---|--------------------|---------------|--|--|

| 2                 | 2 1 0 |   | STM32F302xB/C/D/E  | STM32F302x6/8 |  |  |

| 0                 | 0     | 0 | TIM6               | TRGO          |  |  |

| 0                 | 0     | 1 | TIM3_TRGO (1)      | Reserved      |  |  |

| 0                 | 1     | 0 | Reserved           |               |  |  |

| 0                 | 1     | 1 | TIM15_TRGO         |               |  |  |

| 1                 | 0     | 0 | TIM2               | TIM2_TRGO     |  |  |

| 1                 | 0     | 1 | TIM4_TRGO Reserved |               |  |  |

| 1                 | 1     | 0 | EXTI_9             |               |  |  |

| 1                 | 1     | 1 | SWTRIGx            |               |  |  |

<sup>1.</sup> The DAC1\_TRIG\_RMP bit in the SYSCFG\_CFGR1 register needs to be set by software.

#### 1.2.8 Comparators

The STM32F302x6/8/D/E devices embed ultra-fast comparators while the STM32F302xB/C devices embed fast comparators.

Compared to the STM32F302xB/C devices, the comparators on the STM32F302x6/8/D/E devices:

- Do not support programmable speed/consumption mode: High speed mode only

- Do not support the hysteresis feature

- Have only one VINP input:

- COMP2 INP: PA7

- COMP4\_INP: PB0

- COMP6 INP: PB11

- Do not have COMP2\_OUT on PA7

- Do not support the window mode

On the STM32F302x6/8/D/E devices, the comparators registers are reset only by system reset. However, on the STM32F302xB/C devices, they can be reset also by a reset from the RCC (using the SYSCFGRST bit).

### 1.2.9 Operational amplifier

The OPAMP register is reset only by system reset for both STM32F302x6/8/D/E and STM32F302xB/C devices. However, on the STM32F302xB/C devices, this register can be reset also by a reset from the RCC (using the SYSCFGRST bit).

#### 1.2.10 Timer

*Table 6* lists all the timers that can be clocked at 144 MHz in each device of the STM32F302 line.

Table 6. Timers available for STM32F302 line

| Timers can be clocked at 144MHz <sup>(1)</sup> |               |               |               |  |  |  |  |

|------------------------------------------------|---------------|---------------|---------------|--|--|--|--|

|                                                | STM32F302x6/8 | STM32F302xB/C | STM32F302xD/E |  |  |  |  |

| TIMER1                                         | ✓             | ✓             | ✓             |  |  |  |  |

| TIMER2                                         | -             | -             | ✓             |  |  |  |  |

| TIMER3                                         | -             | -             | ✓             |  |  |  |  |

| TIMER4                                         | -             | -             | ✓             |  |  |  |  |

| TIMER6                                         | -             | -             | -             |  |  |  |  |

| TIMER15                                        | ✓             | -             | ✓             |  |  |  |  |

| TIMER16                                        | ✓             | -             | ✓             |  |  |  |  |

| TIMER17                                        | ✓             | -             | ✓             |  |  |  |  |

<sup>✓=</sup>supported.

Table 7 summarizes the interconnection of timer triggers.

Table 7. Interconnection of timer triggers

| Slave timer | Product           | ITR0 | ITR1     | ITR2     | ITR3              |

|-------------|-------------------|------|----------|----------|-------------------|

| 1           | STM32F302xB/C/D/E | 15   | 2        | 3        | 4 or 17           |

| '           | STM32F302x6/8     | 15   | 2        | Reserved | 17 <sup>(1)</sup> |

| 2           | STM32F302xB/C/D/E | 1    | 8        | 3        | 4                 |

| 2           | STM32F302x6/8     | 1    | Reserved | Reserved | Reserved          |

| 3           | STM32F302xB/C/D/E | 1    | 2        | 15       | 4                 |

| 4           | STM32F302xB/C/D/E | 1    | 2        | 3        | 8                 |

| 15          | STM32F302xB/C/D/E | 2    | 3        | 16       | 17                |

| 15          | STM32F302x6/8     | 2    | Reserved | 16       | 17                |

<sup>1.</sup> The TIM1\_ITR3\_RMP bit in the SYSCFG\_CFGR1 register needs to be set by software.

#### 1.2.11 USART/UART

*Table 8* highlights the differences between the USART/UART available on the STM32F302 line.

Table 8. USART/UART discrepancies(1)

|                                                   | STM32F       | 302x6/8           | ST                           | M32F302xE    | 3/C      | ST                           | M32F302x      | )/E      |

|---------------------------------------------------|--------------|-------------------|------------------------------|--------------|----------|------------------------------|---------------|----------|

| USART modes/<br>features                          | USART1       | USART2/<br>USART3 | USART1/<br>USART2/<br>USART3 | UART4        | UART5    | USART1/<br>USART2/<br>USART3 | UART4         | UART5    |

| Hardware flow control for modem                   | ✓            | ✓                 | ✓                            | -            | -        | ✓                            | -             | -        |

| Continuous communication using DMA                | <b>√</b>     | <b>√</b>          | <b>√</b>                     | ✓            | -        | <b>✓</b>                     | ✓             | -        |

| Multiprocessor communication                      | ✓            | ✓                 | ✓                            | ✓            | ✓        | <b>√</b>                     | ✓             | ✓        |

| Synchronous mode                                  | ✓            | ✓                 | ✓                            | -            | -        | <b>√</b>                     | -             | -        |

| Smartcard mode                                    | <b>√</b> (3) | -                 | <b>√</b> (2)(3)              | -            | -        | <b>√</b> (4)                 | -             | -        |

| Single-wire half-<br>duplex<br>communication      | <b>√</b>     | <b>√</b>          | <b>√</b>                     | ✓            | <b>√</b> | <b>✓</b>                     | ✓             | <b>√</b> |

| IrDA SIR ENDEC<br>block                           | ✓            | -                 | <b>√</b>                     | ✓            | ✓        | ✓                            | ✓             | <b>√</b> |

| LIN mode                                          | ✓            | -                 | ✓                            | ✓            | ✓        | ✓                            | ✓             | ✓        |

| Dual clock domain<br>and wakeup from<br>Stop mode | <b>√</b>     | -                 | <b>√</b>                     | ✓            | ✓        | <b>✓</b>                     | ✓             | ✓        |

| Receiver timeout interrupt                        | ✓            | -                 | ✓                            | ✓            | ✓        | <b>√</b>                     | ✓             | <b>√</b> |

| Modbus communication                              | ✓            | -                 | <b>✓</b>                     | ✓            | ✓        | <b>√</b>                     | ✓             | <b>√</b> |

| Auto baud rate detection                          | ✓            | -                 | ✓                            | -            | -        | <b>√</b>                     | -             | -        |

| Driver Enable                                     | ✓            | ✓                 | ✓                            | -            | -        | ✓                            | -             | -        |

| USART data<br>length                              | 7, 8 an      | d 9 bits          |                              | 8 and 9 bits |          | 7                            | , 8 and 9 bit | S        |

<sup>✓=</sup>supported.

<sup>2.</sup> SCLK output is disabled when UE bit = 0.

<sup>3.</sup> With the following limitation for the STM32F302xB/C device: If the USART is used in the Smartcard mode and the card cannot use the default communication parameters after Answer to Reset and does not support a clock stop, it is not possible to use SCLK to clock the card. This is due to the fact that the USART and its clock output must be disabled while reprogramming some of the parameters.

<sup>4.</sup> SCLK is always available when CLKEN = 1, regardless of the UE bit value.

#### 1.2.12 USB

On the STM32F302x6/8/D/E devices, the USB peripheral supports the LPM.

Note that for the STM32F302xB/C devices, the USB\_DM and USB\_DP are mapped on AF14 of PA11 and PA12, while on the STM32F302x6/8/D/E devices, there is no need to configure AF since those inputs are directly connected to GPIO, when the USB is enabled.

On the STM32F302x6/8/D/E devices, there are 768 bytes dedicated SRAM for the USB plus 256 bytes shared SRAM with the CAN. When the CAN is disabled, the whole 1 Kbyte can be used for the USB.

Consequently, the USB SRAM management is different between the STM32F302xB/C and the STM32F302x6/8/D/E devices.

Table 9. STM32F302 line USB Implementation<sup>(1)</sup>

| USB features                                      | STM32F302x6/8/D/E         | STM32F302xB/C            |

|---------------------------------------------------|---------------------------|--------------------------|

| Number of endpoints                               | 8                         | 8                        |

| Size of dedicated packet buffer memory SRAM       | 1024 bytes <sup>(2)</sup> | 512 bytes <sup>(3)</sup> |

| Dedicated packet buffer memory SRAM access scheme | 2 x 16 bits / word        | 1 x 16 bits / word       |

| USB 2.0 Link Power management (LPM) support       | ✓                         | -                        |

<sup>1. ✓ =</sup> supported.

<sup>2.</sup> When the CAN peripheral clock is enabled in the RCC\_APB1ENR register, only the first 768 bytes are available to the USB while the last bytes are used by the CAN.

<sup>3.</sup> The 512 bytes are totally available to the USB; nothing is shared with the CAN.

# 2 STM32F303 line product differences

## 2.1 STM32F303 line product overview

*Table 10* provides an overview of the STM32F303x6/8/B/C/D/E peripherals.

Table 10. Peripheral overview<sup>(1)</sup>

| STM32F303 line    |                       |                                             |                                                                             |                                                                       |  |  |  |

|-------------------|-----------------------|---------------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|

| Devi              | ice                   | STM32F303x6/8 STM32F303xB/C                 |                                                                             | STM32F303xD/E                                                         |  |  |  |

|                   | System                |                                             |                                                                             |                                                                       |  |  |  |

|                   | Size                  | Up to 12 Kbytes of SRAM                     | Up to 40 Kbytes                                                             | Up to 64 Kbytes                                                       |  |  |  |

| Embedded          | CCM-SRAM<br>size      | 4 Kbytes                                    | 8 Kbytes                                                                    | 16 Kbytes                                                             |  |  |  |

| SRAM              | Parity check          | Implemented on the whole SRAM and CCM SRAM. | Implemented on the first<br>16 Kbytes of SRAM and<br>on the whole CCM SRAM. | Implemented on the first 32 Kbytes of SRAM and on the whole CCM SRAM. |  |  |  |

| MPU               | -                     | N/A                                         | ✓                                                                           | ✓                                                                     |  |  |  |

| Flash memory size | -                     | Up to 64 Kbytes                             | Up to 256 Kbytes                                                            | Up to 512 Kbytes                                                      |  |  |  |

| Direct memory     | -                     | 7-channel DMA controller                    | 12-channel DMA controller                                                   | 12-channel DMA controller                                             |  |  |  |

| access (DMA)      | GP-DMA1               | ✓                                           | ✓                                                                           | ✓                                                                     |  |  |  |

|                   | GP-DMA2               | N/A                                         | ✓                                                                           | ✓                                                                     |  |  |  |

| FMC               | -                     | N/A                                         | N/A                                                                         | ✓                                                                     |  |  |  |

| GPI               | 0                     | Up to 51 fast I/Os Up to 87 fast I/Os       |                                                                             | Up to 115 fast I/Os                                                   |  |  |  |

|                   |                       | Analo                                       | og                                                                          |                                                                       |  |  |  |

|                   | ı                     | 2                                           | 4                                                                           | 4                                                                     |  |  |  |

| Analog to         | Number of<br>channels | Up to 21 channels                           | Up to 39 channels                                                           | Up to 40 channels                                                     |  |  |  |

| digital converter | ADC1                  | ✓                                           | ✓                                                                           | ✓                                                                     |  |  |  |

| (ADC)             | ADC2                  | ✓                                           | ✓                                                                           | ✓                                                                     |  |  |  |

| 5MSPS             | ADC3                  | N/A                                         | ✓                                                                           | ✓                                                                     |  |  |  |

|                   | ADC4                  | N/A                                         | ✓                                                                           | ✓                                                                     |  |  |  |

Table 10. Peripheral overview<sup>(1)</sup> (continued)

|                    | STM32F303 line |                                                                                                         |                                                                                                        |                                                                                            |  |  |

|--------------------|----------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Devi               | ice            | STM32F303x6/8                                                                                           | STM32F303xB/C                                                                                          | STM32F303xD/E                                                                              |  |  |

|                    | -              | 3 x ultra-fast comparators                                                                              | 7 x fast comparators                                                                                   | 7 x ultra-fast comparators                                                                 |  |  |

| Comparators        | COMP1          | N/A                                                                                                     | ✓                                                                                                      | ✓                                                                                          |  |  |

|                    | COMP2          | ✓                                                                                                       | ✓                                                                                                      | ✓                                                                                          |  |  |

|                    | COMP3          | N/A                                                                                                     | ✓                                                                                                      | ✓                                                                                          |  |  |

| (COMP)             | COMP4          | ✓                                                                                                       | ✓                                                                                                      | ✓                                                                                          |  |  |

|                    | COMP5          | N/A                                                                                                     | ✓                                                                                                      | ✓                                                                                          |  |  |

|                    | COMP6          | ✓                                                                                                       | ✓                                                                                                      | ✓                                                                                          |  |  |

|                    | COMP7          | N/A                                                                                                     | ✓                                                                                                      | ✓                                                                                          |  |  |

|                    | -              | 1                                                                                                       | 4                                                                                                      | 4                                                                                          |  |  |

| Available          | OPAMP1         | N/A                                                                                                     | ✓                                                                                                      | ✓                                                                                          |  |  |

| operational        | OPAMP2         | ✓                                                                                                       | ✓                                                                                                      | ✓                                                                                          |  |  |

| amplifiers         | OPAMP3         | N/A                                                                                                     | ✓                                                                                                      | ✓                                                                                          |  |  |

|                    | OPAMP4         | N/A                                                                                                     | ✓                                                                                                      | ✓                                                                                          |  |  |

|                    | -              | 3 x 12-bit DAC channels                                                                                 | 2 x 12-bit DAC channels                                                                                | 2 x 12-bit DAC channels                                                                    |  |  |

| Digital to analog  | DAC1_CH1       | ✓                                                                                                       | ✓                                                                                                      | ✓                                                                                          |  |  |

| converter<br>(DAC) | DAC1_CH2       | ✓                                                                                                       | ✓                                                                                                      | ✓                                                                                          |  |  |

| (DAO)              | DAC2_CH1       | ✓                                                                                                       | N/A                                                                                                    | N/A                                                                                        |  |  |

| Touch Sensing      |                | Up to 18 capacitive<br>sensing channels<br>supporting touch keys,<br>linear and rotary touch<br>sensors | Up to 24 capacitive<br>sensing channels<br>supporting<br>touch key, linear and<br>rotary touch sensors | Up to 24 capacitive sensing channels supporting touch key, linear and rotary touch sensors |  |  |

|                    |                | Communi                                                                                                 |                                                                                                        |                                                                                            |  |  |

|                    | -              | 1 x I <sup>2</sup> C                                                                                    | 2 x I <sup>2</sup> Cs                                                                                  | 3 x I <sup>2</sup> Cs                                                                      |  |  |

| I2C                | I2C1           | ✓                                                                                                       | ✓                                                                                                      | ✓                                                                                          |  |  |

| 120                | I2C2           | N/A                                                                                                     | ✓                                                                                                      | ✓                                                                                          |  |  |

|                    | I2C3           | N/A                                                                                                     | ✓                                                                                                      | ✓                                                                                          |  |  |

Table 10. Peripheral overview<sup>(1)</sup> (continued)

|                         |                | STM32F3                 | 03 line                 |                         |

|-------------------------|----------------|-------------------------|-------------------------|-------------------------|

| Devi                    | ce             | STM32F303x6/8           | STM32F303xB/C           | STM32F303xD/E           |

|                         | -              | 3 x U(S)ARTs            | 5 x U(S)ARTs            | 5 x U(S)ARTs            |

|                         | USART1         | ✓                       | ✓                       | ✓                       |

|                         | USART2         | ✓                       | ✓                       | ✓                       |

| USART/UART              | USART3         | ✓                       | ✓                       | ✓                       |

|                         | UART4          | N/A                     | ✓                       | ✓                       |

|                         | UART5          | N/A                     | ✓                       | ✓                       |

|                         | -              | 1 x SPI                 | 3 x SPIs/ 2 x I2Ss      | 4 x SPIs/ 2 x I2Ss      |

|                         | SPI1           | ✓                       | ✓                       | ✓                       |

| SPI available           | SPI2/I2S2      | N/A                     | ✓                       | ✓                       |

|                         | SPI3/I2S3      | N/A                     | ✓                       | ✓                       |

|                         | SPI4           | N/A                     | N/A                     | ✓                       |

| USB 2.0 ft              | ıll speed      | N/A                     | ✓                       | ✓ with LPM support      |

| CAN interface (         | (2.0 B Active) | ✓                       | ✓                       | ✓                       |

| Infrared tra            | nsmitter       | ✓                       | ✓                       | ✓                       |

|                         |                | Time                    | rs                      |                         |

|                         | Number         | Up to 11 timers         | Up to 13 timers         | Up to 14 timers         |

|                         | TIMER1         | ✓                       | ✓                       | ✓                       |

|                         | TIMER2         | ✓                       | ✓                       | ✓                       |

|                         | TIMER3         | ✓                       | ✓                       | ✓                       |

|                         | TIMER4         | N/A                     | ✓                       | ✓                       |

| General purpose/motor   | TIMER6         | ✓                       | ✓                       | ✓                       |

| control/basic<br>timers | TIMER7         | ✓                       | ✓                       | ✓                       |

| umers                   | TIMER8         | N/A                     | ✓                       | ✓                       |

|                         | TIMER15        | ✓                       | ✓                       | ✓                       |

|                         | TIMER16        | ✓                       | ✓                       | ✓                       |

|                         | TIMER17        | ✓                       | ✓                       | ✓                       |

|                         | TIMER20        | N/A                     | N/A                     | ✓                       |

| SysTick<br>24-bit dowr  |                | ✓                       | ✓                       | ✓                       |

| Watchdog                | g timers       | 2 (independent, window) | 2 (independent, window) | 2 (independent, window) |

| STM32F303 line |                                                          |                                                                  |                                                                  |  |  |  |

|----------------|----------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|

| Device         | STM32F303x6/8                                            | STM32F303xB/C                                                    | STM32F303xD/E                                                    |  |  |  |

| RTC            | Calendar RTC with alarm,<br>periodic wakeup<br>from Stop | Calendar RTC with alarm,<br>periodic wakeup<br>from Stop/Standby | Calendar RTC with alarm,<br>periodic wakeup<br>from Stop/Standby |  |  |  |

|                | Packages                                                 |                                                                  |                                                                  |  |  |  |

| Packages       | LQFP64/48/32                                             | LQFP100/64/48<br>WLCSP100                                        | LQFP144/100/64<br>UFBGA100/WLCSP100                              |  |  |  |

Table 10. Peripheral overview<sup>(1)</sup> (continued)

### 2.2 STM32F303 line product differences

#### 2.2.1 Clock tree

When the HSI is selected as the PLL clock source, the maximum CPU clock can be reached:

- On the STM32F303x6/8/B/C devices, there is one bit PLLSRC (bit 16 in the RCC\_CFGR register) that allows selecting the PLL clock source; and when the HSI is selected as the PLL clock source, the maximum CPU frequency that can be reached is 64 MHz.

- On the STM32F303xD/E devices, two bits (bit 15 and 16 in the RCC\_CFGR register)

are used in order to select the PLL clock source. The purpose is to add a configuration

where the HSI is selected as the PLL clock source and 72 MHz CPU clock is reached.

| Bit 15 | Bit 16 | Configuration description                                  |  |  |  |  |

|--------|--------|------------------------------------------------------------|--|--|--|--|

| 0      | 0      | HSI/2 used as PREDIV1 entry and PREDIV1 forced to div by 2 |  |  |  |  |

| 0      | 1      | HSI used as PREDIV1 entry (only on STM32F303xD/E)          |  |  |  |  |

| 1      | 0      | HSE used as PREDIV1 entry                                  |  |  |  |  |

| 1      | 1      | Reserved                                                   |  |  |  |  |

Table 11. PLL clock source selection

### 2.2.2 Clock out capability

Compared to the STM32F303xB/C devices, on the STM32F303x6/8/D/E devices:

- One PLLNODIV bit in the RCC\_CFGR register is added, its purpose is to control the divider bypass for a PLL clock input to the MCO.

- The MCO frequency can be reduced by a configurable divider, controlled by the MCOPRE [2..0] bits in the RCC CFGR register.

<sup>1. ✓=</sup> supported.

Figure 5. STM32F303xB/C clock out capability

Figure 6. STM32F303x6/8/D/E clock out capability

#### 2.2.3 Embedded SRAM

Table 12. Embedded SRAM for the STM32F303 line

|                                   | STM32F303x6/8              | STM32F303xB/C                              | STM32F303xD/E                              |

|-----------------------------------|----------------------------|--------------------------------------------|--------------------------------------------|

| SRAM                              | 12 Kbytes                  | 40 Kbytes                                  | 64 Kbytes                                  |

| CCM SRAM                          | 4 Kbytes                   | 8 Kbytes                                   | 16 Kbytes                                  |

| Hardware parity check implemented | Whole SRAM and CCM<br>SRAM | First 16 Kbytes of SRAM and whole CCM SRAM | First 32 Kbytes of SRAM and whole CCM SRAM |

#### 2.2.4 **SYSCFG**

In the SYSCFG configuration register2 (SYSCFG\_CFGR2): PVD\_LOCK, SRAM\_PARITY\_LOCK and LOCKUP\_LOCK bits are reset only by system reset in the STM32F303x6/8/D/E devices.

However on the STM32F303xB/C devices, these bits can be reset also by a reset from RCC (using the SYSCFGRST bit).

The SYSCFG\_CFGR3 register is only available on the STM32F303x6/8 devices; this register allows for the remapping of the ADC2, I2C1, SPI1 DMA channels.

The SYSCFG\_CFGR4 register is only available on the STM32F303xD/E devices; this register allows for the remapping of the triggers of the ADCs, mainly the new TIM20 events.

#### 2.2.5 I/O and pinout

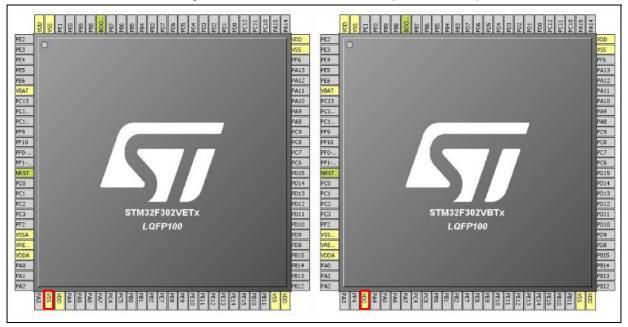

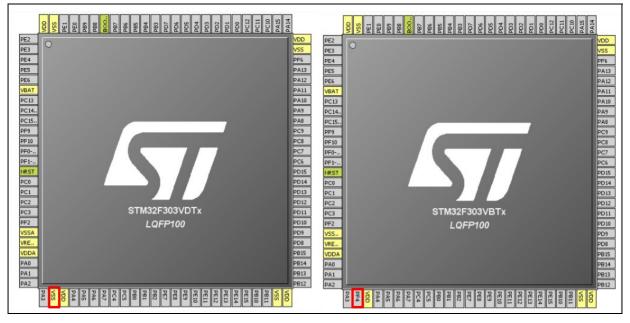

The STM32F303x6/8/B/C/D/E devices are pinout compatible except for the fact that PF4 in the STM32F303xB/C devices, is VSS in the STM32F303x6/8/D/E devices. Refer to *Figure 7* and *Figure 8*:

Figure 7. STM32F303xx LQFP64 pinout discrepancies

The GPIO LOCK feature is only available on Port A, B and D on the STM32F303xB/C devices. It is implemented for all the GPIO ports on the STM32F303x6/8/D/E devices.

*Table 13* summarizes all added alternate functions in the STM32F303x6/8 and the STM32F303xD/E devices compared to the STM32F303xB/C devices.

Table 13. Alternate functions added

| I/O and Alternate function | Added function                      |

|----------------------------|-------------------------------------|

| PB8 (AF7)                  | USART3_Rx                           |

| PB9 (AF7)                  | USART3_Tx                           |

| PC0 (AF2)                  | TIM1_CH1                            |

| PC1 (AF2)                  | TIM1_CH2                            |

| PC2 (AF2)                  | TIM1_CH3                            |

| PC3 (AF2)                  | TIM1_CH4                            |

| PC4 (AF2)                  | TIM1_ETR                            |

| PC5 (AF2)                  | TIM15_BKIN                          |

| PA12 (AF5)                 | I2S_CKIN                            |

| PF0 (AF5)                  | SPI2_NSS/I2S2_WS <sup>(1)</sup>     |

| PF1 (AF5)                  | SPI2_SCK/I2S2_CK <sup>(1)</sup>     |

| PA10 (AF5)                 | SPI2_MISO/I2S2ext_SD <sup>(1)</sup> |

| PA11 (AF5)                 | SPI2_MOSI/I2S2_SD <sup>(1)</sup>    |

| PB5 (AF8)                  | I2C3_SDA <sup>(1)</sup>             |

| PA8 (AF3)                  | I2C3_SCL <sup>(1)</sup>             |

| PC9 (AF3)                  | I2C3_SDA <sup>(1)</sup>             |

| PA9 (AF2)                  | I2C3_SMBAL <sup>(1)</sup>           |

<sup>1.</sup> These alternate functions are only available on the STM32F303xD/E devices.

Note: The FMC is available only on the STM32F303xD/E devices. The corresponding alternate functions are not mentioned in Table 13.

### 2.2.6 Analog to Digital Converter (ADC)

Table 14 shows the mapping differences of ADC channels on the STM32F303 line products.

Table 14. ADC channel mapping differences

| GPIO | STM32F303x6/8 | STM32F303xB/C | STM32F303xD/E |

|------|---------------|---------------|---------------|

| PB0  | ADC1_IN11     | ADC3_IN12     | ADC3_IN12     |

| PB1  | ADC1_IN12     | ADC3_IN1      | ADC3_IN1      |

| PB11 | -             | -             | ADC12_IN14    |

| PB12 | ADC2_IN13     | ADC4_IN3      | ADC4_IN3      |

| PB13 | ADC1_IN13     | ADC3_IN5      | ADC3_IN5      |

| PB14 | ADC2_IN14     | ADC4_IN4      | ADC4_IN4      |

| PB15 | ADC2_IN15     | ADC4_IN5      | ADC4_IN5      |

#### 2.2.7 Digital to Analog Converter (DAC)

The STM32F303xB/C/D/E devices embed two DAC channels with output buffers.

The STM32F303x6/8 devices embed 3 DAC channels: DAC1 channel1 is coming with an output buffer whereas DAC1 channel 2 and DAC2 channel 1 are coming without output buffers.

Table 15 lists DAC external triggers:

**TSEL** control bits **Devices** 2 0 STM32F303xB/C/D/E STM32F303x6/8 0 0 0 TIM6\_TRGO TIM3 TRGO(1) 0 0 1 TIM8\_TRGO or TIM3\_TRGO 0 1 0 Reserved 0 1 1 TIM15 TRGO 1 TIM2\_TRGO 0 0 TIM4 TRGO 1 0 Reserved 1 0 EXTI\_9 **SWTRIGX**

Table 15. DAC external triggers

#### 2.2.8 Comparators

The STM32F303x6/8/D/E devices embed ultra-fast comparators while the STM32F303xB/C devices embed fast comparators.

Compared to the STM32F303xB/C devices, the comparators on the STM32F303x6/8/D/E devices:

- Do not support programmable speed/consumption mode: High speed mode only

- Do not support the hysteresis feature

- Have only one VINP input:

- COMP2 INP: PA7

- COMP3\_INP: PB14

- COMP4 INP: PB0

- COMP5 INP: PB13

- COMP6 INP: PB11

- COMP7 INP: PC1

- Do not have COMP2 OUT on PA7

- Do not support the window mode

On the STM32F303x6/8/D/E devices, the comparators registers are reset only by system reset. However, on the STM32F303xB/C devices, they can be reset also by a reset from the RCC (using the SYSCFGRST bit).

<sup>1.</sup> DAC1\_TRIG\_RMP bit in SYSCFG\_CFGR1 register needs to be set by software.

### 2.2.9 Operational amplifier

On the STM32F303x6/8/D/E devices, the OPAMP register is reset only by system reset. However, on the STM32F303xB/C devices, this register can be reset also by a reset from the RCC (using the SYSCFGRST bit).

#### 2.2.10 Timer

*Table 16* lists all the timers that can be clocked at 144 MHz in each device of the STM32F303 line.

Table 16. Timers that can be clocked at 144 MHz<sup>(1)</sup>

|         | STM32F303x6/8 | STM32F303xB/C | STM32F303xD/E |

|---------|---------------|---------------|---------------|

| TIMER1  | ✓             | ✓             | ✓             |

| TIMER2  | -             | -             | ✓             |

| TIMER3  | -             | -             | ✓             |

| TIMER4  | -             | -             | ✓             |

| TIMER8  | -             | ✓             | ✓             |

| TIMER15 | -             | -             | ✓             |

| TIMER16 | -             | -             | ✓             |

| TIMER17 | -             | -             | ✓             |

| TIMER20 | -             | -             | ✓             |

<sup>✓=</sup> supported.

Table 17 summarizes the interconnection of timer triggers

Table 17. Interconnection of timer triggers

| Slave timer | Product           | ITR0 | ITR1     | ITR2 | ITR3              |

|-------------|-------------------|------|----------|------|-------------------|

| 1           | STM32F303xB/C/D/E | 15   | 2        | 3    | 4 or 17           |

| '           | STM32F303x6/8     | 15   | 2        | 3    | 17 <sup>(1)</sup> |

| 2           | STM32F303xB/C/D/E | 1    | 8        | 3    | 4                 |

| 2           | STM32F303x6/8     | 1    | Reserved | 3    | Reserved          |

|             | STM32F303xB/C/D/E | 1    | 2        | 15   | 4                 |

| 3           | STM32F303x6/8     | 1    | 2        | 15   | Reserved          |

| 4           | STM32F303xB/C/D/E | 1    | 2        | 3    | 8                 |

| 8           | STM32F303xB/C/D/E | 1    | 2        | 4    | 3                 |

| 15          | STM32F303xB/C/D/E | 2    | 3        | 16   | 17                |

|             | STM32F303x6/8     | 2    | 3        | 16   | 17                |

| 20          | STM32F303xD/E     | 1    | 8        | 4    | 15                |

<sup>1.</sup> TIM1\_ITR3\_RMP bit in SYSCFG\_CFGR1 register needs to be set by software.

#### **2.2.11 USART/UART**

*Table 18* highlights the differences between the USART/UART available on the STM32F303 line.

Table 18. USART/UART discrepancies<sup>(1)</sup>

|                                                   | STM32F303x6/8 |                   | STM32F303xB/C                |              |       | STM32F303xD/E                |               |          |

|---------------------------------------------------|---------------|-------------------|------------------------------|--------------|-------|------------------------------|---------------|----------|

| USART modes/<br>features                          | USART1        | USART2/<br>USART3 | USART1/<br>USART2/<br>USART3 | UART4        | UART5 | USART1/<br>USART2/<br>USART3 | UART4         | UART5    |

| Hardware flow control for modem                   | ✓             | ✓                 | ✓                            | -            | -     | ✓                            | -             | -        |

| Continuous communication using DMA                | <b>√</b>      | <b>√</b>          | <b>√</b>                     | ✓            | -     | <b>✓</b>                     | ✓             | -        |

| Multiprocessor communication                      | ✓             | ✓                 | ✓                            | ✓            | ✓     | ✓                            | ✓             | ✓        |

| Synchronous mode                                  | ✓             | ✓                 | ✓                            | -            | -     | ✓                            | -             | -        |

| Smartcard mode                                    | <b>√</b> (2)  | -                 | <b>√</b> (3)(4)              | -            | -     | <b>√</b> (3)                 | -             | -        |

| Single-wire half-<br>duplex<br>communication      | ✓             | ✓                 | <b>√</b>                     | ✓            | ✓     | <b>√</b>                     | ✓             | ✓        |

| IrDA SIR ENDEC<br>block                           | ✓             | -                 | ✓                            | ✓            | ✓     | ✓                            | ✓             | ✓        |

| LIN mode                                          | ✓             | -                 | ✓                            | ✓            | ✓     | ✓                            | ✓             | ✓        |

| Dual clock domain<br>and wakeup from<br>Stop mode | <b>√</b>      | -                 | <b>√</b>                     | <b>√</b>     | ✓     | <b>√</b>                     | ✓             | <b>√</b> |

| Receiver timeout interrupt                        | ✓             | -                 | ✓                            | ✓            | ✓     | <b>√</b>                     | ✓             | ✓        |

| Modbus communication                              | ✓             | -                 | <b>√</b>                     | ✓            | ✓     | ✓                            | ✓             | ✓        |

| Auto baud rate detection                          | ✓             | -                 | <b>√</b>                     | -            | -     | <b>√</b>                     | -             | -        |

| Driver Enable                                     | ✓             | ✓                 | ✓                            | -            | -     | ✓                            | -             | -        |

| USART data<br>length                              | 7, 8 an       | d 9 bits          |                              | 8 and 9 bits |       | 7                            | , 8 and 9 bit | S        |

<sup>✓=</sup> supported.

<sup>4.</sup> With the following limitation for the STM32F303xB/C device: If the USART is used in the Smartcard mode and the card cannot use the default communication parameters after Answer to Reset and does not support clock stop, it is not possible to use SCLK to clock the card. This is due to the fact that the USART and its clock output must be disabled during the reprogramming of some of the parameters.

<sup>2.</sup> SCLK is always available when CLKEN = 1, regardless of the UE bit value.

<sup>3.</sup> SCLK output is disabled when UE bit = 0.

#### 2.2.12 USB

On the STM32F303x6/8 devices, there is no USB.

The USB peripheral contained on the STM32F303D/E devices supports the LPM.

Note that for the STM32F303xB/C devices, the USB\_DM and USB\_DP are mapped on AF14 of PA11 and PA12, while on the STM32F303xD/E devices, there is no need to configure AF since those inputs are directly connected to GPIO, when the USB is enabled.

On the STM32F303xD/E devices, there are 768 bytes dedicated SRAM for USB plus 256 bytes shared SRAM with the CAN. When the CAN is disabled, the whole 1 Kbyte can be used for the USB.

Consequently, the USB SRAM management is different between the STM32F303xB/C devices and the STM32F303xD/E devices.

Table 19. USB RAM management

| Device                                            | STM32F303x6/8 | STM32F303xB/C      | STM32F303xD/E     |

|---------------------------------------------------|---------------|--------------------|-------------------|

| Number of endpoints                               | N/A           | 8                  | 8                 |

| Size of dedicated packet buffer memory SRAM       | N/A           | 512 bytes          | 1024 bytes        |

| Dedicated packet buffer memory SRAM access scheme | N/A           | 1 x 16 bits / word | 2 x16 bits / word |

| USB 2.0 Link Power<br>Management (LPM) support    | N/A           | N/A                | ✓ (supported)     |

AN4807 Revision history

# 3 Revision history

Table 20. Document revision history

| Date        | Revision | Changes                                                                                           |

|-------------|----------|---------------------------------------------------------------------------------------------------|

| 20-Apr-2016 | 1        | Initial release.                                                                                  |

| 13-Oct-2016 | 2        | Updated Section 1.2.8: Comparators and Section 2.2.8: Comparators not supporting the window mode. |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics - All rights reserved