# AN4823 Application note

L99DZ80EP/L99DZ81EP H-bridge driver switching consideration and Rgate calculation

### Introduction

This document gives information about H-bridge driver embedded in the L99DZ80EP and L99DZ81EP: those devices include an SPI-programmable slew-rate circuit that drives 4 external MOSFETs in a H-bridge configuration supporting electric-window applications.

February 2016 DocID028918 Rev 2 1/8

Block diagram AN4823

## 1 Block diagram

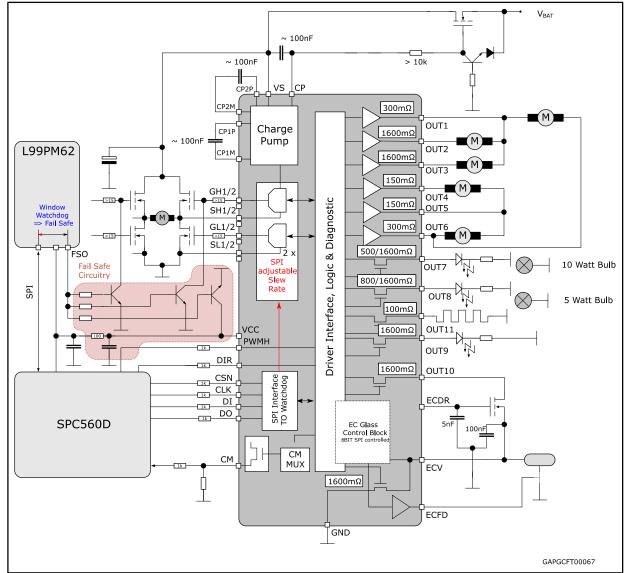

Figure 1: L99DZ80EP and L99DFZ81EP block diagram

L99DZ80EP and L99DZ81EP devices provide, through pins GH1/2, GL1/2 and SL1/2, dedicated driving signals to the external 4 MOSFETs.

## 2 L99DZ80EP/L99DZ81EP smart switching details

Chargepump Voltage ٧S VCP ~(VS + 10V)  $\Box$ I<sub>charge</sub>  $\stackrel{>}{\geq} R_{SW} = 6\Omega$  $SW_{RCSW}$  $\text{SW}_{\text{IC}}$ Measure V<sub>DS</sub>  $V_{\text{DSSW}}$  $\mathsf{T}_\mathsf{H}$ ₋∟  $R_{\text{Gate}} \quad \underline{V_{\text{GS}}}$  $V_{\text{GSSW}}$  $V_{\text{Gate}}$  $V_{DS}$  $SW_{CVSW}$ Measure V<sub>GS</sub> C2  $SW_{\text{ID}}$  $C_{\text{VSW}} \\$  $SW_{RDSW}$ **Motor Inductor**  $R_{SW} = 6\Omega$ Idischarge  $\overline{\mathsf{V}}_{\mathsf{Source}}$  $R_{SW} = 6\Omega$ , typical design value GAPG2601160917CFT

Figure 2: Simplified schematic of driver for external high-side

Typical curves are described in the following figure.

V<sub>GSHX</sub>

Current

Controlled

Low-Resistive

Switch

Controlled

Controlled

V<sub>DSHx</sub>

V<sub>DSHx</sub>

Current

Controlled

Controlled

Controlled

Controlled

Controlled

Figure 3: H-bridge GSHx slope

Some transitions are now analyzed:

#### **Transition A**

Threshold voltage ext FET sampled and stored in C<sub>VSW</sub> during Miller Plateau ↔ V<sub>TH</sub>.

During this phase, threshold stored in  $C_{VSW}$  during Miller Plateau is increased by  $I_{Charge}$  \*  $R_{Gate}$  in reference to  $V_{TH}$  of the external MOSFET

#### **Transition B**

Switch-off started with Rsw, "hard switching".

#### **Transition C**

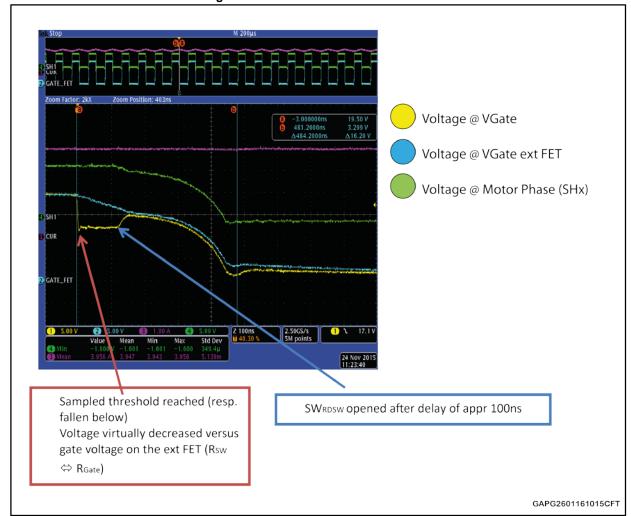

- Reaching V<sub>TH</sub>, R<sub>SW</sub> is turned-off by opening SW<sub>RDSW</sub>

- Opening of SW<sub>RDSW</sub> is done with a certain delay

- Afterwards gate discharge is done by the programmed current source (Idischarge)

During this phase,  $V_{\text{Gate}}$  is decreased by resistive divider  $R_{\text{SW}} \leftrightarrow R_{\text{gate}}$  and "Virtually" the threshold to switch from switch mode to current mode is lower than real gate source voltage on external FET.

Figure 4: "Transition C measurement on a real device" shows measurements performed on a real device.

577

Figure 4: Transition C measurement on a real device

## 2.1 How to choose a proper Rgate resistance

Charge in the beginning of turn-off phase is discharged by the hard switch in series with the external gate resistance. Average current during this phase is approximately (5V +  $V_{TH}/2$ ) / ( $R_{SW} + R_{Gate}$ ).

Due to virtual decreased sample voltage (by resitive divider R<sub>SW</sub> & R<sub>Gate</sub>) the transistion from switch mode to current control mode is started almost immediately after start of turnoff of ext FET (depending on size of R<sub>Gate</sub>).

Delay of opening SW<sub>RDSW</sub> is approximately 100 ns (typical value).

During this time  $Q_{gate}$  must NOT be discharged to ensure to enter  $Q_{GD}$  plateau. As rule of thumb the according  $R_{gate}$  can be calculated by the following formula:

$R_{Gate} \ge (5V + VTH/2) * 100ns / Q_{Gate} - R_{SW}$

That value of R<sub>Gate</sub> is needed to enter current source mode.

Table 1: Rgate values as per different MOSFET choice

| MOSFET            | Q <sub>Total</sub> (nC) | Q <sub>GD</sub><br>(nC) | Q <sub>GS</sub><br>(nC) | Q <sub>Total</sub> – Q <sub>GD</sub> – Q <sub>GS</sub> (nC) | V <sub>TH</sub> @ 40A<br>(V) | Calculated<br>R <sub>Gate</sub> ≈ (Ω) |

|-------------------|-------------------------|-------------------------|-------------------------|-------------------------------------------------------------|------------------------------|---------------------------------------|

| ST<br>STD64N4F6AG | 44                      | 15                      | 12                      | 18                                                          | 5.5                          | 38                                    |

| ST<br>STD80N4F6AG | 36                      | 9                       | 11                      | 16                                                          | 4.8                          | 41                                    |

| ST VNH7013        | 36                      | 5                       | 8,5                     | 22.5                                                        | Not specified (2 4)          | 28<br>(@VTH =<br>5V)                  |

| Supplier A        | 45                      | 12.6                    | 10                      | 22.4                                                        | 4V                           | 26                                    |

| Supplier B        | 17.2                    | 2.4                     | 8                       | 6.8                                                         | 5.5V                         | 109                                   |

AN4823 Revision history

# 3 Revision history

**Table 2: Document revision history**

| Date        | Revision | Changes                                                                                                                                             |  |  |  |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 17-Feb-2016 | 1        | Initial release.                                                                                                                                    |  |  |  |

| 29-Feb-2016 | 2        | Updated Figure 2: "Simplified schematic of driver for external high-side" Section 2.1: "How to choose a proper Rgate resistance":  Updated equation |  |  |  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics - All rights reserved