# AN4990 Application note

# Getting started with sigma-delta digital interface on applicable STM32 microcontrollers

# Introduction

The DFSDM (digital filter for sigma-delta modulators) is an innovative embedded peripheral available in a selection of STM32 microcontrollers (see *Table 1: Applicable products*), and is of particular interest for applications that process external analog signals.

Although the DFSDM is a pure digital peripheral, it is designed to support a wide range of external analog front ends. By keeping the analog front-end part (sigma-delta modulator) outside of the microcontroller, the user has total flexibility to select the analog properties according to the application requirements (analog range, noise, sampling speed).

The raw converted digital data from the sigma-delta modulator is then processed by the DFSDM peripheral (digital filtering). The DFSDM configuration is flexible enough to support a wide range of converted data properties: output data width, output data rate, output frequency range.

From an application point of view, the DFSDM with its external analog front-end behaves like an ADC converter. Additional functions typical of an ADC are also available within the DFSDM such as analog watchdog, extremes detector and offset correction.

#### Reference:

[TUTORIAL]

In this document, <code>[TUTORIAL]</code> refers to a DFSDM simulator available in the form of a Microsoft<sup>®</sup> Excel<sup>®</sup> workbook, that can be downloaded from <code>www.st.com</code>, using home page search engine with keyword "DFSDM tutorial".

Table 1. Applicable products

| Туре             | Applicable perimeter | Series, lines, references                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Microcontrollers | Complete Series      | STM32L4 Series, STM32L4+ Series, STM32H7 Series                                                                                                                                                                                                                                                                                                                                                                   |

|                  | Complete Line        | STM32F412 line, STM32F413/423 line                                                                                                                                                                                                                                                                                                                                                                                |

|                  | STM32F76xxx          | STM32F765BG, STM32F765BI, STM32F765IG, STM32F765II, STM32F765NG, STM32F765NI, STM32F765VG, STM32F765VI, STM32F765ZG, STM32F765ZI, STM32F767BG, STM32F767BI, STM32F767IG, STM32F767II, STM32F767NG, STM32F767NI, STM32F767VG, STM32F767VI, STM32F767ZG, STM32F767ZI, STM32F768AI, STM32F769AG, STM32F769AI, STM32F769BG, STM32F769BI, STM32F769NI, STM32F769NI, STM32F769NI, STM32F769NI, STM32F769NI, STM32F769NI |

|                  | STM32F77xxx          | STM32F777BI, STM32F777II, STM32F777NI, STM32F777VI, STM32F777ZI, STM32F778AI, STM32F779AI, STM32F779BI, STM32F779II, STM32F779NI                                                                                                                                                                                                                                                                                  |

March 2018 AN4990 Rev 1 1/56

Contents AN4990

# **Contents**

| 1 | Ove   | rview of A                                            | A/D conversion principle using DFSDM        | . 6  |

|---|-------|-------------------------------------------------------|---------------------------------------------|------|

|   | 1.1   | Fundam                                                | ental concept of A/D conversion using DFSDM | . 6  |

|   | 1.2   | Sigma-d                                               | elta modulator                              | . 6  |

|   | 1.3   | Digital fi                                            | Iter                                        | . 8  |

| 2 | _     |                                                       | modulation principle (external analog       | _    |

|   |       |                                                       | ctioning, simulations)                      |      |

|   | 2.1   | Principle of sigma-delta modulation                   |                                             |      |

|   | 2.2   | Advantages of sigma-delta modulation                  |                                             | .11  |

|   |       | 2.2.1                                                 | Noise shaping                               | . 11 |

|   |       | 2.2.2                                                 | Linearity of A/D conversion                 | . 12 |

|   |       | 2.2.3                                                 | Scalable ADC resolution                     | . 12 |

|   | 2.3   | Disadva                                               | ntages of sigma-delta modulation            | 13   |

|   |       | 2.3.1                                                 | Offset and gain error                       | . 13 |

|   |       | 2.3.2                                                 | Lower data rate                             | . 13 |

|   | 2.4   | Simulation                                            | on of sigma-delta modulation                | 14   |

|   |       | 2.4.1                                                 | Simulation with [TUTORIAL]                  | . 14 |

| 3 | Digit | al filterin                                           | g - principle and design                    | 15   |

|   | 3.1   | Function                                              | description                                 | 15   |

|   | 3.2   | Example of Sinc filter function - resolution increase |                                             | 15   |

|   | 3.3   | Hardwar                                               | re design of Sinc filter                    | 17   |

| 4 | DFS   | DM perip                                              | heral operation                             | 22   |

|   | 4.1   | Block dia                                             | agram                                       | 22   |

|   | 4.2   | DFSDM components                                      |                                             |      |

|   |       | 4.2.1                                                 | Serial transceivers                         |      |

|   |       | 4.2.2                                                 | Parallel transceivers                       |      |

|   |       | 4.2.3                                                 | Digital filter                              | . 23 |

|   |       | 4.2.4                                                 | Integrator                                  | . 23 |

|   |       | 4.2.5                                                 | Output data unit                            |      |

|   |       | 4.2.6                                                 | Analog watchdog                             | . 24 |

|   |       | 4.2.7                                                 | Short circuit detector                      | . 24 |

|   |      | 4.2.8 Extremes detector                                  | 25        |

|---|------|----------------------------------------------------------|-----------|

|   | 4.3  | DFSDM simulation                                         | 25        |

|   |      | 4.3.1 Sigma-delta modulator principle                    | 25        |

|   |      | 4.3.2 DFSDM filtering simulation (filter and integrator) | 26        |

|   |      | 4.3.3 Frequency characteristics for Sinc filter          | 27        |

|   |      | 4.3.4 Noise shaping of sigma-delta modulation            | 28        |

|   |      | 4.3.5 High order filters operation                       | 31        |

|   |      | 4.3.6 Delta-sigma DAC simulation                         | 33        |

|   |      | 4.3.7 High pass filter simulation                        | 34        |

|   | 4.4  | Additional functions in DFSDM                            | 35        |

|   |      | 4.4.1 Digital microphones (MEMS) support                 | 35        |

|   |      | 4.4.2 Beamforming support                                | 37        |

|   |      | 4.4.3 Audio clock support – independent clock operation  | 39        |

|   | 4.5  | DFSDM power consumption optimization4                    | 10        |

|   |      | 4.5.1 Power optimization in Sleep mode                   | 10        |

| 5 | DFS  | OM peripheral configuration tutorial4                    | <b>!2</b> |

|   | 5.1  | Configuration introduction                               | 12        |

|   | 5.2  | Clocks configuration                                     | 12        |

|   | 5.3  | Transceivers                                             | 13        |

|   |      | 5.3.1 Serial transceivers configuration                  |           |

|   |      | 5.3.2 Parallel transceivers                              |           |

|   | 5.4  | Filter                                                   | 17        |

|   |      | 5.4.1 Sinc filter                                        |           |

|   |      | 5.4.2 Integrator                                         | 19        |

|   | 5.5  | Analog watchdog                                          |           |

|   | 5.6  | Short circuit detector 5                                 |           |

|   | 5.7  | Pulse skipper                                            |           |

|   | 5.8  | • •                                                      |           |

|   | 5.0  | Configuration using [TUTORIAL]                           | ےر        |

| 6 | Con  | clusion                                                  | 54        |

| 7 | Revi | sion history                                             | 55        |

# AN4990

| Table 1. | Applicable products              | 1 |

|----------|----------------------------------|---|

|          | DFSDM application examples       |   |

|          | DFSDM analog watchdog parameters |   |

|          | Document revision history        |   |

AN4990 List of figures

# **List of figures**

| -igure 1.  | A/D conversion block diagram using the DFSDM                            | 6  |

|------------|-------------------------------------------------------------------------|----|

| igure 2.   | PWM modulation example                                                  |    |

| igure 3.   | Sigma-delta modulation example                                          |    |

| igure 4.   | Sigma-delta modulation principle                                        | 9  |

| igure 5.   | Sigma-delta modulator voltages timing diagram                           | 0  |

| igure 6.   | Spectrum of PWM and sigma-delta modulation                              | 2  |

| igure 7.   | Simulation of sigma-delta modulator                                     | 4  |

| igure 8.   | Example of 3rd order filter outputs with one bit per filter length      | 6  |

| igure 9.   | Example of 3rd order filter outputs with higher density of input pulses | 7  |

| igure 10.  | Basic schematic for simple moving average implementation                | 8  |

| igure 11.  | Simplification of Sinc filter design - step 1                           | 8  |

| igure 12.  | Simplification of Sinc filter design - step 2                           | 9  |

| igure 13.  | Simplification of Sinc filter design - step 3                           |    |

| igure 14.  | Simplification of Sinc filter design - step 4                           |    |

| igure 15.  | Higher order Sinc filter implementation                                 |    |

| igure 16.  | Block diagram of DFSDM peripheral                                       |    |

| igure 17.  | Sigma-delta modulator simulation                                        | :6 |

| Figure 18. | Filtering simulation                                                    |    |

| igure 19.  | Filter frequency characteristics                                        | 8: |

| igure 20.  | Sigma-delta and PWM modulated signals (for frequency spectrum           |    |

|            | comparison)                                                             |    |

| igure 21.  | Spectrum of sigma-delta signal and PWM signal                           | 0  |

| igure 22.  | Spectrum of sigma-delta signal and PWM signal                           |    |

|            | with signal amplitude reduced to 10% of full scale                      |    |

| igure 23.  | High order filters - multiple averaging principle                       |    |

| igure 24.  | First order delta-sigma DAC principle                                   |    |

| igure 25.  | Delta-sigma DAC simulation                                              |    |

| igure 26.  | HP filter simulation                                                    |    |

| igure 27.  | MEMS microphone outputs (L and R channel)                               |    |

| igure 28.  | MEMS microphone connection to DFSDM (stereo support)                    |    |

| igure 29.  | Beamforming principle                                                   |    |

| igure 30.  | Pulse skipping implementation for beamforming                           |    |

| igure 31.  | Pulse skipping example (FOSR=8)                                         |    |

| igure 32.  | Sinc filter frequency characteristic shape                              |    |

| igure 33.  | DFSDM configuration in [TUTORIAL]                                       | 3  |

AN4990 Rev 1 5/56

# 1 Overview of A/D conversion principle using DFSDM

This document supports Arm®(a)-based devices.

# 1.1 Fundamental concept of A/D conversion using DFSDM

The basic block diagram of analog-to-digital conversion using DFSDM is provided in *Figure 1*.

Sigma-Delta modulator

(ΣΔ)

Serial line

DATA

DFSDM

1-bit data

stream

MSv43870V1

Figure 1. A/D conversion block diagram using the DFSDM

The external analog signal is processed by an external sigma-delta modulator which converts the analog signal into a digital 1-bit stream (DATA and CLK signals). The 1-bit stream is a fast serial line stream of logical ones and zeros: the DATA signal is sampled by CLK (clock signal). The average value of these logical ones and zeros, computed during a long enough time duration, represents the analog input value. The duration of the averaging period determine the precision of the analog input signal capture.

The averaging of the 1-bit stream is performed by the STM32 microcontroller DFSDM peripheral (DFSDM = digital filter for sigma-delta modulators). The DFSDM acquires and processes the 1-bit data stream (digital filtering, averaging). The DFSDM outputs data samples at a slower data rate than the input 1-bit stream but with a higher resolution. The DFSDM digital filter settings define the output resolution and data rate.

# 1.2 Sigma-delta modulator

The DFSDM peripheral requires an external analog front-end that performs the A/D conversion of the analog source. This external analog to digital conversion is performed in a sigma-delta modulator.

A sigma-delta modulator consists in a 1-bit<sup>(b)</sup> A/D converter which digitizes the input analog data into a serial digital data stream. The analog input is sampled and converted into a 1-bit digital data stream with alternating zeros and ones. The mean value of the digital stream

b. In general the output of a sigma-delta modulator can be multi-bit however in this document the focus is on a 1-bit A/D converter (which is the most frequent case).

a. Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

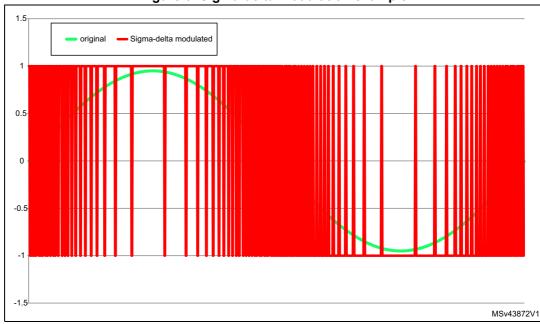

computed during a given time interval represents the average value of the input analog signal during the same time interval. The sigma-delta modulation principle could be presented as a special PWM modulation where both the period and the duty cycle would be modulated (whereas the period is fixed and only the duty cycle is modulated in a typical PWM modulation). See *Figure 2* and *Figure 3* for comparison between PWM and sigma-delta modulation.

The digital data stream outputting the sigma-delta modulator is then processed by the STM32 microcontroller DFSDM peripheral. The DFSDM performs a digital filtering using parameters that need to be configured according the application requirements.

Note:

For analysis, the digital stream is usually "converted" from binary 0 and binary 1 weights into +1 and -1 weights for comparison with input voltages cleared of any DC component. The zero input voltage generates duty cycle 50:50 (first order sigma-delta modulator is used).

AN4990 Rev 1 7/56

Figure 3. Sigma-delta modulation example

# 1.3 Digital filter

The DFSDM peripheral (digital filter for sigma-delta modulators) processes the digital part of the A/D conversion. The digital data stream is provided by an external sigma-delta modulator. The basic functionality of the DFSDM is to implement a digital filter. The DFSDM processing consists in averaging a fast rate input serial stream and producing a parallel, lower rate, data output with higher resolution. The DFSDM embedded filter features a set of configurable parameters that allow to tune the output resolution and data rate and meet the application requirements.

The DFSDM features additional ADC-related functionalities including:

- Independent fast watchdog on each channel with programmable speed and resolution to detect input signals exceeding minimal or maximal allowed voltage levels.

- Break signal generation used to instantaneously report events like analog watchdog or short circuit detection to other peripherals (timers).

- Short circuit detector on each channel for very fast detection of signal clamping: when

input voltage reaches one of the analog range limits and stays steady in excess of a

given time duration (independent from the main conversion).

- Extreme detector to record minimal and maximal input voltage excursion.

577

# 2 Sigma-delta modulation principle (external analog front-end functioning, simulations)

# 2.1 Principle of sigma-delta modulation

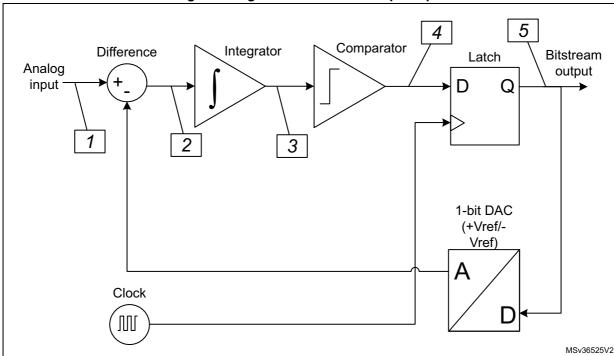

The basic functional block diagram of a sigma-delta modulator is presented on Figure 4.

Figure 4. Sigma-delta modulation principle

1. The references [1] to [5] present in the above figure are used in the following paragraphs.

AN4990 Rev 1 9/56

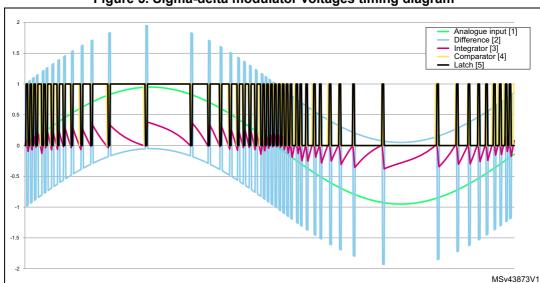

*Figure 5* provides an example of the signals available at the different stages of the analog to digital conversion.

Figure 5. Sigma-delta modulator voltages timing diagram

1. The references [1] to [5] present in the above figure are used in the following paragraph.

The below description of sigma-delta modulation uses references present in *Figure 4* and *Figure 5*:

The analog input signal [1] is added to the 1-bit DAC output feedback from the comparator (+Vref or -Vref voltage) and the result [2] goes to the integrator. The integrator cumulates the difference between the analog input signal [1] and the 1-bit DAC output feedback (+Vref or -Vref voltage). The integrator output [3] is then compared with the zero voltage reference by the comparator. The comparator output [4] is latched periodically at the clock frequency by the D-latch to propagate the comparator result to the modulator output in quantized time steps (clock ticks). The D-latch output [5] is the digital 1-bit output from the sigma-delta modulator. The output is fed back to the 1-bit D/A converter which outputs only 2 possible analog voltages (usually implemented as a switch between +Vref and -Vref reference voltages). The data rate of the 1-bit output data stream is defined by the modulator clock frequency.

The output of the sigma-delta modulation is a digital data stream (black curve on *Figure 5*) that is clocked by the modulator clock. The average value of this output (computed in the digital domain) represents the input analog voltage. This digital average should be computed as the ratio between the number of ones versus the number of zeros observed during a given number of clock periods within the sigma delta output stream.

This digital data stream constitutes the input of the STM32 microcontroller DFSDM peripheral where it can be filtered. DFSDM configurable parameters need to be set according the application requirements.

# 2.2 Advantages of sigma-delta modulation

# 2.2.1 Noise shaping

The output signal from the sigma-delta modulation must be filtered to remove the high frequency content (the quantization noise) and retain only the useful frequency band. In order to properly design such filter, some understanding of the sigma-delta modulated signal spectrum is required. The sigma-delta modulated signal spectrum is different from the PWM modulation spectrum.

The PWM modulation signal is characterized by a fixed period and a variable duty cycle. Due to the fixed modulation period (or frequency), the PWM spectrum exhibits typical peaks of energy corresponding to the modulation base frequency and its harmonics. The removal of these harmonic peaks is more difficult by analog filtering (RC or LC filter).

The sigma-delta modulation uses both variable duty cycle and variable frequency. As a result, the energy on the sigma-delta spectrum is spread more evenly and is not concentrated on regularly spaced peaks like for the PWM (there is no fixed modulation frequency). Furthermore, there is usually more energy at higher frequencies for sigma-delta modulations than for PWM (due to higher modulation frequencies). The noise content of sigma-delta modulation can be easily removed by analog filtering (RC or LC filter).

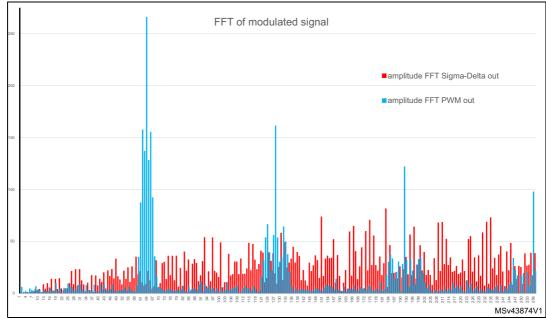

A typical spectrum for a PWM and for a sigma-delta modulation are provided on *Figure 6* (corresponding respectively to signals presented in *Figure 2: PWM modulation example* and *Figure 3: Sigma-delta modulation example*). The PWM modulation produces higher peaks at lower frequencies, therefore the PWM processing requires a filter of higher order in order to properly reject the first peak of energy corresponding to the PWM modulation base frequency. In the sigma-delta modulation spectrum the energy is less present at lower frequencies so the filter design can be simpler. The filtering capabilities must be adapted to the order of the sigma-delta modulator. For example, digital microphones typically have a 4th order sigma-delta modulator, which has a low quantization noise in the useful band, but a very strong out-off band quantization noise. The filter order must be selected in order to suppress this strong out-off band quantization noise without affecting the useful band.

The effect of the sigma-delta modulation to spread the quantization noise more evenly and to higher frequencies is called "noise shaping". One can take advantage of such characteristic to design simpler filters and benefit from less noisy baseband signals.

AN4990 Rev 1 11/56

Figure 6. Spectrum of PWM and sigma-delta modulation

# 2.2.2 Linearity of A/D conversion

The output from the sigma-delta modulator is 1-bit serial data stream. The resolution of this stream is only one bit which is usually not enough for the application. The method to increase the signal resolution consists in averaging the 1-bit stream during a given period of time. The averaged data stream has a wider resolution (typically 16-bit) but a slower sample rate. The averaging (filtering) operation is based on <u>linear</u> mathematical operation in the digital domain hence there is no added non-linear distortion due to filtering.

A/D converters with parallel data output usually use more analog elements than the sigmadelta modulators. For example the SAR ADC type with N-bits resolution uses internally a R-2R resistor network (or C-2C capacitor network) with N resistors (or capacitors). The resistors (capacitors) used in these type of ADCs must have a precise 1:1 or 1:2 resistance (capacitance) ratio. The linearity of the SAR ADC depends on the precision of the resistors (capacitors). In practice the ratios are never perfect and the imprecision is at the origin of non-linearities that impact the transfer curve.

For above mentioned reasons, the linearity of A/D conversion using sigma-delta modulation is usually better than with other type of A/D conversion. The non-linearity in the sigma-delta ADC conversion depends only on the sigma-delta modulator design (see *Figure 4: Sigma-delta modulation principle*). Furthermore, the non-linearity depends only on the influence of the input voltage on analog element intrinsic characteristics (capacitors/resistors in integrator and switches which capacitance/resistance changing with input voltage) and not on ratios between the different component nominal values. Linearity is more important for audio applications where the non-linearity causes signal distortion (static linearity INL is linked with dynamic linearity THD).

### 2.2.3 Scalable ADC resolution

The final output resolution for sigma-delta conversion is not fixed (as it is for example for a 12-bit SAR ADC). The output from a sigma-delta modulator is 1-bit resolution which can then be increased by following digital filtering (averaging) to the required resolution.

The drawback of this resolution increase is the reduction of the output data rate. This data rate decrease is predictable and must be computed for a given application requirement. For example a digital filter can be configured for a 24-bit output @ 1 kHz output data rate, or for

a 16-bit output @ 50 kHz output data rate.

The resolution increase is theoretically unlimited but in practice one needs to take into consideration the noise and the errors caused by the components in the conversion path (sigma-delta modulator design, injected noise ...). Another consideration is the stability of the signal during the sampling period that can affect the precision of the measurement, in particular for applications with very low data rate and high resolution.

# 2.3 Disadvantages of sigma-delta modulation

# 2.3.1 Offset and gain error

The average of the 1-bit data stream signal from sigma-delta modulator represents the mean value of the analog input signal. The precision of this digital output average (in the range [0..1]) can be affected by the following sigma-delta modulator components (see *Figure 4: Sigma-delta modulation principle*):

- · resistors and capacitors in the integrator

- reference voltage in the 1-bit DAC (+Vref / -Vref)

- · offset of the integrator

These components have tolerances: capacitor/resistor values, offset voltage, difference between +Vref and -Vref absolute voltage.

In the ideal case, a 1-bit digital output having in average the same amount of 0's and 1's corresponds exactly to a zero volt input signal. Due to the components tolerances (mentioned above) the input analog voltage corresponding in a same amount of 0's and 1's, is not exactly zero volt, and represents the offset error. The offset error can be compensated by software or by hardware (calibration process).

In the ideal case the output 1-bit digital signal with a 50:50 duty cycle (amount of 0's is equal to the amount of 1's) should correspond exactly to the zero input analog voltage. Due to the components tolerances (mentioned above) the input analog voltage corresponding to the 50:50 duty cycle is not exactly zero and represents the offset error. The offset error can be compensated by software or by hardware (calibration process).

The gain coefficient that is the ratio between the output data and the input voltage is also affected by the sigma-delta component tolerances. The difference between the theoretical gain and the actual measured conversion gain represents the gain error. It can be also compensated by calibration (usually in software).

Some characteristics of the sigma-delta components are also dependent on temperature, which affects in turn the offset and gain errors. The influence of the temperature on the integrator resistors and capacitors affects only the gain error. The offset error is less affected by the temperature changes because the errors affecting +Vref and -Vref, due to the symmetric nature of these references, are self compensated.

#### 2.3.2 Lower data rate

With sigma-delta modulators, a way to increase the resolution is to increase the averaging of the 1-bit data stream (longer averaging time or higher filter order). This is why the sigma-

AN4990 Rev 1 13/56

delta converters are primarily used for lower data rate applications (usually for audio frequency range and lower frequencies). But in special cases where the excellent linearity is a must, the sigma-delta converters can be used for higher data rate applications.

For quasi static applications (temperature sensors) the data rate is not a constraint and the sigma-delta modulator is often chosen for its scalable resolution capability (high resolution on low data rates).

# 2.4 Simulation of sigma-delta modulation

# 2.4.1 Simulation with [TUTORIAL]

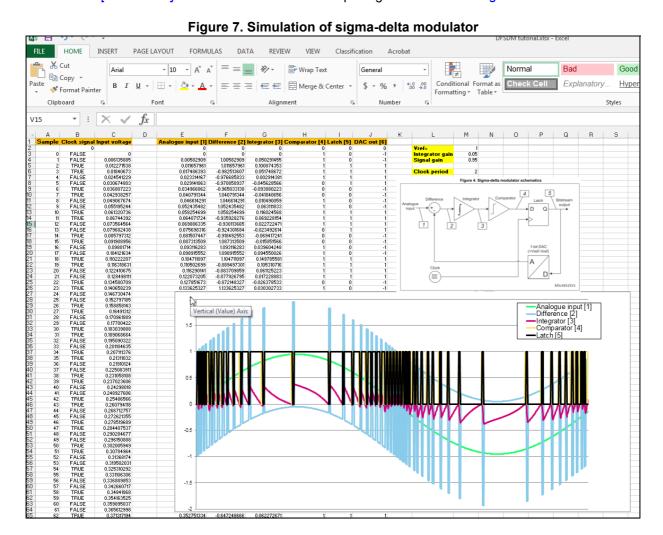

To help understanding the sigma-delta modulation, the sigma-delta model (as shown in Figure 4: Sigma-delta modulation principle) has been implemented in [TUTORIAL]. The timing diagrams are provided for each voltage signal referenced in Figure 4: Sigma-delta modulation principle. The user can change some parameters and input voltages and see the impact at each stage of the sigma-delta modulator. A simulation example available in [TUTORIAL] and based on a sinewave input signal is shown on Figure 7.

# 3 Digital filtering - principle and design

# 3.1 Function description

The digital filter performs the filtering (averaging) of the 1-bit data stream generated from the sigma-delta modulator. The filter output is a data word with higher resolution (usually 12 - 24 bits) but reduced data rate (decimation). The digital filter function consists in removing out-off band frequency components (quantization noise, unwanted signals...) and reducing the data rate according to the useful bandwidth (decimation).

The design of the filter has a strong influence on the A/D conversion characteristics and is the result of a compromise between the required parameters (sharpness of filter, filter tuning, final resolution, ...) and the hardware implementation complexity (which leads to cost issue). The goal is to minimize the filter design complexity while meeting the required A/D characteristics.

Note: Signal filtering often requires more complex processing than simply averaging the 1-bit data stream.

Here are some elements to consider when designing a filter:

Filter type:

Among various types of filter, the Sinc filter presents interesting characteristics, combining a cheap hardware implementation with acceptable level of performance. The Sinc filter has a frequency response that can be modelized by a sinc(x) function (hence its name). The Sinc filter is the most commonly used type in sigma-delta A/D converter implementations. It is cheap because no multipliers are required, and the filter coefficients are integers. The Sinc filter performs a simple "moving average" calculation over the 1-bit samples.

Filter length (FOSR - filter oversampling ratio):

A longer filter (averaging of more samples) generates higher resolution but decreases the output data rate (decimation). Therefore the filter length is selected as a compromise between required conversion rate and final data resolution.

Filter order (FORD):

The "moving average" calculation can be applied multiple times to already averaged samples. The filter order defines how many time the "moving average" calculation is applied to the same input samples. A higher order filter generates higher resolution (by adding more averaging loops) but increases latency.

# 3.2 Example of Sinc filter function - resolution increase

This section focuses on showing how multiple "moving average" calculations can increase the Sinc filter resolution.

Here is a detailed presentation of a 3<sup>rd</sup> order filter (FORD=3) with length FOSR=10 (with moving averaging at each filter stage):

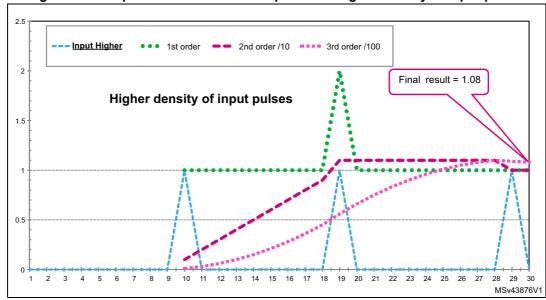

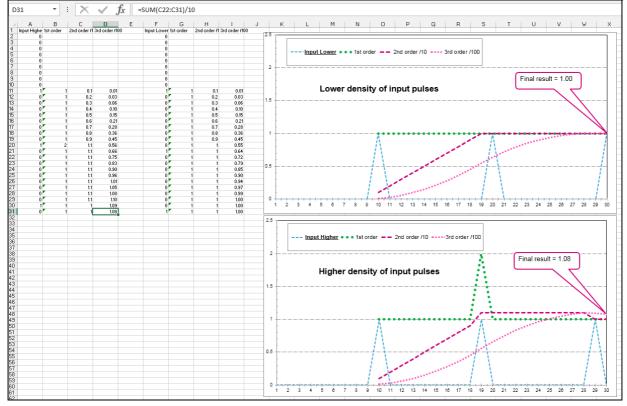

- The observation is done on 3 periods of the input stream: 3 x FOSR = 30 samples (see Figure 8 and Figure 9).

- The input 1-bit data stream is almost always '0' except for '1' pulse per averaging period (FOSR=10) (see the "Input" curves on *Figure 8* and on *Figure 9*). Two input streams are tested: one stream with exactly equidistant pulses (at position 10, 20 and

AN4990 Rev 1 15/56

- 30 on horizontal axis see *Figure 8*) and another stream where the second pulse is anticipated by one period to simulate a slightly higher pulse density (position 10, 19 and 29 on horizontal axis, see *Figure 9*).

- The first order filter stage is performing moving average (see the "1st order" curves) and the final result is sampled at each FOSR cycle and constitutes the 1st order filter result (at 10th, 20th, 30th cycle). It always produces '1' as the final result on both stream cases (*Figure 8* and *Figure 9*) because of simple moving average in 1st filter stage (only one '1' in each period).

- The second order filter stage is performing moving average on samples from first filter order stage (see the "2<sup>nd</sup> order /10" curves). The final result is sampled at each FOSR cycle and constitutes the 2<sup>nd</sup> order filter result (at 20<sup>th</sup>, 30<sup>th</sup> cycle). There is a visible difference in the final results between the two output streams (*Figure 8* and *Figure 9*): due to higher density of '1s' (with the higher density stream of *Figure 9*) it produces higher value than with the lower density stream of *Figure 8*).

- The third order filter stage is performing moving average on samples from the second filter order (see the "3<sup>rd</sup> order /100" curves). The final result is sampled at each FOSR cycle and constitutes the 3<sup>rd</sup> order filter result (at 30<sup>th</sup> cycle). There is a visible difference in the final result between the lower density stream (*Figure 8*) and the higher density stream (*Figure 9*). Due to moving averaging the third output is smoother and more precise.

- The dynamic range of the signal at the output of the filter is FOSR<sup>FORD</sup> but requires FORD x FOSR samples before obtaining the first result because every filter stage must be filled with valid samples from previous filter stage (see *Figure 8* and *Figure 9*). In conclusion, higher order filters offer better resolution for a given stream duration or the same resolution for shorter stream duration. The drawback is a more complex hardware design and a longer initialization time for the filter.

Figure 8. Example of 3<sup>rd</sup> order filter outputs with one bit per filter length

Figure 9. Example of 3<sup>rd</sup> order filter outputs with higher density of input pulses

# 3.3 Hardware design of Sinc filter

Sinc filters are characterized by a Sinc transfer function which equation in the digital domain is provided below. It can be interpreted as multiple moving average of input 1-bit data. The rest of this section focuses on finding simplifications in order to achieve an efficient and ultimately guite simple hardware implementation.

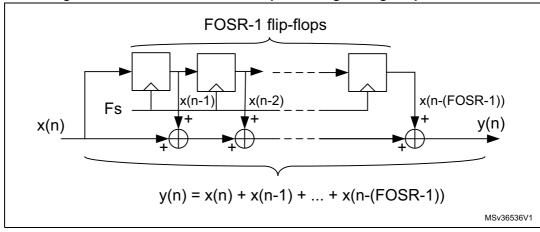

Equation 1:

$$y(n) = x(n) + x(n-1) + x(n-2) + ... + x(n - (FOSR - 1))$$

Where:

x(n) is the input of  $n^{th}$  sample

y(n) is the output of n<sup>th</sup> sample

*Figure 10* provides the straight forward translation of the above equation into a hardware implementation:

AN4990 Rev 1 17/56

Figure 10. Basic schematic for simple moving average implementation

The above hardware implementation required (FOSR -1) adders and (FOSR-1) flip-flops. Some simplifications can be introduced that are developed hereafter.

The Equation 1: can be simplified by using previous output result y(n-1):

Equation 2:

$$y(n) = x(n) + y(n-1) - x(n-FOSR)$$

Equation 3:

$$y(n) = x(n) - x(n - FOSR) + y(n - 1)$$

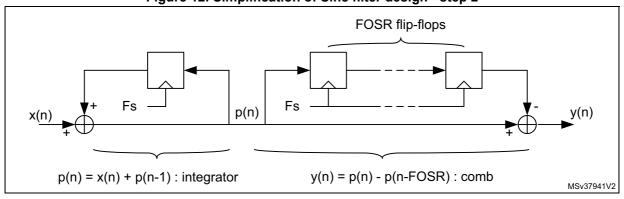

*Figure 11* provides a simplified schematic requiring only 2 adders and FOSR+1 flip-flops. The schematic can now be divided into two parts: comb and integrator.

FOSR flip-flops x(n) = x(n) - x(n-FOSR) : comb y(n) = y(n) + y(n-1) : integrator y(n) = y(n) + y(n-1) : integrator

Figure 11. Simplification of Sinc filter design - step 1

A further simplification can be obtained by converting the equation to Z-domain (frequency domain) according these correspondences:

- X(z) in the Z-domain corresponds to x(n) in the discrete time domain, where n is an

integer number of sample clock periods (sample clock period = 1/Fs; Fs = sampling

frequency)

- $z^{-N} \times X(z)$  corresponds to x(n-N) that is x(n) delayed by N sample periods.

**47**/

The equation for a 1<sup>st</sup> order Sinc filter in Z-domain becomes:

$$Y(z) = X(z) - z^{-FOSR} \times X(z) + z^{-1} \times Y(z)$$

The corresponding transfer function H(z) is:

$$H(z) = \frac{Y(z)}{X(z)} = \frac{1 - z^{-FOSR}}{1 - z^{-1}}$$

In *Figure 11* we introduced a decomposition of the Sinc filter in two stages: "comb" and "integrator". The transfer function of such filter (called CIC: cascaded integrator-comb filter) is given by:

The comb transfer function in Z-domain:

$$H_C(z) = \frac{P(z)}{X(z)} = 1 - z^{-FOSR}$$

The integrator transfer function:

$$H_I(z) = \frac{Y(z)}{P(z)} = \frac{1}{1 - z^{-1}}$$

The overall transfer function is equivalent to the Sinc filter transfer function:

$$H_{C}(z) \cdot \ H_{I}(z) = \frac{P(z)}{X(z)} \cdot \ \frac{Y(z)}{P(z)} = (1 - z^{-FOSR}) \cdot \ \left(\frac{1}{1 - z^{-1}}\right) = \frac{1 - z^{-FOSR}}{1 - z^{-1}} = \ H(z)$$

One more filter simplification consists in permuting the comb and the integrator operation as shown in *Figure 12*:

$$H(z) = H_I(z) \cdot H_C(z) = \left(\frac{1}{1 - z^{-1}}\right) \cdot (1 - z^{-FOSR})$$

Figure 12. Simplification of Sinc filter design - step 2

Because the filtering limits the output signal bandwidth, it is possible to down-sample the output y(n) by a factor FOSR. This down-sampling is achieved by taking one sample of y(n) every FOSR clock cycles (see *Figure 13*).

57

AN4990 Rev 1

FOSR flip-flops

x(n) Fs Fs/FOSR

MSv36539V1

Figure 13. Simplification of Sinc filter design - step 3

The down-sampled clock period is defined as:

$$T = \frac{FOSR}{F_s} = FOSR \cdot \tau$$

where:  $: \tau = \frac{T}{FOSR}$

The equation for the down-sampled comb section can be re-written as follows:

$$\begin{split} y(n \cdot \ \tau) &= p(n \cdot \ \tau) - p(n \cdot \ \tau - FOSR \cdot \ \tau) \\ y\left(\frac{n \cdot \ T}{FOSR}\right) &= p\left(\frac{n \cdot \ T}{FOSR}\right) - p\left(\frac{n \cdot \ T}{FOSR} - \frac{FOSR \cdot \ T}{FOSR}\right) \\ y(m) &= p(m) - p(m-1) \qquad \text{where: } : m = \frac{n}{FOSR} \end{split}$$

This operation corresponds to a down-sampling of p(n) by the factor FOSR, followed by a first order differentiator. The series of flip-flop sampled at high frequency can be replaced by one single flip-flop with down-sampled frequency. The final schematic is shown on *Figure 14*.

An effect of down sampling is to eliminate the moving average operation (because the output data rate is reduced).

x(n) Fs/FOSR p(m) Fs/FOSR p(m) p(m)

Figure 14. Simplification of Sinc filter design - step 4

The final schematic (*Figure 14*) is reduced to 2 flip-flops and 2 adders (all with FOSR-bit width).

Higher order Sinc filters are obtained as a serial cascade of first order filter stages where comb and integrator stages can be grouped together (*Figure 15*).

K integrator stages

K differentiator stages

x(n) Fs/FOSR

Fs/FOSR

MSv36541V1

Figure 15. Higher order Sinc filter implementation

The transfer function of a higher order Sinc filter (with filter order = FORD) is provided by:

Cascading FORD first order filters:

$$H(z) = \left[ \left( \frac{1}{1-z^{-1}} \right) \cdot (1-z^{-FOSR}) \right] \cdot \left[ \left( \frac{1}{1-z^{-1}} \right) \cdot (1-z^{-FOSR}) \right] \dots$$

Reordering:

$$H(z) = \left[ \left( \frac{1}{1 - z^{-1}} \right) \cdot \left( \frac{1}{1 - z^{-1}} \right) ... \right] \cdot \left[ (1 - z^{-FOSR}) \cdot (1 - z^{-FOSR}) ... \right]$$

· Final equation:

$$H(z) = \frac{Y(z)}{X(z)} = \left(\frac{1 - z^{-FOSR}}{1 - z^{-1}}\right)^{FORD}$$

The down-sampling is performed at the output of the final integrator stage, allowing to replace each comb stage with a unity delay differentiator at the down-sampled rate (see *Figure 15*).

Note:

The Sinc filter implementation can be extended to multi-bit width input signal (for example for parallel data input instead of serial data input). In this case the bit-width of flip flops and adders should be extended.

# 4 DFSDM peripheral operation

# 4.1 Block diagram

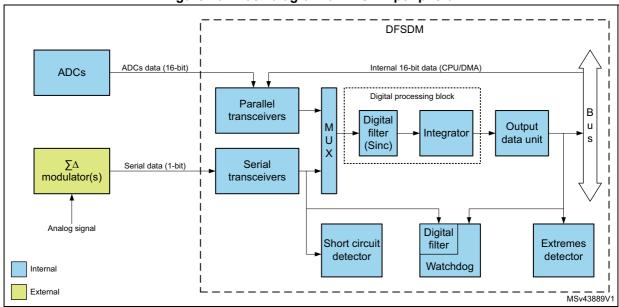

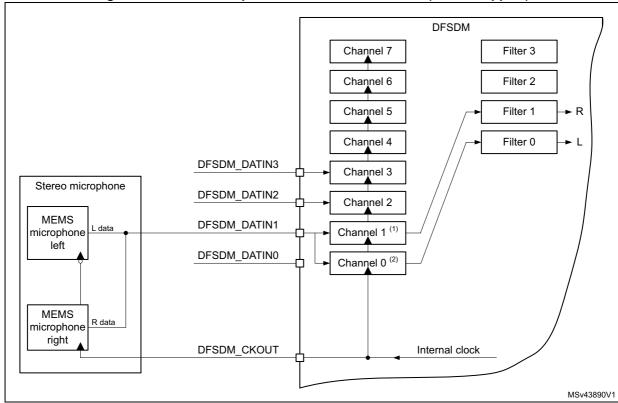

The block diagram of the DFSDM peripheral with all the internal functional blocks and their internal and external connections is provided on *Figure 16*. The DFSDM cannot be reduced to only a digital filter but consists in a complete digital peripheral that handles the overall A/D conversion (when associated with an external sigma-delta modulator).

Figure 16. Block diagram of DFSDM peripheral

# 4.2 DFSDM components

#### 4.2.1 Serial transceivers

The "serial transceivers" block receives serial data from the external sigma-delta modulator. It features SPI and Manchester serial protocol formats with configurable rising/falling sampling clock edge in order to support most of the sigma-delta modulator types. It supports as well the PDM signal format used by digital microphones - see *Figure 28: MEMS microphone connection to DFSDM (stereo support)*.

Up to two digital microphones (configured as stereo microphone) can be connected to one DFSDM\_DATINy pin. In this case, each microphone is configured to be sensitive to a different sampling clock edge (the signals from both microphones are present on a single DFSDM\_DATIN data line). In order to distribute this composite signal to two different channels, both channels must be configured to take their serial input from the same pins (DFSDM\_DATINY, DFSDM\_CKINY) where the two microphones are physically connected (see *Figure 28: MEMS microphone connection to DFSDM (stereo support)*). Each channel is then configured to sample the data on a different sampling edge.

An external clock signal can be connected to DFSDM\_CKINy pin (assuming sigma-delta modulator provides this clock signal) or the clock signal can be taken from the internal clock

generator (assuming sigma-delta modulator needs external clock signal). The internal clock generator drives the sigma-delta modulator through DFSDM\_CKOUT pin. The Manchester format protocol does not require external clock signal because this protocol is single-wire (on DFSDM\_DATINy pin) and clock signal is reconstructed from Manchester coded stream. There is a clock signal presence detector that can be used in case of missing clock (external hardware failure) to trigger an interrupt.

The serial transceiver provides also a "Pulse skipper". The Pulse skipper allows to pause the output of the serial transceivers during a given number of sampling clock pulses (given count of 1-bit data samples are discarded). In practice, the "Pulse skipper" is used in beamforming applications in order to delay one channel data with respect to another channel data. Beamforming is a technique that consists in sensing signals (sounds) from a preferred direction by using an array of detectors (microphones). A delay is injected to each microphone signal relative to the previous microphone signal. The delay defines the preferred sensing angle.

#### 4.2.2 Parallel transceivers

The parallel transceiver is an internal 16-bit parallel input register which can be accessed through the APB bus by the CPU, the DMA, or directly by the internal ADC. Its function is to allow post processing (filtering) of internal signals. Examples of usage:

- Filtering data captured by internal ADC

- Filtering data captured by SPI peripheral (through memory buffer)

- Filtering any 16-bit data stored in memory buffer (DMA transfer to DFSDM parallel transceiver).

# 4.2.3 Digital filter

The digital filter is a key component that processes the input data. The digital filter is configurable to support final application needs (speed, resolution). The following parameters can be configured:

- Filter order: Sinc1 ... Sinc5, FastSinc

- Oversampling ratio:

- FOSR = 1 ... 1024 (for Sinc1 ... Sinc3, FastSinc)

- FOSR = 1 ... 215 (for Sinc4)

- FOSR = 1 ... 73 (for Sinc5)

The FOSR ranges provided above take into account the filter order and the filter internal resolution (32-bit width) in order to avoid overflow (case of a 1-bit input signal, for multi-bit parallel input signal the ranges are reduced).

# 4.2.4 Integrator

The optional integrator works as a simple adder. It sums up a given number of samples provided by the filter output. The number of filter output samples that are summed to provide the single integrator output is configurable in the range IOSR = 1 ... 256. The integrator works like a Sinc1 filter (it is performing the average of a given number of samples).

# 4.2.5 Output data unit

The output data unit performs a final correction that consists in shifting the bits to the right and applying an offset correction on the data coming from the integrator.

AN4990 Rev 1 23/56

Shifting bits to the right is used to:

- fit the 32-bit internal output into the final 24-bit register

- limit even more the final resolution (to 16-bit for instance in case of audio data)

The offset correction allows to calibrate the external sigma-delta modulator offset error. The user configures the offset register with a signed 24-bit correction, and this register is automatically added to the output result. The offset correction value is usually the result of a calibration routine embedded within the microcontroller software that performs the offset calibration calculation and stores the correction into the offset register.

All operations in the DFSDM peripheral are in signed format (filtering, integration, offset correction, right bit shift).

#### 4.2.6 **Analog watchdog**

The analog watchdog function is the same as in the ADC peripheral. Its purpose is to control that the ADC data excursion stays within given limits by triggering the microcontroller CPU (interrupt) or other peripherals (break signal) when the signal exceeds predefined thresholds.

Not only the DFSDM output data but also the raw data from the sigma-delta modulator (serial transceiver output) can be monitored.

The analog watchdog can monitor serial data directly from the serial transceiver through a dedicated configurable digital filter (FOSR = 1...32, FORD = 1...3). This gives the user the ability to find the best compromise between monitoring speed and monitoring resolution, independently from the main data conversion speed. Some applications require that the reaction time to an input signal exceeding the thresholds, be faster than the main conversion speed. The monitoring of the thresholds for the main conversion itself is usually more precise but slower.

#### 4.2.7 Short circuit detector

The short circuit detector is designed for very fast detection of sudden analog input signal saturation, when the signal is over or under the maximum allowed range. In normal situation the analog input signal gain is controlled (current or voltage sensing loop) in order to never reach such saturation levels. In some extreme situations (like a short circuit) the sensed signal measurements can exceed the operating range limits. In this case the reaction time must be as fast as possible (to switch off the supply for instance).

This very fast detection is implemented in the short circuit detector. The detection of signal saturation is based on the analysis of the 1-bit data stream coming from the serial transceiver. A typical sigma-delta modulator outputs a 1-bit signal with frequent transitions between '0' and '1' (to reproduce the analog signal fluctuations). When a saturation of the input signal occurs the output from the sigma-delta modulator gets stuck with either long series of logical '0' (signal under negative threshold) or long series of logical '1' (signal above positive threshold). If this situation exceeds a certain duration the short circuit detector triggers a "short circuit" event. The duration threshold to trigger a detection can be set in the DFSDM short circuit detector threshold setting (SCDT) in the range 1 to 256 input sample counts. For example if SCDT=100 the short circuit detector event is triggered as soon as at least 100 consecutive '0' or '1' are detected in the input 1-bit data stream. The short circuit detector can trigger an interrupt (software intervention) or activate a break signal (fast hardware intervention).

This type of short-circuit detection is much faster than the detection based on analog watchdog involving digital filtering over longer series of 1-bit input samples.

#### 4.2.8 Extremes detector

The extremes detector simply analyzes the final output data samples and stores the minimum and maximum values into extremes registers. By reading those extremes registers it is possible to monitor the maximum and minimum level of the converted signal during a period of time. Those levels are useful inputs for software post processing, for example for signal normalization or for automatic gain control. Each time the extremes registers are read, they are re-initialized with their reset values and the extremes detection is restarted.

# 4.3 DFSDM simulation

The sigma-delta modulator and the DFSDM internal blocks behavior are modeled within *[TUTORIAL]*. The incidence of the input signal and the influence of the DFSDM parameters can be simulated and both the internal and output signals can be observed and analyzed.

The proposed simulations cover:

- Sigma-delta modulator (principle of operation demonstration)

- Sinc filter + integrator (digital filter functionality demonstration)

- Frequency characteristics of Sinc filters (LP filters shape demonstration)

- FFT of PWM and sigma-delta signals (noise shaping demonstration)

- High order filters operation (demonstration of resolution increase by multiple signal average)

- Delta-sigma modulator (DAC converter)

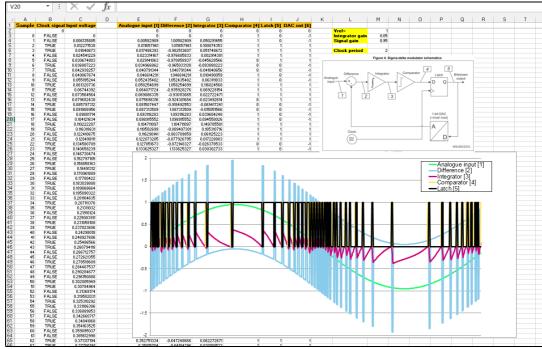

### 4.3.1 Sigma-delta modulator principle

This simulation is provided in the first worksheet of [TUTORIAL].

The simulation of the first order sigma-delta principle is based on the schematic provided in *Figure 4: Sigma-delta modulation principle* where each block has been modeled. The input signal to the modulator corresponds to one period of a sinewave signal. For each observation point (as referenced on *Figure 4*) corresponds a curve in the chart provided in *Figure 17*.

The user can modify the input signal shape or modify some parameters of the modulator (integrator gain,  $V_{ref}$  level) and visualize the impact on the digital output of the sigma-delta modulator.

This simulation illustrates the principle of the sigma-delta modulator and allows to visualize the internal signal at different stages of the processing.

Here the sigma-delta modulator is modeled as a first order, in order to explain the basic principle. In practice most sigma-delta modulators are using 2<sup>nd</sup> order with the exception of digital microphones that are typically using 4<sup>th</sup> order.

AN4990 Rev 1 25/56

Figure 17. Sigma-delta modulator simulation

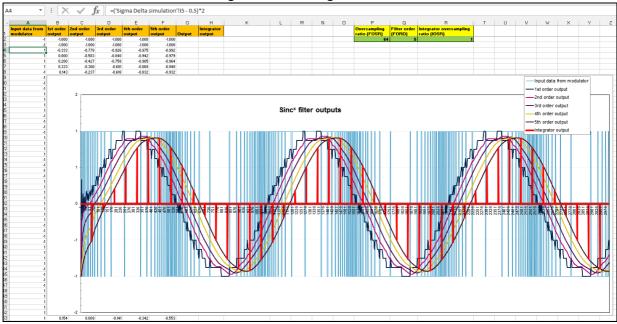

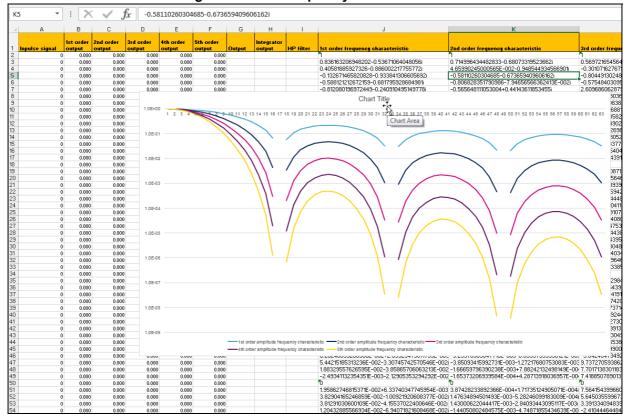

# 4.3.2 DFSDM filtering simulation (filter and integrator)

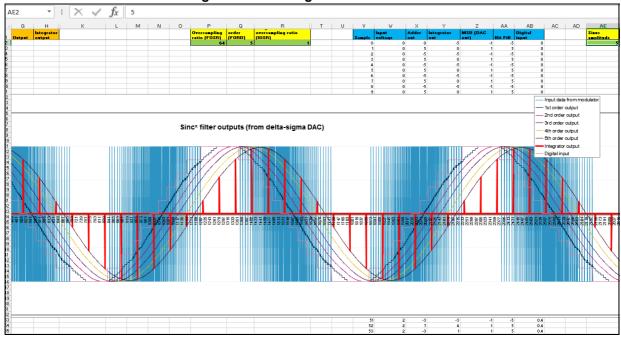

This simulation is provided in the second worksheet of [TUTORIAL]. This part of the DFSDM simulator corresponds to the Sinc filter and the integrator stages (see Section 4.2.3: Digital filter and Section 4.2.4: Integrator for details).

Both the Sinc filter and the integrator models are built within [TUTORIAL] and can be simulated. The user can change the FORD and FOSR parameters for the filter and the IOSR parameter for the integrator. The simulation results are identical to the results obtained with the actual DFSDM block. The user can tune in simulation the filter and the integrator parameters according to his application and observe the impact on the output signal shape without waiting for the actual prototypes.

This simulation requires a digital signal input (1-bit data stream) from the sigma-delta modulator (like in real application). In this particular simulation, the input is provided by the results of the first order sigma-delta modulator simulation also available in [TUTORIAL] (see Section 4.3.1: Sigma-delta modulator principle). By doing so, it is possible to compare the output digital signal (DFSDM filtering simulation curve) with the input analog signal applied to the sigma-delta modulator. The filter parameters should then be adjusted in order to reach the application requirements in term of acceptable error between the analog input signal into sigma-delta modulator versus the output digitized signal from the DFSDM (final output samples).

*Figure 18* provides not only the output curve (FORD = 5) but also the internal data results at the output of each filter order. It shows the resolution gain that is obtained by performing more moving average loops.

Figure 18. Filtering simulation

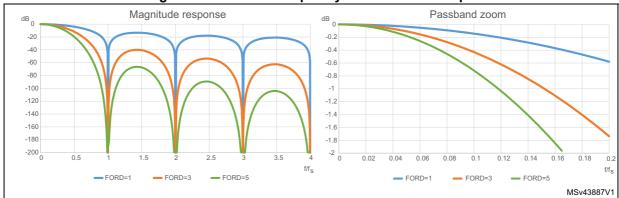

### 4.3.3 Frequency characteristics for Sinc filter

This simulation is provided in the third worksheet of [TUTORIAL]. It allows to visualize the frequency characteristics of the Sinc filter depending on the filter order.

The frequency characteristics of a filter can be determined by applying an impulse signal at the input of the filter and by computing the FFT transform of the impulse response at the output of the filter. This is how the filter characteristics have been computed in the simulation model. The model calculates the impulse response of the filter and submit the result to a 512-point FFT transform. The results for different filter orders are available in [TUTORIAL] and provided in Figure 19.

The frequency response has a comb shape with periodic attenuation points (notches - also called "zeroes") and a decreasing trend for higher frequencies (low pass filtering). The frequency of the first notch depends on the selected FOSR and is given by  $f_{\text{sampling}}/\text{FOSR}$ . In case of continuous sampling,  $f_{\text{sampling}}/\text{FOSR}$  is also the output data rate frequency. The frequency components of the input signal corresponding to the notches are completely rejected by the filter. This property can be used in some applications to remove external noise from the input signal at predetermined frequencies. As an example, the long wires that sometime are necessary to connect distant sensors to the microcontroller are prone to collect noise from the power network (50/60Hz) that can be filtered according the above property.

Another property is that the attenuation of the higher frequencies (other than notches which frequency depends only on FOSR) is proportional to the filter order (FORD). So the higher the filter order, the more rejection on higher frequencies. In applications which are sensing quasi static signals (like temperature or pressure sensors) a high order filter (FORD) is recommended as well as a high oversampling ratio (FORD) to suppress noise from AC perturbations. A further filtering of quasi static signals can be done by using the integrator located after the filter. Increasing the integrator oversampling ratio (IOSR) allows to performs additional averaging of the signal. In practice, the user should first set a (high) FORD and then set correctly the FOSR and the IOSR to suppress the noise from mains

AN4990 Rev 1 27/56

frequency (50/60Hz). The first notch of the overall block consisting of [Sinc filter + integrator] is at frequency:  $f_{sampling}/(FOSR*IOSR)$ .

Figure 19. Filter frequency characteristics

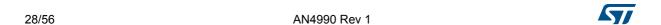

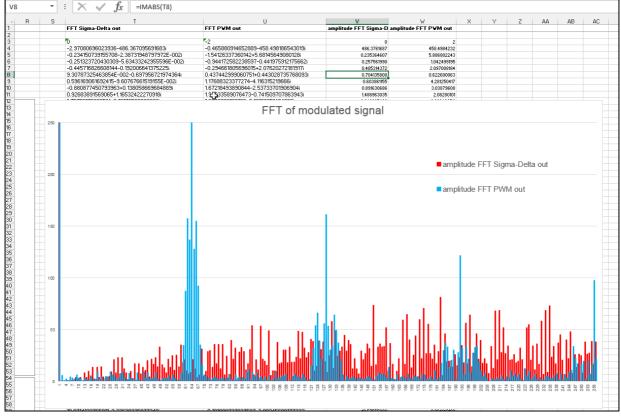

# 4.3.4 Noise shaping of sigma-delta modulation

This simulation is provided in the fourth and the fifth worksheets of [TUTORIAL]. It compares the spectrum of a PWM modulated signal with the spectrum of a sigma-delta modulated signal and highlights the benefits of the later with respect to noise shaping. The same input signal (one period of a sinus wave, see Figure 20) is either sigma-delta modulated or PWM modulated before undergoing an FFT transform. The frequency spectrum of both the PWM modulated signal and the sigma-delta modulated signal are compared in Figure 21. The X-axis represents the frequency in multiple of the base signal frequency (signal base frequency and its harmonics), the Y-axis represent the spectrum density. Logically, the amplitude of the spectrum at index 1 (signal base frequency) is very large (~470). All the other peaks located at indexes > 1 would have to be filtered out in order to reconstruct the original signal.

fx S20 -1

-0.866666667

-0.73333333

-0.6

-0.466666667

-0.333333333

-0.2

-0.066666667 TAUSE TRUE FALSE TRUE original Sigma-delta modulated ₩;

Figure 20. Sigma-delta and PWM modulated signals (for frequency spectrum comparison)

AN4990 Rev 1 29/56

Figure 21. Spectrum of sigma-delta signal and PWM signal

Figure 21 illustrates the fact that a PWM signal spectrum concentrates its energy on peaks located around multiple of the modulation frequency (modulation frequency = 16 x signal base frequency in this case). This is due to the characteristics of a PWM modulation that has a constant modulation frequency and a variable duty cycle. The amplitude of the peaks decreases with frequency increase.

On the opposite a 1<sup>st</sup> order sigma-delta modulation spectrum shows an amplitude that is low on the first harmonics, and then increases progressively with the frequency.

As a consequence of the previous observations, the requirements on the low-pass analog filter that is necessary to reconstruct the original signal (sinewave signal at index 1 on *Figure 21*) are lower for a sigma-delta modulated signal than for a PWM modulated signal. The low-pass filter (analog filter) must be designed with a cut-off frequency slightly higher than the useful analog bandwidth of the original signal to be observed, and must be sharp enough to sufficiently suppress all the higher frequency components resulting from the signal modulation. Because the PWM signal has more unwanted energy concentrated at lower frequency than the sigma-delta modulated signal, the low pass analog filter must be sharper (higher order analog filter).

Another particularity of the sigma-delta modulated signal is that the quantization noise on the lower part of the spectrum is almost constant and independent from the input signal resolution whereas for a PWM modulated signal, a degradation of the quantization noise affects the entire spectrum, and predominately the first harmonic. This higher sensitivity of the PWM modulated signal to a degradation of the quantization noise is put in evidence by decreasing the input signal magnitude from 95% of full scale (*Figure 21*) down to 10% of full scale (*Figure 22*).

Figure 22. Spectrum of sigma-delta signal and PWM signal with signal amplitude reduced to 10% of full scale

# 4.3.5 High order filters operation

This simulation is provided in the sixth worksheet of [TUTORIAL]. It shows how it is possible to increase the filter output resolution by the technique of multiple averaging of the same data (principle of the high order filters).

For this simulation the averaging period is 10 samples (FOSR=10). Over the averaging period the input signal consists of a single pulse (one sample at 1 and the nine other samples at 0). Multiple averaging is performed. Two different cases are observed (see *Figure 23*):

- 1. Equidistant pulses occurring at 10<sup>th</sup>, 20<sup>th</sup> and 30<sup>th</sup> sample. This situation correspond to a constant density signal.

- 2. Non-equidistant pulses occurring at 10<sup>th</sup>, 19<sup>th</sup>, 29<sup>th</sup> sample. This situation correspond to a signal with varying density.

AN4990 Rev 1 31/56

Figure 23. High order filters - multiple averaging principle

The results are presented for both input signal cases, and for 1, 2 or 3 averaging (similar to filter orders FORD=1, FORD=2, FORD=3). The final output is sampled at every 10<sup>th</sup> sample period (end of average period).

In the first case, since the input pulses are at equidistant intervals (every 10<sup>th</sup> sample), the output (sampled at 10<sup>th</sup>, 20<sup>th</sup>, 30<sup>th</sup> sample) is always 1.00, whatever the filter order.

In the second case, the input pulses are a little bit closer (pulses at 10<sup>th</sup>, 19<sup>th</sup> and 29<sup>th</sup> sample), so the pulse density is slightly higher. It has no impact on the simple averaging filter that provides the same result 1.00 (constant over the 1<sup>st</sup>, 2<sup>nd</sup>, 3<sup>rd</sup> averaging period) as in the first case. This is because it performs averaging over one period only (10 samples). That means the first order filter is not able to detect changes in pulse density (or a filter with higher FOSR must be designed, with slower data rate).

The double averaging is a bit different. The first valid result is present on the output after the  $2^{nd}$  averaging period because the double averaging uses 2 periods of signal to build one final sample. The results from this double averaging are: 1.10 (result after  $2^{nd}$  period) and 1.00 (result after  $3^{rd}$  period). That means the second order filter is able to detect the increase of pulse density during the  $2^{nd}$  averaging period of the signal and the decrease of the pulse density during the  $3^{rd}$  averaging period.

The triple averaging gives even more precision. The first valid result is present on the output after the 3<sup>nd</sup> averaging period because the triple averaging uses 3 periods of signal to build one final sample. The results from this triple averaging is: 1.08 (result after 3<sup>rd</sup> period). That means the third order filter gives even more precision on the pulse density.

# 4.3.6 Delta-sigma DAC simulation

This simulation is provided in the seventh worksheet of [TUTORIAL]. The sigma-delta modulation can be used not only for ADC conversion but also for DAC conversion. In this case, all analog blocks of the sigma-delta modulator diagram (see Figure 4: Sigma-delta modulation principle) are replaced by their digital equivalent (Figure 24).

Low pass Comparator Flip-flop Substract Integrate filter Extract D Q Analog output Digital input MSB Q[N:1] D[N:1] Clock Bit fill MSv43891V1

Figure 24. First order delta-sigma DAC principle

Here are the particularities of each block in the digital domain:

- The "Subtraction" block is a digital operation.

- The "Integrator" block is also a simple accumulate operation (sum of incoming bits).

- The "Comparator" block is a digital comparator. It determines the sign of the digital data word coming from the integrator (most significant bit = sign bit).

- The "Bit fill" block is the equivalent of the 1-bit DAC used in *Figure 4: Sigma-delta modulation principle*. It is replaced by an ADC which output is ±digital\_reference\_word according the sign provided by the comparator output. The magnitude of "digital\_reference\_word" should correspond to the input range of the digital signal into the comparator (equivalent to +V<sub>ref</sub>, -V<sub>ref</sub> for sigma-delta converter).

- The "Low pass filter" block is an analog filter which performs analog filtering of the fast 1-bit digital stream. The fast 1-bit digital stream represents the sigma-delta signal and in this case is built from the parallel N-bit width digital input signal (delta-sigma modulator). The 1-bit digital stream has the same properties as a 1-bit digital stream in the sigma-delta modulator (noise shaping) and can be filtered with a simpler analog filter (with respect to PWM signal).

The simulation of this delta-sigma DAC gets a digitized sinewave signal with amplitude +/-5 as an input (see "Digital input" pink-color signal on *Figure 25*). In a real application, the fast 1-bit digital stream output (blue signal on *Figure 25*) should undergo an analog low-pass filtering. For the need of the simulation, the analog low pass filtering is replaced by a digital Sincx filter.

AN4990 Rev 1 33/56

Figure 25. Delta-sigma DAC simulation

The final delta-sigma DAC output (see the various order outputs on *Figure 25*) show a quite well reconstructed "analog" sinewave despite the digital input sinewave quantization uses only 11 discrete levels [-5,...,+5]).

Once again the advantage of using a sigma-delta versus a PWM modulation is a simpler low-pass filtering (analog in the case of the DAC) of the output signal. This is for the same reason as the one developed in *Section 4.3.4: Noise shaping of sigma-delta modulation*.

# 4.3.7 High pass filter simulation

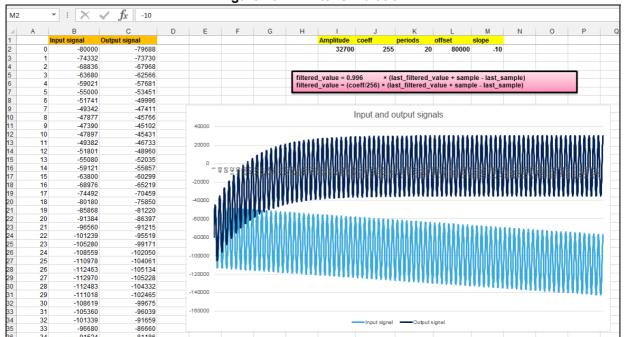

This simulation is provided in the eighth worksheet of [TUTORIAL]. High-pass filters are useful in many applications where the DC component and/or low frequency noise need to be removed from the input signal (audio applications including static pressure changes in microphone output, AC energy measurement, DC offset which vary with temperature, ...).

The DFSDM does not implement any high pass filtering but it can be easily implemented in software as a post processing over the DFSDM sampled data (as an alternative to the use of an external hardware high-pass filter).

The high-pass filter used in the simulation is modeled by the following equation:

```

y(n) = (coeff / 256) \times (y(n-1) + x(n) - x(n-1))

```

with

y(n): = "filtered value" in the simulation (filter output)

coeff: = "coeff" in the simulation (filter cutoff frequency)

$y(n-1) = \text{``last\_filtered\_value''} \text{ in the simulation (previous filter output)}$

x(n) = "sample" in the simulation (filter input sample)

x(n-1) = "last\_sample" in the simulation (filter previous input sample)

The complexity of this filter reduces to one multiplication, two additions and one shift operation (/256).

For the simulation a sinewave with a decreasing DC offset is applied to the high-pass filter (light blue curve in Figure 26).

Figure 26. HP filter simulation

The high-pass filter output is represented by the dark blue line in Figure 26. After an adaptation period, the high-pass filter suppresses the DC and the low frequency content. The speed of adaptation depends on the "coeff" value (cut-off frequency of the filter).

#### Additional functions in DFSDM 4.4

#### 4.4.1 Digital microphones (MEMS) support

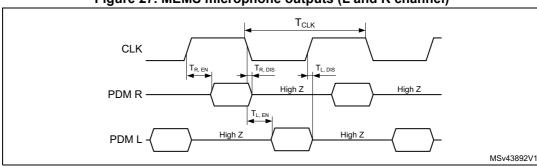

Standardization in the domain of audio application has specified a PDM modulation (pulse density modulation) that is a common output format for digital microphones. A PDM signal is equivalent to a sigma-delta modulated signal and is therefore supported by the DFSDM.

Digital microphones are MEMS devices (micro electro mechanical systems) which are manufactured using semiconductor type of technology. The active actuator of such microphones consists in a membrane and a pair of micro electrodes. One of the electrode is fixed, the other one is incorporated within the membrane. As the air pressure (sound) is applied to the membrane, it moves the mobile electrode away from its default position and produces a change of capacity between both electrodes. The induced signal is processed by built-in electronic and output as a PDM modulated signal (pulse density modulation).

The digital microphones require an external clock signal (microphone CLK input signal) and data are sent over a DATA output line as a PDM modulated signal. The clock speed is usually in the range 1 to 3.2 MHz. The clock signal is provided by the DFSDM\_CKOUT output signal and defines the microphone output data rate into the DFSDM. A schematic of a typical connection between a stereo digital microphone and the DFSDM is provided on Figure 28.

AN4990 Rev 1 35/56 The DFSDM allows to connect 2 microphones in parallel through one single line (stereo configuration: left and right channel). The data and clock signals are common for both microphones. The clock signal is distributed from DFSDM\_CKOUT pin to the left and right microphones. The output data signals from both microphones are multiplexed on the same wire: the left microphone provides data on the rising clock edge and the right microphone provides data on the falling clock edge (see *Figure 27*). The configuration of microphone for left or right channel is usually done configuring a pin on the microphone (L/R selection pin).

Figure 27. MEMS microphone outputs (L and R channel)

Figure 28. MEMS microphone connection to DFSDM (stereo support)

- 1. Direct input, falling edge sampling (R data).

- 2. Redirected from next channel, rising edge sampling (L data).

The separation of the two microphone signals on the DATA wire is performed by the DFSDM. The input to DFSDM channel x can be redirected in order to take the same input as channel (x+1). Then channel x is configured to sample data on rising edge and channel (x+1) is configured to sample data on falling edge. The clock signal for both channels is the

same and internally connected to DFSDM\_CKOUT signal. With such configuration, channel x is receiving data from left microphone and channel (x+1) is receiving data from right microphone. Both channels feed their own digital filters which eventually output two separate parallel data flows for left and right microphone channels. See *Figure 28* for a complete diagram of a stereo microphone application using the DFSDM.

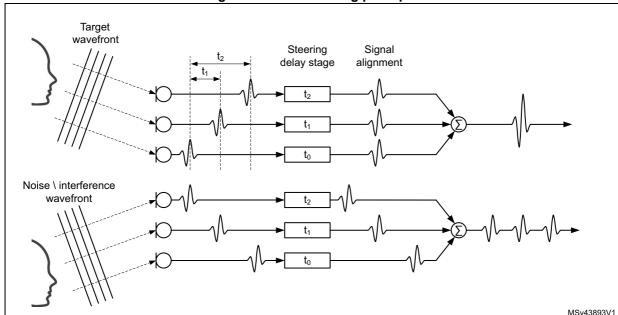

### 4.4.2 Beamforming support

Beamforming is a technique giving to an array of fixed multi-directional sensors the ability to favor the signals coming from a particular direction (array of microphones in the example below). The preferred direction can be changed by firmware (without changing the position of the sensors).

In the example below, an array of microphones are positioned on a line with equidistant spacing (see *Figure 29*). An audio source is placed in front of the microphone array at an arbitrary angle, while at the same time unwanted noise and interferences are present all around. If signals from all microphones are simply summed together then only the sounds coming perpendicularly to the array are coherently summed (and therefore amplified). The sounds coming from non-perpendicular directions are not coherently summed.

Figure 29. Beamforming principle

In order to amplify the signals coming from another direction than perpendicular, one solution would be to mechanically rotate the microphone array, another solution consists in adding a specific delay to each microphone in the array, so that the various propagation delays of the useful signal arriving through each microphone are all compensated at the input of the adder. When the delay lines of all microphone are adjusted, only the sounds coming from the direction of the useful source are in phase and amplified (coherent combination), the sounds coming with a different angle are less amplified (incoherent combination) (see *Figure 29*).

The above description of beam forming algorithm is a introduction (simplified view). More elaborated algorithm can be implemented, providing even better performances.

Beamforming can be achieved with the DFSDM as follows. The DFSDM is able to sense signals coming from several microphones and process them separately to provide parallel outputs samples. The output samples from the different microphones are stored into separate data buffers in the microcontroller memory (for example 4 memory buffers from 4 microphones). The samples are then summed together by the microcontroller in order to provide the final output. The delay line is realized in 2 steps:

- 1. Coarse step: a DFSDM output buffer (for a given microphone) can be shifted with respect to another by a given number of samples (one sample corresponds to a delay of 1/f<sub>datarate</sub>, where f<sub>datarate</sub> is the output data rate (typical audio rates: 44.1kHz, 22.05kHz, 16kHz, ...). A shift of 1 sample corresponds to a propagation distance of the sound in the air of s = v / f<sub>datarate</sub> (v is the sound speed in air ~343m/s). Example of coarse step:

- fdatarate = 44.1 kHz: s = 343 / 44100 = ~7.8 mm

fdatarate = 16 kHz: s = 343 / 16000 = ~21.4 mm

- 2. Fine step: in order to support short distances between microphones in the array and to be able to fine tune the angle of the preferred sound source, a finer step is required. This is achieved by shifting samples on the 1-bit data stream between the microphone and the DFSDM rather than shifting DFSDM output samples in memory. The input 1-bit samples are sampled at PDM frequency. Here are examples of fine step distances:

```

- f<sub>PDM</sub> = 3 MHz: s = 343ms-1 / 3000000Hz = ~0.11mm

- f<sub>PDM</sub> = 200 kHz: s = 343ms-1 / 200000Hz = ~1.7mm

```

This range of values is compatible with the fine tuning of the preferred angle for sound reception even for miniature microphone arrays.

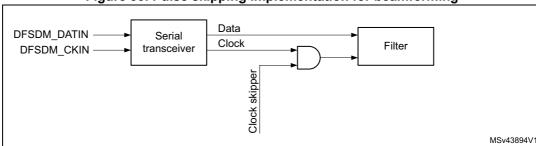

The DFSDM fine step circuitry used to fine tune beamforming is not based on delay lines but consists in skipping some samples of the input 1-bit stream. Some of the 1-bit samples coming from the serial transceiver are masked (by clock signal gating) and are not sent to digital filter. The principle based on skipping clock pulses is shown on *Figure 30*.

Figure 30. Pulse skipping implementation for beamforming

57

*Figure 31* provides an example that illustrates the pulse skipping mechanism and its similarity with a delay line.

Input samples (no sample skipping applied) 10 11 Left S10 S11 S12 S13 S14 S15 Right S9 S10 S11 S12 S13 S14 S15 S16 Output samples (FOSR=8) samole # Left S10 S11 S12 S13 S14 S15 S9 S10 S11 S12 S13 S14 S15 S16 Right S18 S19 like on Left channel => no delay line on Right like on Left channel => no delay line on Right like on Left channel => no delay line on Right Input samples (with 3 samples skipped on Left channel): 12 15 17 18 20 16 Left Right (3 samples delay applied) Output samples (FOSR=8) samole # Left Right like on Left channel => no delay line on Right delay line on Right channel delay line on Right channel channe

Figure 31. Pulse skipping example (FOSR=8)

The top part of *Figure 31* represents the normal operation, without clock skipping applied. Each output sample is built from 8 input samples (FOSR=8). For beam forming several DFSDM filters need to be started simultaneously.

On the bottom part of *Figure 31* samples S10, S11, S12 have been skipped on the Left channel. The filter (with configuration: FOSR=8) waits for 3 more samples in order to get 8 complete 1-bit samples for each channel and be able to build one output sample. From the filter output prospective, it seems like the Right channel uses older 1-bit input samples than the Left channel for the same final output sample index. This is the same behavior as if the Right channel would have a 3-samples delay line (the delay line buffers holding the last 3 samples).

The above description of beam forming algorithm is a introduction (simplified view). More elaborated algorithm can be implemented, providing even better performances.

#### 4.4.3 Audio clock support – independent clock operation

The DFSDM can clock an external sigma-delta modulator through a clock signal provided on the DFSDM\_CKOUT pin. The clock frequency on this pin determines the input sampling frequency from which depends also the output data rate frequency. It is possible to select among the following sources to drive the DFSDM\_CKOUT:

- DFSDM clock:

- APB clock

- System clock (independent from APB clock divider)

- PLL clock (audio PLL used for I2S)

The frequency from the selected clock source is divided by a factor in the range 2-256 (predivider ratio set according CKOUTDIV field in DFSDM\_CHyCFGR1 register) in order to provide the DFSDM\_CKOUT frequency.

AN4990 Rev 1 39/56

In order to achieve a fine tuning of the DFSDM\_CKOUT frequency, the PLL (providing both a multiplication and a division factor) must be selected as clock source. This is the appropriate selection for audio applications that require an accurate sampling frequency.

The DFSDM peripheral itself (transceivers, filters, additional functions) is using the APB clock or the system clock for digital processing. This "processing" frequency should be 4 times faster than the input sampling frequency (or 6 times if Manchester coding is used).

In order to save power consumption, both the sampling frequency and the processing frequency should be configured with the minimum values required by the application.