# STSPIN32F0 and STSPIN32G0 families overcurent protection

#### Introduction

The STSPIN32F0 and STSPIN32G0 families devices are a system-in-package providing an integrated solution suitable for driving three-phase BLDC motors using different driving modes. One of the integrated features of this device is overcurrent protection, which protects the application against damaging when high currents are reached.

The protection is implemented using an integrated comparator. The overcurrent event can be managed both by the gate driving logic and by the microcontroller, according to user selection.

This document gives an overview of the OC protection feature and explains how to connect the device families pins in order to implement the desired current threshold.

### 1 Overcurrent internal block diagram

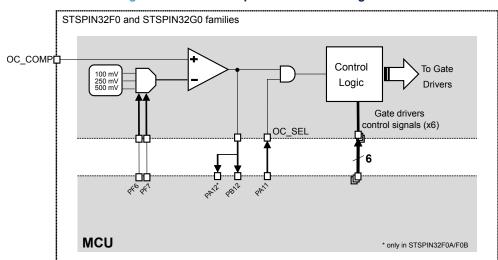

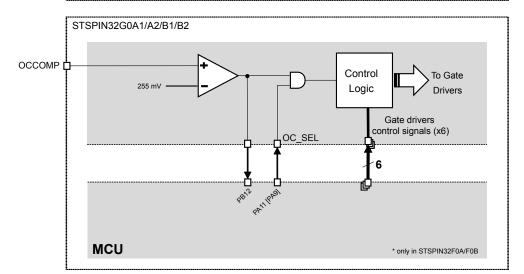

An internal block diagram of overcurrent protection is depicted in Figure 1. The voltage on the comparator input (OC\_COMP in STSPIN32F0 family and OCCOMP in STSPIN32G0 family) is compared with an internal threshold. In the STSPIN32F0 family, the overcurrent threshold is selectable by the MCU lines PF6 and PF7 (see Table 1); in the STSPIN32G0 family the threshold is instead fixed at 255 mV. When the threshold is exceeded, the OC comparator forces the output and then the PB12 and PA12 (only in STSPIN32F0A/F0B) lines of the MCU high. Depending on the status of the OC\_SEL signal (see Figure 1), the comparator output propagates to the control logic of gate drivers triggering the embedded protection. The OC protection implemented in the gate driving logic turns off the external high side power switches until all the high side driving inputs are low (refer to the device datasheet for more details).

Figure 1. Overcurrent protection block diagram

Table 1. OC threshold values (STSPIN32F0/F0A/F0B)

| OC_TH_STBY2 (PF6) | OC_TH_STBY1 (PF7) | OC threshold [mV] | Note         |

|-------------------|-------------------|-------------------|--------------|

| 0                 | 0                 | N.A.              | Standby mode |

| 0                 | 1                 | 100               | -            |

| 1                 | 0                 | 250               | -            |

| 1                 | 1                 | 500               | -            |

AN4999 - Rev 3 page 2/20

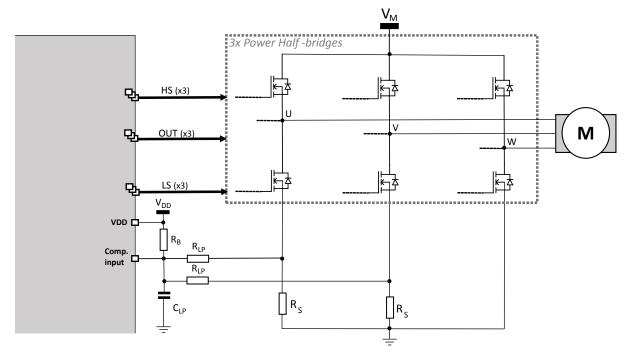

## Overcurrent detection in a single shunt topology

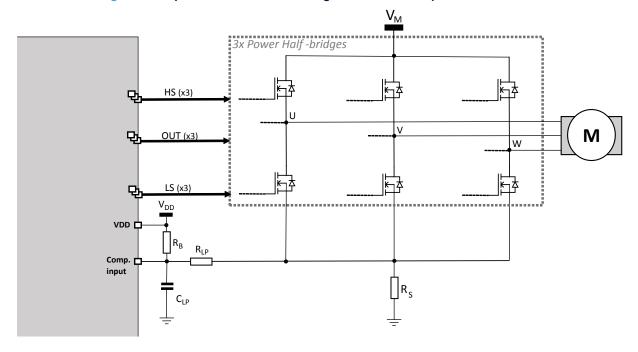

The single shunt topology is shown in Figure 2. As a convention, the phases are indicated by letters U, V and W. Each phase of the motor is connected to its output OUTU, OUTV and OUTW driven by a half-bridge. The currents are noted as  $I_U$ ,  $I_V$ , and  $I_W$  (positive values imply the current is flowing into the motor phase). The sum of the currents is always equal to zero:

$$I_U + I_V + I_W = 0 \tag{1}$$

Currents are measured on a shunt resistor  $R_S$ , so the comparator input is connected directly to it. Therefore, the current flowing in a phase can be measured only when the respective low side MOSFET is turned on. The overall current measured is a combination of  $I_U$ ,  $I_V$ , and  $I_W$  as listed in Table 2. The value of the current in a phase can be determined using the information coming from the other two phases according to Eq. (1).

OUT (x3)

Comparator input

R<sub>S</sub>

Figure 2. Power stage and OC protection schematic - single shunt

Table 2. Measured current according to power MOSFETs state - single shunt

| Power MOSFET turned ON |           | ON        | Measured current on OC COMP input        |  |

|------------------------|-----------|-----------|------------------------------------------|--|

| Phase U                | Phase V   | Phase W   | Measured current on OC_COMP input        |  |

| Low side               | Low side  | Low side  | 0                                        |  |

| Low side               | Low side  | High side | $(I_U + I_V) \cdot R_S = -I_W \cdot R_S$ |  |

| Low side               | High side | Low side  | $(I_U + I_W) \cdot R_S = -I_V \cdot R_S$ |  |

| Low side               | High side | High side | $I_U \cdot R_S$                          |  |

| High side              | Low side  | Low side  | $(I_V + I_W) \cdot R_S = -I_U \cdot R_S$ |  |

| High side              | Low side  | High side | $I_V \cdot R_S$                          |  |

| High side              | High side | Low side  | $I_W \cdot R_S$                          |  |

| High side              | High side | High side | 0                                        |  |

AN4999 - Rev 3 page 3/20

Considering the schematic shown in Figure 2, the threshold current  $I_{\text{max}}$  at which protection acts is:

$$I_{max} = \frac{OC\_COMP_{th}}{R_S} \tag{2}$$

Where  $R_S$  is the value of the shunt resistor and  $OC\_COMP_{th}$  is the internal reference as for Section 1. Should be noticed that power MOSFETs introduce noise when switching, hence a low pass filter can be added in order to reduce noise on comparator input. Referring to Figure 3, a resistor  $R_{LP} >> R_S$  is used to decouple the capacitor  $C_{LP}$  and  $R_S$ . The cut-off frequency of the low pass filter is:

$$f_{LP} \cong \frac{1}{2\pi R_{LP}C_{LP}} \tag{3}$$

OUT (x3)

Comparator input

R<sub>LP</sub>

R<sub>S</sub>

Figure 3. OC protection schematic - single shunt with low-pass filter

#### 2.1 Bias resistor on comparator input (single shunt)

As Eq. (2) states, the current limit can be changed only changing the  $R_S$  or OC\_COMP<sub>th</sub> (STSPIN32F0 family only). To better adjust the overcurrent threshold, it is possible to bias the input pin with a pull-up resistor connected to  $V_{DD}$ , supplied by the device. Consequently, the equivalent threshold is decreased by the same amount of the bias voltage.

Referring to Figure 4, the input pin is biased at:

$$V_{bias} = V_{DD} \cdot \frac{R_{LP}}{R_B + R_{LP}} \tag{4}$$

Due to the  $R_B$ , the signal coming from the shunt resistor  $R_S$  is partitioned too; considering a current  $I_X$  flowing through the  $R_S$ , the voltage contribution on the input pin is:

$$V_{signal} = I_x R_S \cdot \frac{R_B}{R_B + R_{LP}} \tag{5}$$

AN4999 - Rev 3 page 4/20

Combining contributions described by Eq. (4) and Eq. (5) is possible to obtain the total voltage on the input. The value of the current  $I_x$ , for which voltage on the comparator input becomes equal to the internal reference  $OC\_COMP_{th}$ , is the value of the maximum current allowed ( $I_{max,b}$ ):

$$I_{max,b} \cdot R_S \cdot \frac{R_B}{R_B + R_{LP}} + V_{DD} \cdot \frac{R_{LP}}{R_B + R_{LP}} = OC\_COMP_{th}$$

(6)

In this way is possible to regulate the overcurrent threshold just changing the  $R_B$  resistor; its value can be found applying the following formula:

$$R_B \cong R_{LP} \cdot \left( \frac{V_{DD} - OC\_COMP_{th}}{OC\_COMP_{th} - I_{max,b} \cdot R_S} \right)$$

(7)

The presence of the R<sub>B</sub> also modifies the low pass cut-off frequency stated in Eq. (3) as:

$$f_{LP} \cong \frac{1}{2\pi C_{LP} \frac{R_{LP} \cdot R_B}{R_{LP} + R_B}} \tag{8}$$

Figure 4. OC protection schematic - single shunt with low-pass filter and bias

AN4999 - Rev 3 page 5/20

### Overcurrent detection in a dual shunt topology

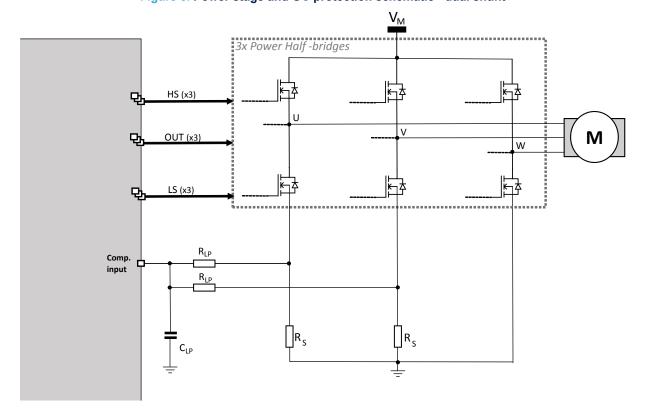

In this topology only two phases have a shunt resistor; the third one is connected directly to GND. Figure 5 gives an example of the dual shunt configuration where no shunt is connected to the W phase.

The current flowing in a phase is measured only when the respective low side MOSFET is turned on. Otherwise, the current does not flow into the related shunt resistor. Therefore, the overall current measured can be a combination of  $I_U$ ,  $I_V$ , and  $I_W$  as listed in Table 3. According to Eq. (1) is possible to know the value of the current about a phase, using the value coming from the other two phases. This is the reason why the third shunt (e.g. on the phase W) is not connected.

However, potential issues can arise in overcurrent protection. Since the current on the phase W is not measured, high currents can flow in the phases but the signal coming from the other two shunt resistor is lower than expected. The worst case is when the U and V high side MOSFETs are on and the W low side MOSFET is on. In this situation, high currents can flow, but the voltage on the comparator input is always zero, hence overcurrent protection cannot be triggered.

For this reason, the dual shunt configuration for overcurrent protection can be used but is not recommended. Taking into account this notice, the overcurrent protection in dual shunt configuration can be analyzed as done in Section 2 for single shunt configuration.

Figure 5. Power stage and OC protection schematic - dual shunt

AN4999 - Rev 3 page 6/20

| Power MOSFET turned ON |           | d ON      | Messured surrent on OC COMP input              |  |

|------------------------|-----------|-----------|------------------------------------------------|--|

| Phase U                | Phase V   | Phase W   | Measured current on OC_COMP input              |  |

| Low side               | Low side  | Low side  | $(I_U + I_V) \cdot R_S = -I_W \cdot R_S$       |  |

| Low side               | Low side  | High side | $(I_U + I_V) \cdot R_S = -I_W \cdot R_S$       |  |

| Low side               | High side | Low side  | I <sub>U</sub> · R <sub>S</sub> <sup>(1)</sup> |  |

| Low side               | High side | High side | $I_U \cdot R_S$                                |  |

| High side              | Low side  | Low side  | I <sub>V</sub> · R <sub>S</sub> <sup>(1)</sup> |  |

| High side              | Low side  | High side | $I_V \cdot R_S$                                |  |

| High side              | High side | Low side  | 0 (1)                                          |  |

| High side              | High side | High side | 0                                              |  |

Table 3. Measured current according to power MOSFETs state - dual shunt

According to the schematic shown in Figure 5, the threshold current I<sub>max</sub> at which protection acts is:

$$I_{max} = \frac{2 \cdot OC\_COMP_{th}}{R_S} \tag{9}$$

Where  $OC\_COMP_{th}$  is the comparator internal reference as for Section 1.

The low pass filter introduced by the  $C_{LP}$  reduces noise on the comparator input. Referring to Figure 5, the cut-off frequency of the filter is:

$$f_{LP} \cong \frac{1}{\pi R_{LP} C_{LP}} \tag{10}$$

#### 3.1 Bias resistor on comparator input (dual shunt)

As Eq. (9) states, the current limit can be changed only by changing the  $R_S$  or  $OC\_COMP_{th}$ . To better adjust the overcurrent threshold is possible to bias the input with a pull-up resistor connected to  $V_{DD}$ , supplied by the device. Consequently, the equivalent threshold is decreased by the same amount of the bias voltage.

Referring to Figure 6, the input is biased at:

$$V_{bias} = V_{DD} \cdot \frac{R_{LP}}{2R_B + R_{LP}} \tag{11}$$

Due to the  $R_B$ , the signal coming from the shunt resistors  $R_S$  is partitioned too; considering the sum of the currents  $I_X$  flowing through the shunts  $R_S$  (in this specific case U and V), the voltage contribution on the input pin is:

$$V_{signal} = \sum_{x = ILV} I_x R_S \cdot \frac{R_B}{2R_B + R_{LP}} \tag{12}$$

Combining contributions described by Eq. (11) and Eq. (12) is possible to obtain the total voltage on the comparator input. The total value of the current for which voltage on the input pin becomes equal to the comparator internal reference  $OC\_COMP_{th}$ , is the value of the maximum current allowed ( $I_{max}$ ,b):

$$I_{max,b} \cdot R_S \cdot \frac{R_B}{2R_B + R_{LP}} + V_{DD} \cdot \frac{R_{LP}}{2R_B + R_{LP}} = OC\_COMP_{th}$$

$$\tag{13}$$

In this way is possible to regulate the overcurrent threshold just changing the  $R_B$  resistor; its value can be found applying the following formula:

AN4999 - Rev 3 page 7/20

<sup>1.</sup> Current is not measured on the phase W, potential issues can arise in overcurrent measurements.

$$R_B \cong R_{LP} \cdot \left( \frac{V_{DD} - OC\_COMP_{th}}{2 \cdot OC\_COMP_{th} - I_{max,b} \cdot R_S} \right)$$

(14)

The presence of the  $R_{B}$  also modifies the low pass cut-off frequency stated in Eq. (10).

$$f_{LP} \cong \frac{1}{2\pi C_{LP} \frac{R_{LP} \cdot R_B}{2R_B + R_{LP}}} \tag{15}$$

Figure 6. OC protection schematic with low-pass filter and bias - dual shunt

AN4999 - Rev 3 page 8/20

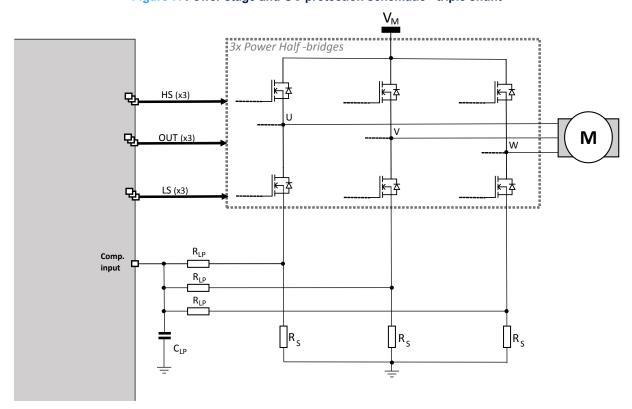

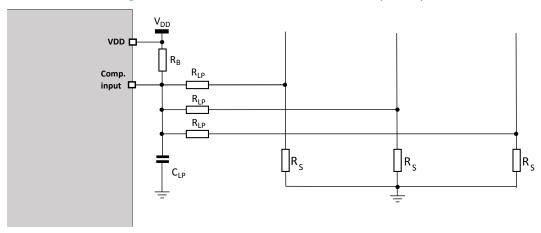

### 4 Overcurrent detection in a triple shunt topology

In this configuration the low side MOSFET of each half-bridge is connected to a shunt resistor used to measure the current in that phase. Referring to Figure 7, three resistors ( $R_{LP}$ ) with the same value are used to sum the voltage of each shunt. Assume to choose  $R_{LP} >> R_S$  so that all the current coming from a phase flows into the  $R_S$ . The voltage on the  $R_S$  is then reported on the comparator input through the partition given by the  $R_{LP}$  resistors.

For a given phase X the voltage on the shunt resistor  $V_{R,x}$  depends on the current flowing through the low side MOSFET on that phase:

$$V_{R,x} \cong I_X \cdot R_S \tag{16}$$

The voltage  $V_{R,x}$  is then reported on the input pin through the partition made by the resistors  $R_{LP}$ . The resulting voltage on the comparator input is:

$$V_{OC\_COMP,x} \cong V_{R,X} \cdot \frac{(R_{LP} + R_S)}{2 \cdot R_{LP} + (R_{LP} + R_S)}$$

$$\tag{17}$$

Using Eq. (16) and considering R<sub>LP</sub> >> R<sub>S</sub>, Eq. (17) becomes:

$$V_{OC\_COMP,x} \cong I_X \cdot R_S / 3 \tag{18}$$

Each phase gives its contribution according to Eq. (18), so that the overall signal on the comparator input is the sum of the voltage on each shunt resistor. As Eq. (18) shows, the main disadvantage of this circuitry is that the signal generated on the shunt resistor is attenuated by 1/3; however just three more resistors are needed.

Figure 7. Power stage and OC protection schematic - triple shunt

AN4999 - Rev 3 page 9/20

The current flowing in a phase is measured only when the respective low side MOSFET is turned on. Otherwise, the current does not flow into the related shunt resistor. Therefore, the overall current measured can be a combination of  $I_U$ ,  $I_V$ , and  $I_W$  as listed in Table 4. The value of the current in a phase can be determined using the information coming from the other two phases according to Eq. (1).

| Power MOSFET turned ON |           | d ON      | Macaurad augreent on OC COMP innut                           |

|------------------------|-----------|-----------|--------------------------------------------------------------|

| Phase U                | Phase V   | Phase W   | Measured current on OC_COMP input                            |

| Low side               | Low side  | Low side  | 0                                                            |

| Low side               | Low side  | High side | $1/3 \cdot (I_U + I_V) \cdot R_S = -1/3 \cdot I_W \cdot R_S$ |

| Low side               | High side | Low side  | $1/3 \cdot (I_U + I_W) \cdot R_S = -1/3 \cdot I_V \cdot R_S$ |

| Low side               | High side | High side | 1/3 · I <sub>U</sub> · R <sub>S</sub>                        |

| High side              | Low side  | Low side  | $1/3 \cdot (I_V + I_W) \cdot R_S = -1/3 \cdot I_U \cdot R_S$ |

| High side              | Low side  | High side | 1/3 · I <sub>V</sub> · R <sub>S</sub>                        |

| High side              | High side | Low side  | 1/3 ⋅ I <sub>W</sub> ⋅ R <sub>S</sub>                        |

| High side              | High side | High side | 0                                                            |

Table 4. Measured current according to power MOSFETs state

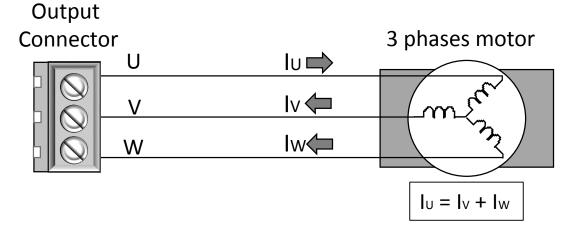

It should be noticed that phases are inductive loads and their current is controlled using the PWM method. This means that voltages and currents are not instantly correlated; e.g. on a given phase X, the high side MOSFET can be turned on but the current  $I_x$  flows into  $OUT_x$ .

Conversely, the low side MOSFET can be on but the current flows out from  $OUT_x$ . This happens when the current in the inductive load is discharging. However, the current limiting based on overcurrent protection acts when the loads are charging. In this case, the maximum current flowing through one phase can be measured as the sum of the other two currents, as shown in Table 4 and considering Eq. (1).

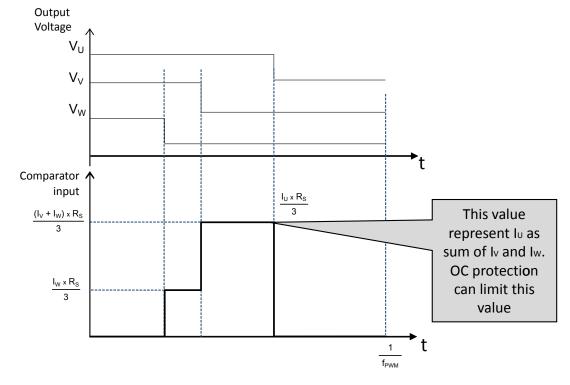

Figure 8. Example showing the output currents

As an example let's now consider the specific situation depicted in Figure 8, where the current is flowing into the phase U and comes back from the phase V and W. The PWM voltage signals are applied on the output nodes in order to control the currents (Figure 9). The higher current in this example is  $I_U$ : the maximum value that the OC\_COMP pin reaches is 1/3  $I_U$   $R_S$ , just when the OUTU high side is on and the OUTV, W low sides are on. The amount of time for which comparator input voltage stays at this value depends on PWM frequency and duty cycles of the outputs. Should be noticed that the  $C_{LP}$  must be sized taking into account this timing, together with the response time of the overcurrent protection.

AN4999 - Rev 3 page 10/20

Figure 9. Example showing PWM voltage signals and related OC\_COMP voltage

### 4.1 Sizing components values

Referring to the general schematic shown in Figure 7, some consideration (already done in Section 2 and Section 3) can be done for components sizing. The  $R_{LP}$  resistors are chosen to be much greater than the  $R_S$  in order to decouple the current signals on each phase, the error due to coupling effects is:

$$\varepsilon = \frac{2R_S}{3(R_{LP} + R_S)} \cong \frac{2R_S}{3R_{LP}} \tag{19}$$

In the most of applications R<sub>S</sub> <1  $\Omega$  and R<sub>LP</sub> >1 k $\Omega$  so coupling error is negligible.

The capacitor  $C_{LP}$  on the input pin reduces noise and spikes generated by power MOSFET switching. The cut-off frequency of the low pass filter is:

$$f_{LP} \cong \frac{3}{2\pi R_{LP} C_{LP}} \tag{20}$$

The cut-off frequency can be chosen in order to have a response time of OC protection suitable for the application. A good trade-off between noise reduction and response time is to set the low pass frequency about 5 times the PWM frequency (f<sub>PWM</sub>). The threshold current I<sub>max</sub> at which the overcurrent protection acts is:

$$I_{max} \cong \frac{3 \cdot OC\_COMP_{th}}{R_S} \tag{21}$$

Where OC\_COMPth is the comparator internal reference as for Section 1.

#### Example 1

Assume PWM control with a  $f_{PWM}$  = 40 kHz that generates three sinusoidal currents in the motor phases. The nominal peak current is 1.5 A and the desired overcurrent threshold should be set at 3 A. Using  $R_S$  = 0.1  $\Omega$   $R_{LP}$  = 2.2 k $\Omega$ ,  $C_{LP}$  = 1 nF and choosing the threshold at 100 mV (STSPIN32F0 family only) is possible to disable the outputs when the current in one of the three phases reaches 3 A. The low pass filtering performed by the  $R_{LP}$  and  $C_{LP}$  has a frequency  $f_{LP} \sim 217$  kHz, which is about 5 times the PWM frequency.

AN4999 - Rev 3 page 11/20

#### 4.2 Bias resistor on OC COMP pin (triple shunt)

As Eq. (21) states, the current limit can be changed only changing the R<sub>S</sub> or OC\_COMPth. To better adjust the overcurrent threshold, is possible to bias the comparator input with a pull-up resistor connected to V<sub>DD</sub>, supplied by the device. Consequently, the equivalent threshold decreases by the same amount of the bias voltage. Referring to Figure 10, the input pin is biased at:

$$V_{bias} \cong V_{DD} \cdot \frac{R_{LP}}{3R_B + R_{LP}} \tag{22}$$

Due to the  $R_B$ , the signal coming from the shunt resistors RS is partitioned too; considering the sum of the currents  $I_x$  flowing through the  $R_S$  for each phase, the voltage contribution on the input pin is:

$$V_{signal} = \sum_{x = U,V,W} I_x R_S \cdot \frac{R_B}{3R_B + R_{LP}}$$

(23)

Combining contributions described by Eq. (22) and Eq. (23) is possible to obtain the total voltage on the input pin. The total value of the current for which voltage on the comparator input becomes equal to the internal reference  $OC\_COMP_{th}$ , is the value of the maximum current allowed ( $I_{max,b}$ ):

$$I_{max,b} \cdot R_S \cdot \frac{R_B}{3R_B + R_{LP}} + V_{DD} \cdot \frac{R_{LP}}{3R_B + R_{LP}} = OC\_COMP_{th}$$

(24)

In this way is possible to regulate the threshold just changing the R<sub>B</sub> resistor; its value can be found applying the following formula:

$$R_B = R_{LP} \cdot \left( \frac{V_{DD} - OC\_COMP_{th}}{3 \cdot OC\_COMP_{th} - I_{max,b} \cdot R_S} \right)$$

(25)

The presence of the R<sub>B</sub> also modifies the low pass cut-off frequency stated in Eq. (20).

$$f_{LP} \cong \frac{1}{2\pi C_{LP} \frac{R_{LP} \cdot R_B}{3R_R + R_{LP}}} \tag{26}$$

#### Example 2

Referring to Example 1, consider to change the overcurrent threshold to 2 A using the same values of the OC\_COMP<sub>th</sub> and R<sub>S</sub>. According to Eq. (25) using a R<sub>B</sub>  $\cong$  70 k $\Omega$  is possible to reduce the overcurrent threshold from 3 A to 2 A thus matching the new requirement on the overcurrent threshold. The filter frequency becomes slightly increased at 219 kHz, so no changes are needed on the C<sub>LP</sub>.

AN4999 - Rev 3 page 12/20

Figure 10. OC COMP read-out with schematic (biased)

AN4999 - Rev 3 page 13/20

#### 5 Conclusions

Despite of different shunt configurations described in Section 2, Section 3, and Section 4, the results obtained are similar. Hereafter all the parameters used in the formulas are listed:

- I<sub>max. th</sub>: current threshold at which the OC protection is triggered.

- OC\_COMP<sub>th</sub>: internal reference for the comparator (see Section 1).

- R<sub>S</sub>: shunt resistor(s).

- R<sub>LP</sub>: resistor used to bring the signal from the shunt resistor(s) to the input pin.

- C<sub>LP</sub>: filter capacitor on the input pin.

- R<sub>B</sub>: optional resistor for the input pin biasing.

- V<sub>DD</sub>: digital voltage supplied.

- f<sub>PWM</sub>: frequency of the PWM driving signals.

Moreover consider the parameter  $N_S$ , which represents the number of the shunt resistors used (e.g. for single shunt configuration  $N_S = 1$ ). Table 5 summarizes the formulas, with orwithout the input biasing the resistor  $R_B$ .

| Bias condition   | Resistor to be chosen                                                                                                   | Low pass cut off frequency                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| No bias on input | $R_{S} = \left(\frac{N_{S} \cdot OC\_COMP_{th}}{I_{max,th}}\right)$                                                     | $f_{LP} = \frac{N_S}{2\pi R_{LP} C_{LP}}$                    |

| Input biased     | $R_{B} = R_{LP} \cdot \left( \frac{V_{DD} - OC\_COMP_{th}}{N_{S} \cdot OC\_COMP_{th} - I_{max,th} \cdot R_{S}} \right)$ | $f_{LP,b} = \frac{N_S R_B + R_{LP}}{2\pi R_{LP} C_{LP} R_B}$ |

Table 5. Formulas summary

#### 5.1 Application example

This paragraph analyzes the setup described in Example 1, and shows how to act the OC protection feature. The power MOSFETs are connected to the STSPIN32F0 in a three shunt configuration and the OC\_COMP pin is connected as shown in Figure 7.

The firmware loaded into the internal MCU generates the 6 PWM signal resulting in 3 sinusoidal currents in the motor phases. Sinewaves are delayed of 120° each other, in order to implement open-loop voltage driving: PWM duty cycles are modulated in order to have a sinusoidal profile with specified amplitude.

As stated in Example 1, the following conditions are used:

- f<sub>PWM</sub> = 40 kHz

- $R_S = 0.1 \Omega$

- R<sub>IP</sub> = 2.2 kΩ

- C<sub>LP</sub> = 1 nF

- OC\_COMP<sub>th</sub> = 100 mV

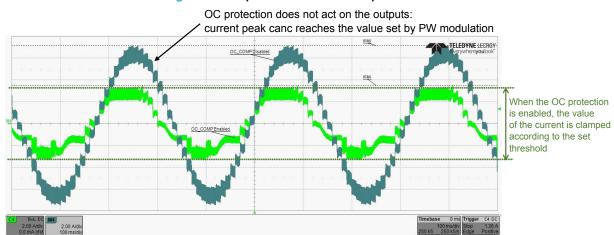

Since the triple shunt configuration is used,  $N_S = 3$ . The current threshold which triggers the OC protection is  $I_{max,th} = 3 \text{ A}$  - see Eq. (21). The analysis here described wants to highlight the effects of the OC protection: therefore, a peak current higher than the threshold is imposed. In this example, PWM duty cycles are chosen in order to have a current in each phase equal to the 7 A peak.

The resulting current acquisition for a single phase is reported in Figure 11. When the OC protection is disabled (OC\_SEL = 0) the power MOSFETs work without limitations and the value of the peak current reaches the expected value of 7 A. Otherwise enabling the OC protection (OC\_SEL = 1), the power MOSFETs are disabled whenever the current reaches the limit of 3 A, so the current is clamped and cannot reach the peak value of 7 A. Although Figure 11 shows just one phase, the clamping due to the OC protection is present in the same way on all the three phases.

AN4999 - Rev 3 page 14/20

Figure 11. OC protection effect on a phase current

Note: When OC protection I enabled the value of currrent is clamped according to the set threshold.

AN4999 - Rev 3 page 15/20

# **Revision history**

Table 6. Document revision history

| Date        | Version | Changes                                                                         |

|-------------|---------|---------------------------------------------------------------------------------|

| 31-Jan-2017 | 1       | Initial release.                                                                |

| 06-Feb-2020 | 2       | STSPIN32F0 changed to STSPIN32F0/F0A/F0B throughout document.26                 |

| 05-Mar-2025 | 3       | Changed title in cover page; changes to extend the AN to the STSPIN32G0 family. |

AN4999 - Rev 3 page 16/20

# **Contents**

| 1        | Ove    | rcurrent internal block diagram                  | 2  |

|----------|--------|--------------------------------------------------|----|

| 2 Overci |        | rcurrent detection in a single shunt topology    | 3  |

|          | 2.1    | Bias resistor on comparator input (single shunt) | 4  |

| 3        | Ove    | rcurrent detection in a dual shunt topology      | 6  |

|          | 3.1    | Bias resistor on comparator input (dual shunt)   | 7  |

| 4        | Ove    | rcurrent detection in a triple shunt topology    | 9  |

|          | 4.1    | Sizing components values                         | 11 |

|          | 4.2    | Bias resistor on OC_COMP pin (triple shunt)      | 12 |

| 5        | Con    | clusions                                         | 14 |

|          | 5.1    | Application example                              | 14 |

| Revi     | ision  | history                                          | 16 |

| List     | of ta  | bles                                             | 18 |

| List     | of fic | nures                                            | 19 |

# **List of tables**

| Table 1. | OC threshold values (STSPIN32F0/F0A/F0B)                         | . 2 |

|----------|------------------------------------------------------------------|-----|

| Table 2. | Measured current according to power MOSFETs state - single shunt | . 3 |

| Table 3. | Measured current according to power MOSFETs state - dual shunt   | . 7 |

| Table 4. | Measured current according to power MOSFETs state                | 10  |

| Table 5. | Formulas summary                                                 | 14  |

| Table 6. | Document revision history                                        | 16  |

AN4999 - Rev 3 page 18/20

# **List of figures**

| Figure 1.  | Overcurrent protection block diagram                                 | . 2 |

|------------|----------------------------------------------------------------------|-----|

| Figure 2.  | Power stage and OC protection schematic - single shunt               | . 3 |

| Figure 3.  | OC protection schematic - single shunt with low-pass filter          | . 4 |

| Figure 4.  | OC protection schematic - single shunt with low-pass filter and bias | . 5 |

| Figure 5.  | Power stage and OC protection schematic - dual shunt                 | . 6 |

| Figure 6.  | OC protection schematic with low-pass filter and bias - dual shunt   | . 8 |

| Figure 7.  | Power stage and OC protection schematic - triple shunt               | . 9 |

| Figure 8.  | Example showing the output currents                                  | 10  |

| Figure 9.  | Example showing PWM voltage signals and related OC_COMP voltage      | 11  |

| Figure 10. | OC COMP read-out with schematic (biased)                             | 13  |

| Figure 11. | OC protection effect on a phase current                              | 15  |

|            |                                                                      |     |

AN4999 - Rev 3 page 19/20

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

AN4999 - Rev 3 page 20/20