# Charge pump stress estimation in switching applications

#### Introduction

The aim of this application note is to provide a criterion for charge pump stress estimation in automotive switching applications.

The present analysis can be exploited to estimate the workload to be accounted for the charge pump when using pre-driver devices.

Peak & Hold injection, electro-valve control and H-Bridge driving can be listed among the most stressing applications in terms of timings and switching frequency.

Independently on the application, this document aims at providing a set of information, equations and criteria useful to choose the correct external transistors and components, along with the switching frequency. The analysis is focused on the charge pump stress induced by these parameters. The ST L9945, an 8-channel configurable HS/LS pre-driver, is considered as the reference device to be used in several applications (P&H, H-Bridge, HS/LS). The ST STD105N10F7AG NMOS transistor is taken as an example of driver used in power applications.

# 1 Charge pump stress factors

The charge pump works by switching the battery voltage  $V_{PS}$  onto flying capacitors and then storing the charge into a tank capacitor by means of a proper circuit re-connection (see Figure 1). Such operation aims at generating an output voltage  $V_{GBHI}$  higher than the battery one. This allows using an NMOS transistor to drive the load in both high-side and low-side configurations. PMOS drivers are usually used as high-side switches and do not require any charge pump intervention during switching. The charge pump stress estimation for a single channel must be done accounting for several aspects:

- Charge pump capability

- Target gate-to-source voltage of the external driver

- Charge pump intervention based on driver side (HS/LS)

- External FET gate charge

- External Miller capacitor charge

- External pull down network

- Eventual Internal absorption due to leakage and polarization of pre-driver circuitry

- · Tolerance Margin

The control signal switching frequency is also a highly relevant parameter that must be taken in account when analyzing many of the points above.

All these aspects can be analyzed separately and then merged to evaluate final workload.

Battery

CFLY1

CFLY2

VPS

CH1

CH2

CH3

CH4

VGBHI

Charge Pump

Figure 1. Charge pump block diagram

GADG0709171603PS

### 1.1 Charge pump capability

The charge pump capability is a feature depending on the design and varies among different devices. It is usually listed in the electrical characteristics of the device.

A well dimensioned charge pump must guarantee a stable output voltage  $V_{GBHI}$  in the worst case applicative scenario foreseen for the flexible device.

As example, Table 1 shows the electrical characteristics of the charge pump embedded in the ST L9945. Focusing on the first row, the charge pump capability is given by the "Test Condition" information.

Note that capability is expressed as the maximum equivalent DC current that charge pump is able to provide. Depending on the internal design, the capability may also vary with the battery voltage.

Therefore, in order to verify the stress induced on the charge pump, it is necessary to estimate the mean current absorbed by each output channel performing different applications. The mean consumption of each channel must be summed and the result compared with the capability.

AN5074 - Rev 1 page 2/25

In this application note, we will consider I<sub>CP MAX</sub> = 15 mA as the charge pump capability of the device. However, in case the application requires external FETs to switch also at very low battery, a worst case analysis shall consider a capability of 6 mA only. In fact, in corner cases of deep cold crank, the battery voltage VPS may drop below the 8 V threshold.

Note: Automotive scenarios feature a wide temperature range (typically from -40 °C to +150 °C).

> Another fundamental characteristic of a charge pump is represented by its ability to resist to current peaks. When several channels are switching synchronously, all the charge requests overlap in a very short time interval, causing peaks higher than 1 A. A well designed charge pump must take in account the maximum number of channels that can switch simultaneously and must resist to such amount of charge that is instantaneously requested. The robustness against peak current request can be evaluated considering the external tank capacitor CTANK. Eq. (1) can be exploited to estimate the voltage drop occurring on VGBHI during a fast discharge. For instance, a peak current of 1 A, lasting 1 µs, causes a 2.13 V voltage drop on a 470 nF tank capacitor. Refer to Section 3.4 Case study: ST L9945 in application for an example.

$$\Delta V_{TANK} = \left(\frac{I_{PEAK}}{C_{TANK}}\right) \times \Delta t_{peak} \tag{1}$$

| Symbol                 | Parameter                     | Test condition                                                              | Min.     | Тур.        | Max.     | Unit |

|------------------------|-------------------------------|-----------------------------------------------------------------------------|----------|-------------|----------|------|

| V                      | Charge pump voltage versus    | V <sub>VPS</sub> ≥ 8 V;<br>I <sub>VGBHI</sub> = 15 mA (DC)                  | VVPS+9   | VVPS<br>+12 | VVPS+16  | V    |

| $V_{VGBHI}$            | charge pump load current      | $V_{VPS\_UV} \le V_{VPS} < 8 \text{ V};$<br>$I_{VGBHI} = 6 \text{ mA (DC)}$ | VVPS+5   |             | VVPS+16  | V    |

| f <sub>CP</sub>        | Charge pump frequency         | Dependent on t <sub>SYS</sub>                                               | 184      | 200         | 216      | kHz  |

| C <sub>TANK</sub>      | Charge pump tank capacitor    | Connected to VPS I <sub>VGBHI</sub> = 15 mA                                 | 420      | 470         | 520      | nF   |

| C <sub>FLY</sub>       | Charge pump flying capacitors | Connected between CH1-CH2, CH3-CH4; I <sub>VGBHI</sub> = 15 mA              | 198      | 220         | 242      | nF   |

| V <sub>CP_UV</sub>     | Under voltage threshold       | Referenced to VVPS                                                          | VVPS+3.9 |             | VVPS+5.1 | V    |

| Vh <sub>CP_UV</sub>    | Under voltage hysteresis      | Referenced to VVPS                                                          | 250      |             |          | mV   |

| t <sub>CP_UV</sub>     | Under voltage filter time     |                                                                             | 10       |             | 30       | μs   |

| V <sub>VGBHI_MAX</sub> | Charge pump max voltage       | Referenced to GND                                                           |          |             | 80       | ٧    |

| t <sub>CPstartup</sub> | Startup time                  |                                                                             | 0.05     |             | 2        | ms   |

Table 1. Charge pump electrical characteristics

#### 1.2 Target gate-to-source voltage of the external driver

In order to switch on the external FET, the gate-to-source voltage (VGS) must be higher than the ON threshold voltage V<sub>TH</sub>. Gate threshold voltage (gathered from STD105N10F7AG electrical characteristics) is shown in the table below.

**Test conditions Symbol** Min. Max. Unit **Parameter** Typ. Drain-source breakdown voltage (V<sub>GS</sub> = 0)  $I_D = 250 \, \mu A$ 100 V<sub>(BR)DSS</sub> V  $V_{DS} = 100 \text{ V}$ 1 μΑ Zero gate voltage IDSS drain current ( $V_{GS} = 0$ )  $V_{DS} = 100 \text{ V}, T_C = 125 \text{ }^{\circ}\text{C}^{(1)}$ 100 μΑ

Table 2. On/Off states

AN5074 - Rev 1 page 3/25

| Symbol              | Parameter                                       | Test conditions                               | Min. | Тур. | Max.  | Unit |

|---------------------|-------------------------------------------------|-----------------------------------------------|------|------|-------|------|

| I <sub>GSS</sub>    | Gate body leakage current (V <sub>DS</sub> = 0) | V <sub>GS</sub> = ± 20 V                      |      |      | ± 100 | nA   |

| V <sub>GS(th)</sub> | Gate threshold voltage                          | $V_{DS} = V_{GS}$ , $I_D = 250 \mu A$         | 2.5  |      | 4.5   | V    |

| R <sub>DS(on)</sub> | Static drain-source on-resistance               | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 40 A |      | 6.8  | 8     | mΩ   |

<sup>1.</sup> Defined by design, not subject to production test.

Considering ST STD105N10F7AG NMOS transistor as an example of power MOS, the maximum threshold voltage listed in the electrical characteristics is  $V_{TH\ MAX}$  = 4.5 V.

In no case  $V_{GS}$  must violate the product AMR. In our case,  $V_{GS\_MAX}$  = 20 V, as highlighted in the table below. It is necessary to operate with  $V_{GS} >> V_{TH}$  in order to guarantee the proper overdrive to the external FET, which ensures operating in the switch region. The higher the VGS, the lower the channel parasitic resistance  $R_{DSon}$ . On the other hand, the higher the  $V_{GS}$ , the higher the charge pump effort in order to inject the gate charge necessary to bias the device, as shown in Figure 3.

| Symbol                         | Parameter                                             | Value      | Unit |

|--------------------------------|-------------------------------------------------------|------------|------|

| V <sub>DS</sub>                | Drain-source voltage                                  | 100        | V    |

| V <sub>GS</sub>                | Gate-source voltage                                   | ± 20       | V    |

| I <sub>D</sub>                 | Drain current (continuous) at T <sub>C</sub> = 25 °C  | 80         | А    |

| I <sub>D</sub>                 | Drain current (continuous) at T <sub>C</sub> = 100 °C | 62         | Α    |

| I <sub>DM</sub> <sup>(1)</sup> | Drain current (pulsed)                                | 320        | Α    |

| P <sub>TOT</sub>               | Total dissipation at T <sub>C</sub> = 25 °C           | 120        | W    |

| T <sub>stg</sub>               | Storage temperature range                             | FF 1- 47F  | 80   |

| T <sub>J</sub>                 | Operation junction temperature range                  | -55 to 175 | °C   |

Table 3. Absolute maximum ratings

The target gate-to-source voltage  $V_{GS\_TYP}$  is usually a feature of the flexible device and depends on the charge pump internal design. Table 1 shows the typical charge pump output voltage  $V_{GBHI\_TYP} = V_{PS} + 12$  V. The voltage step with respect to battery supply VPS will be the target  $V_{GS\_TYP}$  applied on the external FET when used as HS.

Therefore, for our applications, we will consider  $V_{GS\ TYP}$  = 12 V.

It is important choosing an external FET compatible with the device target VGS, following the criteria mentioned above. The ST STD105N10F7AG NMOS transistor fits the requirements because:

- V<sub>TH\_MAX</sub> < V<sub>GS\_TYP</sub> < V<sub>GS\_MAX</sub>

- V<sub>GS</sub> TYP ≈ 3 \* V<sub>TH</sub> MAX.

# 1.3 Charge pump intervention based on driver side (HS/LS)

The main reason behind the implementation of a charge pump is to allow NMOS transistor usage on HS in power applications. Because NMOS has much lower  $R_{DSon}$  than the PMOS, it is usually preferred as both LS and HS switch in power applications in order to limit the power losses on the driver and to feed the load with the full battery voltage. However, this requires a charge pump in order to effectively bias the NMOS transistor with a high  $V_{GS}$  when the driver is used on HS.

As the battery voltage  $V_{PS}$  may undergo severe fluctuations during its operation, some devices make use of the charge pump to drive also the LS NMOS. This helps preventing failure in turning on the FET when battery voltage drops below an acceptable value (e.g.  $V_{PS}$  < 6 V). On the other side, using charge pump to bias also LS transistors implies a higher workload in terms of current absorption from the tank capacitor.

AN5074 - Rev 1 page 4/25

<sup>1.</sup> Pulse width limited by safe operating area.

For instance, L9945 drives both HS and LS NMOS transistors with the charge pump. Therefore, also LS contributions have to be accounted for when evaluating charge pump stress.

BATT12

DRN1

HS NMOS

DRN3

D

Figure 2. HS and LS NMOS biasing

### 1.4 External FET gate charge

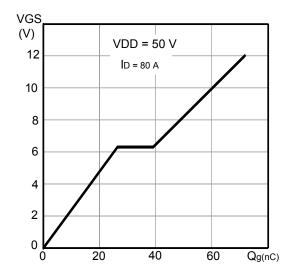

Once the transistor has been chosen according to the criteria mentioned in Target gate-to-source voltage of the external driver, the gate charge needed to switch it on with the target  $V_{GS\_TYP}$  can be evaluated by looking at the  $Q_G - V_{GS}$  graph in its electrical characteristics.

Looking the figure here below, we can estimate that  $Q_{GS\_TYP}$  = 70 nC is the gate charge needed to bring the gate-to-source voltage up to  $V_{GS\_TYP}$ .

Figure 3. STD105N10F7AG: Gate charge vs Gate-to-Source Voltage

GADG1109171114PS

However, as stated in Section 1.1 Charge pump capability, it is necessary to convert this information into a mean current requirement in order to compare it with the I<sub>CP\_MAX</sub>. Every time the external FET needs to be switched ON, a Q<sub>GS\_TYP</sub> charge pulse must be provided by the charge pump. Therefore, the equivalent DC current can be evaluated dividing the charge injected on the switching period TSW, as shown in the equation below.

Eq: Mean current absorption for switching on the external FET:

$$I_{Gmean} = \frac{\Delta Q}{\Delta T} = \frac{Q_{GS_{typ}}}{T_{SW}} = Q_{GS_{typ}} * f_{SW}$$

(2)

AN5074 - Rev 1 page 5/25

For instance, if the switching frequency is 20 KHz, given the gate charge estimated above, an IG\_MEAN = 1.4 mA is absorbed by the channel under analysis.

#### 1.5 External Miller capacitor charge

In order to improve EMI performances, an external Miller capacitor  $C_M$  is usually mounted between gate and drain of the external FET (see Figure 2). This helps smoothing the ON/OFF transitions, thus reducing the electromagnetic emissions. On the other hand, the presence of such capacitor implies an additional amount of charge  $Q_M$  to be supplied by the charge pump when switching ON the transistor.

Such contribution depends on FET side and battery supply voltage:

For HS FETs the gate node voltage swing is V<sub>GS\_TYP</sub> + V<sub>PS</sub>

The amount of charge to be stored in C<sub>M</sub> is

Eq:Amount of charge to be stored in the external Miller capacitor for HS NMOS:

$$Q_{MHS} = C_M^* \Delta V = C_M^* \left( V_{GS_{typ}} + V_{PS} \right) \tag{3}$$

For LS FETs the gate node voltage swing is V<sub>GS\_TYP</sub>

The amount of charge to be stored in C<sub>M</sub> is

Eq: Amount of charge to be stored in the external Miller capacitor for LS NMOS:

$$Q_{M_{LS}} = C_M^* \Delta V = C_M^* V_{GS_{typ}} \tag{4}$$

The dependency on battery supply voltage applies only to HS FETs and varies between Passenger Vehicle (PV) and Commercial Vehicle (CV) applications:

- For PV, the battery voltage is nominally 12 V, but V<sub>PS</sub> = 14 V should be considered as the typical battery voltage

- For CV, the battery voltage is nominally 24 V, but V<sub>PS</sub> = 28 V should be considered as the typical battery voltage

For instance, if  $C_M = 1.5 \text{ nF}$ :

- For HS FETs

- PV: Q<sub>M</sub> H<sub>S</sub> = 39 nC

- CV: Q<sub>M</sub> HS = 60 nC

- For LS FETs, Q<sub>M HS</sub> = 18 nC, independently on V<sub>PS</sub>

These contributions must be converted into mean current absorption aliquots. As for the Section 1.4 External FET gate charge, the  $Q_M$  is an impulsive charge that must be supplied every time the external MOS is switched on. Therefore, the equivalent DC current can be evaluated dividing the charge injected on the switching period  $T_{SW}$ , as shown in the equation below.

Eq: Mean current absorption for charging the external Miller capacitor

$$I_{M_{mean}} = \frac{\Delta Q}{\Delta T} = \frac{Q_M}{T_{SW}} = Q_M * f_{SW} = \begin{cases} C_M * \left( V_{GS_{typ}} + V_{PS} \right) * f_{SW}, & for HSFETs \\ C_M * V_{GS_{typ}} * f_{SW}, & for LSFETs \end{cases}$$

(5)

For instance, if  $C_M = 1.5 \text{ nF}$  and  $f_{SW} = 20 \text{ KHz}$ :

- For HS FETs

- PV:  $I_{M\_MEAN}$  = 780 μA

- CV: I<sub>M MEAN</sub> = 1.2 mA

- For LS FETs,  $I_{M MEAN} = 360 \mu A$

Note: The  $I_{M\_MEAN}$  contribution for LS FETs must be considered only in case the charge pump supplies also LS NMOS.

#### 1.6 External pull down network

In order to avoid wrong biasing of the external drivers at startup, many devices put the output channels in three-state by default. In order to keep the NMOS reliably OFF until the channel is enabled, an external pull down network must be implemented. Usually, a pull down resistor  $R_{PD}$  is mounted between gate and source of the NMOS, as shown in Figure 2.

AN5074 - Rev 1 page 6/25

The pull down network insertion adds a permanent current path between the gate node and the ground (directly to GND in case of LS, to GND through the load in case of HS). Such path causes a sort of "leakage" that cannot be neglected when the device is switched ON. Referring to Figure 2:

- When the NMOS is OFF, no current flows through R<sub>PD</sub> since both gate and source node are brought to GND

- When the NMOS is ON, a V<sub>GS\_TYP</sub> voltage falls on R<sub>PD</sub>, independently on FET side. Even when the driver is fully switched ON, the charge pump must continuously supply a certain amount of charge to keep it ON, thus balancing the charge subtracted by the pull down path. The current needed depends on the pull-down resistor value. Therefore, it's recommended to choose a high value (tens of kΩ) for R<sub>PD</sub> in order not to stress the charge pump. In fact, such resistor is only helpful during the three-state phase at startup, while it has no effect during normal operation since the NMOS is actively switched OFF by the pre-driver.

While the gate charge and the Miller capacitor charge are impulsive contributions, the pull-down network aliquot is a DC contribution to be accounted during the whole ON phase. Therefore, the mean current absorbed by R<sub>PD</sub> over a period depends on the control signal duty-cycle (dc<sub>%</sub>).

Eq: Mean current absorption by the pull down network

$$I_{PD_{mean}} = I_{PD_{ON}}^* dc_{\%} = \frac{V_{GS_{typ}}}{R_{PD}}^* dc_{\%}$$

$$\tag{6}$$

For instance, if R<sub>PD</sub> = 47 k $\Omega$  and dc<sub>%</sub> = 80%, I<sub>PD MEAN</sub>  $\approx$  205  $\mu$ A.

# 1.7 Eventual Internal absorption due to leakage and polarization of pre-driver circuitry

The pre-driver device features an internal circuitry needed to control the biasing of the external FET. In addition, internal and external clamping protections might be present to protect both the pre-driver and the FETs against AMR violations. All these circuitries, along with other eventual hissing needed for internal purpose into the IC, may require a biasing current and add some leakage contributions.

The biasing/leakage internal currents are static contributions depending on the pre-driver output state. Therefore, their weight depends on control signal duty-cycle and can be estimated as follows:

Eq: Internal absorption due to biasing of the pre-driver stages and leakage:

$$I_{BIAS_{mean}} = I_{BIAS_{ON}} * dc_{\%} + I_{BIAS_{OFF}} * \left(1 - dc_{\%}\right)$$

(7)

Depending on the pre-driver architecture, there could or could not be any DC current consumption from the charge pump; the presence of such a contribution shall be checked either on the datasheet or in a specific pre-driver design guideline provided by designers.

The presence or absence of static internal current consumption directly affects Eq. (9), where  $I_{BIAS\_ON}$  and  $I_{BIAS\_OFF}$  can be assumed null in case the architecture under analysis features no internal absorption.

#### 1.8 Tolerance Margin

It is always recommended to consider a TM% additional margin (usually 20%) over the total channel consumption, in order to account all the external leakages and the tolerances of the external components.

AN5074 - Rev 1 page 7/25

# 2 Total charge pump stress evaluation

By evaluating the stress induced on every channel of the device and summing all the contributions, the total charge pump stress can be evaluated.

In order for the flexible pre-driver to operate correctly, the condition  $I_{CP\_MEAN} < I_{CP\_MAX}$  must be verified for all possible configurations.

### 2.1 Single channel mean absorption

As discussed in Charge pump stress factors the channel mean absorption depends on several aspects. In general, the following contributions must be accounted for:

Eq: Channel mean absorption:

$$I_{CH_{mean}} = \left(I_{G_{mean}} + I_{M_{mean}} + I_{PD_{mean}} + I_{BIAS_{mean}}\right)^* (1 + TM_{\%})$$

(8)

Replacing the expressions of each addend in Eq. (8) we provide a formula in order to estimate the consumption for both HS and LS configurations:

Eq: Explicit channel mean absorption for HS and LS configurations

$$I_{CH_{mean}} = \tag{9}$$

$$\begin{cases} \left[ \left[ Q_{GS_{typ}} + C_{M}^{*} \left( V_{GS_{typ}} + V_{PS} \right) \right] * f_{SW} + \left( \frac{V_{GS_{typ}}}{R_{PD}} + I_{BIAS_{ON}} - I_{BIAS_{OFF}} \right) * dc_{\%} + I_{BIAS_{OFF}} \right) * (1 + TM_{\%}) & for \, HS \, FETs \\ \left[ \left[ Q_{GS_{typ}} + C_{M}^{*} V_{GS_{typ}} \right] * f_{SW} + \left( \frac{V_{GS_{typ}}}{R_{PD}} + I_{BIAS_{ON}} - I_{BIAS_{OFF}} \right) * dc_{\%} + I_{BIAS_{OFF}} \right] * (1 + TM_{\%}) & for \, LS \, FETs \end{cases}$$

#### Where:

- Q<sub>GS TYP</sub> is the gate charge to be injected in the external FET in order to generate the VGS\_TYP

- C<sub>M</sub> is the Miller capacitor mounted between gate and source of the external FET in order to improve EMI behavior

- V<sub>GS\_TYP</sub> is the target gate-to-source voltage of the external FET (usually depends on the pre-driver characteristics)

- V<sub>PS</sub> is the battery supply voltage

- f<sub>SW</sub> is the control signal switching frequency

- R<sub>PD</sub> is the external pull-down resistor used to keep the NMOS OFF in case of pre-driver three-state

- · dc% is the duty-cycle of the control signal

- TM<sub>%</sub> is the tolerance margin to account for the pre-driver internal leakage/absorption and for the precision of the external components

Note:

If  $I_{BIAS\_ON}$  and  $I_{BIAS\_OFF}$  are not indicated in the electrical characteristics table of the charge pump, they could have been already been accounted for in the charge pump capability and therefore they must not be considered in Eq. (9)

### 2.2 Total charge pump absorption

By simply summing all channel contributions evaluated according Eq. (9), the total charge pump stress can be estimated.

Eq: Total charge pump absorption

$$I_{CP_{mean}} = \sum_{i=1}^{N_{CH}} I_{CH_{mean_i}} \tag{10}$$

AN5074 - Rev 1 page 8/25

#### 2.2.1 L9945 Charge pump stress calculator

In order to summarize all the points explored in this paper, the **ST L9945 Charge Pump Stress Calculator** has been developed. Such a tool is a Microsoft Excel<sup>®</sup> workbook that applies all the equations formulated during our analysis in order to evaluate final stress on the L9945 charge pump.

The tool allows configuring each channel independently and helps understanding how each channel activity will impact on total stress: a simple color code will highlight channels whose mean consumption is above the average expected value (1/8 of the total capacity).

The analysis can be performed for different values of the power supply, including corner cases for cold cranking and load dump. The charge pump capacity is automatically adapted to the selected battery supply scenario.

The tool is contained in a file attached to this document. Locate the paperclip symbol on the left side of the PDF window, and click it.

# 2.3 Key points for a robust configuration

When building a configuration with a flexible pre-driver device, the following key points should be verified:

- When analyzing charge pump stress, it is useful to consider the worst case for the control signal duty-cycle.

As discussed in Section 1.6 External pull down network, the higher the duty-cycle, the higher the pull down network absorption is;

- Use HS switches only for critical loads that need to be disconnected from battery supply voltage when not used. HS FETs induce a higher stress on the charge pump as discussed in External Miller capacitor charge;

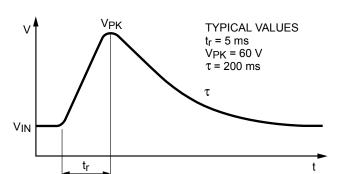

- It is always recommended to keep the charge pump workload below 80% of the total capacity in order to be

robust against phenomena like load dump. During such events, battery voltage may raise up to 35 V (PV) or

60 V (CV) (clamped by external protection circuitry, see Figure 5) for a certain time interval (typ. 500 ms). As

a consequence, charge pump stress will increase during such interval due to External Miller capacitor

charge. However, no functional issue should occur if a suitable workload margin has been left;

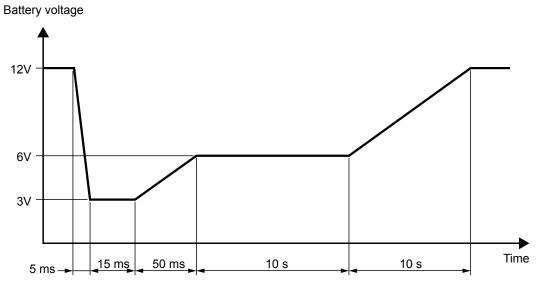

- Charge pump capability is often dependent on battery supply voltage. Events like cold cranking (battery supplying current to electric starter motor in a very cold environment, see Figure 4) may force the battery voltage to drop down to 3 V until the system has been fully started. Usually, charge pump capability is strongly limited under these conditions, and it is very likely to observe failures in trying to control loads. Therefore, when battery voltage drops below an acceptable threshold, it is recommended to disable all the channels that are not safety related in order to guarantee the functionality of the critical features.

Figure 4. Battery voltage profile during a cold cranking event

GADG1109171039PS

AN5074 - Rev 1 page 9/25

Figure 5. Load dump in CV systems

AN5074 - Rev 1 page 10/25

# 3 Case study: ST L9945 configuration for CV applications

The following case study is based on ST L9945 flexible pre-driver, configured to drive all its 8 channels with independent PWM. Common CV applications are:

- Lambda probe heater control

- Lamp control

- Starter relay

- GDI/PFI Injection

- Oil/Fuel pump control

In the following examples, for all channels the following parameters are considered:

- NMOS: STD105N10F7AG

- VGS\_TYP: 12 V

- IBIAS\_ON = 530 μA

- IBIAS\_OFF = 480 μA

Table 4 shows the configuration under analysis.

Safe and starter relays are implemented with HS switches because they need to disconnect the loads from the battery supply in case of safety issues, system stress or simply when the loads are not used. In general, these switches are always ON during normal operation and therefore their absorption is mainly related to the pull-down network and the internal biasing. When the application may tolerate a certain voltage drop on the battery line (e.g. lamp), a HS PMOS switch can be used as safe relay. This solution is not recommended for injectors: they need the full battery voltage to be applied in order to speed up the needle lifting phase.

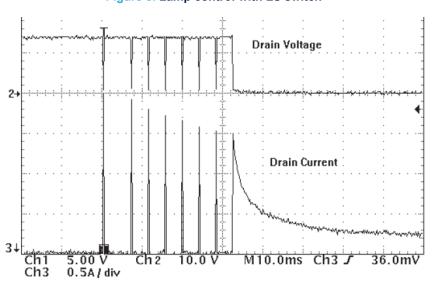

All other switches are mounted LS in order to avoid unnecessary charge pump stress when switching. Some of them are permanently switching (lambda probe heater, see Figure 6), some others like injectors switch only during a time window of fixed length which is periodically activated (see Figure 7). Lamps require an initial switching during the inrush phase, and once the lamp is fully lit, the switch is kept ON in a steady state (see Figure 8).

Table 4. L9945 configuration for CV applications

| Ch. | Function                 | Applicative Considerations                                              |

|-----|--------------------------|-------------------------------------------------------------------------|

| 1   | Safe relay for Injectors | This switch is always ON, unless safety issues occur                    |

| 2   | PFI Injector             | Very high frequency due to small current ripple requirements            |

| 3   | PFI Injector             | Very high frequency due to small current ripple requirements            |

| 4   | Safe relay for Lamps     | This switch is always ON, unless safety issues occur (PMOS)             |

| 5   | Lamp                     | After initial PWM (≈ 200 Hz), the switch is kept ON. (Worst case is DC) |

| 6   | Starter relay            | This switch is always ON, unless safety issues occur                    |

| 7   | Lambda Probe Heater      | Low frequency because thermal phenomena are slow (≈ 100 Hz)             |

| 8   | Lamp                     | After initial PWM (≈ 200 Hz), the switch is kept ON. (Worst case is DC) |

AN5074 - Rev 1 page 11/25

-1.5000 10.000 -1.5000 0.000 Signal voltage regulated heating

-20.000 -10.000 0.000 -20.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 -1.500 0.000 0.000 -1.500 0.000 0.000 -1.500 0.000 0.000 -1.500 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.000 0.

Figure 6. Lambda probe heater control

GADG1109171125PS

Figure 7. Peak and Hold injection example

AN5074 - Rev 1 page 12/25

Figure 8. Lamp control with LS switch

GADG1109171155PS

# 3.1 Proposed configuration for normal operation

Figure 9. Example 1: CV applications with independent PWM an all channels

| Battery supply voltage [V] |      |          |                |             |           |             | CV            | 28  |             |

|----------------------------|------|----------|----------------|-------------|-----------|-------------|---------------|-----|-------------|

| Channel configuration      |      |          |                |             |           |             |               |     |             |

| СН                         | SIDE | FET TYPE | Qgs_typ [nC]   |             |           | Cm [nF]     | Rpd [kOhm]    | TM% | Imean [mA]  |

| 1                          | HS   | NMOS     | 70             | 0           | 80.00     | 1.5         | 47            | 20  | 0.942       |

| 2                          | LS   | NMOS     | 70             | 22          | 80.00     | 1.5         | 47            | 20  | 3.192       |

| 3                          | LS   | NMOS     | 70             | 22          | 80.00     | 1.5         | 47            | 20  | 3.192       |

| 4                          | HS   | PMOS     | 70             | 0           | 80.00     | 1.5         | 47            | 20  | 0.000       |

| 5                          | LS   | NMOS     | 70             | 0           | 80.00     | 1.5         | 47            | 20  | 0.942       |

| 6                          | HS   | NMOS     | 70             | 0           | 80.00     | 1.5         | 47            | 20  | 0.942       |

| 7                          | LS   | NMOS     | 70             | 0.1         | 95.00     | 1.5         | 47            | 20  | 0.935       |

| 8                          | LS   | NMOS     | 70             | 0           | 80.00     | 1.5         | 47            | 20  | 0.942       |

| Total charge pump workload |      |          |                |             |           |             |               |     | 11.089      |

|                            |      |          | Color          | Scale For   | Total Wo  | rkload      |               |     |             |

|                            |      |          | Charge pur     | mp capacity | y has bee | en overco   | me            |     |             |

|                            |      |          | ore than 80% o |             |           |             |               |     |             |

|                            |      | Le       | ess than 80% o | f charge pu | ump capa  | acity is be | eing used     |     |             |

|                            |      |          | Colons         | Saala Far-C | honnol M  | Vouldood    |               |     |             |

|                            |      | The ob   |                | Scale For C |           |             | ump conscit   |     |             |

|                            |      |          | annel uses mo  |             |           |             |               |     |             |

|                            |      |          | annel uses les |             |           |             |               |     |             |

|                            |      |          |                |             |           | 3, 1        | la contractor |     | GADG1109171 |

GADG1109171213PS

AN5074 - Rev 1 page 13/25

# 3.2 Load dump

In case of load dump, nothing would change in terms of charge pump stress because even if the battery supply voltage raises up to 60 V, the HS FETs are almost in a DC regime. On the other hand, stress induced by LS switches is not depending on  $V_{PS}$ .

# 3.3 Cold cranking

In case of cold cranking, charge pump capability is compromised and drops down to  $I_{CP\_MAX}$  = 6 mA. Figure 10 shows that full functionality is not achievable, and a reconfiguration is needed to guarantee critical functions such as starter relay and the control one of the two injectors (see Figure 11).

Figure 10. Charge pump stress during cold cranking

| Battery supply voltage [V] |      |          |                                             |              |          |             | MIN        | 3.8 |            |

|----------------------------|------|----------|---------------------------------------------|--------------|----------|-------------|------------|-----|------------|

| Channel configuration      |      |          |                                             |              |          |             |            |     |            |

| СН                         | SIDE | FET TYPE | Qgs_typ [nC]                                |              |          |             | Rpd [kOhm] | TM% | Imean [mA] |

| 1                          | HS   | NMOS     | 70                                          | 0            | 80.00    | 1.5         | 47         | 20  | 0.942      |

| 2                          | LS   | NMOS     | 70                                          | 22           | 80.00    | 1.5         | 47         | 20  | 3.192      |

| 3                          | LS   | NMOS     | 70                                          | 22           | 80.00    | 1.5         | 47         | 20  | 3.192      |

| 4                          | HS   | PMOS     | 70                                          | 0            | 80.00    | 1.5         | 47         | 20  | 0.000      |

| 5                          | LS   | NMOS     | 70                                          | 0            | 80.00    | 1.5         | 47         | 20  | 0.942      |

| 6                          | HS   | NMOS     | 70                                          | 0            | 80.00    | 1.5         | 47         | 20  | 0.942      |

| 7                          | LS   | NMOS     | 70                                          | 0.1          | 95.00    | 1.5         | 47         | 20  | 0.935      |

| 8                          | LS   | NMOS     | 70                                          | 0            | 80.00    | 1.5         | 47         | 20  | 0.942      |

|                            |      |          | Total charg                                 | e pump v     | workloa  | ad          |            |     | 11.089     |

|                            |      |          | Color                                       | · Scale For  | Total Wo | rkload      |            |     |            |

|                            |      |          | Charge pui                                  |              |          |             | me         |     |            |

|                            |      | Me       | ore than 80% o                              | of charge p  | ump cap  | acity is be | eing used  |     |            |

|                            |      | Le       | ess than 80% o                              | of charge pu | ump capa | acity is be | eing used  |     |            |

|                            |      |          | 0.1                                         | )I- <b>-</b> | l L.V    | /l - ll     |            |     |            |

|                            |      | The      |                                             | Scale For C  |          |             |            |     |            |

|                            |      |          | annel uses mo<br><mark>annel uses mo</mark> |              |          |             |            |     |            |

|                            |      |          | annel uses mo<br>annel uses les             |              |          |             |            | _   |            |

GADG1109171249PS

AN5074 - Rev 1 page 14/25

Figure 11. Limiting charge pump stress during cold cranking

| Battery supply voltage [V]                                 |      |          |                |             |           |                  | MIN          | 3.8   |            |

|------------------------------------------------------------|------|----------|----------------|-------------|-----------|------------------|--------------|-------|------------|

| Channel configuration                                      |      |          |                |             |           |                  |              |       |            |

| СН                                                         | SIDE | FET TYPE | Qgs_typ [nC]   |             |           |                  | Rpd [kOhm]   | TM%   | Imean [mA] |

| 1                                                          | HS   | NMOS     | 70             | 0           | 80.00     | 1.5              | 47           | 20    | 0.942      |

| 2                                                          | LS   | NMOS     | 70             | 22          | 80.00     | 1.5              | 47           | 20    | 3.192      |

| 3                                                          | LS   | NMOS     | 70             | 22          | 80.00     | 1.5              | 47           | 20    | 0.000      |

| 4                                                          | HS   | PMOS     | 70             | 0           | 80.00     | 1.5              | 47           | 20    | 0.000      |

| 5                                                          | LS   | NMOS     | 70             | 0           | 80.00     | 1.5              | 47           | 20    | 0.000      |

| 6                                                          | HS   | NMOS     | 70             | 0           | 80.00     | 1.5              | 47           | 20    | 0.942      |

| 7                                                          | LS   | NMOS     | 70             | 0.1         | 95.00     | 1.5              | 47           | 20    | 0.000      |

| 8                                                          | LS   | NMOS     | 70             | 0           | 80.00     | 1.5              | 47           | 20    | 0.000      |

| Total charge pump workload                                 |      |          |                |             |           |                  |              | 5.077 |            |

|                                                            |      |          |                |             |           |                  |              |       |            |

|                                                            |      |          |                | Scale For   |           |                  |              |       |            |

|                                                            |      |          | Charge pur     |             | -         |                  |              |       |            |

|                                                            |      |          | ore than 80% o |             |           |                  |              |       |            |

|                                                            |      | Le       | ess than 80% o | i charge po | лир сара  | acity is De      | my useu      |       |            |

|                                                            |      |          | Color S        | Scale For C | hannel V  | /orkloa <u>d</u> |              |       |            |

| The channel uses more than 25% of the charge pump capacity |      |          |                |             |           |                  |              |       |            |

|                                                            |      |          | annel uses mo  |             |           |                  |              |       |            |

|                                                            |      | The ch   | annel uses les | s than 12.5 | 5% of the | charge p         | ump capacity | /     |            |

GADG1109171255PS

# 3.4 Case study: ST L9945 in application

The following case study is based on ST L9945 flexible pre-driver, configured to drive all its 8 channels with independent PWM. Corner cases have been found for CV applications in various operating scenarios.

In the following examples, for all channels the following parameters are considered:

- NMOS: STD105N10F7AG

- V<sub>GS\_TYP</sub>: 12 V

- I<sub>BIAS ON</sub> = 530 μA

- I<sub>BIAS\_OFF</sub> = 480 μA

Figure 12 shows ST L9945 charge pump (VGBHI) while resting. All channels have been enabled but kept OFF. Hence,  $I_{BIAS\ OFF}$  represents the only static leakage, causing almost no ripple on VGBHI pin.

AN5074 - Rev 1 page 15/25

Figure 12. Charge pump resting. All channels enabled but kept OFF

GADG1109171304PS

#### 3.4.1 Typical battery supply

These tests have been performed with VPS = 28 V at room temperature ( $\approx$  25 °C). Starting from an initial switching profile, frequency has been gradually increased until the I<sub>CP\_MAX</sub> = 15 mA has been overcome. Refer to Figure 13.

CV Cm [nF] Rpd [kOhm] TM% Cm [nF] Rpd [kOhm] TM% Imean [mA Qgs typ [nC] Fsw [kHz] dc [%] Qgs\_typ [nC] Fsw [kHz] dc [%] 80.00 80.00 80.00 80.00 HS HS 20 20 NMOS NMOS 1.232 1.232 0.000 LS NMOS 80.00 0.47 20 LS LS NMOS 80.00 0.47 20 HS HS PMOS 70 80.00 0.47 47 20 HS HS **PMOS** 70 80.00 0.47 47 20 PMOS PMOS 20 2.866 2.866 LS NMOS 80.00 20 20 NMOS 80.00 47 20 20 15.128 Charge pump capacity has been overcome Less than 80% of charge pump capacity is being used Less than 80% of charge pump capacity is being used Initial profile Critical profile

Figure 13. Switching profiles for supply typical scenario

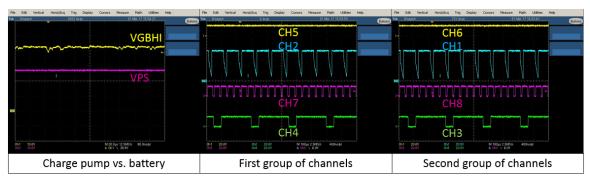

Figure 14 shows the device performance when the initial switching profile is applied. Note how ripple on VGBHI pin has increased, with higher negative peaks corresponding to the simultaneous switching of more than one channel. The external FET gate signal has been monitored on every channel, showing that each output is regularly switching with a stable ON voltage.

AN5074 - Rev 1 page 16/25

Figure 14. Initial profile

image16.png

Figure 15 shows the device performance when the critical switching profile is applied. Note how ripple on VGBHI pin has increased, but still VGBHI is stably above VPS. The external FET gate signal has been monitored on every channel, showing that each output is regularly switching with a stable ON voltage.

Figure 15. Critical profile

image17.png

The 20% tolerance margin guarantees that the critical switching profile can be sustained without any issue.

Note:

L9945 was able to sustain 6 NMOS channels switching at 25 kHz at room temperature without causing any charge pump undervoltage. However, such condition is too stressing and is not guaranteed over the whole temperature range, since performances may degrade too much and the 20% tolerance margin might be insufficient.

Junction temperature has been monitored while switching at critical profile. After an initial transient,  $T_j$  was stable at 73 °C, meaning that a self-heating  $\Delta T$  = 48 °C occurs while performing in this condition. Since L9945 has an operating range equal to [-40;+150] °C, the critical profile can be sustained without issues if ambient temperature  $T_a$  is below 102 °C. Hence, operation is more limited by self-heating rather than charge pump capability.

Note:

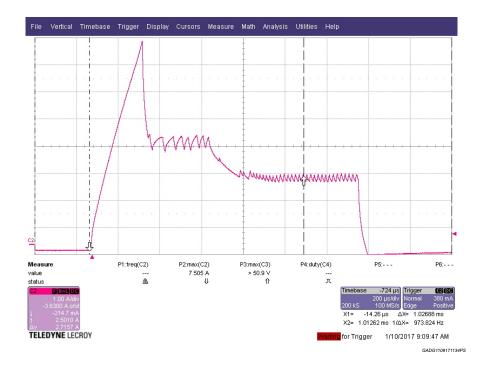

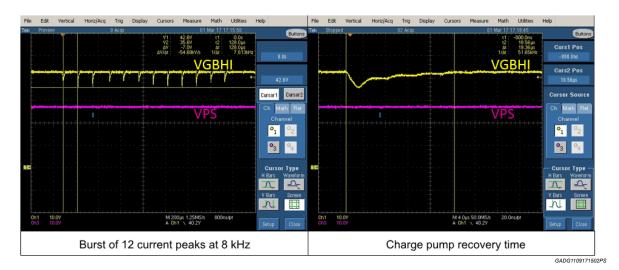

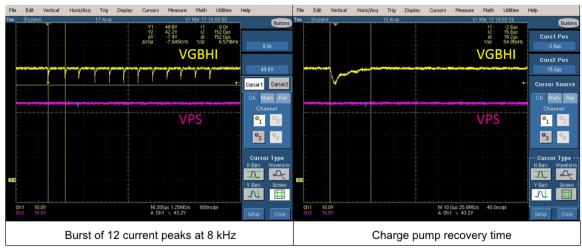

Consider that in real applications loads are not active 100% of the time. Many of them, such as injectors, have a windowed operation. Hence, self-heating should be less than the estimated  $\Delta T$ , that was measured with all channels continuously switching. The actual self-heating is strongly dependent on the application type and package thermal impedance. Results shown here can be considered as a reliable worst case estimation for  $\Delta T$ . A current peak stress test has also been performed, with 6 NMOS channels switching simultaneously at 8 kHz frequency. Results are plotted in Figure 16. Note how peaks on VGBHI are much higher in respect of the previous situations, where the phase relation between control signals was random. When 6 signals are in phase, the negative peak can be as high as 7 V. The recovery time after such peak has been measured and it's around 20  $\mu$ s, meaning that simultaneous switching could be sustained even at 50 kHz at room temperature. Obviously, such estimation doesn't take into account the temperature variations and the process spread. To be conservative, a 50% tolerance margin can be considered so simultaneous switching on 6 NMOS channels can be sustained without issues at a 25 kHz rate, given the configuration reported in the present case study.

AN5074 - Rev 1 page 17/25

Figure 16. Current peaks analysis: charge pump vs battery

#### 3.4.2 Max operating voltage

These tests have been performed with VPS = 36 V at room temperature ( $\approx$  25 °C). Starting from an initial switching profile, frequency has been gradually increased until the  $I_{CP\_MAX}$  = 15 mA has been overcome. Refer to Figure 17.

MAX\_OP 36.0 MAX\_OP dc [%] 80.00 80.00 FET TYPE Qgs\_typ [nC] Fsw [kHz] dc [%] 80.00 80.00 0.47 0.47 FET TYPE SIDE Cm [nF] TM% SIDE TM% NMOS NMOS 0.47 HS HS 20 20 10 10 NMOS 1.232 1.232 0.47 LS LS NMOS 80.00 0.47 20 20 LS NMOS 80.00 HS HS LS PMOS 80.00 0.47 47 20 0.000 HS PMOS 70 80.00 0.47 47 20 20 0.000 NMOS 80.00 0.47 NMOS 80.00 0.47 12.156 Charge pump capacity has been overcome Charge pump capacity has been overcome Initial profile Critical profile

Figure 17. Switching profiles for supply typical scenario

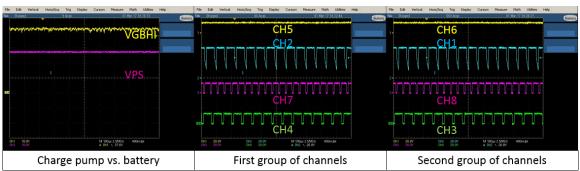

Figure 18 shows the device performance when the initial switching profile is applied. Note how ripple on VGBHI pin has increased, with higher negative peaks corresponding to the simultaneous switching of more than one channel. The external FET gate signal has been monitored on every channel, showing that each output is regularly switching with a stable ON voltage.

AN5074 - Rev 1 page 18/25

Figure 18. Initial switching profile

GADG1109171523PS

Figure 19 shows the device performance when the critical switching profile is applied. Note how ripple on VGBHI pin has increased, but still VGBHI is stably above VPS. The external FET gate signal has been monitored on every channel, showing that each output is regularly switching with a stable ON voltage.

Pie 128 Vertical Novicidica Trig Display Cursors Measure Nath Ullines Need Procedure Trig Display Cursors Nath Ullines Nath U

Figure 19. Critical switching profile

GADG1109171529PS

The 20% tolerance margin guarantees that the critical switching profile can be sustained without any issue.

Note:

L9945 was able to sustain 6 NMOS channels switching at 25 kHz at room temperature without causing any charge pump overvoltage. However, such condition is too stressing and is not guaranteed over the whole temperature range, since performances may degrade too much and the 20% tolerance margin might be insufficient.

Junction temperature has been monitored in while executing critical profile. After an initial transient,  $T_j$  was stable at 90 °C, meaning that a self-heating  $\Delta T$  = 65 °C occurs while performing in this condition. Since L9945 has an operating range equal to [-40;+150] °C, the critical profile can be sustained without issues if ambient temperature  $T_a$  is below 85 °C. Hence, operation is more limited by self-heating rather than charge pump capability.

Note:

Consider that in real applications loads are not active 100% of the time. Many of them, such as injectors, have a windowed operation. Hence, self-heating should be less than the estimated  $\Delta T$ , that was measured with all channels continuously switching. The actual self-heating is strongly dependent on the application type and package thermal impedance. Results shown here can be considered as a reliable worst case estimation for  $\Delta T$ .

A current peak stress test has also been performed, with 6 NMOS channels switching simultaneously at 8 kHz frequency. Results are plotted in Figure 20. Note how peaks on VGBHI are much higher in respect of the previous situations, where the phase relation between control signals was random. When 6 signals are in phase, the negative peak can be as high as 7 V. The recovery time after such peak has been measured: it's around 20  $\mu$ s, meaning that simultaneous switching could be sustained even at 50 kHz at room temperature. Obviously, such estimation doesn't take in account the temperature variations and the process spread. To be conservative, a 50% tolerance margin can be considered: simultaneous switching on 6 NMOS channels can be sustained without issues at a 25 kHz rate, given the configuration reported in the present case study.

AN5074 - Rev 1 page 19/25

Figure 20. Current peaks analysis: charge pump vs battery

GADG1109171539PS

AN5074 - Rev 1 page 20/25

# **Revision history**

Table 5. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 20-Mar-2019 | 1       | Initial release. |

AN5074 - Rev 1 page 21/25

# **Contents**

| 1   | Char   | ge pum   | np stress factors                                                              | 2  |

|-----|--------|----------|--------------------------------------------------------------------------------|----|

|     | 1.1    | Charge   | e pump capability                                                              | 2  |

|     | 1.2    | Target   | gate-to-source voltage of the external driver                                  | 3  |

|     | 1.3    | Charge   | e pump intervention based on driver side (HS/LS)                               | 4  |

|     | 1.4    | Externa  | al FET gate charge                                                             | 5  |

|     | 1.5    | Externa  | al Miller capacitor charge                                                     | 6  |

|     | 1.6    | Externa  | al pull down network                                                           | 6  |

|     | 1.7    | Eventu   | al Internal absorption due to leakage and polarization of pre-driver circuitry | 7  |

|     | 1.8    | Tolerar  | nce Margin                                                                     | 7  |

| 2   | Tota   | charge   | e pump stress evaluation                                                       | 8  |

|     | 2.1    | Single   | channel mean absorption                                                        | 8  |

|     | 2.2    | Total cl | harge pump absorption                                                          | 8  |

|     |        | 2.2.1    | L9945 Charge pump stress calculator                                            | 8  |

|     | 2.3    | Key po   | pints for a robust configuration                                               | 9  |

| 3   | Case   | study:   | ST L9945 configuration for CV applications                                     | 11 |

|     | 3.1    | Propos   | sed configuration for normal operation                                         | 13 |

|     | 3.2    | Load d   | lump                                                                           | 13 |

|     | 3.3    | Cold cr  | ranking                                                                        | 14 |

|     | 3.4    | Case s   | study: ST L9945 in application                                                 | 15 |

|     |        | 3.4.1    | Typical battery supply                                                         | 16 |

|     |        | 3.4.2    | Max operating voltage                                                          | 18 |

| R۵۱ | rision | history  |                                                                                | 21 |

# **List of tables**

| Table 1. | Charge pump electrical characteristics  |

|----------|-----------------------------------------|

| Table 2. | On/Off states                           |

| Table 3. | Absolute maximum ratings                |

|          | L9945 configuration for CV applications |

| Table 5. | Document revision history               |

AN5074 - Rev 1 page 23/25

# **List of figures**

| Figure 1.  | Charge pump block diagram                                       | . 2 |

|------------|-----------------------------------------------------------------|-----|

| Figure 2.  | HS and LS NMOS biasing                                          | . 5 |

| Figure 3.  | STD105N10F7AG: Gate charge vs Gate-to-Source Voltage            | . 5 |

| Figure 4.  | Battery voltage profile during a cold cranking event            | . 9 |

| Figure 5.  | Load dump in CV systems                                         | 10  |

| Figure 6.  | Lambda probe heater control                                     | 12  |

| Figure 7.  | Peak and Hold injection example                                 | 12  |

| Figure 8.  | Lamp control with LS switch                                     | 13  |

| Figure 9.  | Example 1: CV applications with independent PWM an all channels | 13  |

| Figure 10. | Charge pump stress during cold cranking                         | 14  |

| Figure 11. | Limiting charge pump stress during cold cranking                | 15  |

| Figure 12. | Charge pump resting. All channels enabled but kept OFF          | 16  |

| Figure 13. | Switching profiles for supply typical scenario                  | 16  |

| Figure 14. | Initial profile                                                 | 17  |

| Figure 15. | Critical profile                                                | 17  |

| Figure 16. | Current peaks analysis: charge pump vs battery                  | 18  |

| Figure 17. | Switching profiles for supply typical scenario                  | 18  |

| Figure 18. | Initial switching profile                                       | 19  |

| Figure 19. | Critical switching profile                                      | 19  |

| Figure 20. | Current peaks analysis: charge pump vs battery                  | 20  |

|            |                                                                 |     |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2019 STMicroelectronics - All rights reserved

AN5074 - Rev 1 page 25/25