# STEVAL-IPFC01V1 3 kW three channel interleaved PFC with STNRGPF01 digital controller

#### Introduction

The STEVAL-IPFC01V1 is a 3 kW interleaved PFC evaluation board for the STNRGPF01 digital configurable IC, which is able to drive up to three channels in an interleaved PFC for industrial applications.

The evaluation board achieves high power density (52 W/inch<sup>3</sup>), thanks to a compact layout with small magnetic components, which is possible because of the interleaving effect and chosen switching frequency.

Moreover, the PFC is used to satisfy the IEC 61000-3-2 standard for electrical equipment.

Figure 1. STEVAL-IPFC01V1 reference design

The STNRGPF01 controller is embedded on a separate control board and implements mixed signal (analog/digital) average current mode control in CCM at a fixed frequency. The analog section ensures cycle by cycle current regulation, while digital control manages the non-time critical operations, providing further flexibility.

The device can be customized for different applications by using a dedicated software tool.

#### - RELATED LINKS -

Visit the STNRGPF01 web folder on www.st.com for all the available data and information regarding the device

# 1 Safety instructions

#### Danger:

The evaluation board uses voltage levels that can cause serious injury and even death.

Do not touch any of the boards immediately after disconnecting the input power supply as the charged capacitors need time to discharge.

Due to the high power density, the board components and the heat sink can become very hot and cause severe burns when touched.

This board is intended for use by skilled technical personnel who are suitably qualified and familiar with the installation, use and maintenance of power electronic systems. The same personnel must be aware of and must apply national accident prevention rules.

The electrical installation shall be completed in accordance with the appropriate requirements (e.g., cross-sectional areas of conductors, fusing, and GND connections).

AN5235 - Rev 2 page 2/54

#### 2 Functional overview

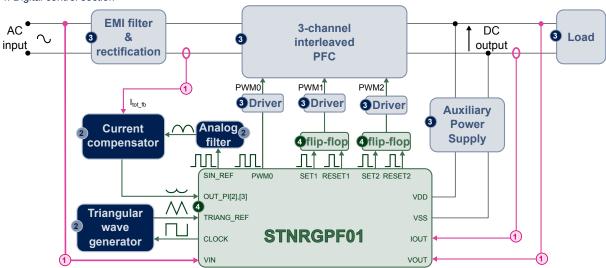

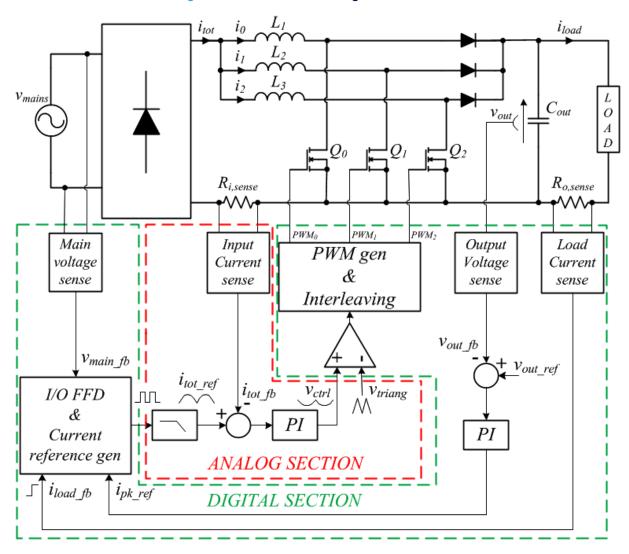

Figure 2. STEVAL-IPFC01V1 block diagram

- 1. I/O measurement signals

- 2. Analog circuitry

- 3. Power stage

- 4. Digital control section

When an AC input voltage in the appropriate range is supplied, the DC output voltage increases up to the peak value of the line input voltage and the auxiliary power supply starts supplying voltages for the STNRGPF01 and drivers.

I/O measurement signals are used to:

- Verify starting and operating conditions (for example, 50/60 Hz, load/no-load start-up etc.)

- Regulate DC output voltage

- Generate feed-forward compensation, phase shedding and current balance functions

- Trigger cooling system and safety shut-down (for example, due to over or undervoltage conditions)

The STNRGPF01 outputs a sinusoidal current reference (SIN\_REF) for the input current regulation performed by analog circuitry, which provides the signals (TRIANG\_REF, OUT\_PI[2],[3]) for triangular-carrier PWM modulation.

The master PWM signal (PWM0) directly drives the first channel, while two external flip-flops receive the set and reset signals from the STNRGPF01 controller and generate the interleaved PWM signals for the other channels (PWM1, PWM2).

The status LEDs indicate the following conditions:

- Green LED: PFC\_OK, start-up has completed

- Red LED: PFC\_FAULT, a fault has occurred

Certain STNRGPF01 functions and parameters are configurable through the eDesign Suite tool.

– RELATED LINKS -

7 PFC controller customization with eDesign Suite on page 31

AN5235 - Rev 2 page 3/54

#### 3 Power factor correction

In many applications, ranging from telecom to common industrial power supplies (SMPS), active Power Factor Corrector (PFC) converters are used as the first stage in AC/DC conversion to draw a sinusoidal-shape input current in phase with grid voltage.

PFCs allow any downstream electrical appliance to appear as a purely resistive load, and improve the overall grid efficiency.

# 3.1 Power factor (PF) - definition

The total power absorbed by a load connected to the grid is known as apparent power, which includes two components:

- 1. Real power: the power that actually produces work (e.g., motion, heating) in a system.

- 2. Reactive power: required by inductive loads for normal operation.

The ratio between real power and apparent power is known as power factor (PF):

$$PF = \frac{realpower}{apparentpower} \tag{1}$$

In a real system, the PF can be calculated as:

$$PF = displacement factor \times distortion factor = \frac{\cos\phi}{\sqrt{1 + THD^2}}$$

(2)

where:

- $\cos \phi$  = displacement factor: the phase shift between input current and line voltage.

- $\frac{1}{\sqrt{1 + THD^2}}$  = distortion factor: the PF degradation due to the harmonic component of input current.

The total harmonic distortion (THD) takes into account the amplitude of input current harmonics with respect to the fundamental component:

$$THD = \sqrt{\sum_{i=2}^{n} \left(\frac{I_i}{I_1}\right)^2} \tag{3}$$

Where:

- I<sub>1</sub> = input current at fundamental frequency

- $I_i = i^{th}$  harmonic of input current

The ideal condition is to have a displacement factor of one and a THD as low as possible, so the apparent power is minimized and the size and cost of generators and transmission lines can be reduced.

#### 3.2 Active PFC

As boost circuits are relatively straightforward to design and drive, they are the preferred topology for implementing PFC's.

The boost PFC pre-regulator receives input from the bridge rectifier and delivers a constant DC output voltage (higher than the peak line voltage), while shaping input current at twice the line frequency.

A second conversion stage provides the appropriate voltage for a generic DC or AC load.

AN5235 - Rev 2 page 4/54

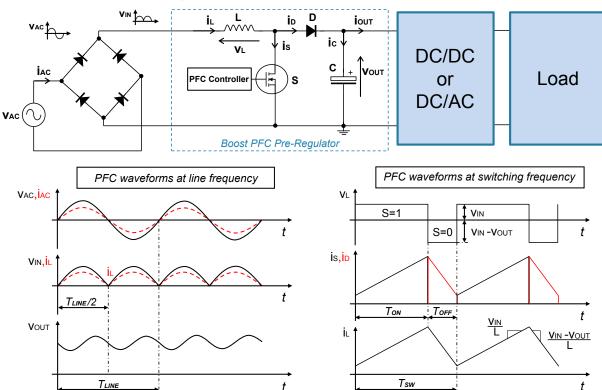

Figure 3. PFC boost circuit and ideal waveforms

As shown in the above figure, the switching period (Tsw) can be divided into the following intervals:

- 1. T<sub>ON</sub> during which the inductor current increases linearly through a switch (S=1).

- T<sub>OFF</sub> after the switch is closed (S=0) and the inductor current flows through the boost diode towards the load.

The following operation modes are defined according to the level which the inductor current drops during T<sub>OFF</sub>:

- 1. Continuous Conduction Mode (CCM)

- 2. Discontinuous Conduction Mode (DCM)

- 3. Critical Conduction Mode (CrM)

Table 1. Boost operation modes

| Inductor current waveform | Operation Mode                      | Features                                                                                              |

|---------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------|

|                           | Continuous Conduction Mode (CCM)    | <ul><li>Always hard-switching</li><li>Inductor value is largest</li><li>Minimal rms current</li></ul> |

| IL.                       | Discontinuous Conduction Mode (DCM) | <ul><li>Highest rms current</li><li>Reduce coil inductance</li><li>Best stability</li></ul>           |

AN5235 - Rev 2 page 5/54

| Inductor current waveform | Operation Mode                 | Features                                                                          |

|---------------------------|--------------------------------|-----------------------------------------------------------------------------------|

|                           | Critical Conduction Mode (CrM) | <ul> <li>Largest rms current</li> <li>Switching frequency is not fixed</li> </ul> |

CCM is the preferred mode for high power PFC converters because it offers advantages like low input peak current (low turn-off switching losses), low input current THD and high power factor.

CCM generates high turn-on switching losses (hard switching), however, which is why parallel solutions are often preferable.

#### 3.2.1 Interleaving

Interleaving consists of paralleling two or more small stages (channels) instead of one larger channel. The advantages of interleaving come at the expense of circuit simplicity, so this architecture is usually reserved for high power applications, above 600 W.

VIN PFC Controller S1 S2 SN

Figure 4. Interleaved boost circuit N-channel

During normal operation, the PWM driving signals are out of phase by the following amount:

$$phase shift = \frac{360^{\circ}}{number of channels} \tag{4}$$

The total power is shared among the parallel circuits.

The interleaved topology has the following advantages over a traditional single-stage PFC:

- Input current ripple reduction

- EMI filter volume reduction

- Inductor volume reduction

- Output capacitor RMS current value reduction

- · Better power management for the switches

- higher efficiency thanks to channel power management

Through interleaving, the equivalent inductor current ripple is reduced and completely eliminated for certain duty cycle values (e.g., at D=0.5 for two-channel boost; D=0.33 and D=0.66 for 3-channel PFC).

The EMI filter size can therefore be reduced thanks to the higher equivalent switching frequency.

AN5235 - Rev 2 page 6/54

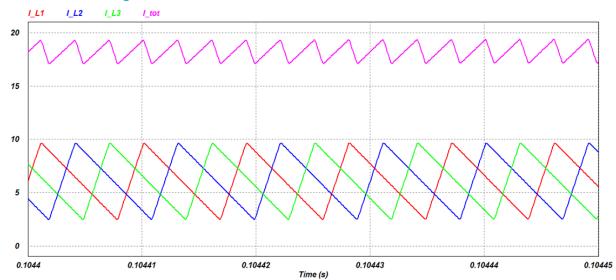

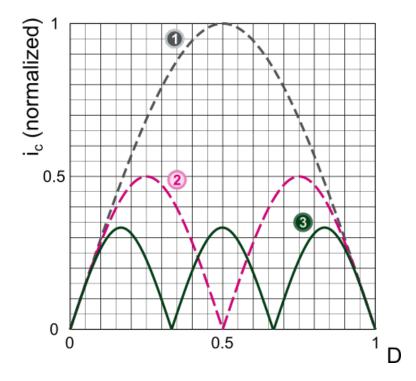

Figure 5. Channel inductor currents vs total current for 3-channel PFC

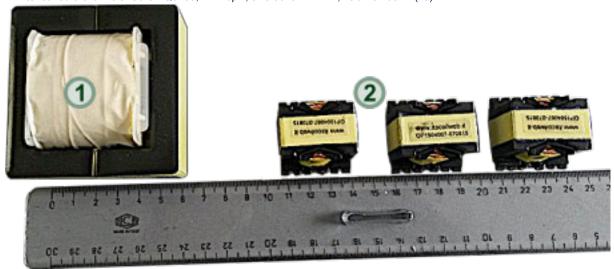

The following diagram shows the difference in inductor size for a single channel PFC with respect to a 3-channel interleaved solution. The 3-channel solution occupies over 40% less volume.

Figure 6. Inductor volume comparison for 3 kW PFC

Switching frequency = 100 KHz

- 1. Single channel: Core EE70, L=150 $\mu$ H, size 70x66x31mm, volume 143cm $^3$

- 2. Interleaved 3 channels: Core PQ3230, L=120µH, size 30x32x27mm, volume 26cm3 (x3)

Interleaving also allows a lower switching frequency than a single-channel PFC for the same power rating, which also helps improve efficiency. Moreover, the inductor current ripple reduction produces a reduced RMS output capacitor current, so capacitors with higher ESR (lower cost) can be used.

AN5235 - Rev 2 page 7/54

Figure 7. Output capacitor current ripple vs duty cycle

- 1. Single channel

- 2. Two channels

- 3. Three channels

Converter efficiency can also be improved by enabling or disabling the parallel channels depending on load percentage (phase shedding).

Even if interleaving leads to an increase in the number of switches, they are still smaller and less costly because the switches only manage a portion of total power. Interleaving also allows the distribution of power dissipation more evenly over the channels.

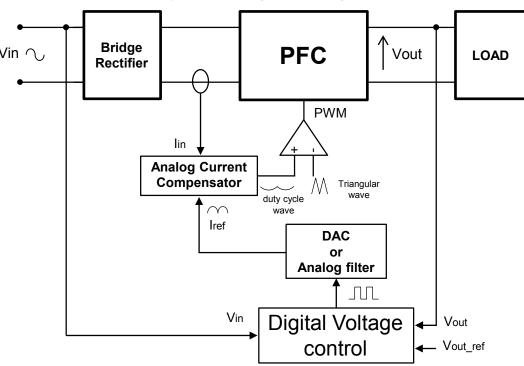

# 3.3 Mixed signal approach

Programmable digital solutions can provide adequate regulation across the entire input and output range of a power supply, which analog ICs alone often cannot deliver. Fully digital solutions, however, require high performance microcontrollers able to manage the high bandwidth of the current control loop.

A good compromise is mixed signal control, where:

- The current loop is managed by a hardware analog compensator, ensuring cycle by cycle regulation.

- The voltage loop is managed by a relatively low-cost digital controller, which provides output voltage

regulation and non-time critical functions such as multiplier, feed-forward compensation, and undervoltage or

overvoltage protection on the input and output voltages.

AN5235 - Rev 2 page 8/54

Figure 8. Mixed signal block diagram

For lower end controllers that do not include a DAC, the current reference can be generated through a PWM waveform, which is then filtered to become the sinusoidal reference ( $I_{ref}$ ) for the current loop.

AN5235 - Rev 2 page 9/54

#### 4 PFC control

The STNRGPF01 three-channel interleaved CCM PFC digital controller offers the advantages of a very high end digital solution without the typical limits of analog controllers.

The STNRGPF01 can drive a PFC in CCM at a fixed frequency, using mixed signal (analog/digital) Average Current Mode control (ACM) to deliver lower inductor ripple current, less EMI filtering, reduced RMS input current and operation at high power levels.

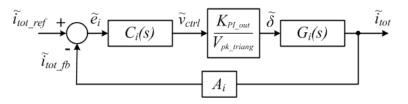

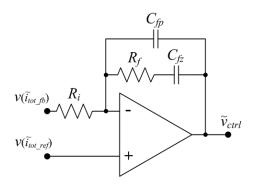

The following figure shows cascaded control of voltage and current loops, which determines the output voltage by regulating the total average inductor current.

Figure 9. STNRGPF01 mixed signal block scheme

This type of control is designed for fast transient responses to avoid large over and under-shoots on the output voltage when the mains voltage changes suddenly or a load current step occurs.

The system works in the following way:

- The difference between output voltage feedback v<sub>out\_fb</sub> and reference v<sub>out\_ref</sub> is sent to a digital PI, which calculates the peak total input average current i<sub>pk\_ref</sub>.

- The PFC current reference is internally generated and exits the I/O FFD block as a PWM waveform; after filtering it becomes the total average sinusoidal input current reference i<sub>tot\_ref</sub> for the inner current loop (analog section, red dashed line).

AN5235 - Rev 2 page 10/54

- The difference between current reference i<sub>tot\_ref</sub> and input current feedback i<sub>tot\_fb</sub> is sent to an analog PI; the

master PWM signal is generated by comparing the analog PI output v<sub>ctrl</sub> and a triangular wave v<sub>triang</sub> at

switching frequency.

- 4. Finally, interleaving produces three 120° phase shifted PWM signals (180° for two channels) to drive the three power switches.

### 4.1 Converter modeling

The interleaved boost converter small-signal transfer functions are obtained through the following operations:

- State-space averaging (SSA), used to average the converter behavior over a switching period, so the

resulting small-signal model is only valid if the control loop bandwidth is suitably lower than the switching

frequency.

- 2. Linearization with Taylor's series around an operating point.

The small-signal transfer functions are useful to calculate the PI regulator parameters and satisfy bandwidth and phase margin specifications for control loops.

For the sake of simplicity, we shall assume that:

- · The converter operates in CCM mode only.

- Active and passive components are ideal.

- The parallel boost inductors are identical and the total power is shared symmetrically across the channels.

- Perturbations on the main voltage are neglected and the voltage is assumed to be constant across several switching cycles.

# 4.2 Current loop design

Figure 10. Current loop block diagram

In the following equations, the tilde (~) symbol above a letter indicates a small-signal variable, while uppercase

letters refer to steady-state operating point variables.

The control-to-input current transfer function is:

$$G_{i}(s) = \frac{\tilde{i}_{tot}}{\tilde{\delta}} = \frac{C_{OUT}V_{OUT}^{3}s + P_{OUT}\left(1 + \frac{1}{\eta}\right)V_{OUT}}{C_{OUT}L_{PFC}V_{OUT}^{2}s^{2} + L_{PFC}P_{OUT}s + N_{ch}V_{IN}^{2}}$$

$$(5)$$

Where:

Note:

- $\tilde{i}_{tot}$  = small-signal total input average inductor current

- $\tilde{i}_{tot}$   $_{ref}$  = small-signal total input average current reference

- $\tilde{i}_{tot\_fb}$  = small-signal total input average inductor current sensing

- $\tilde{e}_i$  = small-signal current error

- $\tilde{v}_{ctrl}$  = small-signal control voltage (analog PI out)

- $\tilde{\delta}$  = small-signal duty cycle

- $V_{pk\ triang}$  = peak-to-peak voltage of triangular wave (carrier at switching frequency)

- $K_{PI\_out}$  = scale factor used to match PI maximum out voltage and  $V_{pk\_triang}$  (resistive divider)

- V<sub>IN</sub> = rms input voltage

- V<sub>OUT</sub> = rms output voltage

- $P_{OUT}$  = output power

AN5235 - Rev 2 page 11/54

- $N_{ch}$  = number of channels

- $L_{PFC}$  = single channel boost inductor

- $C_{OUT}$  = output capacitor

- $\eta$  = estimated efficiency

- $A_i$  = Input current sensing gain

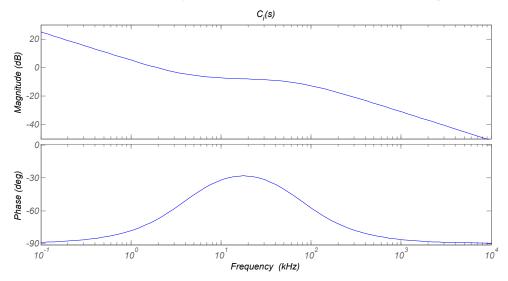

- $C_i(s)$  = Input current compensator transfer function

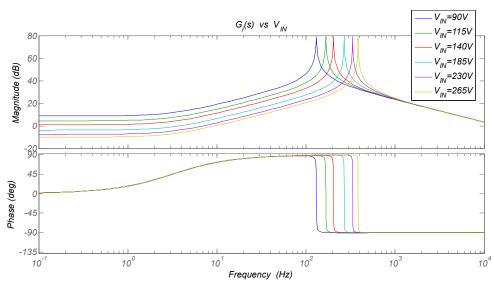

While this formula suggests that  $G_i(s)$  depends on the number of channels and operating input voltage, the following figures show that they do not affect the Bode diagram behavior at high frequencies (current loop crossover frequency).

Figure 11. Control-to-input current TF vs main voltage  $V_{\text{IN}}$  (rms)

AN5235 - Rev 2 page 12/54

Figure 12. Control-to-input current TF vs Number of active channels N<sub>ch</sub>

so  $G_i(s)$  can be simplified as:

$$G_{\hat{i}}(s) = \frac{\tilde{i}_{tot}}{\tilde{\delta}} \simeq \frac{V_{OUT}}{sL_{PFC}}$$

(6)

The typical PI compensator transfer function is:

$$C_{i}(s) = \frac{K_{P\_Itot}s + K_{I\_Itot}}{s} \tag{7}$$

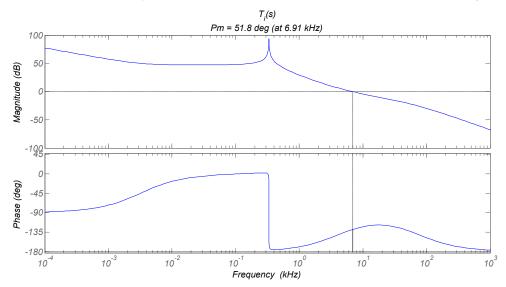

with one pole at zero frequency  $p_i = 0$  to reset the steady-state error and one zero  $z_i = -\frac{K_{I\_Itot}}{K_{P\_Itot}}$  to achieve the desired phase margin at crossover frequency of the following open loop transfer function:

$$T_{i}(s) = C_{i}(s)L_{i}(s) \tag{8}$$

Where:

•

$$L_i(s) = \frac{K_{PI\_out}}{V_{pk\_triang}} A_i G_i(s)$$

Based on general Bode criteria, the following equations ensure system stability for a desired bandwidth  $\omega_{Ti\_des}$  (crossover pulsation) and phase margin  $PM_{i\ des}$

$$\begin{cases}

|T_i(j\omega_{Ti\_des})| = 1 \\

\angle T_i(j\omega_{Ti\_des}) = -180^\circ + PM_{i\_des}

\end{cases}$$

(9)

Current loop crossover frequency  $f_{Ti\_des} = \frac{\omega_{Ti\_des}}{2\pi}$  must be selected in the range:

$$f_{line} \ll f_{Ti\_des} \ll \frac{f_{SW}}{2} \tag{10}$$

Where:

- $f_{line}$  = line voltage frequency

- $f_{SW}$  = switching frequency

This relationship is necessary for good input current regulation and switching noise immunity. Crossover frequency and phase margin for current loop are typically selected as:

AN5235 - Rev 2 page 13/54

$$\begin{cases} f_{Tides} = 2 - 10kHz \\ PM_{ides} = 45 - 60^{\circ} \end{cases}$$

$$\tag{11}$$

So the compensator parameters are calculated by:

$$\begin{cases}

K_{I\_Itot} = \frac{\omega_{Ti\_des}}{|L_i(j\omega_{Ti\_des})|\sqrt{1 + \tan^2(PM_{i\_des} - 90^\circ - \angle L_i(j\omega_{Ti\_des}))}} \\

K_{P\_Itot} = \frac{K_{I\_Itot} \tan(PM_{i\_des} - 90^\circ - \angle L_i(j\omega_{Ti\_des}))}{\omega_{Ti\_des}}

\end{cases}$$

(12)

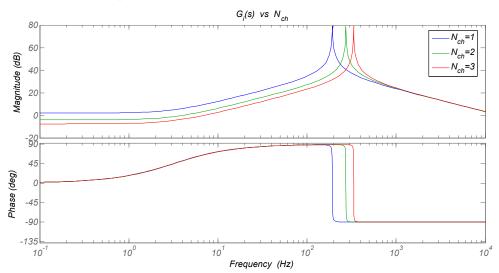

As the current loop is performed in hardware, a PI Type II OP-AMP compensator is used:

Figure 13. PI Type II OP-AMP compensator

The transfer function is:

$$C_{i\_opamp}(s) = \frac{1}{(C_{fz} + C_{fp})R_i} \frac{C_{fz}R_{f}s + 1}{s \left(\frac{C_{fz}C_{fp}R_{f}}{(C_{fz} + C_{fp})}s + 1\right)}$$

(13)

the locations of the poles and zero are:

•

$$f_{pi0} = 0$$

•

$$f_{pi1} = \frac{\left(C_{fz} + C_{fp}\right)}{2\pi C_{fz}C_{fp}R_f} \approx \frac{1}{2\pi C_{fp}R_f}$$

$$f_{zi1} = \frac{1}{2\pi C_{fz} R_f}$$

Comparing Eq. (7) with Eq. (13), an additional high-frequency pole appears in Eq. (13). It is given by capacitor  $C_{fp}$  and is usually set at half the switching frequency to attenuate switching noise without interfering with current loop regulation:

$$\begin{cases} C_{fp} \ll C_{fz} \\ \frac{f_{SW}}{2} \le f_{pi1} \le f_{SW} \end{cases} \tag{14}$$

Proportional and integral gain of the compensator determines the passive network design:

$$\begin{cases} R_i = \frac{1}{C_{fz}K_{I\_Itot}} \\ R_f = R_iK_{P\_Itot} \\ C_{fp} = \frac{1}{\pi f_{sw}R_f} \left( f_{pi1} = \frac{f_{sw}}{2} \right) \end{cases}$$

$$(15)$$

As we need to calculate four components from three equations, capacitor  $\mathcal{C}_{fz}$  must be set. Due to the high-frequency pole, the actual phase margin decreases a few degrees (with respect to a simple PI compensator), which is compensated by using a slightly larger phase margin.

AN5235 - Rev 2 page 14/54

### 4.3 Voltage loop design

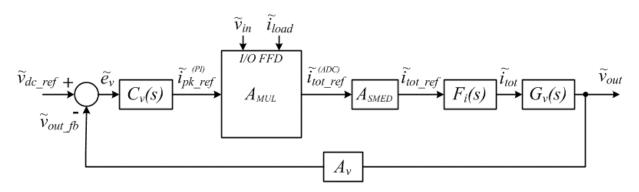

Figure 14. Complete control loop block diagram

Note: In the following equations, the tilde (~) symbol above a letter indicates a small-signal variable, while uppercase letters refer to steady-state operating point variables.

The control-to-output voltage transfer function is:

$$H_{v}(s) = \frac{\tilde{v}_{out}}{\tilde{\delta}} = \frac{2\left(N_{ch}V_{IN} - \frac{P_{OUT}}{\eta V_{IN}}L_{PFC}s\right)V_{OUT}^{2}}{C_{OUT}L_{PFC}V_{OUT}^{2}s^{2} + L_{PFC}P_{OUT}s + N_{ch}V_{IN}^{2}}$$

$$\tag{16}$$

But in this case, it is useful to exploit the input current-to-output voltage transfer function:

$$G_{v}(s) = \frac{\tilde{v}_{out}}{\tilde{i}_{tot}} = \frac{\tilde{v}_{out}}{\tilde{\delta}} \frac{\tilde{\delta}}{\tilde{i}_{tot}} = \frac{2\left(N_{ch}V_{IN} - \frac{P_{OUT}}{\eta V_{IN}}L_{PFCs}\right)V_{OUT}^{2}}{C_{OUT}V_{OUTS}^{3} + P_{OUT}\left(1 + \frac{1}{\eta}\right)V_{OUT}}$$

$$\tag{17}$$

Where:

- $\tilde{v}_{out}$  = small-signal output voltage

- $\tilde{v}_{out\ fb}$  = small-signal output voltage sense

- $\tilde{v}_{dc\ ref}$  = small-signal output voltage reference

- $\tilde{v}_{in}$  = small-signal input voltage sense

- $\tilde{i}_{load}$  = small-signal load current sense

- $\tilde{e}_v$  = small-signal voltage error

- $ilde{i}_{pk\_ref}^{(PI)}$  = small-signal PI peak current reference

- $\tilde{i}_{tot\_ref}^{(ADC)}$  = small-signal digital sinusoidal current reference

- F<sub>i</sub>(s) = Input current closed-loop transfer function

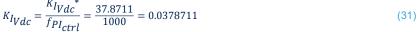

- $C_v(s)$  = Output voltage compensator transfer function

- $A_{MUL}$  = Digital multiplier gain for digital current reference generation

- $A_{SMED}$  = Digital to analog gain for analog current reference generation

- $A_v$  = Output voltage sensing gain

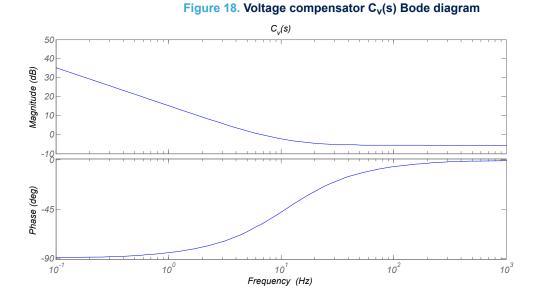

Since the voltage loop crossover frequency is generally selected in the 5-15 Hz range, the right half plane zero (higher frequencies > 20 kHz) can be neglected.

The I/O FFD is currently seen as a constant gain ( $A_{MUL}$ ). The output voltage loop regulation is performed by a digital PI:

$$C_{v}(s) = \frac{K_{P} V dc^{s} + K_{I} V dc}{s} \tag{18}$$

so the PI parameter calculations can be performed by using the same procedure as in current loop design. Starting from system specifics:

AN5235 - Rev 2 page 15/54

$$\begin{cases} f_{Ti\_des} = 5 - 15Hz \\ PM_{i\_des} = 45 - 60^{\circ} \end{cases}$$

(19)

The design equations are:

$$\begin{cases}

|T_{v}(j\omega_{Tv\_des})| = 1 \\

\angle T_{v}(j\omega_{Tv\_des}) = -180^{\circ} + PM_{v\_des}

\end{cases}$$

(20)

Where:

- $T_{v}(s) = C_{v}(s)L_{v}(s)$

- $L_v(s) = A_{MUL}A_{SMED}F_iG_v(s)A_v$

Hence, the compensator parameters are:

$$\begin{cases} K_{I\_Vdc} = \frac{\omega_{Tv\_des}}{|L_i(j\omega_{Tv\_des})|\sqrt{1 + \tan^2(PM_{v\_des} - 90^\circ - \angle L_v(j\omega_{Tv\_des}))}} \\ K_{P\_Vdc} = \frac{K_{I\_Vdc} \tan(PM_{v\_des} - 90^\circ - \angle L_v(j\omega_{Tv\_des}))}{\omega_{Tv\_des}} \end{cases}$$

(21)

# 4.4 I/O feed-forward and current reference generation

When the main voltage or load current changes suddenly, the low bandwidth of the voltage loop may cause output voltage fluctuations.

To counter this effect, the I/O FFD block performs two feed-forwards to reduce the system transient response time.

$\widetilde{i}_{pk\_ref} \xrightarrow{\widetilde{i}_{ff}} + \underbrace{\widetilde{i}_{pk\_ref}}_{\widetilde{i}_{load}} \times \underbrace{K_{ff}}_{\widetilde{v}_{in}} \xrightarrow{\widetilde{i}_{load}} \underbrace{\widetilde{i}_{N_{load}}}_{K_{load}} \times \underbrace{K_{ff}}_{Look-up} \xrightarrow{\widetilde{i}_{load}} \underbrace{\widetilde{i}_{load}}_{Look-up} \times \underbrace{\widetilde{i}_{load}}_{Look-up} \times \underbrace{\widetilde{i}_{load}}_{\widetilde{v}_{in}} \times \underbrace{K_{ff}}_{\widetilde{v}_{in}}$

Figure 15. I/O FFD block

Note:

In the following equations, the tilde (~) symbol above a letter indicates a small-signal variable, while uppercase letters refer to steady-state operating point variables.

The first feed-forward is a load feed-forward that adds a portion of the load current  $\tilde{i}_{ff}$  to the PI output, which helps to rapidly change the peak current reference  $\tilde{i}^*_{pk\_ref}$  when a load step occurs.

$$\tilde{i}_{pk\_ref}^* = \tilde{i}_{pk\_ref}^{(PI)} + \tilde{i}_{ff} \tag{22}$$

For the second feed-forward,  $\tilde{i}^*_{pk\_ref}$  is multiplied by coefficient  $K_{ff}$  to factor in input voltage fluctuations:

$$\tilde{i}_{pk\_ref} = \frac{\tilde{i}_{pk\_ref}^*}{\frac{\tilde{v}_{in}}{V_{IN\_nom}}} = \tilde{i}_{pk\_ref}^* K_{ff}$$

(23)

From the above equation, it is clear that an increase in rms input voltage causes a decrease in  $\tilde{i}_{pk\_ref}$  and vice versa, so the output voltage is maintained relatively constant.

AN5235 - Rev 2 page 16/54

A pseudo-sinusoidal shaped current reference is obtained by multiplying  $\tilde{i}_{pk\_ref}$  for a look-up table:

$$\tilde{i}_{tot\_ref}^{(ADC)} = \tilde{i}_{pk\_ref} A_{MUL} |\sin(\omega t)|$$

(24)

and for Digital to Analog gain:

$$\tilde{i}_{tot\_ref}^{(ANALOG)} = \tilde{i}_{tot\_ref}^{(ADC)} = \tilde{i}_{tot\_ref}^{(ADC)}$$

(25)

The current reference is a PWM signal that must be filtered with appropriate hardware to generate the reference for analog current loop.

# 4.5 Control design example

Typical design parameters for a 3 kW power rating are shown in the following table.

Table 2. Power stage, sensing and current loop parameters

| Design parameter     | Description                             | Value    |

|----------------------|-----------------------------------------|----------|

| POUT                 | output power                            | 3 kW     |

| $N_{ch}$             | Number of channels                      | 3        |

| $v_{IN}$             | rms nominal input voltage               | 230 V    |

| V <sub>OUT</sub>     | rms nominal output voltage              | 400 V    |

| f                    | line frequency                          | 50 Hz    |

| η                    | estimated efficiency                    | 98 %     |

| $L_{PFC}$            | single channel boost inductor           | 120 µH   |

| $c_{OUT}$            | output capacitor                        | 4x470 μF |

| $V_{pk\_triang}$     | peak-to-peak voltage of triangular wave | 2 V      |

| K <sub>PI_out</sub>  | PI out scale factor                     | 0.4054   |

| $A_{i}$              | Input current sensing gain              | 0.1491   |

| $A_{\mathcal{V}}$    | Output voltage sensing gain             | 1.9109   |

| $A_{MUL}$            | Digital multiplier gain                 | 3.3086   |

| $A_{SMED}$           | Digital to analog gain                  | 0.001042 |

| $f_{SW}$             | Switching frequency                     | 111 kHz  |

| f <sub>Ti_des</sub>  | Current loop crossover frequency        | 7.5 kHz  |

| $f_{Tv\_des}$        | Voltage loop crossover frequency        | 10 Hz    |

| PM <sub>i_des</sub>  | Current loop phase margin               | 60°      |

| $PM_{v\_des}$        | Voltage loop phase margin               | 60°      |

| f <sub>PI_ctrl</sub> | Voltage loop control frequency          | 1 kHz    |

Using the values in the above table, the compensator parameters are calculated as:

For a zero capacitor  $\mathcal{C}_{fz}=15nF$  , the input PI resistor is:

$$R_i = \frac{1}{C_{fz} K_{I\_Itot}} = \frac{1}{15 \cdot 10^{-9} \cdot 10996} = 6063\Omega$$

(27)

AN5235 - Rev 2 page 17/54

So a commercial 6.2  $k\Omega$  resistor is appropriate.

The feedback resistor value is given by:

$$R_f = R_i K_{P\_Itot} = 6063 \cdot 0.4044 = 2452\Omega \tag{28}$$

So a commercial 2.4  $k\Omega$  resistor is appropriate.

Finally, the high-frequency pole capacitor is calculated with:

$$C_{fp} = \frac{1}{\pi f_{SW} R_f} = \frac{1}{\pi \cdot 111 \cdot 10^3 \cdot 2452} = 1.168 nF$$

(29)

So a 1 nF capacitor is appropriate.

Figure 16. Current compensator C<sub>i</sub>(s) Bode diagram

AN5235 - Rev 2 page 18/54

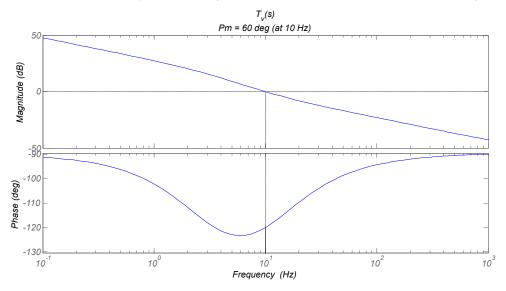

Figure 17. Current open loop transfer function T<sub>i</sub>(s) Bode diagram

The voltage loop compensator parameters can also be calculated:

$$\begin{cases} K_{I\_Vdc}^* = 37.8711 \\ K_{P\_Vdc} = 0.5470 \end{cases}$$

(30)

Note that the integral gain  $K_{l\_Vdc}^*$  cannot be directly used in the firmware calculation routine, but must be divided by the operation frequency of the digital PI, hence:

$$K_{IVdc} = \frac{K_{IVdc}^*}{f_{PI_{ctrl}}} = \frac{37.8711}{1000} = 0.0378711$$

(31)

AN5235 - Rev 2 page 19/54

Figure 19. Voltage open loop transfer function  $T_{\nu}\!\left(s\right)$  Bode diagram

AN5235 - Rev 2 page 20/54

# 5 Power stage design equations

# 5.1 Bridge rectifier

The bridge rectifier selection is based on maximum average input current:

$$I_{IN\_avg(max)} = \frac{2\sqrt{2}}{\pi} I_{IN\_rms(MAX)} = \frac{2\sqrt{2}}{\pi} \frac{P_{OUT}}{\eta \cdot V_{IN\_rms(MIN)} \cdot PF}$$

$$= \frac{2\sqrt{2}}{\pi} \frac{3000}{0.98 \cdot 185 \cdot 0.99} = 15A$$

(32)

Power dissipation is calculated for the GBJ5010 (1000V/50A):

$$P_{BRIDGE} = 2 \cdot V_F \cdot I_{IN\_avg(max)} = 2 \cdot 1 \cdot 15 = 30W$$

(33)

Where:

- $I_{IN\ rms(MAX)}$  = maximum input current (rms)

- $V_{IN\_rms(MIN)}$  = minimum input voltage (rms)

- $P_{OUT}$  = output power

- $\eta$  = PFC efficiency

- PF = power factor

- V<sub>F</sub> = bridge diode forward voltage at 25°C (<1V @100°C; moreover, a higher rated current bridge usually experiences a lower voltage drop, which helps reduce bridge power losses).</li>

# 5.2 Input capacitor

The input capacitor must filter high frequency ripple in the input current. A polypropylene film capacitor rated for maximum input voltage is recommended.

The calculation formula is:

$$C_{in} = \frac{\frac{k_r}{N_{ch}} \cdot I_{IN\_rms(MAX)}}{2\pi \cdot f_{sw} \cdot r \cdot V_{IN\_rms(MIN)}} = \frac{\frac{0.8}{3} \cdot 16.7}{2\pi \cdot 111 \cdot 10^3 \cdot 0.04 \cdot 185} = 863nF$$

(34)

Where:

- $k_r$  = inductor current ripple factor

- r = maximum high frequency voltage ripple factor ( $\Delta V_{IN}/V_{IN}$  = 2-10%)

- $f_{SW}$  = switching frequency

- $N_{ch}$  = number of interleaved channels

A commercially available 1 µF input capacitor is used.

#### 5.3 Boost inductor

The boost inductor is designed to work in CCM.

AN5235 - Rev 2 page 21/54

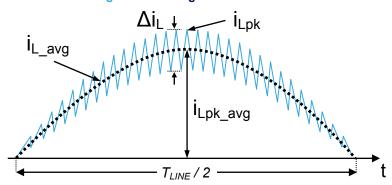

Figure 20. Average inductor current

The duty cycle and maximum average inductor current are evaluated at the minimum line voltage for the rated output power:

$$I_{Lpk\_avg} = \frac{\sqrt{2} \cdot \frac{P_{OUT}}{\eta \cdot N_{ch}}}{V_{IN\_rms(MIN)}} = \frac{\sqrt{2} \cdot \frac{3000}{0.98 \cdot 3}}{185} = 7.8A$$

(35)

$$D = \frac{V_{OUT} - \sqrt{2} \cdot V_{IN\_rms(MIN)}}{V_{OUT}} = \frac{400 - \sqrt{2} \cdot 185}{400} = 0.346$$

(36)

Where:

• *V<sub>OUT</sub>* = nominal output voltage.

So, once the maximum allowable ripple  $(k_r)$  is set, the boost inductor for each channel can be calculated as:

$$L_{PFC} = \frac{\sqrt{2} \cdot V_{IN\_rms(MIN)} \cdot D}{f_{sw} \cdot k_r \cdot I_{Lpk\_avg}} = \frac{\sqrt{2} \cdot 185 \cdot 0.346}{111 \cdot 10^3 \cdot 0.8 \cdot 7.8} = 130 \mu H$$

(37)

$$I_{Lpk} = I_{Lpk\_avg} \cdot \left(1 + \frac{k_r}{2}\right) = 7.8* \left(1 + \frac{0.8}{2}\right) = 10.9A$$

(38)

Hence, the saturation current must be greater than 10.9 A (typical inductor value tolerance is ±10%).

#### 5.4 Power switch

The power switch (MOSFET or IGBT) is selected for minimal power losses. The maximum switch current is evaluated at minimum line voltage (worst case):

$$I_{SW\_rms} = \frac{P_{OUT}/N_{ch}}{V_{IN\_rms}(MIN) \cdot \sqrt{2}} \sqrt{2 - \frac{16 \cdot V_{IN\_rms}(MIN) \cdot \sqrt{2}}{3 \cdot \pi \cdot V_{OUT}}}$$

$$= \frac{3000/3}{185 \cdot \sqrt{2}} \sqrt{2 - \frac{16 \cdot 185 \cdot \sqrt{2}}{3 \cdot \pi \cdot 400}} = 3.6A$$

(39)

#### **5.4.1 MOSFET**

The STW40N60M2 N-channel Power MOSFET with low gate charge is used as the boost switch to manage the high switching frequency requirements. The MOSFET is based on MDmesh $^{\text{TM}}$  M2 technology and features a low on-resistance and excellent output capacitance ( $C_{\text{OSS}}$ ) profile.

The device datasheet provides the necessary values to perform loss calculations.

Conduction losses (worst case R<sub>on(100°C)</sub>=1.8·R<sub>on(25°C)</sub>):

$$P_{cond} = R_{on(100^{\circ}C)} \cdot I_{sw\_rms}^2 = 1.8 \cdot 0.078 \cdot 3.6^2 = 1.82W$$

(40)

Where:

•  $R_{on}$  = Static drain-source on-resistance.

AN5235 - Rev 2 page 22/54

Switching losses (calculated using turn-on and turn-off times):

$$t_{on} = C_{iss} \cdot R_g \cdot \ln \left( \frac{V_g - V_{th}}{V_g - V_{pl}} \right) + C_{rss} \cdot R_g \cdot \left( \frac{V_{ds} - V_{pl}}{V_g - V_{pl}} \right) = = 2.5 \cdot 10^{-9} \cdot 14.4$$

$$\cdot \ln \left( \frac{12 - 3}{12 - 5.3} \right) + 2.4 \cdot 10^{-12} \cdot 14.4 \cdot \left( \frac{400 - 5.3}{12 - 5.3} \right) = 12.66ns$$

(41)

$$t_{off} = C_{iss} \cdot R_g \cdot \ln\left(\frac{V_{pl}}{V_{th}}\right) + C_{rss} \cdot R_g \cdot \left(\frac{V_{ds} - V_{pl}}{V_{pl}}\right) = 2.5 \cdot 10^{-9} \cdot 14.4 \cdot \ln\left(\frac{5.3}{3}\right) + 2.4$$

$$\cdot 10^{-12} \cdot 14.4 \cdot \left(\frac{400 - 5.3}{5.3}\right) = 23.06 ns$$

(42)

$$P_{on} = 0.5 \cdot I_{IN\_avg(max)} \cdot V_{OUT} \cdot t_{on} \cdot f_{sw} = 0.5 \cdot 15 \cdot 400 \cdot 12.66 \cdot 10^{-9} \cdot 111 \cdot 10^{3}$$

$$= 1.4W$$

(43)

$$P_{off} = 0.5 \cdot I_{IN\_avg(max)} \cdot V_{OUT} \cdot t_{on} \cdot f_{sw} = 0.5 \cdot 15 \cdot 400 \cdot 12.66 \cdot 10^{-9} \cdot 111 \cdot 10^{3}$$

$$= 2.56W$$

(44)

#### Where:

- C<sub>iss</sub> = Input capacitance (@V<sub>ds</sub>=V<sub>OUT</sub>)

- C<sub>rss</sub> = Reverse transfer capacitance (@V<sub>ds</sub>=V<sub>OUT</sub>)

- $R_q$  = Sum of intrinsic (internal) and external gate resistance

- $V_q$  = Gate-source driving voltage

- $V_{th}$  = Gate-source threshold voltage

- $V_{nl}$  = Plateau voltage

- $V_{ds}$  = Drain-source voltage

#### **Gate drive loss:**

$$P_g = V_g \cdot Q_g \cdot f_{SW} = 12 \cdot 57 \cdot 10^{-9} \cdot 111 \cdot 10^3 = 0.076W$$

(45)

Where:

•  $Q_q$  = Total gate charge

Output capacitance switching loss:

$$P_{OSS} = E_{OSS} \cdot f_{SW} = 8 \cdot 10^{-6} \cdot 111 \cdot 10^{3} = 0.89W$$

(46)

Where:

E<sub>OSS</sub> = Output capacitance switching energy (@V<sub>ds</sub>=V<sub>OUT</sub>)

#### **Total MOSFET power loss:**

The total power loss is the sum of each specific loss multiplied by the number of interleaved channels:

$$P_{tot} = (P_{cond} + P_{on} + P_{off} + P_g + P_{oss}) \cdot N_{ch} = (1.82 + 1.4 + 2.56 + 0.076 + 0.89) \cdot 3$$

$$= 20.2W$$

(47)

#### 5.5 Boost diode

Like the power switch, appropriate boost diode selection is critical for PFC operation in CCM at high frequencies, in order to minimize the power losses.

The STPSC12065 650 V power Schottky silicon carbide diode offers fast recovery with negligible reverse recovery charge (Qrr) and the minimal capacitive turn-off behavior is independent of temperature.

The average and rms diode currents are calculated from the maximum output power and minimum input voltage, after which the conduction and switching losses can be determined.

$$I_{D\_avg} = \frac{P_{OUT}/N_{ch}}{V_{OUT}} = \frac{3000/3}{400} = 2.5A$$

AN5235 - Rev 2 page 23/54

$$I_{D\_rms} = \frac{P_{OUT}/N_{ch}}{V_{IN\_rms}(MIN) \cdot \sqrt{2}} \sqrt{\frac{16 \cdot V_{IN\_rms}(MIN) \cdot \sqrt{2}}{3 \cdot \pi \cdot V_{OUT}}} = \frac{3000/3}{185 \cdot \sqrt{2}} \sqrt{\frac{16 \cdot 185 \cdot \sqrt{2}}{3 \cdot \pi \cdot 400}} = 4A$$

#### **Conduction losses:**

$$P_{D,cond} = V_{th} \cdot I_{D_{ava}} + R_d \cdot I_{D_{rms}}^2 = 1.02 \cdot 2.5 + 0.065 \cdot 4^2 = 3.6W$$

(48)

Where:

- $V_{th}$  = diode threshold voltage

- $R_d$  = differential resistance

#### **Switching losses:**

$$P_{D,SW} = 0.5 \cdot V_{OUT} \cdot Q_{Ci} \cdot f_{SW} = 0.5 \cdot 400 \cdot 36 \cdot 10^{-9} \cdot 111 \cdot 10^{3} = 0.8W \tag{49}$$

Where:

•  $Q_{Ci}$  = total capacitive charge

Total diode power loss:

$$P_{tot} = (P_{D,cond} + P_{D,sw}) \cdot N_{ch} = (3.6 + 0.8) \cdot 3 = 13.2W$$

(50)

# 5.6 Output capacitor

One of the factors for determining the output capacitor is the PFC output voltage ripple at twice the line frequency:

$$C_{OUT\_R} \ge \frac{P_{OUT}}{2\pi \cdot f \cdot \Delta V_{OUT} \cdot V_{OUT}} = \frac{3000}{2\pi \cdot 50 \cdot 20 \cdot 400} = 1194 \mu F \tag{51}$$

Where:

•  $\Delta V_{OUT}$  = output voltage ripple target

Another factor is the PFC output voltage after a line interruption of a certain duration (hold-up time):

$$C_{OUT\_H} \ge \frac{2 \cdot P_{OUT} \cdot t_{hold_{up}}}{\left(V_{OUT} - \frac{\Delta V_{OUT}}{2}\right)^2 - V_{OUT(MIN)}^2} = \frac{2 \cdot 3000 \cdot 20 \cdot 10^{-3}}{\left(400 - \frac{20}{2}\right)^2 - 300^2} = 1932 \mu F \tag{52}$$

Where:

- $V_{OUT(MIN)}$  = minimum allowable output voltage after a line interruption

- $t_{hold\_up}$  = hold-up time

We select the larger of the two factors:

$$C_{OUT} \ge \max(C_{OUT} R, C_{OUT} H) = 1932\mu F \tag{53}$$

So 4 parallel 560 µF capacitors would normally be selected.

However, when  $C_{OUT\ H} > C_{OUT\ R}$  , the actual ripple may be much lower than the target.

Therefore, to avoid capacitor oversizing and ensure both factors are satisfied, the target  $\Delta V_{OUT}$  can be progressively decreased (through iteration) until  $C_{OUT}$   $_R = C_{OUT}$   $_H$ .

The result is:

$$\begin{cases} \Delta V_{OUT} = 12.9V \\ C_{OUT\_R} = C_{OUT\_H} = 1850\mu F \end{cases}$$

(54)

So 4 parallel 470 µF capacitors is sufficient.

AN5235 - Rev 2 page 24/54

# 6 Sensing design

Sensing circuits must be designed with appropriate voltage, power rating and tolerance selections, as well as bandwidth and slew rates when using OP-AMP circuits.

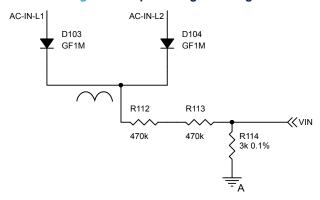

#### 6.1 Input voltage sensing

Following rectification, a voltage divider is used to sense the line input voltage.

Figure 21. Input voltage sensing

V<sub>IN</sub> is obtained from the equation:

$$V_{IN} = V_{RECT} \frac{R_{114}}{R_{112} + R_{113} + R_{114}} \tag{55}$$

The maximum peak of the sensed voltage must not exceed 1.25 V so, if we set R112 and R113 to 470 k $\Omega$ , R114 can be calculated as:

$$R_{114} \le \frac{V_{IN(\text{max})} \cdot \left(R_{112} + R_{113}\right)}{V_{RECT(\text{max})} - V_{IN(\text{max})}} = \frac{1.25 \cdot \left(470 + 470\right) \cdot 10^3}{1.04 \cdot 265 \cdot \sqrt{2} - 1.25} = 3.02k\Omega \tag{56}$$

Where:

•  $V_{RECT(MAX)} = 1.04 \cdot V_{RECT}$  is the maximum peak line voltage increased by a certain margin (4% in this design)

You should use R114 with 0.1% tolerance and insert a low-pass filter as close as possible to VIN PIN 31 (10  $k\Omega$ , 100 nF in this design).

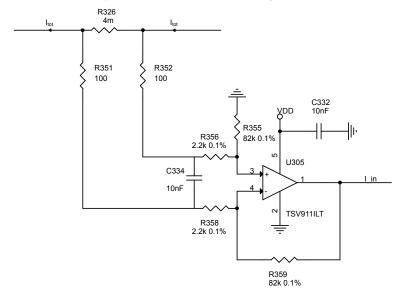

# 6.2 Input current sensing

Shunt resistor R144 converts the total input current into a voltage. A differential OP-AMP circuit (TSV911: single supply, rail-to-rail) is used to amplify the sensing signal.

AN5235 - Rev 2 page 25/54

Figure 22. Input current sensing circuit

For adequate sensing margins due to component tolerances, the maximum total inductor peak current is increased by a certain percentage (15% in our example).

The relationship  $\frac{R_{355}}{R_{356}} = \frac{R_{359}}{R_{358}}$  must be satisfied to reduce the Common Mode Rejection Ratio (CMRR), so 0.1% tolerance input and feedback resistors are recommended.

In this configuration, the output voltage is proportional to the difference between positive and negative input voltage:

$$V_{I\_in} = I_{tot} R_{326} \frac{R_{359}}{R_{358}} \tag{57}$$

The maximum value must not exceed 4.7 V. So, if R326 and R358 are set at 2.2 k $\Omega$ , R359 can be derived:

$$R_{359} \le \frac{V_{I\_in(\max)} \cdot R_{358}}{I_{tot(\max)} \cdot R_{326}} = \frac{4.7 \cdot 2200}{31 \cdot 0.004} = 83.4 \, k\Omega \tag{58}$$

Hence an 82 kΩ 0.1% resistor can be selected.

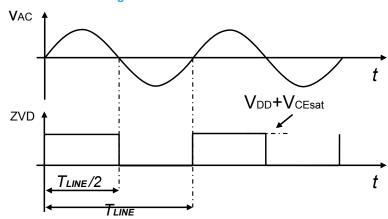

# 6.3 ZVD sensing

A zero voltage detection (ZVD) isolated circuit is used to synchronize PFC operation with the zero crossing of the input voltage.

VDD D102 R105 33k R107 ISO100 10M R106 TLP385 R108 R109 **(**ZVD 33k 33k R110 R111 10M 47k

Figure 23. ZVD circuit

Resistors R105, R108 and R109 limit the sensing current to a few milliamps, while R106 sets the voltage for correct conduction of the optocoupler diode.

AN5235 - Rev 2 page 26/54

During the positive half-cycle, diode D102 si directly polarized and the optocoupler is turned on, so capacitor C101 is charged and ZVD voltage is clamped to  $V_{DD}$ - $V_{CEsat}$ .

During the negative half-cycle, the optocoupler is open, so the capacitor is discharged (through R110) and the ZVD voltage equals GND.

Figure 24. ZVD circuit waveform

You should insert a low-pass filter as near as possible to ZVD PIN 17 (10 k $\Omega$  100 pF, in this design).

# 6.4 Output voltage sensing

A common voltage divider is used to sense the PFC output voltage.

R304 470k R308 470k R324 3.3k 0.1%

Figure 25. Output voltage sensing

The sensing voltage must not exceed 1.25 V and is calculated with the following equation:

$$V_{BUS} = V_{OUT} \frac{R_{324}}{R_{301} + R_{304} + R_{308} + R_{324}}$$

(59)

Starting again from R301=R304=R308= 470 kΩ, we can determine the lower resistor:

$$R_{324} \le V_{BUS(\text{max})} \cdot \frac{R_{301} + R_{304} + R_{308}}{V_{OUT(\text{max})} - V_{BUS(\text{max})}} = 1.25 \cdot \frac{\left(470 + 470 + 470\right) \cdot 10^3}{500 - 1.25} \cdot 3.53k\Omega \tag{60}$$

AN5235 - Rev 2 page 27/54

A 3.3 k $\Omega$  0.1% resistor is used and a low-pass filter should be placed as near as possible to VOUT PIN 34 (10 k $\Omega$  220 nF, in this design)

# 6.5 Output current sensing

Similar to input current sensing a shunt resistor (R9) and a differential OP-AMP circuit are used to sense the output current.

R325 10k 0.1%

Figure 26. Output current sensing circuit

The equation for the output is:

$$V_{O(Iload)} = I_{load}R_{300}\frac{R_{325}}{R_{309}}$$

(61)

The maximum output voltage must not exceed 1.25 V. The relationship  $\frac{R_{311}}{R_{310}} = \frac{R_{325}}{R_{309}}$  must be satisfied (0.1% tolerance resistors) and a sensing margin is applied (10%).

If R309=R310=2.2 k $\Omega$  and R300=30 m $\Omega$ :

$$R_{325} \le \frac{V_{I\_LOAD(\max)} \cdot R_{309}}{I_{LOAD(\max)} \cdot R_{300}} = \frac{1.25 \cdot 2200}{1.1 \cdot 7.5 \cdot 0.030} = 11.1k\Omega \tag{62}$$

So a 10 k $\Omega$  0.1% resistor is selected.

You should place a low-pass filter as near as possible to IOUT PIN 33 (10 kΩ 15 nF, in this design).

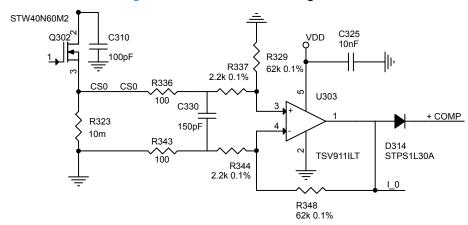

# 6.6 Switch current sensing

Three circuits similar to the output current sensing circuit are used to sense the switch current of each channel.

AN5235 - Rev 2 page 28/54

Figure 27. Switch current sensing circuit

The maximum output voltage is set at 4.7 V in order to maximize the sensing dynamic and the noise immunity. In this case, the maximum input current is the inductor saturation current (10% margin).

If R337=R344=2.2 k $\Omega$  and R323=10 m $\Omega$ :

$$R_{348} \le \frac{V_{I\_0(\text{max})} \cdot R_{344}}{I_{sw\_0(\text{max})} \cdot R_{323}} = \frac{4.7 \cdot 2200}{1.1 \cdot 14 \cdot 0.010} = 67.1k\Omega$$

(63)

So a 62 k $\Omega$  0.1% is selected.

The sensed current is used by the hardware fast overcurrent protection (OCP) and switch average current balance (CB) functions (signals coming from I\_0, I\_1 and I\_2 are filtered and sent to PIN 35, 36, 37 respectively).

## 6.7 Overcurrent protection circuit

The peak current of each switch needs to be limited to prevent inductor saturation, which could cause very high currents and damage the board.

OCP EN R331 R366 D319 11304 Q303 MMBT6429LT1G 11309 STPS1L30A EN1 EN2 PWM1 OUT1 GND Vcc PWM2 OUT2 R345 TS3011ILT R350<sup>-</sup> 10k R349 3.3k PM8834 C313 D315 R353 6.8k OCP1 BAT46JFILM R354 330k C331 100nF

Figure 28. Overcurrent protection circuit

The three switching currents (I\_0, I\_1, I\_2) are sent to an analog comparator (TS3011ILT) in OR configuration. For example, if the peak current is set at 14 A, the output of switch current sensing is:

$$V_{I\_0(ocp)} = I_{sw\_0(ocp)} \cdot R_{323} \frac{R_{348}}{R_{344}} = 14 \cdot 0.010 \cdot \frac{62000}{2200} = 3.95V$$

(64)

AN5235 - Rev 2 page 29/54

The output of the comparator becomes high when one of the three signals exceeds the threshold voltage of the inverting input:

$$V_{th\_ocp} = (V_{I\_0(ocp)} - V_{fdiode}) = (3.95 - 0.16) = 3.79V$$

(65)

For R349=3.3 k $\Omega$ , R350 can be calculated:

$$R_{350} \le V_{th\_ocp} \cdot \frac{R_{349}}{V_{DD} - V_{th\_ocp}} = 3.79 \cdot \frac{3300}{5 - 3.79} = 10.3k\Omega$$

(66)

A 10  $k\Omega$  resistor is selected.

Q303 is used as a fast switch off actuator (a few  $\mu$ s) for the input of all the drivers (PM8834). In case of consecutive OCP events, C333 is charged until the FAULT voltage level (1.23 V) is reached on OCP[1] PIN 28 of the STNRGPF01.

AN5235 - Rev 2 page 30/54

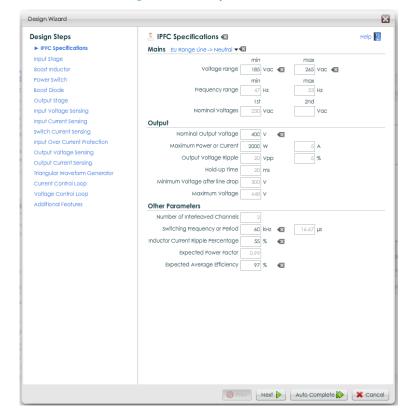

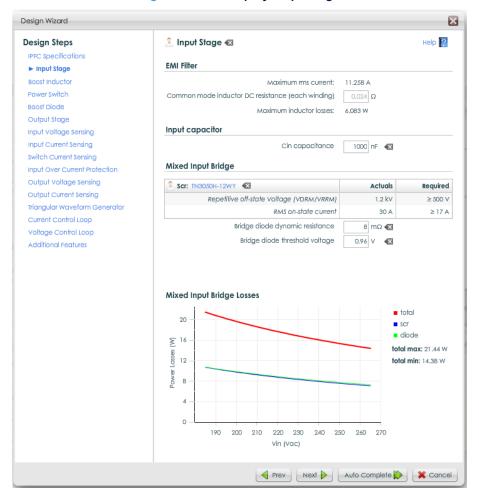

# 7 PFC controller customization with eDesign Suite

The eDesignSuite suite software tool developed by STMicroelectronics helps you configure ST products power conversion applications. You can use it to customize the PFC controller for a specific application: you start by entering the main specifications for your design and then generate an automatic design or follow a sequential process to build a highly customized design.

Figure 29. PFC specifications

AN5235 - Rev 2 page 31/54

Figure 30. PFC step-by-step design

#### - RELATED LINKS -

See RM0446 for details on how to use eDesignSuite to generate specialized firmware

AN5235 - Rev 2 page 32/54

# 8 Experimental results: steady-state, dynamic waveforms and typical PFC performance curves

# 8.1 Startup behavior

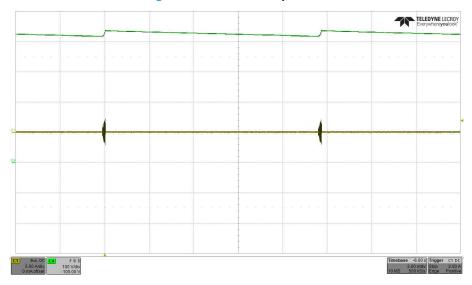

Following connection to the grid, the auxiliary power supply starts and the device is supplied. During the output capacitor pre-charging phase, the inrush current is limited by an input series resistor that is shorted by a relay at the end of this phase.

The board is designed to start in a no load condition, and if the grid parameters (voltage and frequency) are within the correct range, the board initiates a no-load startup with burst mode operation and output voltage regulated between 416 V and 436 V.

Once the startup phase has finished, a green LED indicates that the PFC is ready for a load connection.

Figure 31. No-load startup

AN5235 - Rev 2 page 33/54

#### 8.2 Inductor currents

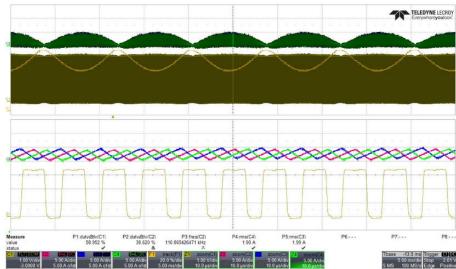

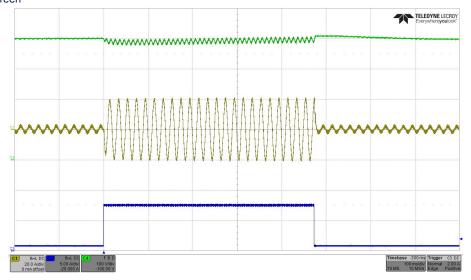

The following figure shows the inductor currents waveforms of the converter. The interleaving operation is evident and the channels currents are phase shifted 120 degrees. In this case, the master PWM signal (yellow) has a duty cycle of about 60%.

Figure 33. Inductor currents

# 8.3 Behavior during operation

An Agilent 6813B AC power source is used to supply the board at low line: 115  $V_{AC}$  with 1.5 kW load (the maximum power that the converter can manage is de-rated for 115  $V_{AC}$  for thermal reasons).

The line current in the figure below is a perfect sinusoidal wave and in phase with the line voltage, while the output voltage is regulated at 400 V.

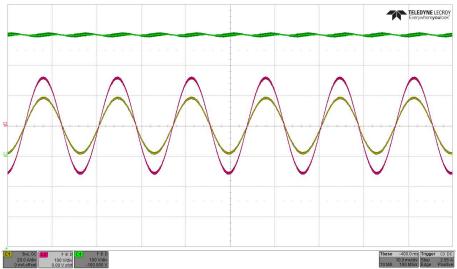

Figure 34. PFC input voltage and current at 1.5 kW and 115  $V_{AC}$

Output voltage: green line voltage: magenta line current: yellow

AN5235 - Rev 2 page 34/54

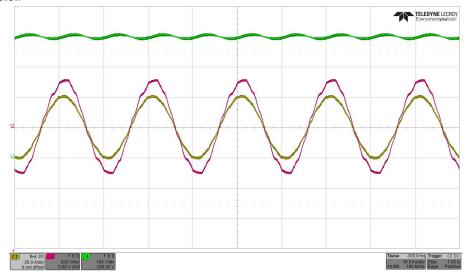

The high performance of the proposed control scheme is more evident at 230  $V_{AC}$  and nominal power. In this case, the board is directly supplied from the grid and, even if the line voltage is distorted, the line current adheres to the current reference properly.

Figure 35. PFC input voltage and current at 3 kW with 230 V<sub>AC</sub> input

Output voltage: green line voltage: magenta line current: yellow

During a load step sequence 10% - 100% - 10%, the PFC demonstrates a rapid dynamic response thanks to the load feed-forward. Also, the DC bus voltage is tightly regulated at the reference value.

Figure 36. 10% to 100% load transition at 230 V<sub>AC</sub>

load current: blue input current: yellow bus voltage: green

# 8.4 Steady state performance

A universal power analyzer (Voltech PM6000) is used to evaluate the steady state performance of the PFC.

AN5235 - Rev 2 page 35/54

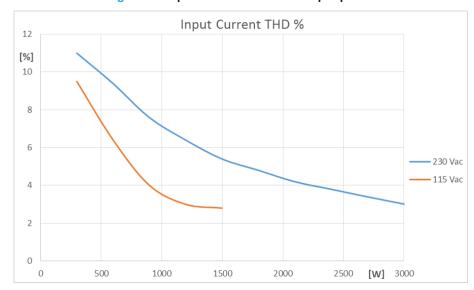

#### 8.4.1 THD

The input current THD is below 10% for a load higher than 20%. It decreases down to 3% at 230  $V_{AC}$  (full load) and below 3% at 115  $V_{AC}$  (1.5 kW).

Figure 37. Input current THD% vs output power

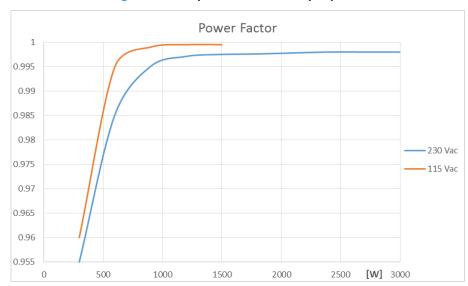

#### 8.4.2 Power factor

An almost unity power factor is achieved, with values higher than 0.99 for loads above 20% of rated power.

Figure 38. PFC power factor vs output power

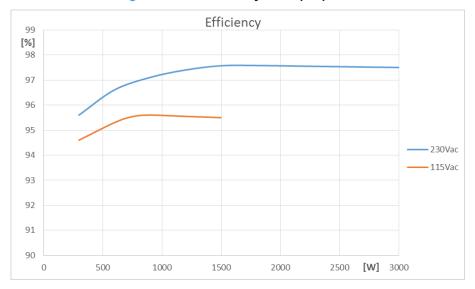

# 8.4.3 Efficiency

The phase shedding control strategy produces a flat curve (97.5% at 230 V<sub>AC</sub>) in the measured efficiency results.

AN5235 - Rev 2 page 36/54

Figure 39. PFC efficiency vs output power

AN5235 - Rev 2 page 37/54

#### 9 Conclusions

We presented a 3 kW, 3-channel interleaved PFC for industrial applications in this document. The interleaving technique used on the STEVAL-IPFC01V1 yielded very good power density (52 W/inch3) and mixed signal control provided optimal PFC performance.

In particular, the analog current loop allowed us to achieve a high power factor (PF>0.99) and very low THD (3%) for the rated power, while digital voltage loop helped to maintain excellent output voltage regulation (I/O feed-forwards) and flat efficiency curve, just below 98% from 50% to 100% load (phase shedding).

Once bandwidth and phase margins are specified, the design procedure discussed in this document lets you calculate the key control parameters and ensure system stability through the small-signal transfer functions.

The proposed control scheme is implemented on the STNRGPF01 controller, which is able to drive the application and respond appropriately to input and output conditions.

You can also customize the controller and the entire application with the eDesignSuite software tool, which can take the complexity out of the design work and eliminate firmware development efforts altogether.

AN5235 - Rev 2 page 38/54

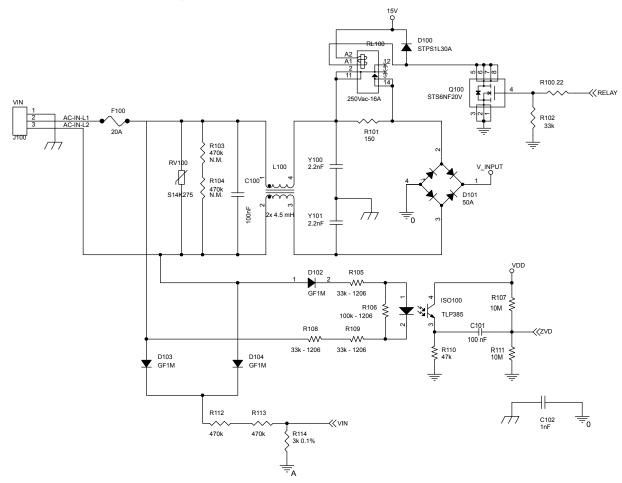

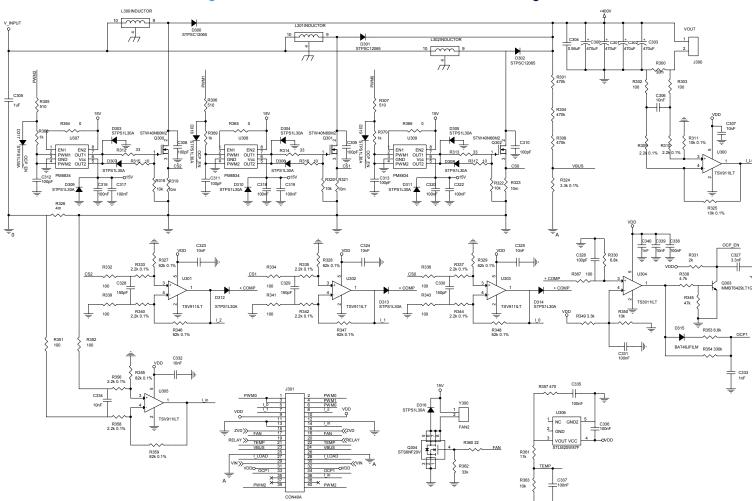

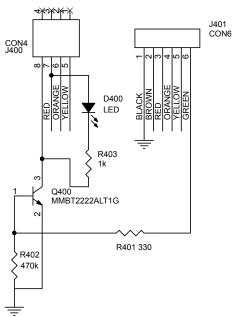

Figure 40. STEVAL-IPFC01P1 schematic - input section

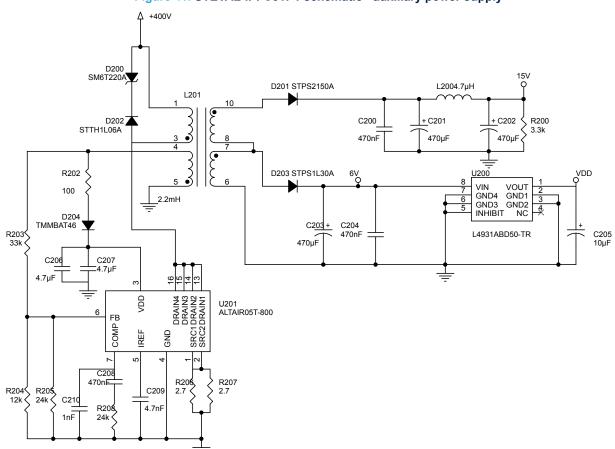

Figure 41. STEVAL-IPFC01P1 schematic - auxiliary power supply

11

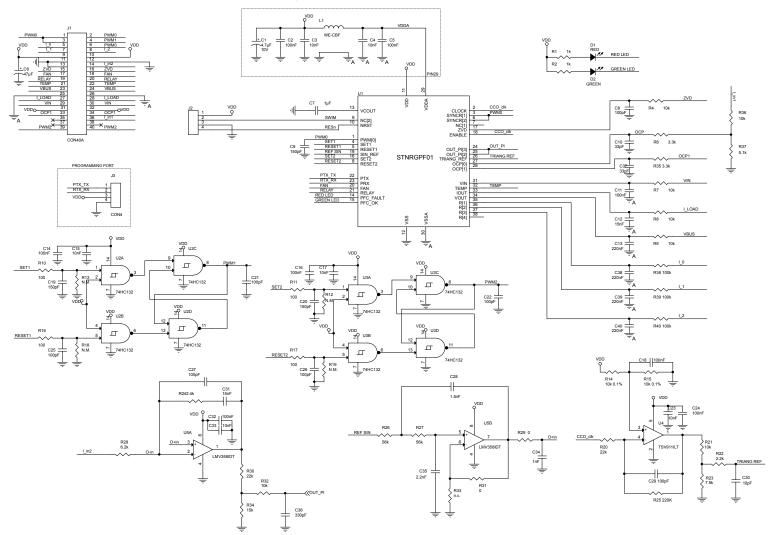

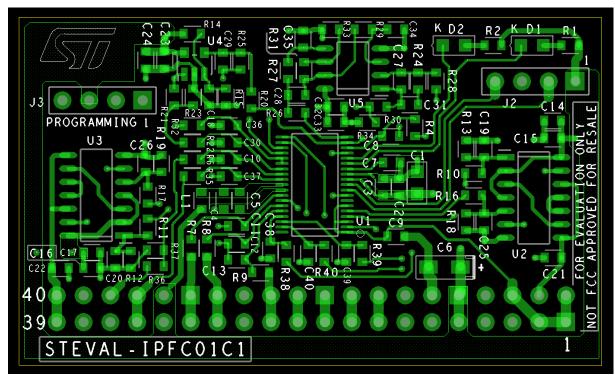

Figure 43. STEVAL-IPFC01C1 schematic

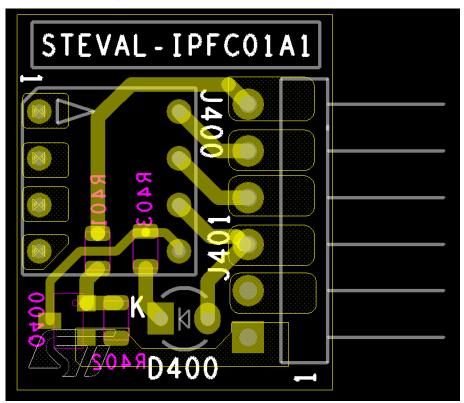

Figure 44. STEVAL-IPFC01A1 schematic

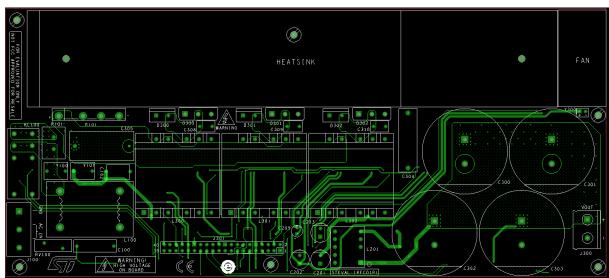

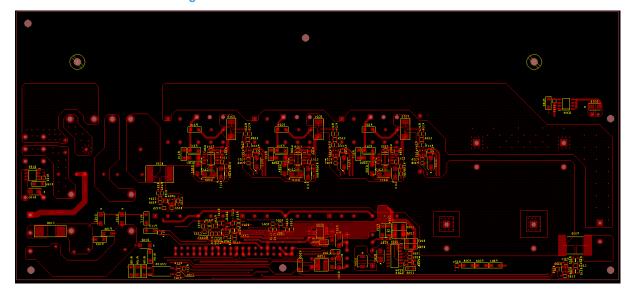

## 13 STEVAL-IPFC01P1 power board layout

Figure 45. STEVAL-IPFC01P1 silkscreen - top

AN5235 - Rev 2 page 44/54

## 14 STEVAL-IPFC01C1 control board layout

Figure 47. STEVAL-IPFC01C1 silkscreen - top

AN5235 - Rev 2 page 45/54

## 15 STEVAL-IPFC01A1 adapter board layout

Figure 48. STEVAL-IPFC01A1 silkscreen - top

AN5235 - Rev 2 page 46/54

## 16 STNRGPF01 pinout

PWM0 R[4] 38 CLOCK R[3] 2 37 SYNCR[1] R[2] 3 36 SET1 R[1] 4 35 RESET1 VOUT 5 34 SYNCR[2] IOUT 6 33 NC **TEMP** 7 32 RESET2 VIN 8 31 NC VSSA 9 30 STNRGPF01 NRST 10 **VDDA** 29 VDD 11 OCP1 28 VSS OCP 12 27 VOUT TRIANG\_REF 13 26 PFC\_FAULT 14 OUT\_PI[2] 25 PFC\_OK OUT\_PI[3] 15 24 SET2 RTX 16 23 ZVD PTX 17 22 **ENABLE** RELAY 18 21 SIN REF FAN 19 20

Figure 49. STNRGPF01 pinout

AN5235 - Rev 2 page 47/54

#### 17 References

- STMicroelectronics, Application Note, AN628, "Designing a high power factor switching pre-regulator with the L4981 continuous mode

- STMicroelectronics, Data Sheet, DS10246, "STNRGPF01 three-channel interleaved CCM PFC digital controller"

- 3. STMicroelectronics, Application Note, AN4149, "Designing a CCM PFC pre-regulator based on the L4984D"

- 4. STMicroelectronics, Reference Manual, RM0446, "STNRGPF01 digital controller for interleaved PFC"

- 5. STMicroelectronics, Online Software Tool, E-Design: www.st.com/content/st\_com/en/support/resources/edesign.html

AN5235 - Rev 2 page 48/54

## **Revision history**

Table 3. Document revision history

| Date        | Version | Changes                                                               |

|-------------|---------|-----------------------------------------------------------------------|

| 04-Dec-2018 | 1       | Initial release.                                                      |

| 09-Sep-2019 | 2       | Throughout document: minor text edits                                 |

| 09-3ер-2019 |         | Updated Figure 41. STEVAL-IPFC01P1 schematic - auxiliary power supply |

AN5235 - Rev 2 page 49/54

## **Contents**

| 1 | Safe | ety instructions                                  | 2  |  |  |  |

|---|------|---------------------------------------------------|----|--|--|--|

| 2 | Fun  | nctional overview                                 |    |  |  |  |

| 3 | Pow  | ver factor correction                             | 4  |  |  |  |

|   | 3.1  | Power factor (PF) - definition                    | 4  |  |  |  |

|   | 3.2  | Active PFC                                        | 4  |  |  |  |

|   |      | 3.2.1 Interleaving                                | 6  |  |  |  |

|   | 3.3  | Mixed signal approach                             | 8  |  |  |  |

| 4 | PFC  | control                                           | 10 |  |  |  |

|   | 4.1  | Converter modeling                                | 11 |  |  |  |

|   | 4.2  | Current loop design                               | 11 |  |  |  |

|   | 4.3  | Voltage loop design                               | 14 |  |  |  |

|   | 4.4  | I/O feed-forward and current reference generation | 16 |  |  |  |

|   | 4.5  | Control design example                            | 17 |  |  |  |

| 5 | Pow  | ver stage design equations                        | 21 |  |  |  |

|   | 5.1  | Bridge rectifier                                  | 21 |  |  |  |

|   | 5.2  | Input capacitor                                   | 21 |  |  |  |

|   | 5.3  | Boost inductor                                    | 21 |  |  |  |

|   | 5.4  | Power switch                                      | 22 |  |  |  |

|   |      | 5.4.1 MOSFET                                      | 22 |  |  |  |

|   | 5.5  | Boost diode                                       | 23 |  |  |  |

|   | 5.6  | Output capacitor                                  | 24 |  |  |  |

| 6 | Sen  | sing design                                       | 25 |  |  |  |

|   | 6.1  | Input voltage sensing                             | 25 |  |  |  |

|   | 6.2  | Input current sensing                             | 25 |  |  |  |

|   | 6.3  | ZVD sensing                                       | 26 |  |  |  |

|   | 6.4  | Output voltage sensing                            | 27 |  |  |  |

|   | 6.5  | Output current sensing                            | 28 |  |  |  |

|   | 6.6  | Switch current sensing                            | 28 |  |  |  |

|   | 6.7  | Overcurrent protection circuit                    | 29 |  |  |  |

|   |      |                                                   |    |  |  |  |

| 7                | PFC | controll                 | er customiz     | ation with eDes  | sign Suite… |  |  |     | 31                   |

|------------------|-----|--------------------------|-----------------|------------------|-------------|--|--|-----|----------------------|

| 8                |     |                          |                 | steady-state,    | •           |  |  | • • |                      |

|                  | 8.1 | Startup                  | behavior        |                  |             |  |  |     | 33                   |

|                  | 8.2 | Inducto                  | r currents      |                  |             |  |  |     | 33                   |

|                  | 8.3 | Behavio                  | or during opera | ation            |             |  |  |     | 34                   |

|                  | 8.4 | Steady state performance |                 |                  |             |  |  |     | 35                   |

|                  |     | 8.4.1                    | THD             |                  |             |  |  |     | 35                   |

|                  |     | 8.4.2                    | Power factor .  |                  |             |  |  |     | 36                   |

|                  |     | 8.4.3                    | Efficiency      |                  |             |  |  |     | 36                   |

| 9                | Con | clusions                 | ·               |                  |             |  |  |     | 38                   |

| 10               | STE | VAL-IPF                  | C01P1 powe      | er board schema  | atics       |  |  |     | 39                   |

| 11               | STE | VAL-IPF                  | C01C1 contr     | ol board schen   | natic       |  |  |     | 42                   |

| 12               | STE | VAL-IPF                  | C01A1 adap      | ter board scher  | natic       |  |  |     | 43                   |

| 13               | STE | VAL-IPF                  | C01P1 powe      | er board layout. |             |  |  |     | 44                   |

| 14               | STE | VAL-IPF                  | C01C1 contr     | ol board layout  | :           |  |  |     | 45                   |

| 15               | STE | VAL-IPF                  | C01A1 adap      | ter board layou  | t           |  |  |     | 46                   |

| 16               |     |                          |                 |                  |             |  |  |     |                      |

| . <b>.</b><br>17 |     |                          | •               |                  |             |  |  |     |                      |

|                  |     | history                  |                 |                  |             |  |  |     | <del>4</del> 0<br>49 |

|                  |     |                          |                 |                  |             |  |  |     |                      |

# **List of figures**

| Figure 1.                | STEVAL-IPFC01V1 reference design                                         |      |

|--------------------------|--------------------------------------------------------------------------|------|

| Figure 2.                | STEVAL-IPFC01V1 block diagram                                            |      |

| Figure 3.                | PFC boost circuit and ideal waveforms                                    | . 5  |

| Figure 4.                | Interleaved boost circuit N-channel                                      | . 6  |

| Figure 5.                | Channel inductor currents vs total current for 3-channel PFC             | . 7  |

| Figure 6.                | Inductor volume comparison for 3 kW PFC                                  | . 7  |

| Figure 7.                | Output capacitor current ripple vs duty cycle                            | . 8  |

| Figure 8.                | Mixed signal block diagram                                               | . 9  |

| Figure 9.                | STNRGPF01 mixed signal block scheme                                      | 10   |

| Figure 10.               | Current loop block diagram                                               | . 11 |

| Figure 11.               | Control-to-input current TF vs main voltage V <sub>IN</sub> (rms)        | 12   |

| Figure 12.               | Control-to-input current TF vs Number of active channels N <sub>ch</sub> | 13   |

| Figure 13.               | PI Type II OP-AMP compensator                                            | . 14 |

| Figure 14.               | Complete control loop block diagram                                      |      |

| Figure 15.               | I/O FFD block                                                            |      |

| Figure 16.               | Current compensator C <sub>i</sub> (s) Bode diagram                      |      |

| Figure 17.               | Current open loop transfer function T <sub>i</sub> (s) Bode diagram      |      |

| Figure 18.               | Voltage compensator $C_v(s)$ Bode diagram                                |      |

| Figure 19.               | Voltage open loop transfer function $T_v(s)$ Bode diagram                |      |

| Figure 20.               | Average inductor current                                                 |      |

|                          | Input voltage sensing                                                    |      |

| Figure 21.               | Input current sensing circuit                                            |      |

| Figure 22.<br>Figure 23. | ZVD circuit                                                              |      |

| Figure 23.<br>Figure 24. | ZVD circuit waveform                                                     |      |

| Figure 25.               | Output voltage sensing                                                   |      |

| Figure 26.               | Output current sensing circuit.                                          |      |

| Figure 27.               | Switch current sensing circuit                                           |      |

| Figure 28.               | Overcurrent protection circuit                                           |      |

| Figure 29.               | PFC specifications                                                       |      |

| Figure 30.               | PFC step-by-step design                                                  |      |

| Figure 31.               | No-load startup.                                                         |      |

| Figure 32.               | Burst Mode operation                                                     |      |

| Figure 33.               | Inductor currents.                                                       |      |

| Figure 34.               | PFC input voltage and current at 1.5 kW and 115 V <sub>AC</sub>          |      |

| Figure 35.               | PFC input voltage and current at 3 kW with 230 V <sub>AC</sub> input     |      |

| Figure 36.               | 10% to 100% load transition at 230 V <sub>AC</sub>                       |      |

| Figure 37.               | Input current THD% vs output power                                       |      |

| Figure 38.               | PFC power factor vs output power.                                        |      |

| Figure 39.               | PFC efficiency vs output power.                                          |      |

| Figure 40.               | STEVAL-IPFC01P1 schematic - input section                                |      |

| Figure 41.               | STEVAL-IPFC01P1 schematic - auxiliary power supply                       |      |

| Figure 42.               | STEVAL-IPFC01P1 schematic - boost interleaving section                   |      |

| Figure 43.               | STEVAL-IPFC01C1 schematic                                                |      |

| Figure 44.               | STEVAL-IPFC01A1 schematic                                                |      |

| Figure 45.               | STEVAL-IPFC01P1 silkscreen - top.                                        |      |

| Figure 46.               | STEVAL-IPFC01P1 silkscreen - bottom                                      |      |

| Figure 47.               | STEVAL-IPFC01C1 silkscreen - top                                         |      |

| Figure 48.               | STEVAL-IPFC01A1 silkscreen - top.                                        |      |

|                          | STNRGPF01 pinout                                                         | 47   |

|                          |                                                                          |      |

## **List of tables**

| Table 1. | Boost operation modes                            | 5 |

|----------|--------------------------------------------------|---|

| Table 2. | Power stage, sensing and current loop parameters | 7 |

| Table 3. | Document revision history                        | 9 |

AN5235 - Rev 2 page 53/54

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2019 STMicroelectronics - All rights reserved

AN5235 - Rev 2 page 54/54