# STM32MP151/153/157 MPU lines and STPMIC1 integration on a battery powered application

## Introduction

This application note applies to the STM32MP151/153/157 MPU line devices and are now referred to as STM32MP15x. The STPMIC1 device used for this application is the STPMIC1BPQR.

This application note provides a sample hardware reference design based on STM32MP15x and STPMIC1BPQR power management IC, powered from a single cell Li-Ion / Li-Po battery.

This document is intended for product architects and designers who require information on hardware integration and settings, focusing on:

- · Reference design block diagram

- · Power distribution

- · Start up, shutdown and low-power management

- · Battery management (USB charging and monitoring overview)

- USB high speed port management.

## 1 General information

This document applies to the STM32MP15x lines dual-core  $\text{Arm}^{\text{\scriptsize @}}\text{-}\text{based Series microprocessor.}$

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

AN5260 - Rev 2 page 2/54

## 2 Overview

This application note covers the STM32MP15x together with the STPMIC1BPQR with DDR and Flash memory and together with the following peripherals:

- DC input power source from 1-Cell Li-lon / Li-Po: 3.6 V nominal (2.8 V to 4.3 V).

- Peripheral I/O interface voltage at 1.8 V supplied by the STPMIC1BPQR.

- IpDDR2 or IpDDR3 with 32-bit wide bus.

- eMMC Flash memory powered from a 2.9 V power source and 1.8 V I/O interface.

- USB high-speed port supporting power sink mode (for battery charging capability) and source mode (to supply a USB device).

- Battery charging and battery monitoring is introduced for illustration.

Not covered by this application note:

- DDR3 and DDR3L: these memory devices are not appropriate for use with battery powered products due to their high power consumption.

- Peripheral interface with an I/O voltage of 3.3 V: the assumption is that the 1-cell Li-lon / Li-PO battery has still enough energy when battery voltage drops below 3.3 V. If an I/O peripheral such as the STPMIC1A is used, it no longer operates under these circumstances.

## 2.1 Reference documents

Table 1. Reference documents

| Document number              | Title                                                                                                                                                               |  |  |  |  |  |  |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| STMicroelectronics documents |                                                                                                                                                                     |  |  |  |  |  |  |  |

| [1]                          | Getting started with STM32MP1 Series hardware development (AN5031)                                                                                                  |  |  |  |  |  |  |  |

| [2]                          | Highly integrated power management IC for micro processor units (DS12792)                                                                                           |  |  |  |  |  |  |  |

| [3]                          | STM32MP1 Series using low-power modes (AN5109)                                                                                                                      |  |  |  |  |  |  |  |

| [4]                          | STM32MP151/153/157 Lines and STPMIC1A hardware and software integration (AN5089)                                                                                    |  |  |  |  |  |  |  |

| [5]                          | STM32MP157 advanced Arm <sup>®</sup> -based 32-bit MPUs (RM0436)                                                                                                    |  |  |  |  |  |  |  |

| [6]                          | Arm <sup>®</sup> dual Cortex <sup>®</sup> -A7 800 MHz + Cortex <sup>®</sup> -M4 MPU, 3D GPU, TFT/DSI, 37 comm. interfaces, 29 timers, adv. analog, crypto (DS12505) |  |  |  |  |  |  |  |

| [7]                          | Standalone USB Type-C™ controller with high voltage protections (DS11503)                                                                                           |  |  |  |  |  |  |  |

| [8]                          | STM32MP1 Series lifetime estimates (AN5438)                                                                                                                         |  |  |  |  |  |  |  |

| USB specification            |                                                                                                                                                                     |  |  |  |  |  |  |  |

| [9]                          | USB Type-C cable and connector specification release 1.4 or later available from USB implementation forum web site                                                  |  |  |  |  |  |  |  |

Note: For STMicroelectronics documents refer to www.st.com.

AN5260 - Rev 2 page 3/54

## 3 Glossary

Table 2. Glossary

| Term | Definition                                                                             |

|------|----------------------------------------------------------------------------------------|

| DR   | Dual-role. In this document, a peripheral supporting USB host mode or USB device mode. |

| FSBL | First stage boot loader                                                                |

| HSI  | High speed internal oscillator                                                         |

| IC   | Integrated circuit                                                                     |

| LDO  | Low drop out linear regulator                                                          |

| MPU  | Microprocessor unit                                                                    |

| PMIC | Power management integrated circuit                                                    |

| RTC  | Real-time clock                                                                        |

| SMPS | Switching mode power supply                                                            |

| SW   | Software                                                                               |

| TAMP | Tamper detection circuit                                                               |

AN5260 - Rev 2 page 4/54

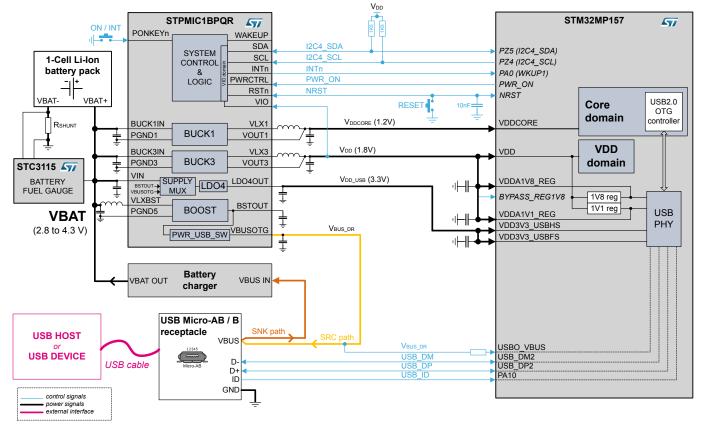

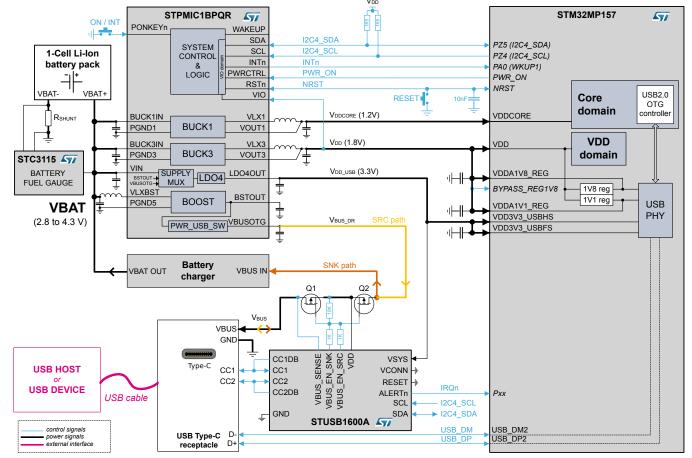

## 4 Battery application reference design

This reference design targets an application powered from a rechargeable battery with low power lpDDR2 or lpDDR3, an eMMC, an SD-card, a USB HS dual role data port (also known as OTG).

The USB HS dual role data port is also used as a power source to charge the battery. A battery fuel gauge monitors the battery energy level. Other peripherals like audio, display, Wi-Fi $^{\text{@}}$  / Bluetooth $^{\text{@}}$  sensors are added to illustrate the application.

The main peripheral interfaces work with an I/O voltage of 1.8 V. The overall system is illustrated in Figure 1.

AN5260 - Rev 2 page 5/54

STM32MP157 STPMIC1BPQR 47/ 477 ON / INT 1 WAKEUP WAKEUP PC13 (RTC\_OUT1) SDA I2C4 SDA PZ5 (I2C4\_SDA) SYSTEM I2C4 SCL 1-Cell Li-lon SCL CONTROL PZ4 (I2C4 SCL) INTn INTn battery pack PA0 (WKUP1) PWRCTRL LOGIC PWR ON RSTr NRST NRST VBAT-VBAT+ VIO RESET Core domain VDDCORE (1.2V) **VDDCORE** BUCK1IN VLX1 BUCK1 PGND1 VOUT1 PDR\_ON\_CORE VSW Vpp (1.8V) **BUCK3IN** VLX3 VDDA Analog PGND3 BUCK3 VOUT3 domain VREF+ STC3115 47/ domain VREF-BATTERY (ADC/DAC) INTLDO VSSA FUEL GAUGE INTLDO VBAT BSTOUT - SUPPLY - LDO4 VDD\_USB (3.3V) LDO4OUT ports **VDD** *PDR\_ON* VDD\_ANA Ī domain õ V<sub>DD2\_DDR</sub> (1.2V) BUCK2IN VLX2 VDD\_PLL **VBAT** BUCK2 PGND2 VOUT2 VDD (2.8 to 4.3 V) V<sub>REF\_DDR</sub> (0.6V) VDD\_DSI DDR\_REF VREFDDR 1V2 reg VDD1V2\_DSI\_REG Ţ DSI  $V_{DD1\_DDR}$  (1.8V) VDD1V2\_DSI\_PHY LD03IN LDO3OUT LDO3 V<sub>DD</sub> (1.8V) • VDDA1V8 DSI Ţ **BUCK4IN** VDDA1V8 REG V<sub>DD</sub> FREE (3.3V) BUCK4 VOUT4 PGND4 BYPASS\_REG1V8 1V8 reg 1V1 reg VDDA1V1\_REG USB DO16IN LDO10UT LDO1 VDD AUDIO (1.8V) VDD3V3\_USBHS Ţ VDD3V3\_USBFS LDO6OUT LDO6 V<sub>DD LCD</sub> (2.8V) Ŧ VDDQ DDR DDR DDR VREF LDO25IN LDO2OUT LDO2 VDD\_eMMC (2.9V) Ŧ LDO5OUT LDO5 V<sub>DD</sub> <sub>SD</sub> (2.9V) IpDDR2 / IpDDR3 memory **VLXBST BSTOUT** VDD2 / VDDQ / VDDQ **BOOST** PGND5 VREFQ / VREFCA  $V_{DD1}$ VBUSOTG PWR\_USB\_SW Ţ SWIN **SWOUT** PWR SW V<sub>DD</sub> (1.8V) -→ V<sub>CCQ</sub> eMMC **→** Vcc VDD\_EMMC (2.9V) (BOOT peripheral) VDD\_SD (2.9V) VSUPPLY Batterv VDD VBAT OUT VBUS IN SD-Card V<sub>DD</sub> (1.8V) V<sub>CCA</sub> Level Translator SD-Card charger USB Micro-AB / B Audio peripherals (CODEC, digital mic.)  $V_{DD\_AUDIO}$  (1.8V) = receptacle VBUS OTG\_VBUS To STM32MP157 DM2 Display D+ DP2 USB HS port VDD LCD (2.8V) • (LCD, touch-screen...) ID PA10 GND Other peripherals control signals (WiFi/BT, Sensors ...) VDD\_FREE -->

Figure 1. STM32MP15x and STPMIC1BPQR with IpDDR2/3, eMMC, SD-card and USB DR

Note: The following are not shown in the diagram:

- STM32MP15x decoupling scheme (see [1] related chapter),

- STPMIC1BPQR discrete components value (see [2]),

- Additional protection, such as ESD, EMI filtering, overvoltage.

AN5260 - Rev 2 page 6/54

## 4.1 Battery as main power source

This application is powered by a single cell rechargeable 3.6 V nominal voltage Li-Ion or Li-PO battery pack (VBAT) with a range of 2.8 V to 4.3 V. The battery capacity of the reference design in Figure 1 depends on the application use cases and the peripheral power consumptions. For instance, assuming a 500 mAh – 1000 mAh battery pack is used.

#### Warning:

In this document, the STM32MP15x VBAT pin (used for RTC/TAMP supply) must not be confused with the battery voltage domain VBAT that supplies the application.

The battery pack is used as main power source (VBAT) to supply the STPMIC1BPQR. The STPMIC1BPQR has all the required power converters to supply the complete application.

The battery voltage (VBAT) is monitored by two STPMIC1BPQR thresholds:

- VINOK\_rise: To prevent the STPMIC1BPQR from starting when the battery voltage (VBAT) is too low. STPMIC1BPQR VINOK rise threshold = 3.3V nominal.

- VINOK\_fall: To force the STPMIC1BPQR to power down to prevent battery fully discharging (dead battery).

STPMIC1BPQR VINOK\_fall threshold = 2.8V nominal.

VINOK\_fall threshold = 2.8V nominal.

VINOK\_rise and VINOK\_fall thresholds can be adjusted by re-programming the STPMIC1BPQR NVM via I<sup>2</sup>C.

The STC3115 fuel gauge monitors the battery voltage and acts as current sensor to accurately estimate the remaining battery charge level. Additionally, the STC3115 also monitors the battery temperature if the battery pack is located close to the STC3115.

The battery charge process is managed by a discrete battery charger IC. Charge energy is provided by the USB connector (Type Micro-AB or Micro-B). The charger IC converts the USB voltage (VBUS) to battery voltage (VBAT).

## 4.2 Power distribution

The STPMIC1BPQR integrates the regulators required to supply all the STM32MP15x in addition to a set of regulators to supply the application peripherals.

## **4.2.1** VDD power domain (1.8 V)

VDD is the reference design main I/O voltage domain used by the STM32MP15x, STPMIC1BPQR and peripherals.

It is powered from the STPMIC1BPQR BUCK 3 step-down SMPS which has high efficiency and low quiescent current across all load conditions.

The VDD voltage domain is the first voltage available during power up sequence (STPMIC1BPQR Rank 1) and the last disabled during power down sequence.

VDD is enabled in Run, LP-stop, LPLV-stop and Standby modes. VDD is disabled in Off mode.

STPMIC1BPQR has dedicated NVM settings to set BUCK 3 (I/Os) at 1.8 V during the STPMIC1BPQR power up to fit with battery reference design in Figure 1. See [2] for details.

## STM32MP15x VDD power supply:

Connect VDD\_PLL, VDD\_ANA, VDD\_DSI and VDDA1V8\_DSI to VDD in addition to supplying the STM32MP1 Series microprocessor VDD I/O voltage domain.

ADC/DAC analogue voltage (VDDA) and related analogue reference voltage (VREF+) may be powered from VDD depending on expected ADC performances. If high ADC performances are expected or to ensure the DAC functions correctly, power VDDA (and VREF+) from a low noise power source with a voltage greater than 1.8 V. In that case, a STPMIC1BPQR LDO may be dedicated to supply the STM32MP15x VDDA voltage domain.

## 4.2.2 VDDCORE power domain (1.2 V / 1.35 V)

VDDCORE is the main STM32MP15x digital power domain.

AN5260 - Rev 2 page 7/54

It is powered from the STPMIC1BPQR BUCK1 step-down SMPS. This voltage domain is the next power domain to be available during power up sequence (STPMIC1BPQR Rank 2) and the penultimate to be disabled during power down sequence.

VDDCORE is enabled in Run, LP-stop and LPLV-stop modes. VDDCORE is reduced in LPLV-stop to save power. VDDCORE is disabled in Standby and in Off mode.

STPMIC1BPQR has NVM settings to configure BUCK1 (VDDCORE) to 1.2 V when STPMIC1BPQR is in power up. The STM32MP15xD and STM32MP15xF devices have an enhanced consumer mission profile (see [8]). This profile allows the Arm<sup>®</sup> dual Cortex<sup>®</sup>-A7 CPUs to the clock frequency run up to 800MHz (see [6] for details and limitations).

Accordingly, the VDDCORE supply voltage must be increased to 1.35 V when the CPU frequency (Fmpuss\_ck) operates up to 800 MHz. When it does not operate in Run mode (800 MHz), the VDDCORE supply voltage must be set back to its nominal voltage (1.2 V typ).

## 4.2.3 VDD\_USB power domain (3.3 V)

VDD\_USB is dedicated to supplying power to the STM32MP15x USB PHYs (VDD3V3\_USBHS and VDD3V3\_USBFS).

It is powered from the STPMIC1BPQR LDO4 linear regulator, which has been specifically designed for this feature.

LDO4 has a 3 power input source multiplexor which selects automatically the highest input voltage. It is designed specially to keep the STM32MP15x USB PHY working in following uses cases:

USB embedded host with low battery voltage (VBAT ≤ 3.3 V ): A USB peripheral (eg: mass storage device) is connected to the application and is powered by VBUS\_DR (5.2 V) from STPMIC1BPQR boost converter via PWR\_USB\_SW (see Figure 1). In this case, LDO4 cannot generate VDD\_USB at 3.3 V from battery as VBAT is below 3.3 V. The LDO4 input source multiplexor automatically sets BSTOUT (BOOST converter providing a 5.2 V voltage) as LDO4 input source to generate VDD\_USB at 3.3 V.

Note: Ignoring LDO4 dropout voltage for illustration.

USB peripheral (device) with low battery voltage (VBAT <= 3.3 V): A USB host such as a standard downstream port from a PC is connected to the application and it provides VBUS (5 V) to VBUS\_DR (see Figure 1). The LDO4 cannot generate VDD\_USB at 3.3 V from battery as VBAT is below 3.3 V. The LDO4 input source multiplexor automatically sets VBUSOTG (from VBUS\_DR) as LDO4 input source (5 V) to generate VDD\_USB at 3.3 V.</li>

STPMIC1BPQR LDO4 mux input sources are VBAT via VIN pin, BOOST converter via BSTOUT pin, and VBUS DR via VBUSOTG pin.

This voltage domain is the last domain available during power up sequence (STPMIC1BPQR Rank 3) and the first disabled during power down sequence (except regulators enabled by software that are disabled before LDO4 in Rank 0. See [2] for details).

VDD\_USB is enabled in Run, LP-stop and LPLV-stop modes if a USB peripheral is connected to the application. It can be disabled if no USB peripheral is connected. VDD\_USB is disabled in Standby and in Off mode.

STPMIC1BPQR has NVM settings to set LDO4 (VDD\_USB) to 3.3 V when STPMIC1BPQR powers up. LDO4 (VDD\_USB) is needed at power up to supply the USB PHY for the USB flashing use case (STM32MP15x peripheral boot from ROM).

To save power at power up, re-programme the STPMIC1BPQR NVM to automatically enable LDO4 only when VBUS is present on VBUS\_DR at power-up.

## 4.2.4 VDD1\_DDR (1.8 V), VDD2\_DDR (1.2 V), VREF\_DDR (0.6 V) power domains

- VDD1\_DDR is dedicated for lpDDR2 or lpDDR3 core power supply 1 (VDD1) at 1.8 V.

- VDD2\_DDR is dedicated for IpDDR2 or IpDDR3 core power supply 2 (VDD2 / VDDQ / VDDCA) and for STM32MP15x DDR I/Os supply (VDDQ\_DDR) at 1.2 V.

- VREF\_DDR is dedicated for lpDDR2 or lpDDR3 reference voltage (VREFQ / VREFCA) and for STM32MP15x DDR reference voltage (DDR VREF) at VDD2 DDR / 2 (0.6 V).

- VDD1\_DDR (1.8 V) is powered from the STPMIC1BPQR LDO3. To optimize power efficiency, LDO3 is

powered from VDD (LDO3IN = VDD = 1.8 V). LDO3 has been designed to support Bypass mode (like a

power switch) with low RDSon to fit lpDDR2 / lpDDR3 VDD1 voltage tolerance. This takes into account both

BUCK3 (VDD) voltage tolerance and LDO3 RDSon tolerance to fit lpDDR's VDD1.

AN5260 - Rev 2 page 8/54

- VDD2\_DDR (1.2 V) is powered from the STPMIC1BPQR BUCK2 step down SMPS with high efficiency and low quiescent current across all load conditions. BUCK2 is powered from battery voltage (VBAT).

- VREF\_DDR (0.6 V) is powered from the STPMIC1BPQR REFDDR sink/source LDO. When enabled REFDDR output voltage is equal to VDD2\_DDR / 2 (BUCK2 output voltage / 2).

The STPMIC1BPQR does not start VDD1\_DDR, VDD2\_DDR and VREF\_DDR at power up. They must be powered up and powered down by STM32MP15x software, respectively at STM32MP15x boot up and shutdown.

#### Software IpDDR2 / IpDDR3 power up sequence:

After power up, when the STM32MP15x is booting up, its software must enable VDD1\_DDR, VDD2\_DDR and VREF\_DDR voltage domains in the following order to comply with IpDDR2 / IpDDR3 power sequence (see JESD209-2B chapter 3.4 or latest JEDEC revision):

- 1. Enable LDO3 in Bypass mode: VDD1 DDR rises to 1.8 V (= VDD voltage) in ~100 µs.

- 2. After 100 µs, enable REFDDR LDO: VREF\_DDR voltage is kept at 0 V as BUCK2 is disabled.

- 3. Set BUCK2 to 1.2 V and enable BUCK2.

The constraint is that step 1 to step 3 must be performed in less than 20 ms to comply IpDDR2 / IpDDR3 JEDEC constraints.

#### Software IpDDR2 / IpDDR3 power down sequence:

Before the STM32MP15x software goes in Off mode or in Standby mode (assuming the software policy is to turn the DDR off in Standby mode), the STM32MP15x software must manage the IpDDR2 / IpDDR3 power down in the following order:

- Software receives an event to go into Off or Standby mode.

- 2. Assert IpDDR CKE low.

- Disable BUCK2:

- a. VDD2 DDR voltage falls in less than 1.5 ms (thanks to the BUCK2 Slow Pull-Down discharge resistor).

- b. VREF\_DDR voltage follows VDD2\_DDR / 2 (REFDDR is push-pull LDO).

- 4. Wait 1.5 ms, disable REFDDR (VREF DDR is already 0 V as voltage falls in previous step).

- 5. Disable LDO3: VDD1\_DDR falls in less than 3 ms (thanks to LDO3's pull-down discharge resistor). The constraint is that step 3 to step 5 must be performed in less than 20 ms to comply IpDDR2 / IpDDR3 JEDEC constraints.

## IpDDR2 / IpDDR3 uncontrolled power-off sequence:

Uncontrolled power off sequence occurs typically on battery voltage removal or when a reset occurs. In that case, STPMIC1BPQR manages power off sequence:

- 1. Battery is removed: VBAT drop.

- 2. VBAT crosses the VINOK\_fall : STPMIC1BPQR turn off condition.

- STPMIC1BPQR starts a power off sequence:

- a. STPMIC1BPQR assert reset (NRST) → STM32MP15x asserts DDR\_CKE pin low and DDR\_CLKP / DDR\_CLKN clock signals are stopped.

As soon as STPMIC1BPQR asserts the NRST, the reset signal is propagated to the STM32MP15x: DDR\_CKE is set low, DDR\_CKP and DDR\_CKN are stopped: lpDDR IC power consumption drops immediately.

- b. STPMIC1BPQR disables Rank0 regulators: BUCK2, LDO3 and REFDDR:

- i. Pull-down discharge resistors are set on BUCK2, LDO3, REFDDR.

- ii. VDD1\_DDR, VDD2\_DDR, VREF\_DDR voltage drops. VDD2\_DDR drops faster because a pull-down discharge resistor is stronger than VDD1\_DDR and VREF\_DDR ones.

BUCK2, LDO3 and REFDDR are disabled by STPMIC1BPQR immediately after reset occurs (Rank0) as those regulators are enabled last (by software) after power up. See [2] for details.

- 4. STPMIC1BPQR disables Rank3, then Rank2 and finally Rank1 regulators (see [2] for details)

- STPMIC1BPQR is off (or no supply).

See Section 5.2.3 for details and limitations.

AN5260 - Rev 2 page 9/54

## 4.2.5 VDD\_eMMC power domain (2.9 V)

VDD\_eMMC is dedicated to power the eMMC Flash memory core domain (VCC). The eMMC Flash memory device has also to be powered from VDD voltage to supply its I/O power domain (VCCQ).

Pull-up resistors must be placed on VDD for CLK, CMD and D0 to avoid extra eMMC power consumption on VDDQ when VDD eMMC is OFF.

VDD\_eMMC is powered from the STPMIC1BPQR LDO2 linear regulator. This voltage domain is the second domain to be enabled during the power up sequence (STPMIC1BPQR Rank2) and it is the penultimate domain to be disabled during the power down sequence.

VDD\_eMMC is enabled in Run, LP-stop and LPLV-stop modes if STM32MP15x software requires a R/W access. Software must disable VDD\_eMMC when no R/W access is expected. VDD\_eMMC is disabled in STANDBY and in Off mode.

STPMIC1BPQR has NVM settings to set LDO2 (VDD\_eMMC) to 2.9 V when the STPMIC1BPQR is powered up. LDO2 (VDD\_eMMC) is needed at power up to supply the eMMC Flash device allowing the STM32MP15x to access this memory from the ROM to boot up.

VDD\_eMMC can be either switched on or off at runtime by the application software.

If the eMMC device is the boot Flash peripheral, the application software must program the STPMIC1BPQR in order to power off the eMMC in Standby mode (PWR\_ON signal low) and power on the eMMC in Run mode (PWR\_ON signal high) before the application goes into Standby mode. In such a case, when the application recovers from Standby mode to Run mode, the eMMC is powered up and ready to be accessed by the STM32MP15x bootROM (peripheral boot).

## 4.2.6 VDD\_SD power domain (2.9 V)

VDD\_SD is dedicated to powering an SD-card device and an SD-card level shifter (VSUPPLY). The SD-card level shifter device is also to be powered from VDD voltage to supply its I/Os power domain (VCCA).

It is powered from the STPMIC1B LDO5 linear regulator.

This voltage domain is the second domain to be enabled during the power up sequence (STPMIC1BPQR Rank2) and it is the penultimate to be disabled during power down sequence.

VDD SD is managed by software and can be turned on or off at runtime.

STPMIC1B has NVM settings to set LDO5 (VDD\_SD) to 2.9 V when the STPMIC1B powers up. LDO5 (VDD\_SD) is needed at power up to supply an SD-card and its level shifter IC allowing the STM32MP15x to access this memory from the ROM to boot up.

VDD SD can be either switched on or off at runtime by the application software.

If the SD-card device is the boot Flash peripheral, the application software must program the STPMIC1B in order to power off the SD-card in Standby mode (PWR\_ON signal low) and power on the SD-card in Run mode (PWR\_ON signal high) before the application goes into Standby mode. In such case, when the application recovers from Standby mode to Run mode, the SD-card is powered and ready to be accessed by the STM32MP15x bootROM (peripheral boot).

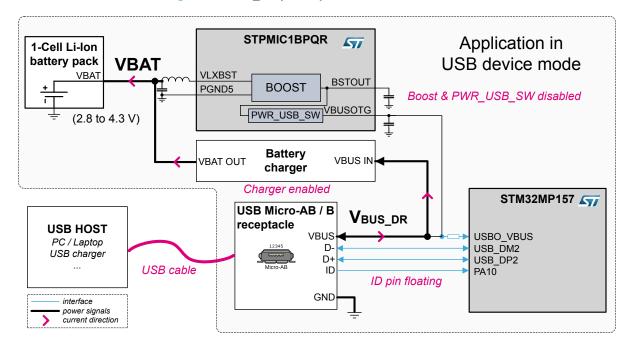

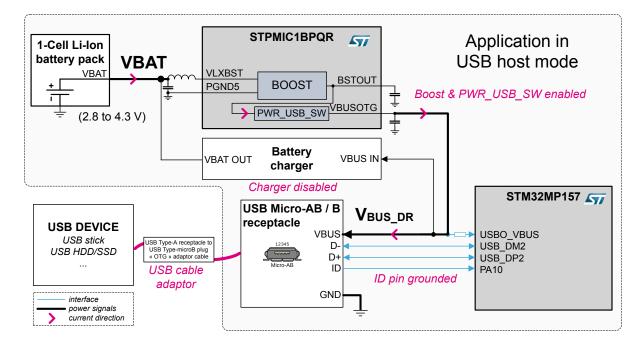

## 4.2.7 VBUS\_DR power domain (5 V)

VBUS\_DR is a dedicated power domain for the USB High Speed interface. VBUS\_DR is connected to the VBUS pin of the USB receptacle and has dual direction current:

- Application in USB device mode: a USB host peripheral is connected to the application and provides VBUS DR to the application (see Figure 2).

- Application in USB host mode: a USB device peripheral is connected to the application and powered from VBUS DR by the application (see Figure 3).

AN5260 - Rev 2 page 10/54

Figure 2. VBUS\_DR power path in USB device mode

Figure 3. VBUS\_DRD power path in USB host mode

## 4.2.8 VDD\_AUDIO (1.8 V), VDD\_LCD (2.8 V) power domains

VDD\_AUDIO and VDD\_LCD are provided to illustrate the reference design in Figure 1. They are respectively powered from LDO1 and LDO6 linear regulators.

VDD\_AUDIO and VDD\_LCD are not enabled by the STPMIC1BPQR at power up. They are enabled and set at the right voltage after power up by software when the related peripheral requires them.

VDD\_AUDIO and VDD\_LCD are managed by software and can be turned on or off at runtime. VDD\_AUDIO and VDD\_LCD are disabled in Standby and in Off modes.

AN5260 - Rev 2 page 11/54

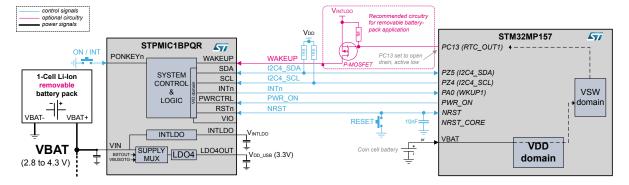

## 4.3 Control signals and interface between STM32MP157 and STPMIC1BPQR

This section outlines the way the STM32MP157 microprocessor communicates with the STPMIC1BPQR device. There are several interface choices which can be used depending on the application requirements. Each interface is described in this first part.

#### I<sup>2</sup>C interface:

The STPMIC1BPQR can be controlled by the STM32MP15x via the I<sup>2</sup>C interface to:

- Enable or disable a regulator

- Set a regulator voltage and mode (low-power or high-power)

- Set low-power management (PWRCTRL behavior)

- Set the interrupt controller or read interrupt status

- Set the protection (watchdog, overcurrent, under-voltage) or read protection status.

- Reprogram the NVM to change the startup behavior.

The STPMIC1BPQR has special default NVM settings that allows it to boot an STM32MP15x application with 1.8 V I/Os from the USB interface (for flashing or loading then executing software) from SD-card or from Flash memory (such as an eMMC). Once the STM32MP15x is able to execute software, it is also able to reprogram the STPMIC1BPQR NVM on the fly to fine tune the application.

## ON / INT push button:

The user "ON / INT" push button is connected to the STPMIC1BPQR PONKEYn pin (active low). This button allows:

- To power up the STPMIC1BPQR.

- To send an interrupt to the STM32MP15x on a button press event or a button release event when the

application is operating.

- To force a power off of the STPMIC1BPQR with a long press (16s by default).

## NRST signal:

The NRST is a bidirectional active low signal for the STM32MP15x and the STPMIC1BPQR. The STM32MP15x NRST pin and STPMIC1BPQR RSTn pin are of digital input / open drain output topology:

- When STPMIC1BPQR asserts RSTn (such as during the power up or the power down sequence), it drives the NRST signal low: the STM32MP15x is forced into a reset state until STPMIC1BPQR releases the NRST.

- When the STM32MP15x asserts an NRST signal (such as an STM32MP15x watchdog reset) or a user

presses on the "RESET" button, STPMIC1BPQR immediately asserts the RSTn pin and performs a noninterruptible power-cycle: the STPMIC1BPQR performs a power down sequence followed by a power up

sequence and finally releases the RSTn.

At the end of power-cycle sequence, STPMIC1BPQR waits for the NRST signal to go high before rearming the reset to avoid infinite reset loop.

#### INTn signal:

The INTn is a STPMIC1BPQR output active low interrupt line connected to the STM32MP15x PA0 input pin. PA0 has both interrupt and wakeup capability:

- To manage interrupt from the STPMIC1BPQR when the STM32MP15x is in either Run or Stop mode.

- To wake-up the STM32MP15x when it is in Standby mode.

## PWR\_ON signal:

The PWR\_ON signal is driven by the STM32MP15x PWR\_ON pin to control STPMIC1BPQR PWRCTRL pin. This allows the STM32MP15x to switch the STPMIC1BPQR power strategy very quickly to one of the following application power modes:

- From Run mode to LPLV\_Stop mode and back

- From Run mode to STANDBY mode and back.

(See [3] for details about Low-power mode management and PWR\_ON pin setting when using STPMIC1BPQR)

AN5260 - Rev 2 page 12/54

After a power-up or a reset, the STPMIC1BPQR PWRCTRL pin is disabled. Before going in Low-power mode, the STM32MP15x sets the STPMIC1BPQR via I²C to program the expected power behavior according to the PWR\_ON signal state.

#### **EADLY** timer

The EADLY timer prevents the Boot ROM from performing any access to the boot peripheral before it is ready. Typically waiting for a stable voltage on the Flash memory (eMMC or SD-card) to ensure the boot software is reliably read by the Boot ROM. Default delay period after reset is 10 ms. (see [5] for details)

#### **POPL** timer

The STM32MP15x POPL timer allows the STM32MP15x to be kept in standby and to assert a PWR\_ON signal low for a minimum duration to allow the peripheral regulators to stop before restarting them. This is to ensure the peripherals restart properly if a wakeup event occurs just after application goes into standby. The STPMIC1BPQR has a discharge resistors on each regulator output that allows all of the regulator output voltages to discharge in less than 3 ms. So, POPL can be set to a minimum of 3 ms or can be kept with default value (10 ms) if the wakeup duration from standby is not critical.

#### WAKEUP signal (optional):

The WAKEUP signal is driven by the STM32MP15x PC13 (RTC\_OUT) pin to control the STPMIC1BPQR WAKEUP pin. It allows the STM32MP15x to power up the STPMIC1BPQR; typically, when real time clock timer elapses.

This feature is available if a coin cell battery is connected to the STM32MP15x VBAT pin.

## 4.3.1 WAKEUP pin management with removable battery pack application.

If a coin cell battery is connected to the STM32MP1 Series microprocessor VBAT pin with a product powered by a removable battery pack, the circuit diagram described in Figure 4 must be implemented.

Figure 4. WAKEUP pin control circuitry for removable battery pack application

The circuit in Figure 4 isolates the STM32MP1 Series microprocessor PC13 IO voltage from the STPMIC1BPQR WAKEUP pin. This prevents current leakage from the STM32MP1 Series microprocessor PC13 IO:

- When PC13 is set to STPMIC1BPQR VIN via STPMIC1BPQR WAKEUP pin.

- When battery pack is removed.

- When VBAT voltage lower than PC13 voltage.

When using this circuit implementation (see Figure 4), the STM32MP1 Series microprocessor PC13 must be set as open-drain active low I/O. The P-MOSFET must be selected to have a minimum Vgs threshold under 1.8 V (below VINTLDO). The P-MOSFET is able to sustain a drain current (ID) greater than 40  $\mu$ A to drive the WAKEUP pin.

Note: STPMIC1BPQR WAKEUP pin has internal pull-down resistor ( $45K\Omega < Rpd < 80 K\Omega$ ) internally connected to GND.

AN5260 - Rev 2 page 13/54

## 5 Power management

The following power modes are reviewed:

- Operating modes

- · Application Power-up and Power-down modes

- · Low-power management mode

- User reset and crash recovery management

- Software management examples

## 5.1 Operating modes

The application can switch to different operating modes depending of the system activity. The operating modes are managed by the STM32MP15x and they control the power management and the clock distribution (see details in [3]).

Table 3 summarizes the application level operating modes. The STPMIC1BPQR power modes depend on the application Operating mode.

AN5260 - Rev 2 page 14/54

| Operating<br>mode | STPMIC1BPQR Power mode | VBAT <sup>(1)</sup>                                                                                               |   | Description                                                                                                       | Notes |

|-------------------|------------------------|-------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------------------------|-------|

| Run               | Power-on-main          | > VINOK_fall                                                                                                      | 1 | VDD power on VDDCORE power on, system clock on IpDDR active / auto refresh Peripherals power on / off             | (2)   |

| Stop              | Power-on-main          | > VINOK_fall  1  VDD power on  VDDCORE power on, system clock off  IpDDR self refresh  Peripherals power on / off |   | VDDCORE power on, system clock off IpDDR self refresh                                                             | (2)   |

| LPLV-stop         | Power-on-alternate     | > VINOK_fall                                                                                                      | 0 | VDD power on  VDDCORE power on at lower voltage, system clock off  IpDDR self refresh  Peripherals power on / off | (3)   |

| Standby           | Power-on-alternate     | > VINOK_fall                                                                                                      | 0 | VDD power on VDDCORE power off, system clock off IpDDR self refresh / off Peripherals power off                   | (3)   |

| Power-off         | Off                    | > VIN_POR_fall                                                                                                    | - | All power off                                                                                                     | -     |

|                   | No_supply              | < VIN_POR_fall                                                                                                    | - | All power off                                                                                                     | -     |

| Coin-cell-VBAT    | No_supply              | < VIN_POR_fall                                                                                                    | - | All power off except the STM32MP1 Series microprocessor VSW                                                       | (4)   |

Table 3. Application operating modes

- 1. STPMIC1BPQR hardware thresholds. See [2] for details.

- 2. The difference between Run and Stop modes is only based on the STM32MP1 Series microprocessor clock management. For power management, there is no difference between Run and Stop mode.

- 3. There is no difference on the PWR\_ON control pin when entering LPLV\_Stop mode or Standby mode from Run mode (PWR\_ON signal goes from high to low in both cases). But before entering LPLV\_Stop mode or Standby mode, the STM32MP1 Series microprocessor programs the STPMIC1BPQR via I<sup>2</sup>C interface to set the regulators accordingly.

- 4. To retain the content of the STM32MP1 Series microprocessor VSW domain (RTC, backup registers, backup RAM and retention RAM) when VDD is turned off, the STM32MP1 Series microprocessor VBAT pin can be connected to an optional coin cell battery.

## 5.1.1 Application turn-on / turn-off conditions

When the application is in Power-off mode, a turn-on condition is required to Power-up the STPMIC1BPQR into Run mode. Similarly, if the application needs to go into Power-off mode, a turn-off condition is required to Power-down the STPMIC1BPQR.

The STPMIC1BPQR autonomously manages the Power-up and the Power-down sequence when respectively a turn-on or a turn-off condition occurs (see [2] for details).

#### **Turn-on conditions**

The STPMIC1BPQR automatically powers up when the battery voltage (VBAT) rises above VINOK\_rise (an AUTO turn-on feature enabled by default in STPMIC1BPQR NVM). If the STPMIC1BPQR is in the off state (and VBAT > VINOK\_rise), it can be powered up by one of three external triggers:

- "ON / INT" user button press: PONKEYn pin voltage falling edge.

- USB host or USB charger cable insertion: VBUSOTG pin voltage rising edge.

- The STM32MP15x wakeup event occurs (for example RTC or Tamper wake-up via STM32MP15x PC13 pin): WAKEUP pin voltage rising edge.

Note: The STM32MP157 wakeup feature is available if a coin cell battery is connected to STM32MP15x VBAT pin.

AN5260 - Rev 2 page 15/54

On power-up, the STPMIC1BPQR undergoes a transitional power up state where the regulators start sequentially in a predefined order (rank) and voltage, and ends by releasing the NRST signal. After this state, the STPMIC1BPQR goes into Power-ON state and remains there, the application can now be run. This state is reached from Off mode with a Turn-ON condition or from NO\_SUPPLY with VBAT voltage rising higher than VINOK rise (AUTO turn-ON)

#### **Turn-off conditions**

A turn-off condition leads the STPMIC1BPQR to power down and go into the off state. In the off state, all regulators are turned off. If the STPMIC1BPQR is in the ON state, it can be powered down by one of six conditions:

- Software switch-off: I2C command sent by the STM32MP15x to the STPMIC1BPQR.

- "ON / INT" user button long press: when the reset button is pressed for 16 s, the STPMIC1BPQR is turned

off (the delay is programmable).

- Thermal shutdown: if overheating, STPMIC1BPQR shuts down and it restarts when the temperature returns to a correct level.

- Over-current protection: if enabled by software, a over-current on a regulator leads to the STPMIC1BPQR shut down.

- Watchdog: if enabled by software, when the countdown timer reaches 0, the STPMIC1BPQR goes to the off state.

- VINOK\_fall: if VBAT goes below VINOK\_fall threshold, the STPMIC1BPQR goes to the off state.

On power-down, the STPMIC1BPQR undergoes a transitional power down state where the NRST is asserted leading to the regulators stopping sequentially in the reverse order of Power-up sequence. After this state, the STPMIC1BPQR is in the OFF state and remains as such until a Turn-ON condition occurs. This state is reach from Power-ON state with a Turn-OFF condition.

It is important to point out that as soon as a STPMIC1BPQR regulator is disabled, a pull-down resistor is enabled on its output to discharge the decoupling capacitor voltage. The LDO and BUCK regulator output voltages are discharged in 3 ms and 1.5 ms respectively (see [2] for details).

An application can set the STPMIC1BPQR "restart request" feature to automatically restart the application after a turn-off condition (see [2] for details).

## 5.1.2 STPMIC1BPQR restart request and mask reset options

Before a turn-off condition occurs, the STM32MP15x software can program the STPMIC1BPQR to restart instead of turning it off by setting the restart\_request feature in the STPMIC1BPQR. This setting must be done before initiating the turn-off condition; such as after an application power-up.

For example, the software can completely reboot the application by setting the restart request bit in the STPMIC1BPQR (RREQ\_EN = 1) then to program a software switch off (SWOFF = 1). The STPMIC1BPQR performs a power cycle sequence, a power down sequence (disabling all regulators) followed by a power up sequence (restarting regulators then releasing NRST signal).

If the application needs one or several STPMIC1BPQR regulators to be kept enabled during a power cycle, the STM32MP15x software can program the STPMIC1BPQR mask\_reset option by setting the STPMIC1BPQR BUCKS\_MRST\_CR register to target the buck converter and LDOS\_MRST\_CR register to target LDOs (see [2] for details on the STPMIC1BPQR mask\_reset option). This setting must be done before a power cycle, such as after the application power-up.

This is typically the case for the BUCK3 powering the STM32MP15x VDD power domains. The power cycle on VDD must be masked (BUCKS MRST CR[2] = 1) to prevent losing:

- The STM32MP15x backup RAM

- Retention RAM

- The backup register content.

If the BUCKS\_MRST\_CR[2] is not set, this information is lost when a power cycle is triggered by an NRST from the STM32MP15x (see Section 5.4 ) or by a turn-off condition with the restart\_request bit enabled.

AN5260 - Rev 2 page 16/54

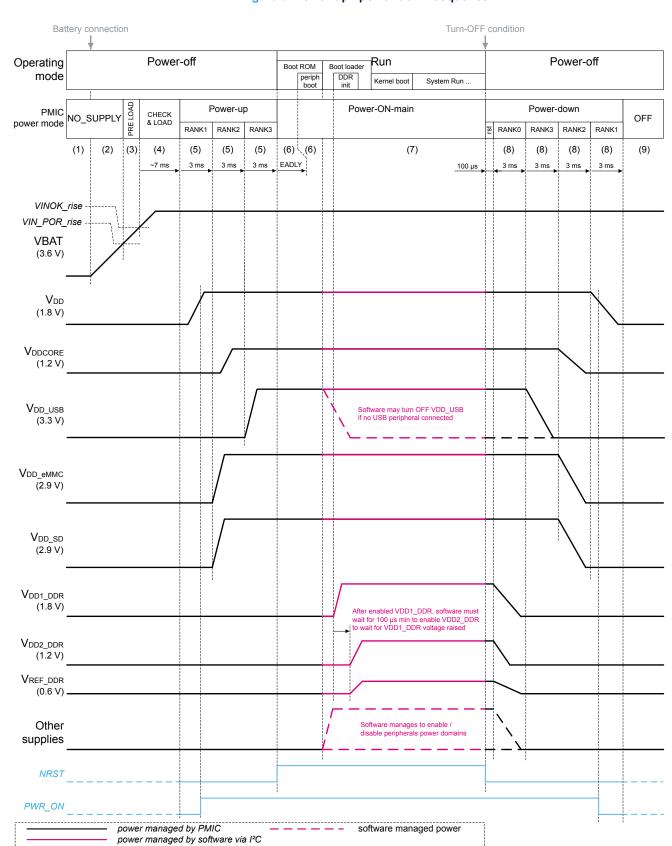

## 5.2 Application power-up / power-down sequence

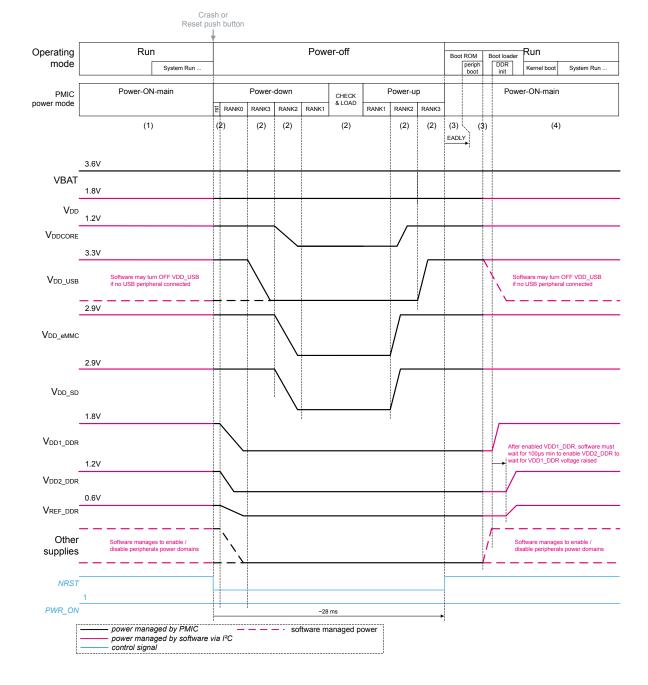

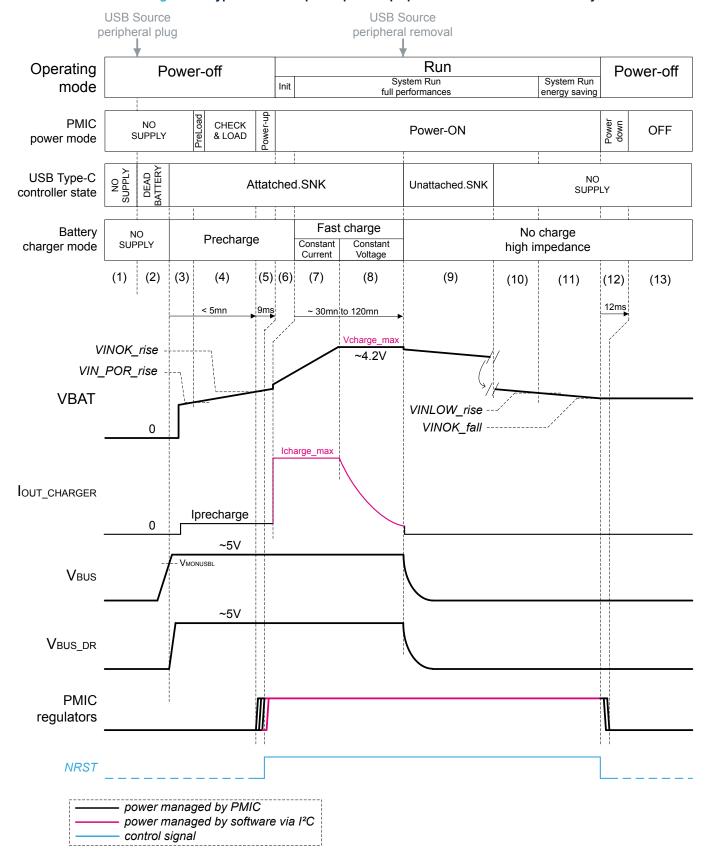

The power-up sequence is the transition managed by the STPMIC1BPQR between Power-off and Run operating modes and similarly for the power-down sequence. The application power-up and power-down sequence is shown in Figure 5 based on the reference design in Figure 1.

## 5.2.1 Power-up by battery insertion

The application is in off condition and has no power connected to it. A battery is connected up and the application starts automatically when VBAT rises (the STPMIC1BPQR has the auto-turn ON enabled by default in its NVM). When the STPMIC1BPQR is powered-up, the application boots (including the IpDDR initialization) and finally the system reaches Run mode. When a turn-off condition occurs, the STPMIC1BPQR powers-down and goes into the Off mode: the application goes into Power-off mode. The whole process is detailed below and illustrated in Figure 5:

- 1. Application has no power or the STM32MP15x is in coin-cell-VBAT mode (powered from coin cell battery to supply the STM32MP15x VSW).

- 2. A well charged battery pack (VBAT > VINOK\_rise) is connected to the application. VBAT voltage rises.

- Once VBAT supply is above VIN\_POR\_rise (STPMIC1BPQR VIN\_POR\_rise threshold is initially set to 2.3 V):

- a. The STPMIC1BPQR initializes and pre-loads its NVM contents.

- b. The STPMIC1BPQR asserts the NRST.

- 4. VBAT supply rises above VINOK\_rise, the STPMIC1BPQR checks the Turn-ON condition (auto turn-ON is enabled in the STPMIC1BPQR NVM). The STPMIC1BPQR starts a power up sequence as a valid turn-on condition is detected.

- The STPMIC1BPQR follows the power-up sequence:

- a. Rank1: BUCK3 (VDD) is enabled at 1.8 V and waits for 3 ms.

- b. Rank2: BUCK1 (VDDCORE) is enabled at 1.2 V. LDO2 (VDD\_eMMC) and LDO5 (VDD\_SD) are enabled at 2.9 V and waits for 3 ms. The STM32MP15x now performs an internal initialization and releases its reset, the STM32MP15x remains in reset as the STPMIC1BPQR is still asserting its NRST signal.

- Rank3: LDO4 (VDD\_USB) is enabled at 3.3 V (hard setting). After 3 ms, the STPMIC1BPQR releases

the NRST signal.

- As the NRST signal rises, both the STM32MP15x and the STPMIC1BPQR release their respective reset pins:

- The STM32MP15x EADLY delay timer (10 ms) starts. Refer to EADLY timer section for more information.

- b. When the EADLY elapses, the boot ROM starts accessing external peripherals (either eMMC or SD-card depending of the STM32MP15x boot pin settings) to load and execute boot loader software.

- The Boot loader can control any STPMIC1BPQR regulator (such as initialize an LCD and plot a splash screen).

- 7. The Boot loader initializes the DDR then loads and executes the Kernel:

- a. LDO3 (VDD1 DDR) is enabled in bypass mode. The software waits at least for a further 100 µs.

- b. DDR VREF (VREF DDR) is enabled.

- c. BUCK2 (VDD2 DDR) is enabled at 1.2 V. The software waits for at least 1.4 ms for BUCK2 readv.

- d. The software initializes the STM32MP15x DDR controller and lpDDR device.

- e. the Boot loader loads and executes the kernel. The kernel initializes.

- f. System is now running.

- 8. A turn-off condition occurs. The STPMIC1BPQR performs a power-down sequence:

- a. The STPMIC1BPQR asserts the NRST (STM32MP15x reset) and waits for 100  $\mu$ s.

- Rank0: the STPMIC1BPQR disables all regulators it has not enabled at power-up (LDO3, BUCK2, DDR\_REF, LDO1, LDO6, BOOST, PWR\_USB\_SW, PWR\_SW) and waits for 3 ms. See also Turn-off conditions section.

- Rank3: LDO4 (VDD\_USB) is disabled and waits for 3 ms.

- Rank2: BUCK1 (VDDCORE), LDO2 (VDD\_eMMC) and LDO5 (VDD\_SD) are disabled and wait for 3 ms.

- e. Rank1: BUCK3 (VDD) is disabled waits for 3 ms.

AN5260 - Rev 2 page 17/54

9. The STPMIC1BPQR is now in Off mode: the application is in Power-off.

AN5260 - Rev 2 page 18/54

Figure 5. Power-up / power-down sequence

AN5260 - Rev 2 page 19/54

## 5.2.2 Power-up from the STPMIC1BPQR Off mode

The application in Figure 5 is powered up from NO\_SUPPLY state, where the battery insertion is the turn-on condition (auto turn-on is enabled in the STPMIC1BPQR NVM).

A power-up from the STPMIC1BPQR Off mode follows a similar sequence as in Figure 5 from Off mode. The difference is when a turn-on condition occurs, the sequence starts from step (4) " CHECK & LOAD" instead of waiting for VBAT to rise.

The differences are detailed below:

- The STPMIC1BPQR is initially powered from a VBAT voltage higher than VINOK\_rise allowing the STPMIC1BPQR to power-up (instead of a battery insertion which triggers VBAT rise in Figure 5).

- Steps (1), (2), (3) of Figure 5 are replaced by a single one; merging "NO-SUPPLY" and "PRE-LOAD" of the STPMIC1BPQR Power modes to "OFF".

- The "Battery connection" event is replaced by the "Power-ON condition" event and is placed between "OFF" and "CHECK & LOAD" of the STPMIC1BPQR state.

## 5.2.3 Power-down by battery removal

The application in Figure 5 is powered off by a turn-off condition with VBAT maintaining a valid voltage.

If the application is powered off by a battery removal, the turn-off condition is VBAT dropping below VINOK\_fall. Once VBAT supply is below VINOK\_fall, the STPMIC1BPQR asserts an NRST for 100µs then powers-down as shown in step (8) onwards in Figure 5.

Limitation: When the battery is removed, VBAT voltage drops very quickly to VINOK\_fall value, in less than a few milliseconds (depending on system activity), only then does the power-down sequence start. As soon as the STPMIC1BPQR asserts an NRST, system activity is immediately stopped and power consumption drops, slowing VBAT drop. Nevertheless, VBAT may drop below VIN\_POR\_fall threshold before the power-down sequence ends. In this case, the STPMIC1BPQR regulators pull-down discharge resistors are no longer controlled by the STPMIC1BPQR. A bulk decoupling capacitor (a few hundred  $\mu$ F) may be inserted on VBAT path to limit VBAT dropping speed.

This sequence is important mainly to manage the "lpDDR2 / lpDDR3 uncontrolled power-off sequence" described in Section 4.2.4 .

AN5260 - Rev 2 page 20/54

## 5.3 Low-power mode management

The STM32MP15x supports several operating modes to reduce power consumption (see Section 5.1 ). This section describes the LPLV-stop and Standby low-power modes (see [3] for details).

Note:

Stop mode concerns the STM32MP15x internal clock management without external power management. So Stop mode is not described in this section.

Low-power modes are managed by the STM32MP15x. The STM32MP15x PWR\_ON output pin is connected to the STPMIC1BPQR PWRCTRL input pin. The STPMIC1BPQR states can then be switched: Power-ON-main to Power-ON-alternate and vice versa.

After power-up, the STPMIC1BPQR goes into Power-ON-main until the STM32MP15x tells the STPMIC1BPQR to activate PWRCTRL pin in active low by setting PWRCTRL\_POL = 0 and PWRCTRL = 1 in STPMIC1BPQR MAIN\_CR register.

Table 3 summarizes the STPMIC1BPQR states according to PWR\_ON signal with related operating modes.

When the STPMIC1BPQR goes from Power-ON-main to Power-ON-alternate, it internally switches from the MAIN control registers (xxxx\_MAIN\_CR) content to the ALTERNATE control registers (xxxx\_ALT\_CR) content and vice versa (see [2] for details).

Before entering in Low-power mode, the STM32MP15x must set the STPMIC1BPQR ALTERNATE control registers in line with the expected STPMIC1BPQR regulator settings for Low-power mode behavior. If needed, the STM32MP15x must set the STPMIC1BPQR MAIN control registers to guarantee that the application leaves the Low-power mode.

## 5.3.1 LPLV-stop mode

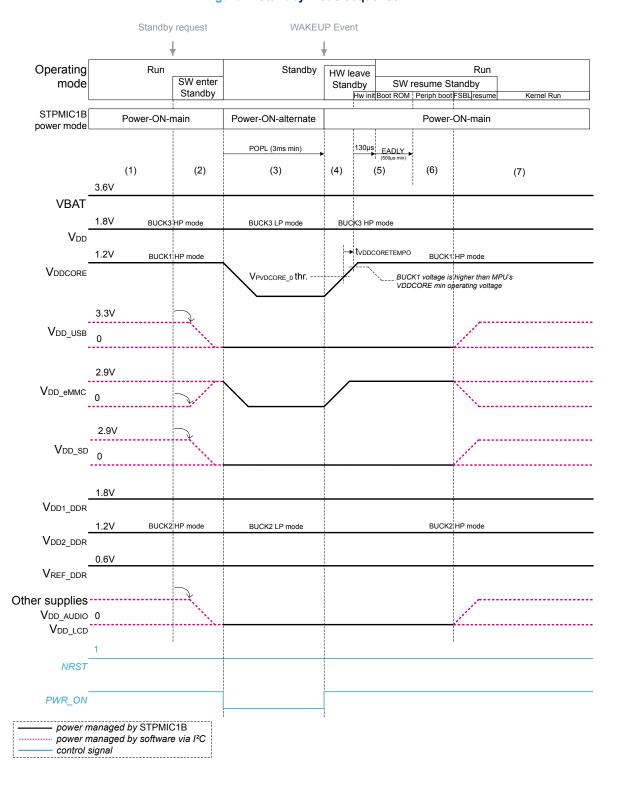

The application LPLV-stop mode sequence is shown in Figure 6 based on to the implementation shown in Figure 1.

- The application is powered up and works in Run operating mode; the STPMIC1BPQR is in Power-ON-main state

- 2. When the LPLV Stop operating mode is requested, the software prepares LPLV process:

- a. the STM32MP15x settings such as: stoping some clocks, setting DDR to Self-Refresh, setting PWRLP\_TEMPO.

- b. STPMIC1BPQR settings:

- BUCK1 (VDDCORE): 1.2 V HP in main mode, 0.9 V LP in alternate mode

- BUCK2 (VDD2 DDR), BUCK3 (VDD): ON HP in main mode and ON LP in alternate mode.

- The STM32MP15x sets the LPDS and LVDS bits of the PWR\_CR1 register to wait entering LPLV-: PWR\_ON signal is de-asserted when the STM32MP15x enters LPLV-stop. The STPMIC1BPQR goes in Power-ON-alternate state:

- Buck1 voltage decreases to 0.9 V

- All buck regulators go into Low-power mode.

- 4. On a wakeup event, the STM32MP15x leaves LPLV- mode and asserts a PWR\_ON signal:

- a. The STM32MP15x tSEL\_VDDCORETEMPO is timed out to wait for VDDCORE to reach the Run mode operating supply voltage level.

Note:

$tSEL\_VDDCORETEMPO = 380 \mu s typ (see [5] and [6]).$

- b. The STPMIC1BPQR goes in Power-ON-main state:

- BUCK1 voltage rises from 0.9 V to 1.2 V (in 130 μs max )

Note:

STPMIC1BPQR Buck1 has 2.3 mV/µs min slew rate.

- In parallel, all buck converters go from Low-power to High power mode (100 μs).

- 5. Once the tSEL VDDCORETEMPO is elapsed, a clock restore process is performed in the STM32MP15x.

- 6. Once the STM32MP15x HSI clock oscillator is stable (~5 μs), the PWRLP\_TEMPO timer is timed out to waiting for peripheral to be stable.

Where PWRLP\_TEMPO is an STM32MP15x dedicated timer designed to wait for the regulator recovery when the application goes from LPLV- mode to Run mode. When using the STPMIC1, PWRLP\_TEMPO delay can be set to 0 or bypassed as tSEL\_VDDCORETEMPO duration is higher than the STPMIC1BPQR total recovery time. Nevertheless, if an application is set in LP\_ (instead of LPLV\_), the STM32MP15x does not time out the tSEL\_VDDCORETEMPO delay. So, PWRLP\_TEMPO must be set to  $100\mu$ s to let the STPMIC1BPQR regulators recover from LP to HP mode.

AN5260 - Rev 2 page 21/54

\* Only if IpDDR works in self-refresh, else BUCK2 must be kept in HP mode if IpDDR keeps to work in auto-refresh.

7. When PWRLP\_TEMPO elapses, the application goes into Run mode. The software resume LPLV- mode (restores clocks, resumes IpDDR from self-refresh, ...).

LPLV\_STOP request WAKEUP Event Run Run LPLV-Stop Operating HW leave SW enter LPLV-Stop SW resume mode LPLV-Stop wait HSI osc LPLV-Stop **PMIC** Power-ON-main Power-ON-alternate Power-ON-main power mode ~5µs PWRLP\_TEMPO (1) (2) (3) (6) (7) (4) (5) 3.6V **VBAT** BUCK3 HP mode BUCK3 LP mode BUCK3 HP mode  $V_{\text{DD}}$ BUCK1 LP mode 0.9V 1.2V BUCK1 HP mode 1.2V BUCK1 HP mode  $V_{\text{DDCORE}}$ 130µs max V<sub>DD\_USB</sub> <sub>0</sub> VDD\_eMMC or  $V_{DD\_SD}$  0 VDD1\_DDR 1.2V BUCK2 LP mode \*  $V_{DD2\_DDR}$ VREF\_DDR Other supplies --- $V_{\text{DD\_AUDIO}} \ 0$  $V_{DD\_LCD}$ NRST PWR\_ON - power managed by PMIC

Figure 6. LPLV-stop mode sequence

AN5260 - Rev 2 page 22/54

power managed by software via I<sup>2</sup>C

control signal

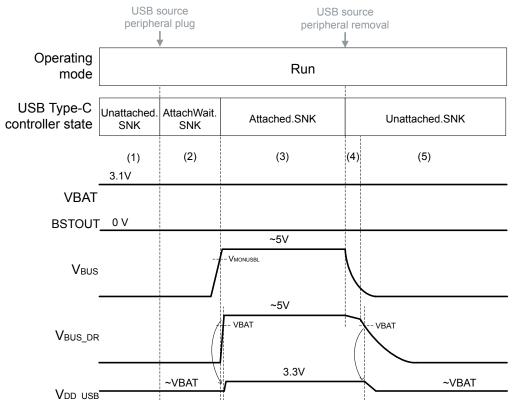

## 5.3.2 Standby mode

The application Standby mode sequence is shown in Figure 6 according to the implementation shown in Figure 1. In this application, the eMMC flash memory voltage (VDD\_eMMC) must be present when leaving Standby mode allowing the STM32MP15x to read the boot software (FSBL). In Standby mode, IpDDR memory works in self-refresh.

- The application is powered up and is operating in Run mode; the STPMIC1BPQR is in Power-ON-main state.

- 2. When Standby mode is requested, the software prepares to enter standby by changing:

- a. The STM32MP15x settings such as:

- Stopping certain clocks

- Sets DDR in Self-Refresh

- Sets POPL and EADLY

For details on the POPL refer to POPL timer.

For details on the EADLY timer refer to the EADLY timer. In this application, VDD\_eMMC rises in less than 500  $\mu$ s (LDO2). So EADLY can be set to 500  $\mu$ s minimum or can be kept with default value (10 ms) if wakeup duration from standby is not critical.

- Timers and so on.

- b. The STPMIC1BPQR settings:

- i. BUCK1 (VDDCORE), LDO2 (VDD\_eMMC): ON HP in main mode, OFF in alternate mode

- LDO4 (VDD\_USB), LDO5 (VDD\_SD), LDO1 (VDD\_AUDIO), LDO6 (VDD\_LCD): OFF in main and alternate modes.

- iii. BUCK2 (VDD2 DDR), BUCK3 (VDD) ON HP in main mode and ON LP in alternate mode

- 3. The STM32MP15x resets the LPDS and LVDS bits to wait while entering Standby mode: PWR\_ON signal is de-asserted when the STM32MP15x enters standby:

- a. The POPL timer is started to prevent the STM32MP15x leaving standby before POPL elapses.

- b. The STPMIC1BPQR goes in Power-ON-alternate state:

- i. BUCK1 (VDDCORE), LDO2 (VDD eMMC): regulators are powered OFF

- BUCK2 (VDD2\_DDR), BUCK3 (VDD) regulators go in LP mode

- 4. On a wakeup event, the STM32MP15x leaves Standby mode and asserts a PWR\_ON signal:

- a. The STPMIC1BPQR goes in Power-ON-main state:

- i. BUCK1 (VDDCORE), LDO2 (VDD eMMC): regulators are powered ON

- ii. BUCK2 (VDD2 DDR), BUCK3 (VDD) regulators go into HP mode

- b. When VDDCORE voltage is above the VPVDCORE\_0 min threshold, a tVDDCORETEMPO is started.

As long as the tVDDCORETEMPO timer is not elapsed, the STM32MP15x is kept in reset internally.

The STM32MP15x internal voltage threshold, VPVDCORE\_0 rising edge, is 0.95 V min.

The STM32MP15x internal delay. tVDDCORETEMPO is 200 µs min.

- 5. When tVDDCORETEMPO elapses, the STM32MP15x is taken out of internal reset (VDDCORE\_OK):

- vDDCORE voltage is higher than STM32MP15x VDDCORE min operating voltage.

BUCK1 has a 2.3 mV/µs minimum slew rate guarantying the VDDCORE voltage is higher than the STM32MP15x VDDCORE min operating voltage when tVDDCORETEMPO elapses.

- b. The STM32MP15x performs an internal hardware initialization (enables the HSI and option bytes loading over a 130 µs duration) then enters in Run mode.

- c. EADLY delay timer is started.

- 6. When the EADLY delay timer is elapsed, the boot ROM starts accessing external peripherals (flash memory) to load and execute boot software. Implicitly, when EADLY has elapsed, VDD\_eMMC voltage is stable:

- a. The boot ROM is read from the eMMC, verifies and executes the FSBL.

- b. From this step, the software can set the STPMIC1BPQR via I<sup>2</sup>C interface to set any regulator.

- 7. The software detects an "exit from Standby mode" it then resumes and runs the Kernel software.

AN5260 - Rev 2 page 23/54

Figure 7. Standby mode sequence

AN5260 - Rev 2 page 24/54

## 5.4 User reset and crash recovery management

As introduced in Section 4.3 , the STM32MP15x and the STPMIC1BPQR both have bidirectional active low reset pins interconnected (see Figure 1 signal NRST).

If an STM32MP15x crash occurs (iwdg1\_out\_rst or iwdg2\_out\_rst watchdog elapsing), a reset pulse is generated by the STM32MP15x on NRST signal. The reset pulse is caught by the STPMIC1BPQR that triggers an immediate power cycle sequence: a STPMIC1BPQR power-down sequence followed by a STPMIC1BPQR power-up sequence.

A power cycle allows the peripherals to restart and reset properly after a crash occurs; especially for peripherals that do not have a reset input signal. Power cycling is mainly recommended for peripheral boot devices and Flash memory devices such as: eMMC, NAND, NOR, SD-Card. Power cycling is not performed on the STPMIC1BPQR BUCK3 (VDD) that needs to be keep enabled during reset (see Section 5.1.2 for details of the STPMIC1BPQR mask reset option).

If the reset button is pressed by a user, the same power cycle sequence is performed by the STPMIC1BPQR.

## 5.4.1 Crash recovery management or user reset sequence

The sequence in Figure 8 illustrates a crash recovery sequence according to the implementation shown in Figure 1. In this sequence, the crash happens in Run mode (by IWDG reset). Neverthless, a IWDG reset could occur in all modes, including: Run, Stop, LP-stop, LPLV-stop, and STANDBY modes.

- The application is powered up and is in Run mode; the STPMIC1BPQR is in Power-ON-main state. A

crash occurs (iwdg1\_out\_rst or iwdg2\_out\_rst watchdog elapsing) or the reset button is pressed by the user

generating a pulse on NRST signal.

- The STPMIC1BPQR detects the reset assertion (NRST pulse low) and starts a non-interruptible power cycle:

- a. The STPMIC1BPQR asserts NRST low.

- b. The STPMIC1BPQR performs power-down sequence.

- The STPMIC1BPQR checks the conditions to restart (such as VBAT, temperature) and reloads the internal NVM.

- d. The STPMIC1BPQR performs power-up sequence.

- e. The STPMIC1BPQR releases NRST.

If the reset signal (NRST) is still asserted at this step (such as the user is still pressing reset button), the STPMIC1BPQR waits for the reset signal to be released before rearming the reset circuit. This is to avoid the STPMIC1BPQR repeating a power cycle loop.

## Note: STPMIC1BPQR power cycle duration is ~28 ms.

- The NRST signal rises as the STM32MP15x and the STPMIC1BPQR release their respective reset pins (and reset button released):

- a. The STM32MP15x EADLY delay timer (10 ms) is started. For information on the EADLY timer refer to EADLY timer.

- b. When EADLY is elapsed, the Boot ROM starts accessing external peripherals (either eMMC or SD-card depending on the STM32MP15x boot pins setting) to load and execute boot loader software.

- c. The Boot loader controls any STPMIC1BPQR regulator (such as to initiate an LCD and plot splash screen).

- 4. The boot loader initializes the DDR then loads and executes the Kernel:

- a. LDO3 (VDD1 DDR) is enabled in bypass mode. The software waits at least 100 μs.

- b. DDR\_VREF (VREF\_DDR) is enabled.

- BUCK2 (VDD2\_DDR) is enabled at 1.2 V. The software waits for at least 1.4 ms for BUCK2 to be readv.

- The software initializes the STM32MP15x DDR controller and lpDDR device.

- e. The Boot loader loads and executes the kernel and the kernel initializes.

- f. System is running.

AN5260 - Rev 2 page 25/54

Figure 8. Crash recovery sequence

AN5260 - Rev 2 page 26/54

## 5.5 Software management example

This section presents one possible software integration strategy of the STPMIC1BPQR management by the STM32MP15x.

The OpenSTLinux software distribution integrates the way the STPMIC1BPQR regulators are driven and configured by the STM32MP15x to match Operating mode presented in Section 5.1.

To summarize the main OpenSTLinux integration points:

- Interface with the STPMIC1BPQR is performed in the low level "secure monitor" part of the boot chain split between FSBL (for example : TF-A) and SSBL (for example: U-Boot).

- The STPMIC1BPQR power management strategy presented in Table 4 below is configured in Secure Monitor dts file (typ TF-A) using Linux Regulator framework binding terminology.

- Each STPMIC1BPQR power source is seen as a "regulator" on which software application and driver registers as a "consumer". Typically, a regulator is enabled when it is requested by one consumer. The exception is made for the core supply which has to be kept alive whatever consumer registration state with the "Always-on" option.

To learn more about the Power management function in OpenSTLinux, refer to following online user guide articles:

https://wiki.st.com/stm32mpu/wiki/Power\_overview https://wiki.st.com/stm32mpu/wiki/Regulator overview .

AN5260 - Rev 2 page 27/54

Table 4. STPMIC1BPQR power management options

| Application<br>Power<br>Domain | STPMIC1BPQR<br>supply source | Default<br>Power<br>On<br>State<br>(NVM) | STM32MP15x =<br>Run / Stop<br>PMIC=<br>POWER_ON<br>Main | STM32MP15x = LPLV-<br>stop<br>PMIC= POWER_ON<br>Alternate | STM32MP15x = STANDBY DDR OFF PMIC= POWER_ON Alternate | Options/<br>Comments                                                    |

|--------------------------------|------------------------------|------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------|

| VDD                            | BUCK3                        | 1.8V                                     | 1.8V / HP <sup>(1)</sup> / Always-on <sup>(2)</sup>     | 1.8V / LP                                                 | 1.8V                                                  | Mask_reset <sup>(3)</sup> ,<br>overcurrent<br>protection <sup>(4)</sup> |

| VDDCORE                        | BUCK1                        | 1.2V                                     | 1.2V/ HP /<br>Always-on                                 | 0.9V / LP                                                 | Off                                                   | Overcurrent protection                                                  |

| VDD_USB                        | LDO4                         | 3.3V                                     | 3.3V/ Consumer driven <sup>(5)</sup>                    | 3.3V / Consumer driven                                    | Off                                                   | -                                                                       |

| VDD1_DDR                       | LDO3                         | OFF                                      | 1.8V/ Always-on                                         | 1.8V                                                      | Off                                                   | Overcurrent protection                                                  |

| VDD2_DDR                       | BUCK2                        | OFF                                      | 1.2V / HP /<br>Always-on                                | 1.2V / LP                                                 | Off                                                   | Overcurrent protection                                                  |

| VREF_DDR                       | DDR_REF                      | OFF                                      | 0.6V / Always-on                                        | 0.6V                                                      | Off                                                   | -                                                                       |

| VDD_eMMC                       | LDO2                         | 2.9V                                     | 2.9V/ Consumer driven                                   | 2.9V/ Consumer driven                                     | Off / Boot on <sup>(6)</sup>                          | -                                                                       |

| VDD_SD                         | LDO5                         | 2.9V                                     | 2.9V/ Consumer<br>Driven                                | 2.9V/ Consumer driven                                     | Off                                                   | -                                                                       |

| VBUS_DR                        | PWR_USB_SW                   | OFF                                      | ON                                                      | Off (suspend not supported on MP1 side )                  | Off                                                   | Pure software.<br>No alternate<br>registers                             |

| VDD_AUDIO                      | LDO1                         | OFF                                      | 1,8V / Consumer<br>Driven                               | 1,8V / Consumer driven                                    | Off                                                   | -                                                                       |

| VDD_LCD                        | LDO6                         | OFF                                      | 1,8V / Consumer<br>Driven                               | 1,8V / Consumer driven                                    | Off                                                   | -                                                                       |

- 1. HP/LP mode of the STPMIC1BPQR regulator. Refer to [2]

- 2. Always-on: Keeps the core voltage on even if there is no software consumer.

- 3. Mask\_reset: Specify the STPMIC1BPQR mask\_reset option to this regulator not to be impacted by a reset power cycle. (see Section 5.1.2 )

- 4. Overcurrent protection: Specify the STPMIC1BPQR option OCPOFF on this regulator. Overcurrent detection leads to a STPMIC1BPQR shutdown. Refer to [2]

- 5. Consumer driven: Linux driver turns the regulator on/off following consumer demand. When entering Low-power mode, the last Run status is applied (Main mode duplicate in Alternate mode). The user has to consider the required status before entering Low-power mode. For example when the powered peripheral is set as wake-up source.

- 6. Boot on: Software must set this regulator on in POWER\_ON Main mode before entering into Low-power mode (switch to STPMIC1BPQR Alternate mode) in order to turn on immediately on wake-up (switch back to Main mode).

AN5260 - Rev 2 page 28/54

## 6 USB port management

## 6.1 USB port using legacy micro-AB (OTG) or micro-B receptacle (DR)

Figure 1, Figure 2 and Figure 3 illustrate a micro-AB receptacle for USB OTG extension support. Alternatively, a micro-B receptacle (having an ID pin) may be used only if USB DR mode is expected. Using a micro-B receptacle, the application natively supports the USB peripheral mode and it also supports the USB host mode if a "non USB compliant" adapter pin ID is set to ground.

Note: Adaptor stands for a USB micro-B plug with ID pin grounded to USB type-A receptacle.

Figure 9 provides details on the USB port integration with a Type micro-B or a Type micro-AB receptacle.

The VBUS pin of a USB receptacle is connected to VBUS DR power domain and it is interconnected to:

- The STPMIC1BPQR VBUSOTG pin: PWR\_USB\_SW is a power switch which provides VBUS to the USB receptacle from Boost SMPS converter for a A-session or to detect a valid VBUS from USB receptacle for a B-session.

- The STM32MP15x USBO VBUS pin to detect the presence of VBUS DR voltage for a B-session

- The Battery charger input to charge the Li-lon battery pack from the USB receptacle in B-session.

Figure 9. USB port management using a USB micro-AB or micro-B receptacle

Note:

- 1. STM32MP15x and STPMIC1BPQR are simplified figures focusing on USB feature integration.

- 2. STM32MP15x decoupling scheme not shown (see [1] related chapter).

- 3. STPMIC1BPQR discrete component values not shown (see [2]).

- 4. Additional protection, such as ESD, EMI filtering, overvoltage, not shown.

AN5260 - Rev 2 page 29/54

## 6.1.1 USB peripheral plug detection and peripheral removal detection management

## Power-up by USB host peripheral plug:

This document assumes the application in Figure 9 is in Power-off mode with the STPMIC1BPQR in Off mode (See Table 3 for details on the operating modes). The battery voltage VBAT is higher than the STPMIC1BPQR VINOK\_rise allowing STPMIC1BPQR to Power-ON. A cable from USB host peripheral or USB charger peripheral is plugged into the USB receptacle causing the VBUS\_DR voltage to rise. This triggers a STPMIC1BPQR Turn-ON conditions (STPMIC1BPQR VBUSOTG pin connected to VBUS\_DR).

A USB device peripheral cable plug is not a STPMIC1BPQR Turn-ON condition as USB\_ID signal is not connected to the STPMIC1BPQR to detect a Turn-ON event.

## Wake up by USB peripheral plug:

This document assumes the application in Figure 9 is in Stop, LPLV-stop or Standby operating mode. Implicitly, the STPMIC1BPQR is in Power-ON mode.

A cable from the USB host peripheral or USB charger peripheral is plugged into the USB receptacle causing the VBUS\_DR voltage to rise. The rising voltage on the STPMIC1BPQR VBUSOTG pin triggers an interrupt to the STM32MP15x via INTn signal that wakes up the STM32MP15x.

The STPMIC1BPQR interrupts need to be enabled by software before being activated by setting the STPMIC1BPQR INT\_MASK\_R1[VBUSOTG\_RI] bit. See [2] for details.

## Wake up by USB peripheral removal:

This document assumes the application in Figure 9 is in Stop or LPLV-stop or Standby operating mode. Implicitly, the STPMIC1BPQR is in Power-ON mode.

A cable from the USB host peripheral or USB charger peripheral is removed from the USB receptacle causing the VBUS\_DR voltage to fall. The falling voltage on the STPMIC1BPQR VBUSOTG pin triggers an interrupt on the STM32MP15x via INTn signal that wakes up the STM32MP15x.

The STPMIC1BPQR interrupts need to be enabled by software before being activated by setting the STPMIC1BPQR INT\_MASK\_R1[VBUSOTG\_FA] bit. See [2] for details.

## Run time detection by USB peripheral plug:

The application in Figure 9 is in Run operating mode. Implicitly, the STPMIC1BPQR is in Power-ON mode.

## · USB host or charger peripheral case:

A cable from USB host peripheral or USB charger peripheral is plugged into USB receptacle causing the VBUS\_DR voltage to rise. In Run operating mode, there are two detection sources:

- Voltage rising on the STPMIC1BPQR VBUSOTG pin which triggers an interrupt to STM32MP15x via INTn signal.

- The rising voltage on the STM32MP15x USBO\_VBUS pin can trigger an interrupt to the STM32MP15x USB OTG controller.

For this to happen, the STM32MP15x USB OTG controller interrupts need to be enabled. The status can be read in STM32MP15x GINTSTS[SRQINT]. See [5] for details.

## USB device peripheral case:

A cable from a USB device peripheral is inserted into the USB receptacle grounding the USB\_ID signal and pulling the STM32MP15x PA10 signal low. This triggers an interrupt in the STM32MP15x USB OTG controller.

For this to happen, the STM32MP15x USB OTG controller interrupts need to be enabled. The status can be read in STM32MP15x GOTGINT [IDCHNG]. See [5] for details.

## Run time detection by USB peripheral removal:

The application in Figure 9 is in Run operating mode. Implicitly, the STPMIC1BPQR is in Power-ON mode.

AN5260 - Rev 2 page 30/54

## USB host or charger peripheral case:

A cable from USB host peripheral or USB charger peripheral is removed from USB receptacle causing the VBUS DR voltage to drop. In Run operating mode, there are two detection sources:

Voltage drop on the STPMIC1BPQR VBUSOTG pin which triggers an interrupt to the STM32MP15x via INTn signal.

Voltage drop on the STM32MP15x USBO\_VBUS pin triggers an interrupt in the STM32MP15x USB OTG controller.

For this to happen, the STM32MP15x USB OTG controller interrupts need to be enabled. The status can be read in STM32MP15x GINTSTS[DISCINT]. See [5] for details.

## USB device peripheral case:

A cable from a USB peripheral device is removed from USB receptacle causing the USB\_ID signal to go high and so the STM32MP15x PA10 signal to go high also. This triggers an interrupt in STM32MP15x USB OTG controller.

For this to happen, the STM32MP15x USB OTG controller interrupts need to be enabled. The status can be read in STM32MP15x GOTGINT [IDCHNG]. See [5] for details.

## 6.1.2 Generate VBUS\_DR voltage from battery voltage in USB host mode

When a USB device peripheral is plugged in and is detected by the STPMIC1BPQR (see Section 6.1.1 ), the STPMIC1BPQR initiates an A-session:

- 1. Software initializes USB OTG controller in A-device mode (host mode)

- Software sets the STPMIC1BPQR to generate VBUS DR from the battery:

- a. Enable the STPMIC1BPQR Boost converter (to convert VBAT to 5.2 V)

- b. Wait for at least 1.5 ms for the BSTOUT voltage to stabilize

- c. Enable STPMIC1BPQR PWR USB SW power switch: VBUS DR rises to 5.2 V

Conversely, when the USB device peripheral is removed and a detached state is detected by the STM32MP15x, it ends the A-session and disable VBUS DR:

- 1. Disable the STPMIC1BPQR PWR\_USB\_SW power switch: VBUS\_DR is tied low by discharge pull down (see Section 6.1.3 )

- 2. Disable the STPMIC1BPQR boost converter

## 6.1.3 VBUS\_DR discharge pull-down management with STPMIC1BPQR

The STPMIC1BPQR PWR\_USB\_SW power switch has a programmable pull-down to discharge the decoupling capacitor on the VBUS\_DR path.

After the STPMIC1BPQR Power-ON, the pull-down needs to be enabled by software (disabled by default).

When PWR\_USB\_SW is enabled (A-session valid), the pull-down is automatically disabled by the STPMIC1BPQR. When the USB device peripheral is removed and a detached signal has been detected by the STM32MP1 Series microprocessor, the STM32MP1 Series microprocessor disables the STPMIC1BPQR PWR\_USB\_SW. The pull-down is automatically enabled by the STPMIC1BPQR tying VBUS\_DR low (discharge decoupling capacitor on VBUS\_DR).

When a USB host peripheral is connected to a USB receptacle and a B-session valid voltage is detected, disable the STPMIC1BPQR PWR\_USB\_SW pull-down by software to avoid continued current consumption. When the USB host peripheral is removed and a detached signal has been detected by the STM32MP1 Series microprocessor, the STPMIC1BPQR PWR\_USB\_SW is set to pull-down by software to completely discharge VBUS\_DR.

### 6.1.4 The STM32MP15x USB PHY supply with battery discharged below 3.3 V

The STM32MP15x USB PHY has three voltage domains 1.1 V, 1.8 V and 3.3 V (see Figure 9):

The 1.8 V (VDDA1V8 REG) is supplied from VDD power source from the STPMIC1BPQR BUCK3.

The 1.1 V (VDDA1V1\_REG) is supplied by the STM32MP15x 1V1\_reg (internal STM32MP15x LDO) having VDD as power source.

The 3.3 V (VDD3V3\_USBHS and VDD3V3\_USBFS) are supplied from VDD\_USB from STPMIC1BPQR LDO4. When the battery is discharged (VBAT is under than 3.3 V), the STPMIC1BPQR LDO4 cannot generate VDD\_USB voltage at 3.3 V from VBAT (PMIC's VIN pin). So the voltage is too low to supply 3.3 V the USB PHY power domain.

AN5260 - Rev 2 page 31/54

To continue supplying the STM32MP15x USB PHY with the right voltage (VDD\_USB at 3.3 V) from a partially discharged battery, it uses one of the STPMIC1BPQR LDO4 input: VIN, BSTOUT or VBUSOTG. The STPMIC1BPQR automatically manages the LDO4 input from the highest voltage source.

## **USB** host peripheral case

When a USB host peripheral (like a Personal Computer) is plugged, it provides VBUS ( $\sim$ 5 V) to the application: the VBUS\_DR (and the STPMIC1BPQR VBUSOTG) voltage rises. The LDO4 input is automatically switch to VBUSOTG power source as it is higher than battery voltage: VBUSOTG = VBUS  $\sim$ 5 V and VBAT  $\leq$  3.3 V. With  $\sim$ 5 V as supply input source, the LDO4 is able to generate VDD USB at 3.3 V.

#### USB device peripheral case

When a USB device peripheral (like a USB memory stick) is plugged in and has been detected by the STM32MP15x (see Section 6.1.1 ), the STM32MP15x initiates a A-session and the STPMIC1BPQR generates VBUS\_DR voltage from the battery voltage (VBAT) via the boost converter (see section Section 6.1.2 ). The boost converter output (BSTOUT) generates a 5.2 V supply. The LDO4 input is automatically switch to BSTOUT power source as BSTOUT voltage is higher than battery voltage: BSTOUT = 5.2 V and VBAT  $\leq$  3.3 V. With 5.2 V as supply input source, the LDO4 is able to generate VDD USB at 3.3 V.

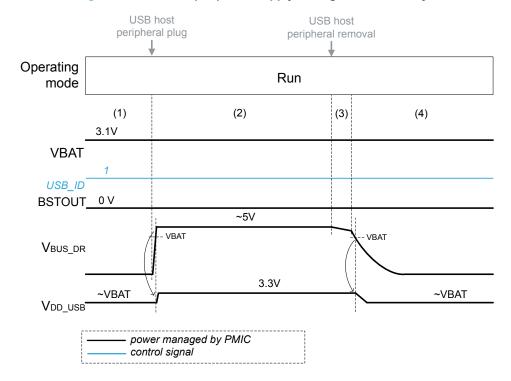

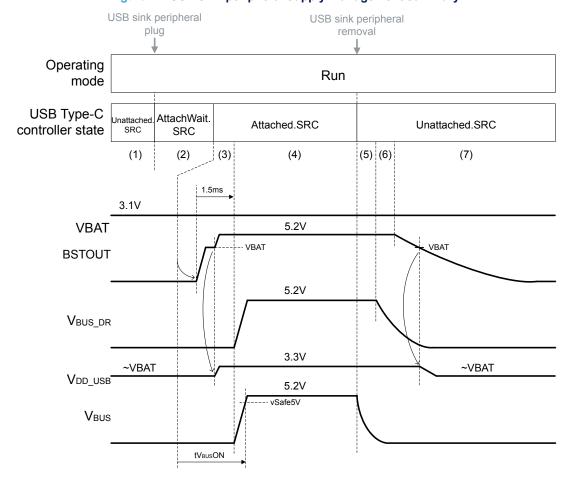

## 6.1.5 USB host peripheral supply management summary

The sequence in Figure 10 is dedicated to USB host peripheral management and provides a summary of Section 6.1.1 to Section 6.1.4 according to the implementation shown in Section 6.1 . For simplification, it is assumed that battery voltage is constant during the whole sequence (battery charging not shown). This can be a personal computer host for example.

- 1. The application is powered by a discharged battery (VBAT = 3.1 V) and is in Run operating mode. The STPMIC1BPQR is in Power-ON-main state. The STPMIC1BPQR PWR\_USB\_SW discharge pull down is initially enabled by software (see Section 6.1.3)

- 2. A USB host peripheral is plugged into the USB receptacle:

- VBUS\_DR rises (as VBUS voltage is provided by host peripheral) pulls both the STPMIC1BPQR VBUSOTG and STM32MP15x USBO\_VBUS up. Both signals can trigger an interrupt (see Section 6.1.1 ).

- b. Once the interrupt is caught by the software, the software initializes the STM32MP15x USB OTG controller in B-device mode (device mode) and initiates USB communication.

- c. Once VBUS\_DR is above VBAT, the STPMIC1BPQR LDO4 is powered from VBUS\_DR (see Section 6.1.4 ) and LDO4 output (VDD\_USB) returns to 3.3 V.

- d. The software disables the STPMIC1BPQR PWR\_USB\_SW discharge pull down (see Section 6.1.3 )

- 3. The USB host peripheral is unplugged from the USB receptacle:

- VBUS DR decreases slowly.

- b. Once VBUS\_DR is below a defined voltage threshold, the STPMIC1BPQR PWR\_USB\_SW (via the VBUSOTG pin) or the STM32MP15x USB OTG controller (via the USBO\_VBUS pin) triggers an interrupt (see Section 6.1.1 ).

- c. The software ends the USB B-device session.

- 4. The software enables the STPMIC1BPQR PWR USB SW discharge pull down:

- a. VBUS DR is tied low.

- b. Once VBUS\_DR is below VBAT, the STPMIC1BPQR LDO4 is powered back from VBAT and LDO4 output (VDD\_USB) returns to a value under 3.3 V. (see Section 6.1.4 ).

AN5260 - Rev 2 page 32/54

Figure 10. USB host peripheral supply management summary

AN5260 - Rev 2 page 33/54

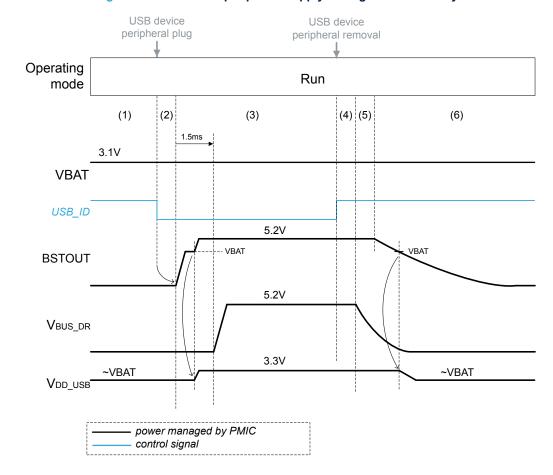

## 6.1.6 USB device peripheral supply management summary

The sequence in Figure 11 is dedicated to USB device peripheral management and provides a summary for Section 6.1.1 to Section 6.1.4 according to the implementation shown in Section 6.1 . For simplification, it is assumed that battery voltage is kept constant during the whole sequence (battery discharge not shown). This can be a USB mass storage dongle for example.

- 1. The application is powered by a discharged battery (VBAT = 3.1 V) and is in Run operating mode. The STPMIC1BPQR is in Power-ON-main state.