# Double output, isolated PSR Flyback converter for Smart Meter and Power Line Communication systems using VIPER267KDTR

### **Description**

The STEVAL-VP26K03F evaluation board implements a double output isolated flyback with primary side regulation (PSR), specifically designed to supply smart meter and PLC systems.

The evaluation board has been developed using the VIPER267KDTR offline high-voltage converter, which features a 1050 V avalanche-rugged power section, PWM operation at 60 kHz with frequency jittering for lower EMI, current limiting with 700 mA fixed set point, on-board soft-start, safe auto-restart after fault and low standby power.

The power supply provides 12 V at 700 mA<sub>rms</sub> (1 A peak) to the power line modem (PLM) and the analog circuitry, and 6 V at 200 mA to supply digital circuitry and other low voltage parts.

The power supply is designed to operate across a three-phase input mains from 50 to 290  $V_{AC}$ , but can also be connected to a single phase mains from 85 to 500  $V_{AC}$ .

Figure 1. STEVAL-VP26K03F evaluation board top

#### — RELATED LINKS -

The board can also be configured for SSR operation. Refer to STEVAL-VP26K02F

### 1 Features and specifications

Table 1. STEVAL-VP26K03F electrical specifications

| Parameter                                            | Min.               | Тур. | Max.                |

|------------------------------------------------------|--------------------|------|---------------------|

| Operative AC main input voltage (3-phase connection) | 50 V <sub>AC</sub> | -    | 290 V <sub>AC</sub> |

| Operative AC main input voltage (2-phase connection) | 85 V <sub>AC</sub> | -    | 498 V <sub>AC</sub> |

| Mains frequency                                      | 47 Hz              | -    | 63 Hz               |

| Output voltage 1 – V <sub>OUT1</sub>                 | 11 V               | 12 V | 16 V                |

| Output current 1 – IOUT1                             | 10 mA              | -    | 700 mA (rms)        |

| Output current 1 – 10011                             | -                  | -    | 1000 mA (peak)      |

| Output voltage 2 – V <sub>OUT2</sub>                 | 5.5 V              | 6 V  | 7 V                 |

| Output current 2 – I <sub>OUT2</sub>                 | 10 mA              | -    | 200 mA              |

| Maximum peak power                                   | -                  | -    | 13.2 W              |

| Maximum rms power                                    | -                  | -    | 9.6 W               |

| Efficiency at full load                              | -                  | 78%  | -                   |

| Ambient operating temperature                        |                    | -    | 85 °C               |

AN5375 - Rev 1 page 2/27

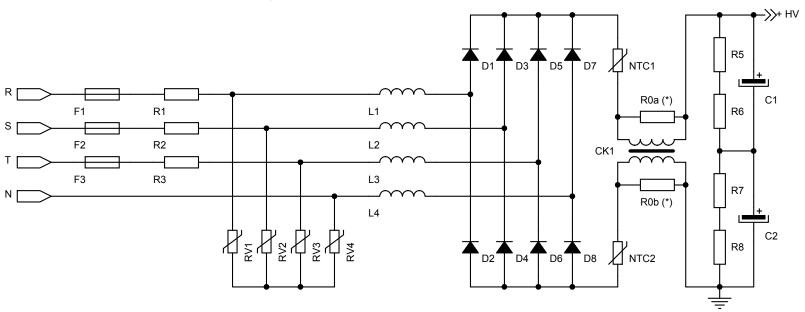

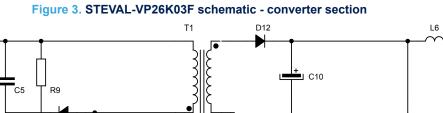

#### 1.1 **Schematic diagrams**

AN5375

Schematic diagrams

AN5375

Schematic diagrams

C15

C14

C13

C12 C20

C11

#### 1.2 Bill of materials

Table 2. STEVAL-VP26K03F bill of materials

| ltem | Q.ty | Ref.                                                                                | Part/Value                      | Description                                                     | Manufacturer    | Order code          |

|------|------|-------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------|-----------------|---------------------|

| 1    | 3    | R1, R2, R3                                                                          | 22 Ω, 1W, ±5%                   | Metal Oxide<br>Resistor, TH                                     | TE Connectivity | EP1W22RJ            |

| 2    | 4    | R5, R6, R7,<br>R8                                                                   | 1MΩ, 0.33W, ±5%                 | Resistor, 1206                                                  | Panasonic       | ERJP08J105V         |

| 3    | 1    | R9                                                                                  | 220 KΩ , 0.25W,<br>±5%          | Resistor, 1206                                                  | Panasonic       | ERJT08J224V         |

| 4    | 2    | R11 ,R21                                                                            | 10 KΩ, ±1%                      | Resistor, 0603                                                  | TE Connectivity | CRG0603F10K         |

| 5    | 2    | R0a, R0b,                                                                           | 0 Ω , 0.25W, ±1%                | Resistor, 0603                                                  | Vishay          | CRCW06030000Z0EAHP  |

| 6    | 1    | R12                                                                                 | 150 kΩ, ±1%                     | Resistor, 0603                                                  | Vishay          | CRCW0603150KFKEA    |

| 7    | 1    | R13                                                                                 | 43 KΩ, ±1%                      | Resistor, 0603                                                  | Vishay          | CRCW060343K0FKEA    |

| 8    | 1    | R22                                                                                 | 47Ω, 0.125W, ±1%                | Resistor, 0603                                                  | TE Connectivity | CRG0805F47R         |

| 9    | 1    | Rbl                                                                                 | 8.2 kΩ, 0.125W,<br>±1%          | Resistor, 0603                                                  | TE Connectivity | CRG0603F8K2         |

| 10   | 13   | R10, R14,<br>R15, R16,<br>R17, R18,<br>R19, R20,<br>C16, C22,<br>OPTO1,<br>IC2, CK1 | -                               | Not mounted                                                     | -               | -                   |

| 11   | 2    | C1, C2                                                                              | 68 μF, 400 Vcc -<br>105°C, ±20% | Electrolitic<br>Capacitor, TH<br>D=18 mm, H=25<br>mm, P=7.5 mm  | Rubycon         | 400BXC68MEFC18X25   |

| 12   | 1    | C5                                                                                  | 1 nF 630 Vdc, 630<br>Vdc, ±5%   | Multi layer capacitor, 1206                                     | TDK             | C3216C0G2J102J085AA |

| 13   | 2    | C7, C9                                                                              | 1 nf, 200 Vdc, ±5%              | Multi layer capacitor, 0603                                     | TDK             | C3216C0G2J102J085AA |

| 14   | 1    | C8                                                                                  | 47 μF, 35 Vdc,<br>±20%          | Electrolitic<br>Capacitor, H D=4<br>mm, H=7 mm,<br>P=1.5 mm     | Rubycon         | -                   |

| 15   | 2    | C10, C11                                                                            | 220 μF, 25 Vcc,<br>+105°C, ±20% | Electrolitic<br>Capacitor, TH<br>D=6.3 mm, H=11<br>mm, P=2.5 mm | Rubycon         | 35ZLH220MEFC8X11.5  |

| 16   | 3    | C6, C12,<br>C15                                                                     | 100nF, 25 Vcc,<br>±10%          | Multi layer capacitor, 0603                                     | KEMET           | C0603C104K3RACTU    |

| 17   | 1    | C13                                                                                 | 470 μF, 35 Vcc,<br>+105°C, ±20% | Electrolitic<br>Capacitor, TH<br>D=10 mm, H=12.5<br>mm, P=5 mm  | Rubycon         | 25ZLH470MEFC10X12.5 |

| 18   | 1    | C14                                                                                 | 100 μF, 35 Vcc,<br>+105°C, ±20% | Electrolitic<br>Capacitor, TH<br>D=6.3 mm, H=11<br>mm, P=2.5 mm | Rubycon         | 35ZLH100MEFC6.3X11  |

| 19   | 1    | C17                                                                                 | 2.2nF, 250 Vac                  | X1 Y2 Capacitor,<br>TH 8 mm X 5 mm,<br>P 7.5 mm                 | Murata          | DE2E3KY222MA2BM01F  |

AN5375 - Rev 1 page 5/27

| Item | Q.ty | Ref.                                 | Part/Value                               | Description                                                         | Manufacturer             | Order code           |

|------|------|--------------------------------------|------------------------------------------|---------------------------------------------------------------------|--------------------------|----------------------|

| 20   | 1    | C18                                  | 330 pF, 10 Vdc,<br>±5%                   | Multi layer capacitor, 0603                                         | Vishay                   | VJ0603A331JXBAC      |

| 21   | 1    | C19                                  | 100pF, 250 Vdc,<br>±5%                   | Multi layer capacitor, 0603                                         | TDK                      | CGA3E3C0G2E101J080AA |

| 22   | 1    | C20                                  | 1μF, 25 Vdc, ±10%                        | Multi layer capacitor, 0603                                         | Murata                   | GRM188C81E105KAADD   |

| 23   | 3    | F1, F2, F3                           | 2A                                       | Fuse, 10.1mm X<br>1.43 mm                                           | Schurter                 | 3403.0169.24         |

| 24   | 1    | T1                                   | LP 1.5 mH, out1<br>12V, out2 6V          | WURTH_75031813<br>5r00 Flyback<br>Transformer                       | Wurth Eleltronik         | 750318135            |

| 25   | 4    | L1, L2, L3,<br>L4                    | 1mH                                      | Inductor, TH, D<br>8mm, P 5mm, H<br>10mm                            | Wurth Elektronik         | 7447728102           |

| 26   | 1    | L6                                   | 3.3 μH / 33 mΩ,<br>3.23A                 | Inductor, Lu x La:<br>0,157 x 0,157"<br>(4,00 x 4,00 mm)            | Wurth Electronics<br>Inc | 74404043033A         |

| 27   | 2    | NTC1,<br>NTC2                        | 10 Ω                                     | PTC, TH 9 mm X 4 mm , P 5mm                                         | Murata                   | NTPA7100LBMB0        |

| 28   | 1    | Dz1                                  | 22 V, 22, 0.5W                           | Zener Diode, SOD<br>123                                             | ON Semiconductor         | MMSZ22T1G            |

| 29   | 4    | VR1, VR2,<br>VR3, VR4                | Vrms=275,<br>VDCmax=350V, ,W<br>max=155J | 275 Vac Metal<br>Oxide Varistor, TH<br>series 14, 16.5mm<br>X 4.5mm | Wurth Elektronik         | 820442711E           |

| 30   | 1    | Q1                                   | BC807, 45, 0.5,<br>HFE 30                | pnp Bipolar<br>Transistor, SOT23                                    | ON Semiconductor         | BC807-40LT3G         |

| 31   | 8    | D1, D2, D3,<br>D4, D5, D6,<br>D7, D8 | RGP02-20E-E3/54,<br>1800V                | High Voltage<br>Rectifier Diode, TH<br>Axial, Body 5.2 x<br>2.7     | Vishay                   | RGP02-20E-E3/54      |

| 32   | 1    | D9                                   | -                                        | Rectifier Diode,<br>SMA                                             | ON Semiconductor         | MRA4007T3G           |

| 33   | 1    | D10                                  | 150 V, 1 A                               | Schottky Diode,<br>SMA                                              | ST                       | STPS1150A            |

| 34   | 1    | D12                                  | 200 V, 10 A                              | Schottky Diode,<br>SMA                                              | ST                       | STPS2200UF           |

| 35   | 1    | D13                                  | 100 V, 1 A                               | Schottky Diode,<br>SMA                                              | ST                       | STPS1H100A           |

| 36   | 1    | IC1                                  | 1050 V                                   | SMPS IC                                                             | ST                       | VIPER267KDTR         |

| 37   | 2    | M1                                   | M.4 TH                                   | 2-way terminal block                                                | Phoenix Contact          | 1706785              |

| 38   | 1    | M2                                   | M.3 TH                                   | 3-way terminal block                                                | Phoenix Contact          | 1725669              |

| 39   | 4    | H1, H2, H3,<br>H4                    | 9.5 mm                                   | Hex spacers                                                         | Richco                   | HS 4 3               |

AN5375 - Rev 1 page 6/27

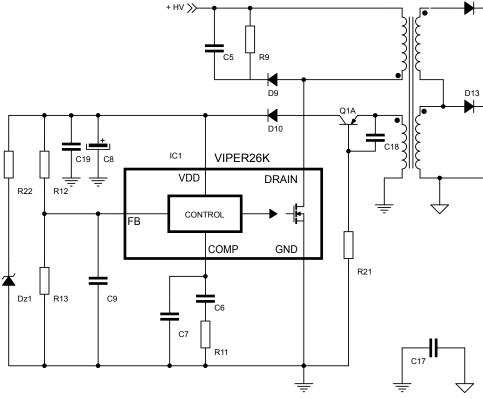

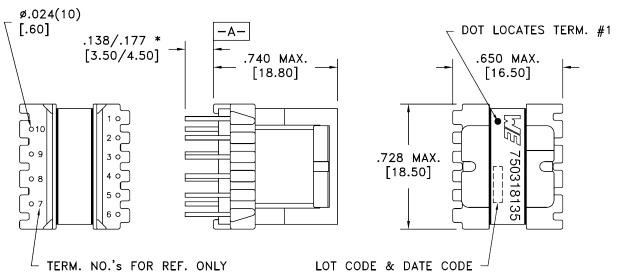

#### 1.3 Transformer

**Table 3. Transformer characteristics**

| Manufacturer                     | Wurth Elektonik                    |

|----------------------------------|------------------------------------|

| Part number                      | 750318135                          |

| Core                             | E16                                |

| Primary Inductance               | 1.5 mH ±10%                        |

| Saturation current               | 950 mA (20% roll-off from initial) |

| Leakage inductance               | 100 μH typ., 200 μH max.           |

| Primary-to-auxiliary turns ratio | 5.03 ±1%                           |

| Primary-to-sec1 turns ratio      | 10.94 ±1%                          |

| Primary-to- sec2 turns ratio     | 10.94 ±1%                          |

Figure 4. Dimensional drawing, pin placement (distances, bottom view) and electrical diagrams

Figure 5. Dimensional drawing and pin placement diagram (bottom, side and top view)

AN5375 - Rev 1 page 7/27

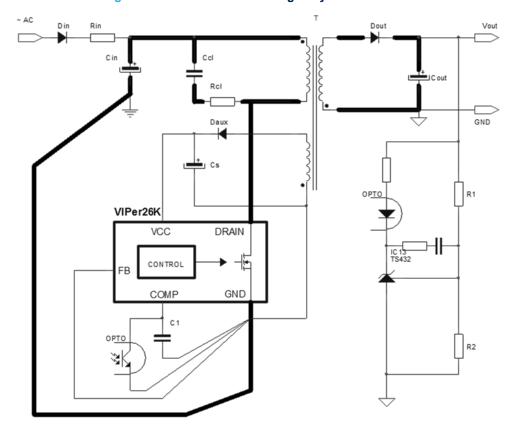

### 2 Circuit description

#### 2.1 Input stage and filtering

The input stage is designed for the power supply to sustain operation at up to  $500 \text{ V}_{AC}$ . It consists of three fuses (F1, F2 and F3) implemented to prevent catastrophic failure and two input NTCs to limit the inrush current of the capacitors during startup and to protect the three-phase bridge rectifier (BR). The total required resistance of the NTC is divided into two for safe operation of the NTC components without exceeding the allowed voltage rating across them.

The total bulk capacitance consists of two capacitors in series for a total voltage rating above the maximum operating rectified input voltage ( $730V_{DC}$  approx.); resistors R5 to R8 ensure equal voltage sharing between the capacitors.

Special care has been placed on filtering conducted converter noise to render powerline communication less sensitive to the switching power supply. Both differential and common mode filters have been implemented.

#### 2.2 Snubber network

A low cost RCD (R9-C5-D9) clamp is implemented for the snubber network to limit the leakage inductance voltage spike by dissipating the associated energy during MOSFET turn-off to ensure reliable power supply operation.

The 1050 B<sub>VDSS</sub> voltage of the VIPER26K means that further protection against input overvoltage using a parallel transil diode is not required.

The adoption of this low-cost clamp configuration helps to improve EMC performance through smooth drain voltage ringing slopes, and the absence of the transil eliminates a loop that could degrade EMI performance.

#### - RELATED LINKS

Appendix B Effect of ouptut LC post filter stage in flyback converters on page 20

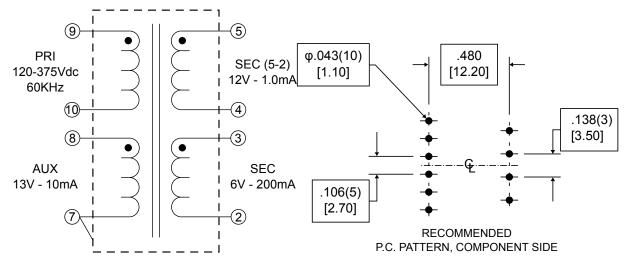

#### 2.3 HV converter

The core of the power supply is the VIPER267KDTR offline high-voltage converter with 1050 V avalanche-rugged power section with a maximum  $R_{DS(on)} \le 8.5 \Omega$ , and a current-mode 60 kHz fixed frequency PWM controller.

The device includes several features which considerably reduce the overall BoM cost and improve system reliability.

Control is achieved by adjusting the voltage on COMP pin, which transfers the output voltage information via the optocoupler. Capacitor C7 connected across the pin is used for appropriate loop compensation.

During normal operation, the  $V_{DD}$  pin is powered by the output of the auxiliary winding of the transformer, which is rectified by diode D10 and capacitor C8. Resistor R4 is used to filter the auxiliary spikes at turn-off, and limit voltage fluctuation on the pin. Capacitor C19 is used to filter any narrow voltage spikes entering the  $V_{DD}$  pin. A clamp network consisting of R22 and Dz1 is connected across the  $V_{DD}$  pin to avoid transient voltages exceeding the absolute maximum rating of the pin.

#### 2.4 Output stage

The secondary of the transformer is designed for a two-output option: the secondary windings are wound using a stack arrangement to improve the cross regulation of the non-regulated output.

The first secondary signal is rectified by diode D12 and filtered by output capacitor C13, and is designed to allow sufficient AC ripple capability to avoid component overheating. The L6-C14 post filter is used to further reduce the residual output ripple, while capacitors C15 and C21 further reduce the output switching noise.

The other secondary signal is rectified by diode D13 and capacitor C11.

The output voltage is sensed by voltage divider R12 and R13 and compared with the internal 3.3 V reference of the integrated error amplifier; its output is then converted via the internal OTA into a current control signal for the primary PWM IC.

AN5375 - Rev 1 page 8/27

### 3 Performance data

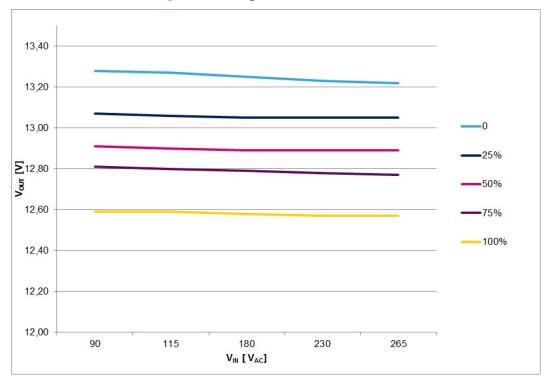

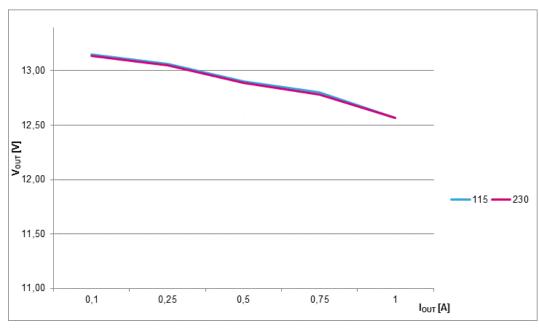

### 3.1 Output voltage characteristics

The line and load regulation of the board is measured at the PCB output connectors for both 115  $V_{AC}$  and 230  $V_{AC}$ .

Figure 6. Line regulation at different loads

AN5375 - Rev 1 page 9/27

### 3.2 Efficiency and light load measurements

The efficiency and the light load consumption of the converter are measured at nominal input voltages (115  $V_{AC}$  and 230  $V_{AC}$ ).

Table 4. Efficiency at typical and maximum loads

| Output condition                | Efficiency          |                     |  |

|---------------------------------|---------------------|---------------------|--|

| Output condition                | 115 V <sub>AC</sub> | 230 V <sub>AC</sub> |  |

| 12 V at 700 mA / 6 V at 200 mA  | 77.15%              | 79.92%              |  |

| 12 V at 1000 mA / 6 V at 200 mA | 72.37%              | 76.45%              |  |

AN5375 - Rev 1 page 10/27

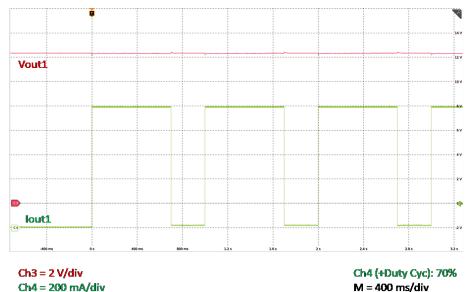

### 4 Typical waveforms

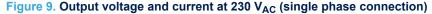

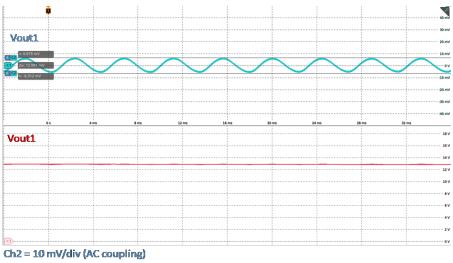

In TX mode, the load on output 1 changes from 10 to 1000 mA with a 1-Hz repetition rate and 70% duty cycle. Output 2 is loaded at typical values (200 mA).

During PLM operation, it is important that the output voltage remains regulated within specification limits to ensure correct operation of the PLM power amplifier (see Figure 8 and Figure 9). The output voltage is quite stable and clean with no abnormal oscillation during load changes and the steady-state values are within specification by very good margins.

Figure 8. Output voltage and current at 115  $V_{AC}$  (single phase connection)

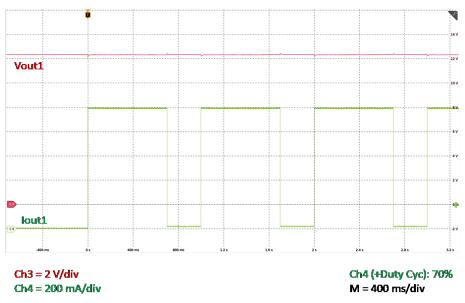

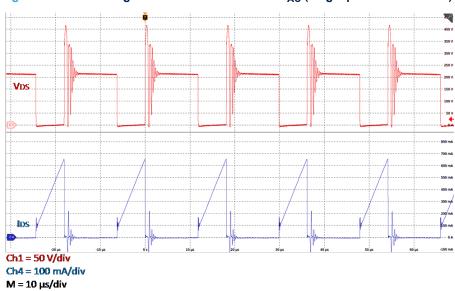

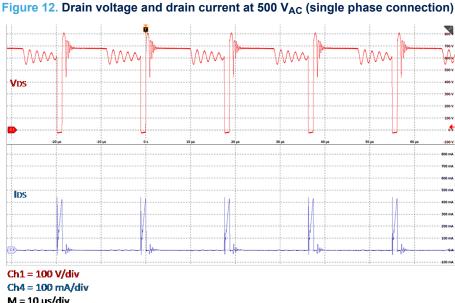

The drain voltage and the drain current waveforms are reported for the two nominal input voltages and for  $500V_{AC}$  (see Figure 10 to Figure 12).

AN5375 - Rev 1 page 11/27

Figure 10. Drain voltage and drain current at 115  $V_{AC}$  (single phase connection)

Ch1 = 100 V/div Ch4 = 100 mA/div M = 10 µs/div

AN5375 - Rev 1 page 12/27

$M = 10 \mu s/div$

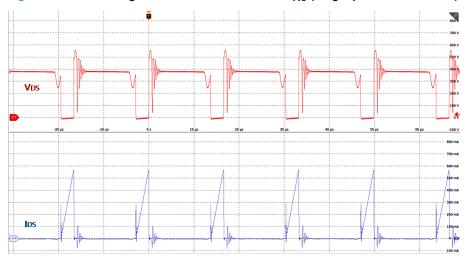

The output voltage ripple at 12 V output at nominal input voltage and full load is also measured (see Figure 13). It must be very low in order to ensure appropriate sensitivity during PLM operation . The measured value is extremely low at around 0.1% of the nominal output voltage.

Figure 13. Low frequency ripple at 230 V<sub>AC</sub> (single phase connection)

Ch3 = 2 V/div

M = 4 ms/div

AN5375 - Rev 1 page 13/27

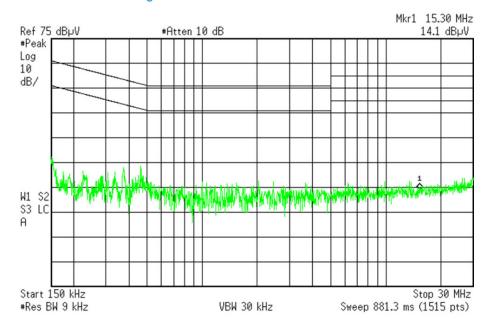

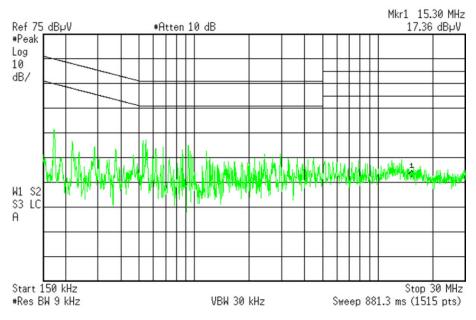

#### 5 Noise measurements

The pre-compliance tests for conducted noise emissions as per EN55022 (Class B) European normative were performed using a Quasi-Peak detector and an Average detector of the conducted art nominal mains voltage, and compared with the associated limits.

Figure 14 and Figure 15 show that the measured results are well within their respective limits by a very good margin.

Figure 14. LINE conducted disturbance

AN5375 - Rev 1 page 14/27

### 6 Conclusion

We tested our double output isolated PSR flyback converter design based on the VIPER267KDTR, and we demonstrated that the input filter setup, its compliance with the European standards for smart metering and PLC applications, as well as for Electromagnetic compatibility, and the overall performance of the board render it suitable for use in Smart Meter and PLC systems.

AN5375 - Rev 1 page 15/27

#### Appendix A CCM flyback converter transfer function

The control-to-output transfer function of the flyback converter in CCM,  $G_{\mathcal{VC}}(s)$  , is given by the approximation:

$$G_{VC}(s) \approx H_O \cdot \frac{\left(1 + \frac{s}{\omega_{Z1}}\right) \cdot \left(1 - \frac{s}{\omega_{Z2}}\right)}{1 + \frac{s}{\omega_{P1}}}$$

(1)

Gain, poles and zero are defined below:

$$H_0 = \frac{n \cdot R_0}{H_{COMP}} \cdot \frac{1 - D}{1 + D} \tag{2}$$

$$\omega_{Z1} = \frac{1}{R_C \cdot C_O} \tag{3}$$

$$\omega_{Z2} = \frac{n^2 \cdot (1 - D)^2 \cdot R_O}{D \cdot L} \tag{4}$$

$$\omega_{P1} = \frac{1+D}{R_O \cdot C_O} \tag{5}$$

#### A.1 CCM flyback type-2 compensator design

To compensate the CCM flyback, we use a type-2 compensator featuring the integrator effect that provides high DC gain to minimize static error, as well as a pole-zero pair to boost the phase according to the phase margin target.

The compensator is determined using a manual pole-zero placement technique in which the zero is placed in the vicinity of the power stage dominant pole to cancel its effect and the pole position is adjusted to achieve the required phase margin.

Follow the procedure below to design compensation with a type 2 compensator:

**Step 1.** Select the crossover frequency  $f_C$  and the phase margin  $\Phi_m$ :

For CCM flyback, the crossover frequency must be selected as low as possible with respect to the RHP zero  $\omega_{Z2}$  in order to limit the phase degradation that it introduces.

As a general rule, you should set  $f_{\mathcal{C}}$  to below 20% of the RHP zero.

Step 2. Evaluate the gain and phase of the plant at crossover frequency:

$$G_{vc(f_C)} = |G_{vc}(2 \cdot \pi \cdot f_C)| \tag{6}$$

$$\Phi_{vc(f_C)} = arg[G_{vc}(2 \cdot \pi \cdot f_C)] \tag{7}$$

**Step 3.** Design the compensator to have following gain and phase (at  $f_{\mathcal{C}}$ ):

The compensated open-loop gain must attain unit gain at  $f_{\mathcal{C}}$ , with the required phase margin.

$$G_{\mathcal{C}(f_{\mathcal{C}})} = |G_{\mathcal{C}}(2 \cdot \pi \cdot f_{\mathcal{C}})| = \frac{1}{G_{\mathcal{VC}(f_{\mathcal{C}})}}$$

$$\tag{8}$$

$$\Phi_{C}(f_{C}) = arg[G_{C}(2 \cdot \pi \cdot f_{C})] = 90 - 180 + \Phi_{m} - \Phi_{vc}(f_{C})$$

(9)

Step 4. Cancel the pole of the plant  $f_{P(p)}$  by placing the zero of the compensator  $f_{Z(c)}$  in the neighborhood (  $\alpha = 1$  to 5):

$$f_{Z(c)} = \frac{\omega_{Z(c)}}{2 \cdot \pi} = \alpha \cdot f_{P(p)} \tag{10}$$

Step 5. Place the pole of the compensator to boost the phase and to obtain the desired phase margin:

$$f_{P(c)} = \frac{f_C}{tan\left[tan^{-1}\left(\frac{f_C}{f_{Z(c)}}\right) - \Phi_c(f_C)\right]}$$

(11)

AN5375 - Rev 1 page 16/27

**Step 6.** Calculate the gain  $G_{co}$ :

$$G_{co} = G_{c(f_C)} \cdot \frac{\omega_C \cdot \sqrt{1 + \left(\frac{f_C}{f_{P(c)}}\right)^2}}{\sqrt{1 + \left(\frac{f_C}{f_{Z(c)}}\right)^2}}$$

(12)

$G_C(s)$  is thus determined.

#### A.2 Compensator implementation

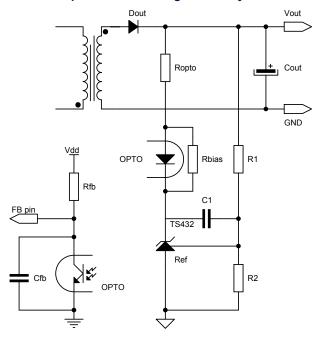

Figure 16 shows the complete schematic arrangement for the type-2 error amplifier in secondary side regulation (SSR). The resistors  $R_1$  and  $R_2$  are used to define the output voltage setpoint. The resistor  $R_{OPTO}$  is used to bias the emitter, while the resistor  $R_{BIAS}$  is used to provide the minimum biasing current to the reference voltage IC. The capacitors  $C_1$  and  $C_{FB}$  are used for the compensation, even if the other components also affect the overall compensator transfer function.

Figure 16. Secondary feedback implementation using secondary reference voltage and optocoupler

The transfer function of the compensator can be expressed as:

$$G_{C}(s) = \frac{CTR \cdot R_{FB}}{R_{OPTO}} \cdot \frac{1 + \frac{1}{s \cdot R_{1} \cdot C_{1}}}{1 + s \cdot R_{FB} \cdot (C_{FB} + C_{OPTO})}$$

$$\tag{13}$$

In the equation, capacitor  $C_{OPTO}$  is the intrinsic capacitor across the collector that introduces a pole in the transfer function and limits the frequency response. As this pole becomes part of the controller transfer function, specific test measurements are required to determine the correct value as close as possible to the real operating conditions of the selected optocoupler.

Component selection is based on the procedure shown below.

**Step 1.** First calculate the value of the resistor R<sub>BIAS</sub>.

The purpose of this resistor is to provide the minimum bias current to the reference IC necessary for correct operation. Considering that the forward voltage of the opto-diode is almost constant (typically  $\approx$  1 V), the value of  $R_{BIAS}$  is simply given by:

$$R_{BIAS} \le \frac{V_F}{I_{BIAS}} \tag{14}$$

AN5375 - Rev 1 page 17/27

**Step 2.** The next step is the selection of  $R_1$ .

The value must be high enough to minimize the residual losses across the output, but low enough to ensure that the input current of the REF pin of the reference IC is negligible compared with the current across  $R_1$  itself: a general rule is to set the current across  $R_1$  30 to 50 higher than the REF input current.

**Step 3.** Select resistor R<sub>2</sub> to define the output voltage set-point:

$$R_2 = R_1 \cdot \frac{V_{REF}}{V_{OUT} - V_{REF}} \tag{15}$$

**Step 4.** Calculate the value of capacitor  $C_1$  to fix the zero  $f_{Z(c)}$ :

$$C_1 = \frac{1}{2\pi \cdot R_1 \cdot f_{ZC}} \tag{16}$$

**Step 5.** Set the value of  $R_{OPTO}$  to fix the mid-band gain  $G_{co}$ :

$$R_{OPTO} = \frac{CTR \cdot R_{FB}}{G_{CO}} \tag{17}$$

**Step 6.** Check that  $R_{OPTO}$  satisfies the following equation:

This is to ensure the minimum current through the optodiode to properly drive the FB pin with the current  ${\rm I}_{FB}$ , ensuring the full dynamic of the pin.

$$R_{\text{OPTO}} \le \frac{V_{\text{OUT}} - V_F - V_{\text{REF}}}{\frac{I_{\text{FB}}}{\text{CTR}} + \frac{V_F}{R_{\text{BIAS}}}}$$

$$\tag{18}$$

Step 7. Set the value of  $C_{FB}$  to fix the proper phase boost of the compensator:

$$C_{FB} = \frac{1}{2\pi \cdot R_{FB} \cdot f_{PC}} - C_{OPTO}$$

(19)

The design of  $G_{\mathbb{C}}(s)$  is now ready.

#### A.3 Compensator implementation of PSR

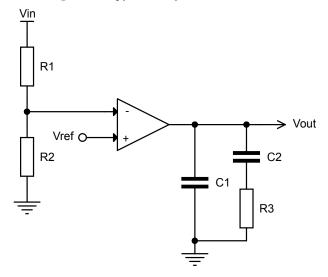

A type-2 compensator with OTA is used for PSR, as shown in the following figure.

Figure 17. Type 2 compensator with OTA

The transfer function of the compensator can be expressed as:

AN5375 - Rev 1 page 18/27

$$G_C(s) = \frac{N_{AUX}}{N_{SEC}} \cdot \frac{R_{EA} \cdot R_2 \cdot g_m}{R_1 + R_2} \cdot \frac{1 + s \cdot R_3 \cdot C_2}{\left(1 + s \cdot R_0 \cdot C_2\right) \cdot \left[\left[1 + s \cdot R_3 \cdot \left(C_1 + C_{EA}\right)\right]\right]} \tag{20}$$

The terms  $C_{EA}$  and  $R_{EA}$  are the output capacitance and the output resistance of the error amplifier, which are 400 pF and 1.1 M $\Omega$  respectively in the Viper26K.

The first component to be chosen is the resistor  $R_1$ , which must be high enough to render the current offset entering the inverting pin negligible, but low enough so that other compensation components are not too large. Resistor  $R_2$  is fixed to set the DC operating point of the loop. Both  $R_1$  and  $R_2$  play a role in the definition of the gain of the compensator.

The remaining components can be calculated.

$$c_1 = \frac{f_{Z1}}{f_{P1}} \cdot \frac{R_2 \cdot g_m}{G_{co} \cdot (R_1 + R_2)} - c_{EA}$$

(21)

$$c_2 = \frac{R_2 \cdot g_m}{G_{co} \cdot (R_1 + R_2)} - (C_1 + C_{EA})$$

(22)

$$R_3 = \frac{1}{2\pi \cdot f_{Z1} \cdot c_2} \tag{23}$$

AN5375 - Rev 1 page 19/27

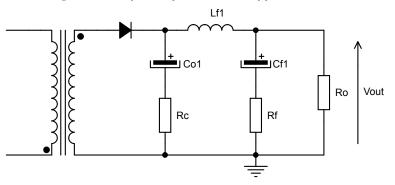

#### Appendix B Effect of output LC post filter stage in flyback converters

Large capacitors are usually used in flyback converters to build the output filter, and it is important to factor in the RMS ripple rating and the parasitic resistance ESR when determining the size of the capacitor to satisfy the output ripple specification.

When the requirement of the ripple is very tight, a simple low cost LC filter can be used to attenuate the ripple to the desired level instead of using a large number of capacitors that increase the cost.

Figure 18. Output LC post filter for ripple reduction

Although this solution is very simple and cost effective, it changes the behavior of the plant and extra care must be placed to deal with the compensation design.

Assuming that  $c_0$  is much larger than  $c_F$ , the total transfer function of the plant in presence of the LC filter can be expressed as:

$$G'_{vc}(s) = G_{vc}(s) \cdot \frac{1 + \frac{s}{\omega_{ZF}}}{1 + \frac{s}{\omega_F \cdot Q_F} + \left(\frac{s}{\omega_F}\right)^2}$$

(24)

Where:

$$\omega_F = \frac{1}{\sqrt{L_F \cdot C_F}} \tag{25}$$

$$Q_F = \frac{1}{\frac{1}{R_O} \cdot \sqrt{\frac{L_F}{C_F}} + (R_F + R_C) \cdot \sqrt{\frac{C_F}{L_F}}}$$

(26)

Where  $G_{VC}(s)$  is the transfer function of the plant without the filter, given in Eq. (1).

The presence of the LC output post filter introduces a further zero and a pair of poles in the transfer function. This causes a peak at frequency  $\omega_F/2\pi$  to appear in the amplitude diagram and a sudden 180° reduction of the phase to occur at the same frequency. Therefore, when you use an LC post filter, it is necessary to design its resonance frequency well above the crossover frequency to keep the resonance peak outside the converter band and to avoid eroding the phase margin or going as far as making the system unstable.

In our board, the LC filter in designed to have the pole pair at frequency  $f_F = 8.76kHz$ , with a quality factor equal to  $Q_F = 0.801$ , ensuring negligible phase margin erosion at the crossover frequency.

#### - RELATED LINKS -

2.2 Snubber network on page 8

AN5375 - Rev 1 page 20/27

#### Appendix C Layout guidelines and design recommendations

An appropriate PCB layout is essential for the correct operation of any switch-mode converter. It ensures the delivery of clean signals to the IC and higher immunity to external and switching noise, as well as reducing radiated and conducted electromagnetic interference, all of which help a given solution satisfy EMC requirements. Below are some general concepts to keep in mind when designing SMPS circuit layouts.

Separate signal and power tracks:

- Traces carrying signal currents should generally be run at a distance from other tracks carrying pulsed currents or with rapidly changing voltages.

- Signal ground traces should be connected to the IC signal ground, GND, using a single "star point", placed close to the IC.

- Power ground traces should be connected to the IC power ground, GND.

- The compensation network should be connected to the COMP, maintaining the trace to GND as short as

possible.

- In two-layer PCBs, it is a good practice to route signal traces on one PCB side and power traces on the other side.

Filter sensitive pins and crucial points on the circuit:

- A small high-frequency bypass capacitor to GND might be useful to get a clean bias voltage for the signal part of the IC and protect the IC itself during EFT/ESD tests.

- A low ESL ceramic capacitor (a few hundred pF up to  $0.1~\mu F$ ) should be connected across VCC and GND, placed as close as possible to the IC.

- With flyback topologies, when the auxiliary winding is used, it is suggested to connect the VCC capacitor on the auxiliary return and then to the main GND using a single track.

Keep power loops as confined as possible:

- Minimize the area circumscribed by current loops where highly pulsed currents flow in order to reduce its

parasitic self-inductance and the radiated electromagnetic field; this will greatly reduce the electromagnetic

interferences produced by the power supply during the switching.

- In a flyback converter the most critical loops are:

- The one with the input bulk capacitor, the power switch and the power transformer

- the one with the snubber.

- the one with the secondary winding, the output rectifier and the output capacitor.

- In a buck converter the most critical loop is:

- The one with the input bulk capacitor, the power switch, the power inductor, the output capacitor and the free-wheeling diode.

Reduce line lengths as any wire will act as an antenna:

- With the very short rise times exhibited by EFT pulses, any antenna has the capability of receiving high voltage spikes. Shorter lines reduce the level of radiated energy received and lower the spikes resulting from electrostatic discharges. This will also keep both resistive and inductive effects to a minimum.

- All traces carrying high currents, especially if pulsed (tracks of the power loops), should be as short and wide

as possible.

#### Optimize track routing:

- as levels of pickup from static discharges are likely to be greater closer to the extremities of the board, it is

wise to keep any sensitive lines away from these areas.

- Input and output lines will often need to reach the PCB edge at some stage, but they can be routed away from the edge as soon as possible where applicable.

- Since vias are considered inductive elements, they should be kept to a minimum in signal paths and avoided in power paths.

Improve thermal dissipation:

- An adequate copper area must be provided under the DRAIN pins to dissipate heat

- It is not recommended to place large copper areas on the GND.

Finally, in order to improve immunity against fast transient and capacitive noise injection, since pin number 4 is mechanically connected to the controller die pad of the frame, it is highly recommended to connect it to GND.

AN5375 - Rev 1 page 21/27

Figure 19. Recommended routing of flyback converter

AN5375 - Rev 1 page 22/27

### **Revision history**

Table 5. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 20-Sep-2019 | 1       | Initial release. |

AN5375 - Rev 1 page 23/27

### **Contents**

| 1   | Feat       | ures and specifications                                       | 2          |

|-----|------------|---------------------------------------------------------------|------------|

|     | 1.1        | Schematic diagrams                                            | 3          |

|     | 1.2        | Bill of materials                                             | 5          |

|     | 1.3        | Transformer                                                   | 6          |

| 2   | Circ       | uit description                                               | 8          |

|     | 2.1        | Input stage and filtering                                     | 8          |

|     | 2.2        | Snubber network                                               | 8          |

|     | 2.3        | HV converter                                                  | 8          |

|     | 2.4        | Output stage                                                  | 8          |

| 3   | Perf       | ormance data                                                  | 9          |

|     | 3.1        | Output voltage characteristics                                |            |

|     | 3.2        | Efficiency and light load measurements                        | 10         |

| 4   | Турі       | cal waveforms                                                 | 11         |

| 5   | Nois       | se measurements                                               | 14         |

| 6   | Con        | clusion                                                       | 15         |

| Apı | endix      | A CCM flyback converter transfer function                     | 16         |

|     | <b>A.1</b> | CCM flyback type-2 compensator design                         | 16         |

|     | <b>A.2</b> | Compensator implementation                                    | 17         |

|     | <b>A.3</b> | Compensator implementation of PSR                             | 18         |

| Apı | pendix     | B Effect of output LC post filter stage in flyback converters | 20         |

| Apı | endix      | C Layout guidelines and design recommendations                | <b>2</b> 1 |

| Rev | ision      | history                                                       | 23         |

## **List of figures**

| Figure 1.  | STEVAL-VP26K03F evaluation board top                                                | . 1 |

|------------|-------------------------------------------------------------------------------------|-----|

| Figure 2.  | STEVAL-VP26K03F schematic - input section                                           | . 3 |

| Figure 3.  | STEVAL-VP26K03F schematic - converter section                                       | . 4 |

| Figure 4.  | Dimensional drawing, pin placement (distances, bottom view) and electrical diagrams | . 7 |

| Figure 5.  | Dimensional drawing and pin placement diagram (bottom, side and top view)           | . 7 |

| Figure 6.  | Line regulation at different loads                                                  | . 9 |

| Figure 7.  | Load regulation at 115 V <sub>AC</sub> and 230 V <sub>AC</sub>                      | . 9 |

| Figure 8.  | Output voltage and current at 115 $V_{AC}$ (single phase connection)                | 11  |

| Figure 9.  | Output voltage and current at 230 V <sub>AC</sub> (single phase connection)         | 11  |

| Figure 10. | Drain voltage and drain current at 115 V <sub>AC</sub> (single phase connection)    | 12  |

| Figure 11. | Drain voltage and drain current at 230 V <sub>AC</sub> (single phase connection)    | 12  |

| Figure 12. | Drain voltage and drain current at 500 V <sub>AC</sub> (single phase connection)    | 13  |

| Figure 13. | Low frequency ripple at 230 V <sub>AC</sub> (single phase connection)               | 13  |

| Figure 14. | LINE conducted disturbance                                                          | 14  |

| Figure 15. | NEUTRAL conducted disturbance                                                       | 14  |

| Figure 16. | Secondary feedback implementation using secondary reference voltage and optocoupler | 17  |

| Figure 17. | Type 2 compensator with OTA                                                         | 18  |

| Figure 18. | Output LC post filter for ripple reduction                                          | 20  |

| Figure 19. | Recommended routing of flyback converter                                            |     |

|            |                                                                                     |     |

AN5375 - Rev 1 page 25/27

### **List of tables**

| Table 1. | STEVAL-VP26K03F electrical specifications | 2  |

|----------|-------------------------------------------|----|

| Table 2. | STEVAL-VP26K03F bill of materials         | 5  |

| Table 3. | Transformer characteristics               | 7  |

| Table 4. | Efficiency at typical and maximum loads   | 10 |

| Table 5. | Document revision history                 | 23 |

AN5375 - Rev 1 page 26/27

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2019 STMicroelectronics - All rights reserved

AN5375 - Rev 1 page 27/27