## SPC58EHx/SPC58NHx OctalSPI HyperBus

#### Introduction

Nowadays the HyperBus interface technology offers many advantages supporting both legacy and many new features available inside the memory devices. These are for enhancing the overall performance e.g. Single/Double Data Rate (SDR/DDR), simplifying the design (due to low-pin usage) and reducing the global system cost.

To meet the growing requests in the automotive context about the integration of high-speed memories, STMicroelectronics offers the SPC58EHx/SPC58NHx micro-controller family that embeds two OctalSPI interfaces.

These interfaces enable the connection of the OctalSPI and HyperBus high-speed volatile and non-volatile memories available in the market and automotive graduated.

The OctoSPI's memory-mapped mode also allows to access to the external memories as if they were internal ones.

This application note documents how to setup the OctalSPI controllers inside the SPC58EHx/SPC58NHx micro-controller. It provides generic information about the protocols and literature to enter in the topic.

This document aims at explaining how to configure both OctalSPI instances in order to write and read HyperBus memories (HyperRAM and HyperFLASH).

It also describes some typical use cases to use the OctoSPI interface and providing some practical examples on how to use the interface depending on the type of the targeted memory.

This application is written by using SPC5Studio (tool is available at the following URL: https://www.st.com/en/development-tools/spc5-studio.html).

## 1 OctalSPI introduction

The OctoSPI is a serial interface which allows the communication on 8 data lines between the micro-controller and an external memory.

The OctoSPI provides a flexible hardware interface, which enables the support of multiple hardware configurations. It supports the Single-SPI (traditional SPI), Dual-SPI, Quad-SPI, Dual Quad-SPI and Octal-SPI.

The SPC58EHx/SPC58NHx OctalSPI has several features:

- Three functional modes: indirect, status-polling, and memory-mapped.

- Read and write support in the memory-mapped mode.

- Supports for single, dual, quad and octal communications.

- SDR and DTR support. Latter is supported and validated on this product.

- Data strobe support.

- Fully programmable opcode.

- Fully programmable frame format.

- · HyperBus support.

- Integrated FIFO for reception and transmission.

- 8, 16, and 32-bit data accesses are allowed.

- DMA channel for indirect mode operations.

- · Interrupt generation on FIFO threshold, timeout, operation complete, and access error.

This application note is focused on HyperBUS in DDR mode according to the Microcontroller requirements and on Cypress memories.

Note: for additional information refer to the "Octo-SPI" chapter inside the Microcontroller reference manual (see Section Appendix C Reference documents).

#### 1.1 OctalSPI protocol and operating modes

The OctoSPI interface can operate in two different low-level protocols:

- Regular command mode.

- HyperBus frame format.

Each protocol supports three operating modes:

- Indirect mode.

- Memory-mapped mode.

- · Status-polling mode.

## 1.1.1 Regular command mode

The regular-command mode is the classical frame format where the OctoSPI communicates with the external memory device by using commands; each command can include up to five phases and, at least, one of the five phases must be present. The interface provides a fully programmable frame support.

#### 1.1.2 HyperBUS mode

The OctoSPI supports the HyperBus protocol which enables the communication with HyperRAM and HyperFlash memories

The HyperBus has a Double Data Rate (DDR) interface where two data-bytes per clock cycle are transferred over the DQ input/output (I/O) signals, leading to high read and write throughputs.

Note: for additional information on HyperBus interface operation, refer to the HyperBus specification (see Section Appendix C Reference documents).

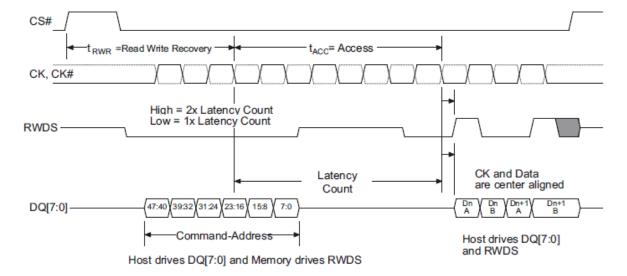

The HyperBus frame is composed of two phases:

- Command/address phase (CA).

- Data phase.

AN5524 - Rev 2 page 2/40

On the command/address phase, the HyperRAM memory will use the read-recovery time (RWDS) to understand if an additional initial access latency has to be inserted.

The OctoSPI peripheral can be configured in the following HyperBus modes:

- HyperBus memory mode: to allow the read/write access from/to the HyperBus memory.

- HyperBus register mode: to access to the memory device register space.

See Section Appendix A HyperBus timing for timing considerations.

## 1.2 OctalSPI operating modes

#### 1.2.1 Indirect mode

The indirect mode is used either for both HyperBus and regular-command protocols.

The commands are started by writing to the OCTOSPI registers and the data is transferred by writing or reading the data registers.

Typically, this mode is adopted to configure the external memory or resetting/erasing a HyperFLASH device. In the next chapters, this mode is implemented, and related examples are provided on both HyperRAM and HyperFLASH cases but only on the supported HyperBus mode.

## 1.2.2 Memory-mapped mode

The external memory device is seen as an internal one, but no more than 256 MB can be addressed in this architecture. The MCU can also execute code from the external memory. The application shows how to configure and debug this mode.

The memory mapped regions for both OctalSPI instances are reported in Table 1. OctalSPI memory map.

#### 1.2.3 Status polling mode

This feature is used to avoid the polling made by the software when, for example, the memory has been configured or when the ongoing operation (like FLASH programming/erasing) is completed. In automatic-polling mode, in fact, the OctoSPI hardware can periodically read the status and data generating an interrupt on a matching flag.

AN5524 - Rev 2 page 3/40

# SPC58EHx/SPC58NHx OctalSPI mapping

Each instance has its own chip select. The below table indicates the memory map layout:

Table 1. OctalSPI memory map

| Instance   | Description          | Address space            |  |  |  |  |

|------------|----------------------|--------------------------|--|--|--|--|

|            | Memory mapped        | 0x70000000 - 0x7FFF_FFF  |  |  |  |  |

| OctalSPI 1 | Controller Registers | 0x80000000 - 0x8000_03FF |  |  |  |  |

|            | Delay Block          | 0x80000400 - 0x8000_0407 |  |  |  |  |

|            | Memory mapped        | 0x60000000 - 0x6FFF_FFF  |  |  |  |  |

| OctalSPI 2 | Controller Registers | 0x80001000 - 0x800013FF  |  |  |  |  |

|            | Delay Block          | 0x80001400 - 0x80001407  |  |  |  |  |

The two OctalSPI share the same data lines to reduce the number of signals and a dedicated IO manager is used to mux them.

The IO manager is mapped at 0x80002000 - 0x8000200B. For full description point to the micro-controller reference manual.

AN5524 - Rev 2 page 4/40

## 3 OctalSPI clock selection

The CGM registers  $CGM\_AC14\_DC1$  (Aux Clock 14 Divider Configuration 1) and  $CGM\_AC14\_SC$  (Aux Clock 14 Select Control) have to be configured to provide the right clock to the controllers.

CGM\_AC14\_SC.SELCTL

CGM\_AC14\_DC0

CMU\_15

MMC\_CLK

CGM\_AC14\_DC1

CMU\_16

OCTSPI\_CLK

Figure 1. OCTSPI\_CLK GCM selecion

The  $OCTSPI\_CLK$  is configured to 200 MHz (from PLL); a pre-scaler is adopted later by programming the controller registers (see Figure 3. OctalSPI prescaler selection (200 / 2 = 100 MHz) ) to obtain 100 MHz, this is the default clock in this application for both instances.

Calculated Clock Points XOSC 40000000 IRC 16000000 PLL0-IN 40000000 PLL0-VCO 800000000 PLL0-PHI 40000000 200000000 PLL0-PHI1 PLL1-IN 40000000 PLL1-VCO 800000000 PLI1-PHI0 200000000 SYSCLK 200000000 CORE CLK 200000000 HPBM\_CLK 100000000 FBRIDGE\_CLK PBRIDGE\_CLK 50000000 200000000 PFBRIDGE\_CLK 100000000 SARADC\_CLK 5000000 EMIOS\_CLK 50000000 FRAY\_CLK 20000000 I2S\_CLK 20000000 SYSCLK0\_CLK RTC CLK 32000 0 CANCLK0\_CLK 8000000 PIT\_RTI\_CLK 8000000 CANCLK1\_CLK 8000000 DSPI\_CLK0 50000000 DSPI\_CLK1 50000000 LIN\_CLK0 100000000 LIN CLK1 100000000 PER\_CLK0 50000000 CANCLK2\_CLK 8000000 MMC\_CLK 40000000 OCTSPI\_CLK 200000000 PER\_CLK1 50000000

Figure 2. Application clock details (SPC5Studio wizard)

AN5524 - Rev 2 page 5/40

Figure 3. OctalSPI prescaler selection (200 / 2 = 100 MHz)

|                        | •            | ,                                              |

|------------------------|--------------|------------------------------------------------|

| ⊕ OctalSPI - Octal Ser |              |                                                |

| CR 30000009            | EN           | 1: OCTOSPI is enabled                          |

|                        | ABORT        | 0: No abort requested                          |

|                        | DMAEN        | 0                                              |

|                        | TCEN         | 1                                              |

|                        | DQM          | 0: Dual-quad mode disabled                     |

|                        | FSEL         | 0                                              |

|                        | FTHRES       | 0                                              |

|                        | TEIE         | 0: Interrupt disabled                          |

|                        | TCIE         | 0: Interrupt disabled                          |

|                        | FTIE<br>SMIE | 0: Interrupt disabled<br>0: Interrupt disabled |

|                        | TOIE         | 0: Interrupt disable                           |

|                        | APMS         | 0                                              |

|                        | PMM          | Ŏ                                              |

|                        | FMODE        | 3: Memory-mapped mode                          |

| DCR1 04180000          |              | 0                                              |

|                        | FRCK         | 0: CLK is not free running                     |

|                        | RESRVED      | 00                                             |

|                        | CSHT         | 0                                              |

|                        | DEVSIZE      | 24                                             |

|                        | MTYP         | 4_                                             |

| DCR2 00000001          | PRESCALER    | 01                                             |

| I                      | WRAPSIZE     | 0                                              |

AN5524 - Rev 2 page 6/40

# 4 Hardware setup

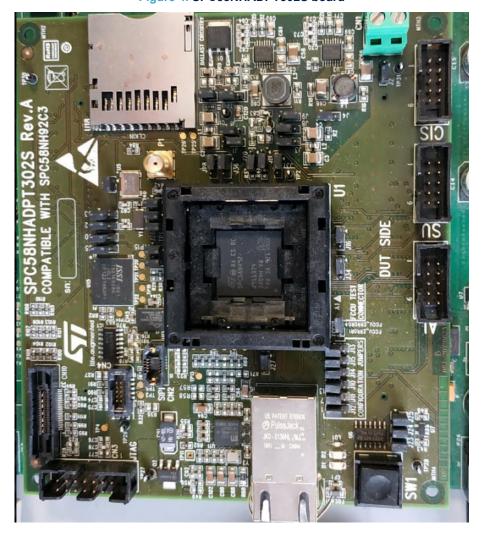

The OctalSPI instances can be tested on different platforms designed for this MCU family. In this application, the SPC58NHADPT302S board is the reference PCB.

Figure 4. SPC58NHADPT302S board

AN5524 - Rev 2 page 7/40

## 5 HyperRAM multi-chip package

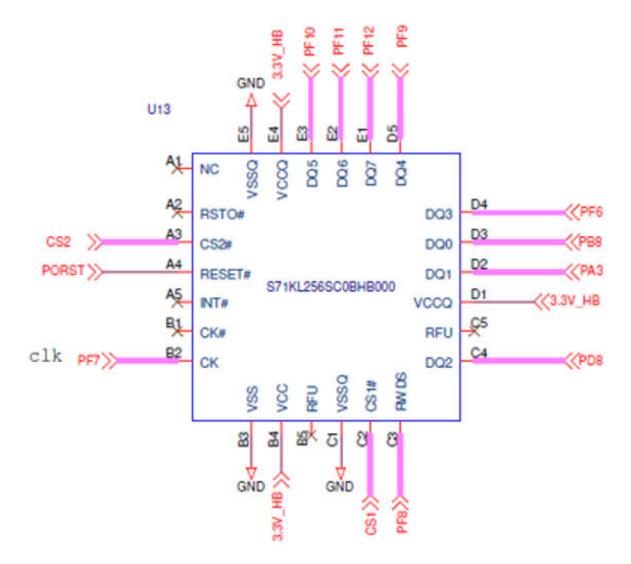

The SPC58NHADPT302S embeds the S71KL256SC0BHB000 by Cypress that's an HyperFlash and HyperRAM multi-chip package composed by:

- S26K HyperFlash device.

- S27K HyperRAM device.

Software can dialog with the two devices by using the OctalSPI instances **but not simultaneously.** For HyperFlash and HyperRAM operating conditions refer to cypress related datasheets.

Note:

the OCTOSPI\_1 chip select (CSN0) addresses the HyperRAM (on CS2#) while the OCTOSPI2 (CSN1) addresses the HyperFLASH (on CS1#).

Figure 5. S71KL256SC0BHB000 package

AN5524 - Rev 2 page 8/40

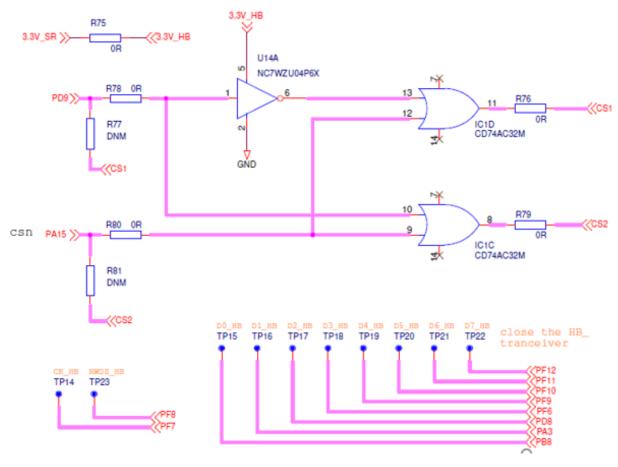

Figure 6. S71KL256SC0BHB000 wiring

Note: Ensure that on this PCB the following resistors R78, R80, R76 and R79 are removed and 0 Ohm fits to R81 and R77 instead of 0 Ohm fits to both R81 and R77.

AN5524 - Rev 2 page 9/40

## 6 OctalSPI signals

The OctoSPI interface uses up to eleven lines:

- CNS line for chip select.

- CLK line for clock.

- · DQS line for data strobe.

- DQ[0...7] eight lines for data.

Below the configuration of the pins used in this application for this micro-controller:

Table 2. OctalSPI IO mapping

| Port   | SIUL MSCR# | MSCR SSS             | Function               | Description            | Dir |

|--------|------------|----------------------|------------------------|------------------------|-----|

|        |            | OctalSPI 1 and Octa  | alSPI 2 - Data signals | 5                      |     |

| PN[8]  | 216        | 0000010              | DATA0                  | OctalSPI Data 0        | i/o |

| PN[8]  | 912        | 0000001              | DATA0                  | OctalSPI Data 0        | i   |

| PN[9]  | 217        | 0000010              | DATA1                  | OctalSPI Data 1        | i/o |

| PN[9]  | 913        | 0000001              | DATA1                  | OctalSPI Data 1        | i   |

| PN[10] | 218        | 0000010              | DATA2                  | OctalSPI Data 2        | i/o |

| PN[10] | 914        | 0000001              | DATA2                  | OctalSPI Data 2        | i   |

| PN[11] | 219        | 0000010              | DATA3                  | OctalSPI Data 3        | i/o |

| PN[11] | 915        | 0000001              | DATA3                  | OctalSPI Data 3        | i   |

| PN[13] | 221        | 0000010              | DATA4                  | OctalSPI Data 4        | i/o |

| PN[13] | 916        | 0000001              | DATA4                  | OctalSPI Data 4        | i   |

| PN[14] | 222        | 0000010              | DATA5                  | OctalSPI Data 5        | i/o |

| PN[14] | 917        | 0000001              | DATA5                  | OctalSPI Data 5        | i   |

| PN[15] | 223        | 0000010              | DATA6                  | OctalSPI Data 6        | i/o |

| PN[15] | 918        | 0000001              | DATA6                  | OctalSPI Data 6        | i   |

| PO[0]  | 224        | 0000010              | DATA7                  | OctalSPI Data 7        | i/o |

| PO[0]  | 919        | 0000001              | DATA7                  | OctalSPI Data 7        | i   |

|        | 0          | ctalSPI 1 and Octals | SPI 2 – Clock and DO   | QS                     |     |

| PP[14] | 254        | 0000010              | CLK                    | OctalSPI Clock         | i/o |

| PP[14] | 920        | 0000001              | CLK                    | OctalSPI Clock         | i   |

| PQ[1]  | 257        | 00000010             | DQS                    | OctalSPI Data strobe   | i/o |

| PQ[1]  | 911        | 0000010              | DQS                    | OctalSPI Data strobe   | i   |

|        |            | OctalSPI 1 and Oct   | alSPI 2 – Chip select  | t                      |     |

| PD[9]  | 57         | 00000111             | CSN1                   | OctalSPI 2 Chip select | 0   |

| PN[12] | 220        | 0000010              | CSN0                   | OctalSPI 1 Chip select | 0   |

In the SIUL2 configuration the Output Edge Rate Control (OERC) bit for output pins should be set as very strong  $\prime$  ultra strong drive.

AN5524 - Rev 2 page 10/40

## 7 Delay block overview

The delay block module is integrated with the OctalSPI to generate a delay on DQS signal. This block is designed to be used for both SDR and DDR modes. Only the DDR mode and 100 MHz as frequency are supported.

The usage of delay block allows to align the DQS edge to start the valid data window eye and try to give the maximum hold margin.

Generally, data and DQS are edge aligned so there is no extra delay necessary, in any case, the application can tune at runtime the block according to the concurrency of some events (e.g. temperature variation).

## 7.1 Delay block timing example

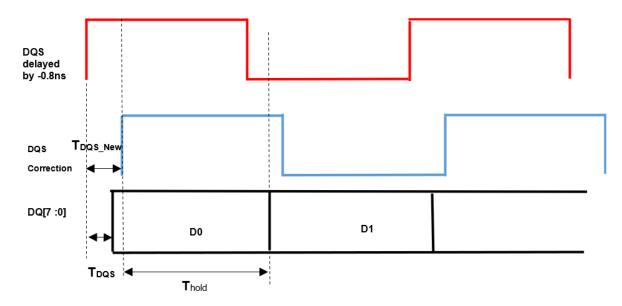

The DQS delay range can vary according to the memory type and constructor. This paragraph shows an example of the delay block timing adopted on this reference platform. According to Cypress HyperRAM timing parameter specification, for 3.0 Volt, in case of 100 MHz the RDWS, that is mapped on DQS, can be -0.8 or +0.8 ns.

DQS

DQ[7:0]

D0

D1

Figure 7. DQS and data signals aligned

So considering the case where the DQS introduces a delay of -0.8 ns, it is before the DQ [7:0] (issue on properly toggling the data).

Note that the delay introduced by the internal logic ( $T_{PAD}$ ) on DQS w.r.t. DQ [7:0] lines must be also considered. This delay is ranging from 50 ps to 2.1 ns. The following figure shows the correction and hold margin when the delay block applies to a positive shift of 1/12.

AN5524 - Rev 2 page 11/40

Figure 8. DQS is delayed by -0.8 ns and DLYBLK adds 1/12 as correction

The following formulas can be considered to calculate the correction:

$T_{correct} = T_{DLY} + T_{PAD}$

$T_{DQS New} = T_{correct} + T_{DQS}$

T<sub>hold</sub> is the time to toggle data valid after the RWDS edge.

$T_{hold} = T_{half\_period} - T_{DQS\_New}$

Where the T<sub>half\_period</sub> is 4.5 ns, the minimum half period according to the Cypress Hyperbus specification at 100 MHz.

T<sub>DLY</sub> **T<sub>DQS</sub>** T<sub>correct</sub> TDQS\_New Thold T<sub>PAD(min)</sub> Sel/Unit [ns] [ns] [ps] [ps] [ns] [ns] 1/10 1 50 1050 0.25 4.25 1/12 8.0 50 850 0.05 4.45 -0.8 2/10 2 2050 1.25 3.25 50 2/12 50 1650 0.85 3.65 1.6

Table 3. Hold margin according to a DQS delayed by - 0.8 ns

Table 4. Hold margin according to a DQS delayed by + 0.8 ns

| T <sub>DLY</sub> |      | T <sub>DQS</sub> | T <sub>PAD(max)</sub> | T <sub>correct</sub> | TDQS_New | T <sub>hold</sub> |

|------------------|------|------------------|-----------------------|----------------------|----------|-------------------|

| Sel/Unit         | [ns] | [ns]             | [ps]                  | [ps]                 | [ns]     | [ns]              |

| 1/10             | 1    |                  | 2100                  | 3100                 | 3.9      | 0.6               |

| 1/12             | 0.8  | +0.8             | 2100                  | 2900                 | 3.7      | 0.8               |

| 2/10             | 2    | +0.6             | 2100                  | 4100                 | 4.9      | -0.4              |

| 2/12             | 1.6  |                  | 2100                  | 3700                 | 4.5      | 0                 |

When the DQS anticipates the data ( $T_{DQS}$  = - 0.8 ns), as mentioned in Table 4. Hold margin according to a DQS delayed by + 0.8 ns, applying a  $T_{DLY}$  of 1/12 or 1/10 there is a margin to toggle the data and  $T_{hold}$  is quite high.

AN5524 - Rev 2 page 12/40

In the second case, when the DQS is after than the data ( $T_{DQS} = +0.8$ ), selecting a  $T_{DLY}$  equals to 2/10 or 2/12 the  $T_{hold}$  is reduced so this  $T_{DLY}$  selection should be avoided and a delay of 1/12 or 1/10 remains a reasonable choice.

Concluding, in this specific case for this platform and test condition, applying a  $T_{DLY}$  from 1/12 to 1/10 can guarantee acceptable margins to toggle the right data in time.

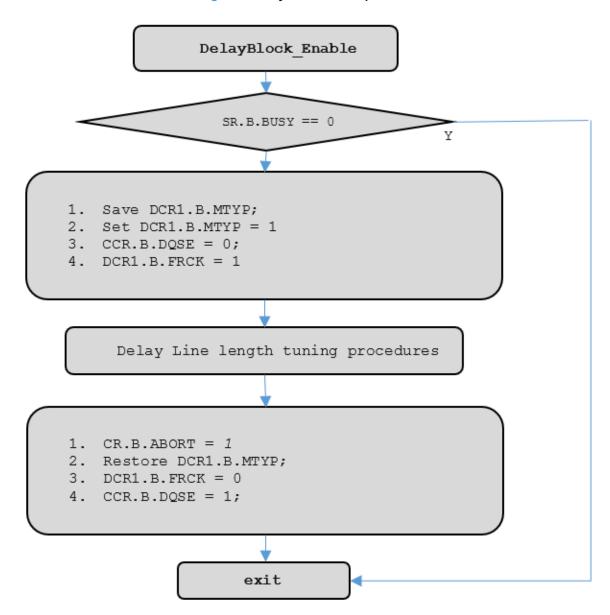

## 7.2 Delay block enable

$\label{lem:lemble_lock_enable} \begin{picture}(200,0) \put(0,0){\line(1,0){100}} \put(0,0){\line(1$

This function can be called when the OctalSPI instance is initialized.

Before re-calibrating the delay block, If SR.B.BUSY is set to 1, the DelayBlock\_Enable has to save some parts of the configuration and after raising an ABORT it can start tuning the block as described in the next paragraph.

The initial status will be restored after completing the whole procedure.

Any error condition will be reported to the caller function.

Figure 9. Delay block enable procedure

AN5524 - Rev 2 page 13/40

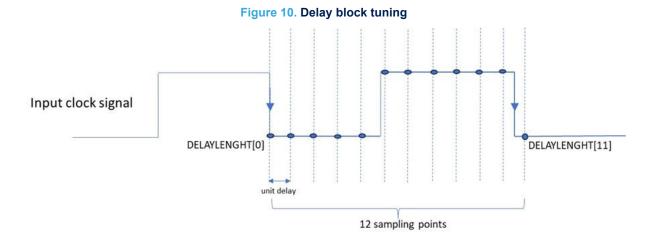

## 7.3 Delay block length tuning

When the delay block is enabled the following algorithm must be adopted to tune the lanes and select the delay desired on this platform.

Below an extract of the delay line length tuning procedures implemented inside the <code>DelayBlock\_Enable</code> function and related to the full period measurement.

```

uint32 t unit = 0;

uint32_t tuning_done = 0;

uint32 t length value;

//Enable Sampler and Delay blocks

OCTALSPI.DELAY CTRL.B.SE = 1U;

OCTALSPI.DELAY CTRL.B.DE = 1U;

//Enable all 12 delay cells

OCTALSPI.DELAY_CFG.B.DELAYSEL = 12U;

for(unit = 0; DLYB MAX UNIT >= unit; unit++)

//apply new DELAYUNIT

OCTALSPI.DELAY CFG.B.DELAYUNIT = unit;

//Wait for DELAYF

while (OU == OCTALSPI.DELAY CFG.B.DELAYF)

NOP();

length value = OCTALSPI.DELAY CFG.B.DELAYLENGTH;

//0111 11x0 0000 >>> FULL PERIOD we detect 2nd falling edge

if((OU < length value) && (OU == (length value & DLYB CFGR LNG 11)))

//tuning is finished properly

tuning_done = 1;

break;

}

if(1U == tuning_done)

//set the delay to 1/12 of CLK period

OCTALSPI.DELAY_CFG.B.DELAYSEL = 1;

//Sample length disabled

OCTALSPI.DELAY_CTRL.B.SE = 0;

//Delay Block enabled (output clock generated with the selected phase)

OCTALSPI.DELAY_CTRL.B.DE = 1;

else

//The algo did not find the right DELAYUNIT. The CLK period is probably too slow.

//Issue may be reported to upper SW layer end/or Delay block may be disabled

//only for debugging !

OCTALSPI.DELAY CFG.B.DELAYSEL = 1;

OCTALSPI.DELAY_CTRL.B.DE = 0U;

OCTALSPI.DELAY_CTRL.B.SE = 0U;

OCTALSPI.CR.B.EN = OU;

OCTALSPI.DCR1.B.FRCK = 0U;

while(1);

}

```

Note: Used values #define DLYB MAX UNIT 127U #define DLYB CFGR LNG 11 0x800U.

#### 7.3.1 Code/algorithm description

The algorithm proposed consists of tuning the delay block on a full period.

AN5524 - Rev 2 page 14/40

DELAYLENGHT field can be considered as a shift register containing the sampling of the input clock signal done every delay unit (defined by the correspondent DELAYUNIT field) once the falling edge of the input clock is triggered, as described in the picture below.

The algo increases the duration of delay units (from 0 to 127) until the entire period is covered, passing through following phases:

- As long as 12\*delay units is lower than half a period, DELAYLENGHT field will remain at 0x0.

- 2. When "12\*delay units" is between half a period and a period, the first bits of DELAYLENGHT will be at 0, and the last bits will be at 1.

- 3. When "12\*delay units" is just greater than a full period, then the first bits of DELAYLENGHT will be at 0, then we will see some bits at 1, then the last bit (DELAYLENGHT[11]) will be at 0.

The condition 3) determines the completion of the tuning.

There is also the possibility to tune the delay block on a half period: in this case, it can be considered completed when the "12 \*delay units" is just greater than a half period with the last bit of DELAYLENGHT at 1 and all the others at 0.

Such kind of algorithm can be optimized and modified according to the hardware constraints and not to typical temperature conditions. In some cases, further corrections need to be adopted for TDLY to guarantee a better alignment of the RWDS with the data signals. In fact, the delay selection in this example, is in-line with the timing calculated on this specific platform on normal temperature conditions. The application could retune the delay block when the voltage/temperature forces the DQS/RDWS to go out of the data valid window. This case is not covered in this demo application.

AN5524 - Rev 2 page 15/40

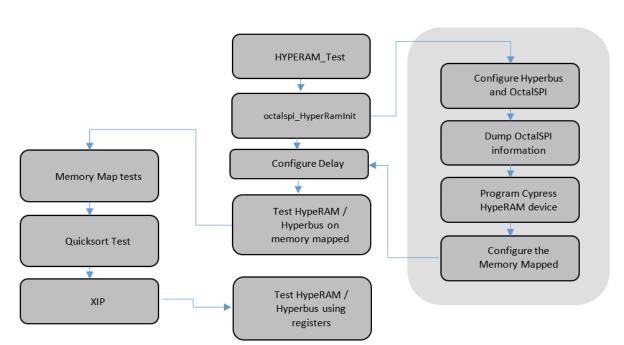

## 8 Application overview

This application after configuring the whole micro-controller, setup clocks and signals, then in a loop sequentially tests both OctalSPI\_1 and OctalSPI\_2. The focus is on the HyperBUS protocol implementation.

Below is the simple main function:

```

int main(void)

{

int i, j;

int fail = 0;

componentsInit();

irqIsrEnable();

for (i=0; i < test_loops; i++) {

for (j=0; j <=1; j++) {

/* Arguments: instance number - delay block enabled */

fail += HYPERRAM_Test(1, j);

fail += HYPEFLASH_Test(2, j);

}

}

printf("\nOCTALSPI result: %d failures in %d loops\r\n", fail, test_loops);

}</pre>

```

The first instance is mapped on the HyperRAM while the second one is mapped on HyperFLASH.

Both devices will be tested with a set of user case to check some features and robustness.

The test output is visible over serial console, a LINFLEX instance is properly configured as UART for this purpose. The LIN\_RX PIN PD[14] is configured as UART TX signal.

Before accessing the OctalSPI, the following platform setup must be applied to enable the controller accesses.

```

static void octalspi_pltfrm_setup(void)

{

PMCDIG.VSIO.B.VSIO_EMMC = 0;

PMCDIG.VSIO.B.VSIO_ETH1 = 0;

SPCSetPeripheralClockMode(SPC5_OCTALSPI_PCTL, SPC5_ME_PCTL_RUN(1) |

SPC5_ME_PCTL_LP(2));

/* Reset of peripheral to clear all registers */

MC_RGM.PRST2.B.OCTALSPI_RST = 1;

MC_RGM.PRST2.B.OCTALSPI_RST = 0;

/* This enables the multiplexing of the two OctoSPI.

* Note: this can be done before init the devices. */

OCTALSPI_IOM.IOM_CR.R = 1U;

}

```

Where:

```

#define SPC5_OCTALSPI_PCTL 77 /* -> Reference Manual - PCTL */

```

Note: the two OSPI instances are embedded along with an IO manager. This is controlled by a single PCTL.

## 8.1 HyperRAM application

After configuring the OctalSPI 1, the following tests are executed on the device:

- The memory map space is filled with a fixed pattern and a memory copy is tested. The data moved from/to memory mapped space (e.g. 0x70000000) must be coherent.

- A quick sort algorithm is implemented. The data sorted in SRAM and on a memory mapped region must be equal.

AN5524 - Rev 2 page 16/40

- The indirect-mode transfer via registers.

- XIP mode (see the related paragraph).

In case an error occurs, while configuring the device, the application will exit with an error.

Any test failure will be logged and reported at the end of the execution. The following block diagram aims at summarizing the test execution.

Figure 11. HyperRAM test simplified block schema

#### 8.1.1 HyperRAM configuration

The HYPERRAM Test function configures the OctalSPI from scratch by invoking the following API:

```

static void octalspi_init(const ospi_cfg_t *config)

octalspi_pltfrm_setup(); /* Platform configuration */

octalspi->DCR1.B.MTYP = config->memoryType;

octalspi->DCR1.B.DEVSIZE = config->deviceSize - 1;

octalspi->DCR1.B.CSHT = config->chipSelectHighTime - 1;

octalspi->DCR1.B.FRCK = config->freeRunningClock;

octalspi->DCR1.B.CKMODE = config->clockMode;

octalspi->DCR2.B.WRAPSIZE = config->wrapSize;

octalspi->DCR2.B.PRESCALER = config->clockPrescaler;

octalspi->DCR3.R = 0;

octalspi->DCR3.B.CSBOUND = config->chipSelectBoundary;

octalspi->CR.B.FTHRES = config->fifoThreshold - 1;

/* Wait until the device is not BUSY */

while (octalspi->SR.B.BUSY)

osalThreadDelayMilliseconds(1UL);

octalspi->CR.B.DQM = config->dualQuad;

octalspi->TCR.B.SSHIFT = config->sampleShifting;

octalspi->TCR.B.DHQC = config->delayHoldQuarterCycle;

octalspi ccr(); /* setup the communication configuration register */

octalspi->CR.B.EN = 1; /* Enable the OctalSPI */

```

The const ospi\_cfg\_t is a structure to configure the OctalSPI device that is fixed in the project configuration. All the parameters used to fill this structure must be selected according to the memory device adopted.

AN5524 - Rev 2 page 17/40

When accessing to the HyperRAM device, the following configuration is used to access the device and get the information from registers, the fixed latency mode is adopted:

```

const ospi_hyperbus_cfg_t octalspi_HyperRAM_cypress_bus_conf = {

4,    /* Read write recovery time */

6,    /* Device access time */

1,    /* 1: no latency on Write to access registers */

1    /* Latency mode => 0: variable, 1: fixed */

};

```

After configuring the device, the variable latency mode can be set up.

```

const ospi_hyperbus_cfg_t octalspi_HyperRAM_bus_conf = {

4,    /* Read write recovery time */

6,    /* Device access time */

0,    /* 0 latency on write to access HyperRAM (device dependent) */

0    /* Latency mode => 0: variable, 1: fixed */

};

```

If a fixed latency is selected, the memory will always indicate a refresh latency and delay the read data transfer accordingly. If a variable latency is selected, a latency is only added when a refresh is required at the same time a new transaction is starting. A variable latency is preferred for performance reasons on these kind of memories. For variable latency, the device access time has to be up to 6. For the fixed latency it might decrease according to the frequency used.

See also Section Appendix A HyperBus timing for timing considerations.

The configuration is propagated to the cypress memory device by using another low-level driver. This will be described later.

In the HyperBus mode, the device timing (tACC and tRWR) and the latency mode must be configured in the OCTOSPI HyperBus latency configuration register as shown below:

```

void octalspi_HyperbusCfg(const ospi_hyperbus_cfg_t *config)

{

octalspi->HLCR.R = 0;

octalspi->HLCR.B.TRWR = config->rwRecoveryTime;

octalspi->HLCR.B.TACC = config->accessTime;

octalspi->HLCR.B.WZL = config->writeZeroLatency;

octalspi->HLCR.B.LM = config->latencyMode;

}

```

The following function is used to select the memory map mode.

```

void octalspi_MemoryMapped(const ospi_cfg_t *config)

{

octalspi->LPTR.R = 0U;

octalspi->LPTR.B.TIMEOUT = config->timeoutPeriod;

octalspi->CR.B.TCEN = config->timeoutActivation;

octalspi->CR.B.FMODE = OSPI_FMODE_MEMORY_MAPPED;

octalspi->DCR1.B.MTYP = config->memoryType;

}

```

The memoryType, according to the reference manual, can be programmed with the following values, considering that it should be set in HyperBus memory mode on this platform.

- 0: Micron mode, D0/D1 ordering in DTR 8-data-bit mode.

- 1: Macronix mode, D1/D0 ordering in DTR 8-data-bit mode.

- 3: Macronix RAM mode, D1/D0 ordering in DTR 8-data-bit mode.

- 4: HyperBus memory mode, the protocol follows the Cypress

- 5: HyperBus register mode, addressing register space.

Switching to memory map mode,  ${\tt memoryType}$  is equal to 4.

Concerning the functional modes, the application defines the following:

AN5524 - Rev 2 page 18/40

```

#define OSPI_FMODE_INDIRECT_WRITE 0

#define OSPI_FMODE_INDIRECT_READ 1

#define OSPI_FMODE_AUTO_POLLING 2

#define OSPI_FMODE_MEMORY_MAPPED 3

```

Completing the whole setup the application executes the battery of tests, mentioned above, to check the transfer through the memory map space. Completing those, a simple test using the indirect-mode is run as well.

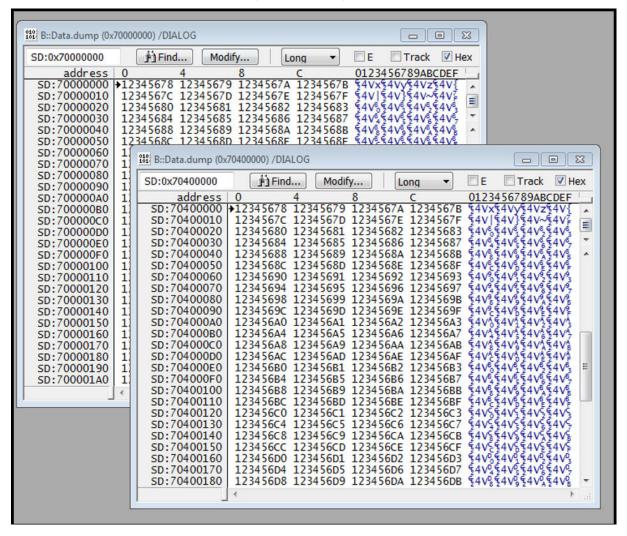

#### 8.1.2 Memory map example

The following figure shows a basic test where a block of the memory mapped space, e.g. 0x70000000, is filled with a pattern and then is copied to another memory. The test fails in case a bit differs.

Figure 12. Memory dump

#### 8.1.3 Indirect mode example

In this mode, the following two APIs are implemented to write and read on the device by using the registers. This test just performs the write operation reading back the value. It fails in case just one bit differs.

AN5524 - Rev 2 page 19/40

```

void octalspi HyperbusMemWrite(uint32 t *buffer, int size, uint32 t addr)

int i;

octalspi HyperbusCommand(SPC5 OSPI MEMTYPE HYPERBUS RAM, size, addr);

octalspi->CR.B.FMODE = OSPI FMODE INDIRECT WRITE;

while (!(octalspi->SR.B.FTF)) {};

for (i=0; i< size / (sizeof(uint32_t)); i++) {</pre>

*((uint32 t *) &octalspi->DR.R) = buffer[i];

/* In polling mode checks the transfer status */

octalspi_xfer_completed();

void octalspi HyperbusMemRead(uint32 t *buffer, int size, uint32 t addr)

octalspi_HyperbusCommand(SPC5_OSPI_MEMTYPE_HYPERBUS_RAM, size, addr);

octalspi->CR.B.FMODE = OSPI FMODE INDIRECT READ;

addr = octalspi->AR.R;

octalspi->AR.R = addr;

while (!(octalspi->SR.B.FTF)) {};

for (i=0; i< size / (sizeof(uint32_t)); i++) {</pre>

buffer[i] = *((uint32_t *) &octalspi->DR.R);

octalspi xfer completed();

```

The following code is to check if the transfer has been completed (no interrupt is used in this case):

```

static inline void octalspi_xfer_completed(void)

{

while (!octalspi->SR.B.TCF) {};

octalspi->FCR.B.CTCF = 1;

}

```

The octalspi\_HyperbusCommand is invoked to prepare the transfer of data from/to the memory by programming the MTYP field in the device configuration register 1.

```

static void octalspi_HyperbusCommand(uint8_t memtype, uint32_t data_length, uint32_t address)

{

while (octalspi->SR.B.BUSY){};

/* Functional mode */

octalspi->CR.B.FMODE = OSPI_FMODE_INDIRECT_WRITE;

/* Memory Type to access on register or memory address */

octalspi->DCR1.B.MTYP = memtype;

/* Specify a number of data bytes to read or write in the OCTOSPI_DLR */

octalspi_ccr();

octalspi->DLR.R = data_length-1;

/* Specify the targeted address in the OCTOSPI_AR */

octalspi->AR.R = address;

}

```

## 8.2 Cypress low level driver

A low level driver is necessary to program the S71KL256SC0BHB000 device.

The designed driver provides a set of basic APIs to access the registers and implement a part of the protocol.

## 8.2.1 Cypress S27K HyperRAM

There are two identification read only, non-volatile, word registers, that provide information on the device plus two registers used for configuring power mode and access protocol operating conditions.

AN5524 - Rev 2 page 20/40

The following code is used to access these registers:

```

static void cypress_read_config_reg(void)

{

uint16_t cfg0;

uint16_t cfg1;

cfg0 = octalspi_HyperbusRegRead(CYPRESS_CFG0_REG);

cfg1 = octalspi_HyperbusRegRead(CYPRESS_CFG1_REG);

...

```

While the identification information can be read as shown below:

```

id0 = octalspi_HyperbusRegRead(CYPRESS_ID0_REG);

id1 = octalspi_HyperbusRegRead(CYPRESS_ID1_REG);

```

The offset of the mentioned registers is:

```

#define CYPRESS_ID0_REG 0x0

#define CYPRESS_ID1_REG 0x2

#define CYPRESS_CFG0_REG 0x1000

#define CYPRESS_CFG1_REG 0x1002

```

Through the configuration register 0 it is possible to define the operating conditions for the HyperRAM device and setting latency and initial latency modes or entering in power down.

#### 8.2.2 Cypress S26K HyperFlash

To test the S26K HyperFLASH, the application invokes the cypress low level APIs for example to reset, erase and program the device.

The S26K does not use a traditional serial flash command protocol so the regular command protocol is not implemented.

To perform each operation the software must implement the device protocol to send the commands to the device in HyperBUS.

The cypress Programming Guide documents all supported commands, so this paragraph reports how the application implements one of them (for reference).

The code below shows the Cypress Macro Erase (Chip Erase) Command Sequence List. According to the protocol, this is completed in 6 cycles with a sequence of ADDRESS/DATA. The octalspi\_HyperbusMemWrite8 is invoked to access the device according to the APIs mentioned in the previous sections.

AN5524 - Rev 2 page 21/40

```

4th

5th

3rd

555h|00AAh 2AAh|0055h 555h|0080h 555|00AAh 2AAh|0055h 2AAh|0010

*/

void cypress flash erase(void)

int i;

uint8_t *status;

uint32_t erase_address[6] = { ADDR_PATTERN_1, ADDR_PATTERN_2,

ADDR_PATTERN_1, ADDR_PATTERN_1, ADDR_PATTERN_2, ADDR_PATTERN_1};

uint8_t erase_data[(2*6)] = {DATA_PATTERN_1, 0x00, DATA_PATTERN_2, 0x00,

ERASE_CMD, 0x00, DATA_PATTERN_1, 0x00,

DATA PATTERN 2, 0x00,

CHIP_ERASE_CMD, 0x00);

for (i=0; i < 6; i++) {

octalspi_HyperbusMemWrite8(&erase_data[2*i], 2, erase_address[i]);

do {

status = cypress read status();

} while(!(status[0] & 0x80)); /* READY BIT SR[7] */

printf("S26K HyperFlash erase phase completed\r\n");

```

Where:

```

#define ADDR_PATTERN_1 (0x555 << 1)

#define ADDR_PATTERN_2 (0x2AA << 1)

#define DATA_PATTERN_1 0xAA

#define DATA_PATTERN_2 0x55</pre>

```

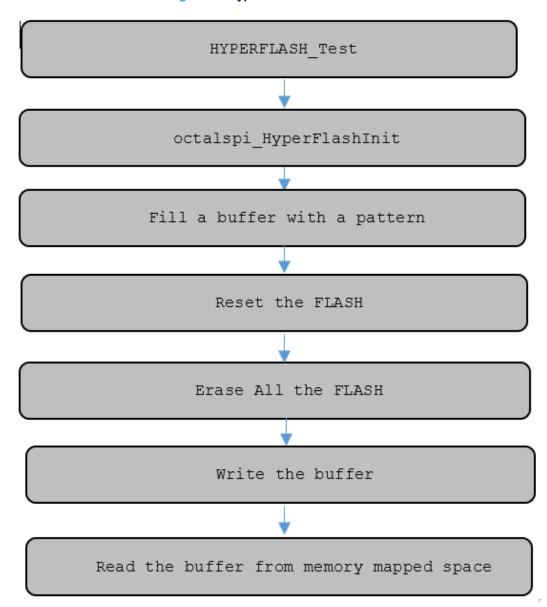

## 8.3 HyperFLASH application

After configuring the OctalSPI to use the HyperFLASH, the applications have to reset and erase the whole flash. Then a user buffer is filled and written to the device. The application reads back the buffer from memory map and fails if any bits differ.

AN5524 - Rev 2 page 22/40

Figure 13. HyperFLASH block schema

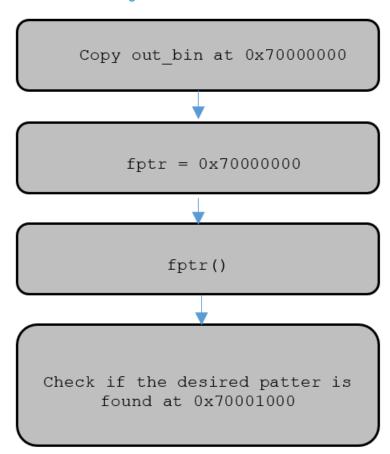

## 8.4 HyperRAM XIP test

The execute in place (XIP) operation is implemented in this architecture. The XIP feature allows to execute programs directly from the external device.

This paragraph aims at showing how to test this kind of feature where a program is placed in HyperRAM.

The first step is to prepare an application that will be copied in the external memory. For this purpose, a very simple main has been developed: it just writes a pattern to a known address, e.g.: 0x70001000.

Then its binary data are converted into a source header file:

AN5524 - Rev 2 page 23/40

This header file can be included in the OctalSPI application and, at runtime, the application copies it inside the HyperRAM at the following address: 0x70000000. It is necessary to take care about the endianness.

Figure 14. XIP block schema

After copying the binary in the selected portion of the external device, the code can jump to it (see block schema above). As soon as the  $out\_bin$  code is executed, the program counter will keep on the caller. The following debug session shows the result of the execution of the  $out\_bin$ .

AN5524 - Rev 2 page 24/40

octalspi\_demo.c

★ Over

L Diverge

Find:

L Diverge

Find:

addr/line source 151 static unsigned int mem\_xip\_test(void) int i, ret = 0;

void (\*fptr)(void);

int32\_t \*hram = (int32\_t \*) hram\_addr;

int32\_t \*a = (int32\_t \*) (hram\_addr + 0x1000);

unsigned int size = sizeof(out\_bin); 153 buff\_le8\_to\_cpu(&out\_bin, size);

memcpy(hram, out\_bin, size); /\* Prepare the machine to jump and execute the code in HypeRAM \* Test will write OxFOCACCIA at a fixed memory address \*/

fptr = hram;

fptr(); /\* Check if hram\_addr + 0x400 has been set with 0xF0CACC1A \*/ for (i = 0; i < 100; i++) { | (a|t) | | (a|t) | | (a|t) | | (bxF0CACC1A + i)) } 810 B::Data.dump (0x70001000) /DIALOG 111 B::Data.dump (0x70000000) /DIALOG j Find... Modify... Long ▼ ☐ Track ☑ Hex SD:0x70001000 Find... | Long -SD:0x70000000 SD:70000000 SD:70000010 SD:70000020 SD:70000030 SD:70000030 SD:70000050 SD:70000050 SD:70000060 SD:70000060 SD:70000080 SD:70000080 SD:70000080 SD:70000080 SD:70000080 SD:70000080 SD:70000080 SD:70000080 SD:70000080 SD:70000100 SD:70000100 SD:70000110 SD:70000110 SD:70000110 SD:70000110 SD:70000110 SD:70000110 SD:70000110 SD:70000110 SD:70000110

Figure 15. XIP test result

## 8.5 Interrupts handling

Table 5. OctalSPI interrupt shows the interrupt mapping for the two controllers.

OctalSPI2 OctalSPI1 **IRQ Name** Number Global Interrupt 186 192 187 Timeout 193 Status match 194 188 FIFO threshold 189 195 Transfer complete 190 196 Transfer error 191 197

Table 5. OctalSPI interrupt

The global interrupt vector handles the other five interrupts. The following code is to install the global interrupt inside the SPC5Studio tool.

AN5524 - Rev 2 page 25/40

```

#define SPC5 OCTALSPI 1 HANDLER

vector186

#define SPC5_OCTALSPI_2_HANDLER

vector192

#define SPC5_OCTALSPI_1_NUMBER

#define SPC5_OCTALSPI_2_NUMBER

#define SPC5_OCTALSPI_PRIORITY

186

192

INTC PSR ENABLE (INTC PSR CORE2, 10)

IRQ HANDLER (SPC5 OCTALSPI 1 HANDLER) {

IRO PROLOGUE();

osalEnterCriticalFromISR();

octalspi_main_isr();

/* Interrupt Service Routine */

osalExitCriticalFromISR();

IRQ EPILOGUE();

}

void octalspi irq install(unsigned int instance)

if (instance == 1)

INTC_PSR ( SPC5_OCTALSPI_1_NUMBER ) = SPC5_OCTALSPI_PRIORITY;

INTC_PSR ( SPC5_OCTALSPI_2_NUMBER ) = SPC5_OCTALSPI PRIORITY;

/* Enable the IRQ events */

octalspi EnableIRQ();

```

Where the octalspi\_main\_isr is the low-level APIs that just enables, inside the control register (CR) the related IRQ, i.e.:

- Timeout interrupt enable (TOIE)

- Status match interrupt enable (SMIE)

- FIFO threshold interrupt enable (FTIE)

- Transfer complete interrupt enable (TCIE)

- Transfer error interrupt enable (TEIE)

Note: refer to OctalSPI related guide inside the Reference manual for a complete description of the bits mentioned above (see Section Appendix C Reference documents).

Note: in the examples reported in the previous chapters the transfer status is checked in polling mode to better show the flow of each single operation.

The application configuration adopts a specific defines macro to enable / disable interrupt support.

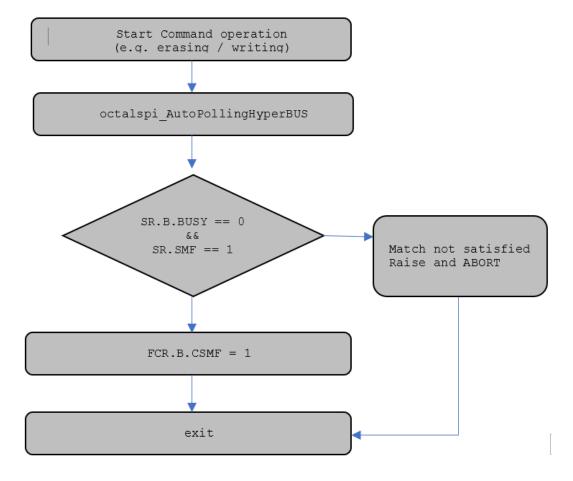

## 8.6 Automatic polling mode

The status match flag is set in automatic-polling mode when the unmasked received data match the corresponding bits in the match register (OCTOSPI\_PSMAR). This paragraph shows an example code on how to configure this mode (HyperBUS / Regular Command protocols) and also shows a diagram that aims at detailing the logic flow.

AN5524 - Rev 2 page 26/40

```

uint32 t octalspi AutoPollingHyperBUS(ospi polling cfg t *cfg, uint32 t poll addr)

If PSMAR.B.MASK[n] = 1 and the content of bit[n] is the same as

* PSMAR.B.MATCH[n] so the match is satisfied.

If PSMAR.B.MASK[n] = 0, so the bit n is masked and not considered.

octalspi->PSMAR.B.MATCH = cfg->Match;

octalspi->PSMKR.B.MASK = cfg->Mask;

octalspi->PIR.B.INTERVAL = cfg->Interval;

octalspi->CR.B.FMODE = OSPI_FMODE_AUTO_POLLING;

/* 1: stop after a match */

octalspi->CR.B.APMS = cfg->AutomaticStop;

* Match Mode: 0: AND, 1: OR

^{\star} In AND mode means that only when there is a match on all of the

^{\star} unmasked bits, then the status match flag (SMF) is set.

* then "OR" match mode is activated, which means that the SMF gets set if

* there is a match on any of the unmasked bits.

* BUSY goes to 0 as soon as a match is detected

* OCTOSPI DLR = 1, 8bit

octalspi->CR.B.PMM = cfg->MatchMode;

/* The maximum amount of data read in each frame is 4 bytes. If more data is

requested in OCTOSPI_DLR, it will be ignored and only 4 bytes will be

read.

octalspi->DLR.R = 3;

/* The command sequence starts as soon as the address is updated

* with a write to OCTOSPI_AR */

/* Targeted address is saved in the OCTOSPI AR */

octalspi->AR.R = poll_addr;

/* Note: In automatic polling mode, OCTOSPI DR contains the last data read

from the external device (without masking).

Same can be done by using IR register.

```

Note: When programming the match mask and read the DR register, the endianess format must be considered because the data could be swapped due to a different flash device endianess.

Note: Used values: #define DLYB\_MAX\_UNIT 127U; #define DLYB\_CFGR\_LNG\_11 0x800U

AN5524 - Rev 2 page 27/40

Figure 16. Automatic polling mode (generic flow diagram)

Note: The reference manual gives a detailed description of the matching flag programming and the controller status on each state of the polling mode (see Section Appendix C Reference documents).

## 8.7 Application output

On the serial console the following output messages are logged for both OctalSPI 1 and OctalSPI2 tests.

Note: After the configuration of the peripheral and delay block, all the test can be executed in one or more loops.

AN5524 - Rev 2 page 28/40

#### 8.7.1 HyperRAM test output

```

OctalSPI Application

OCTALSPI 1 (0x80000000 - 0x70000000)

OctalSPI version: 0x22, ID 0x140041, Magic ID 0xA3C5DD01

device configured as Master

Memory mapped write present

AHB interface

No memory mapped write 8 byte

DelayBlock_Enable (OCTSPI_1)

Delay Block Tuning completed

HyperBus Configuration

- Read write recovery time = 4

- Device access time = 6

- no latency on Write

- Fixed latency Mode

Found Cypress Manufacturer ID

HyperRAM mode selected

- 64 Mbit

Card Configuration reg: 0x8F17, 0x2

HyperBus Configuration

- Read write recovery time = 4

- Device access time = 6

- latency on Write

- Variable latency Mode

-- S27K HyperRAM Test --

TEST 1: filled 131072 byte of memory (0x70000000)

TEST 1: memcpy check PASSED

TEST 2: Quick Sort Test

TEST 2: QuickSort PASSED

TEST 3: transfer through registers PASSED

DelayBlock Disable (OCTSPI 1)

Reconfiguring the Hyperbus ...

OctalSPI version: 0x22, ID 0x140041, Magic ID 0xA3C5DD01

device configured as Master

Memory mapped write present

AHB interface

No memory mapped write 8 byte

DelayBlock Enable (OCTSPI 1)

Delay Block Tuning completed

TEST 4: XIP test: PASSED

DelayBlock_Disable (OCTSPI_1)

```

AN5524 - Rev 2 page 29/40

## 8.7.2 HypeFLASH test output

```

OCTALSPI 2 (0x80001000 - 0x60000000)

-- S26K HyperFlash Test --

OctalSPI version: 0x22, ID 0x140041, Magic ID 0xA3C5DD01

device configured as Slave

Memory mapped write present

AHB interface

No memory mapped write 8 byte

DelayBlock Enable (OCTSPI 2)

Delay Block Tuning completed

HyperBus Configuration

- Read write recovery time = 0

- Device access time = 16

- no latency on Write

- Variable latency Mode

S26K HyperFlash reset done

S26K HyperFlash erase phase completed

[Writing data 0x528003C0 (512 bytes)]

S26K HyperFlash write test done: 512 bytes

>>> Reconfiguring the Hyperbus for memory mapped addressing...

HyperBus Configuration

- Read write recovery time = 0

- Device access time = 16

- no latency on Write

- Variable latency Mode

DelayBlock Disable (OCTSPI 2)

TEST: memory mapped data are coherent

Test Completed!

```

AN5524 - Rev 2 page 30/40

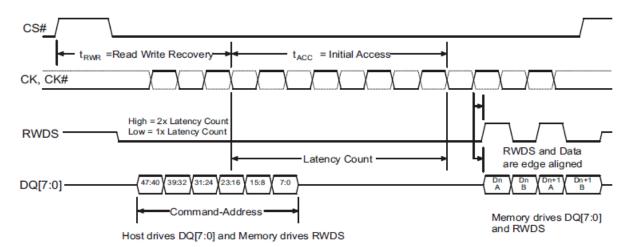

## Appendix A HyperBus timing

The commands, the addresses and data are transferred over the eight DATA [7:0] signals. The clock is used for information capture by the device. The command or address values are aligned with clock transitions which start with the assertion of CS# and Command-Address (CA) signals. These are followed by the start of clock transitions to transfer six command bytes. Then there is the initial access latency and either read or write data transfers, until the chip select is de-asserted.

The read and write operations need to respect two timings: tRWR that is the minimal read/write recovery time for the device and tACC used as access time for the device. Both must be programmed in the OctalSPI registers as shown below:

```

octalspi->HLCR.B.TRWR = config->rwRecoveryTime;

octalspi->HLCR.B.TACC = config->accessTime;

```

The DRAM cells cannot be refreshed during a read or write transactions: a host is required to limit the duration of transactions and allow an additional initial access latency as well. An additional latency is before tACC and after RWR and it is driven by the RWDS signal.

If a variable latency is selected, a latency for a refresh is only added when a refresh is required at the same time a new transaction is starting.

Figure 17. Read operation with an initial latency

Figure 18. Write operation with an initial latency

AN5524 - Rev 2 page 31/40

It is possible to force the latency to be fixed to 2 x tACC by programming the following register:

octalspi->HLCR.B.LM = 1;

The state of the RWDS signal is not considered in this mode. If a fixed latency is selected the memory will always indicate a refresh latency and delay the read data transfer accordingly.

AN5524 - Rev 2 page 32/40

# **Appendix B Acronyms and abbreviations**

Table 6. Acronyms

| Abbreviation | Complete name                  |

|--------------|--------------------------------|

| SIUL2        | System integration unit lite 2 |

| CGM          | Clock Generation Module        |

| XIP          | Execution in place             |

| SRAM         | System RAM                     |

| PCM          | Platform configuration module  |

| PSR          | Protocol Status Register       |

| SDR/DDR      | Single / Double Data Rate      |

AN5524 - Rev 2 page 33/40

# **Appendix C Reference documents**

**Table 7. Reference documents**

| Name    | Title                                                                                                                   |

|---------|-------------------------------------------------------------------------------------------------------------------------|

| RM0452  | SPC58EHx/SPC58NHx 32-bit Power Architecture microcontroller                                                             |

| DS12304 | SPC58EHx/SPC58NHx Errata sheet, Datasheet and IO map excel file                                                         |

| -       | S27KL0641/S27KS0641 S70KL1281/S70KS1281 3.0 V/1.8 V, 64 Mbit (8 Mbyte)/128 Mbit (16 Mbyte), HyperRAM™ Self-Refresh DRAM |

| -       | S71KL256SC0_S71KL512SC0, HYPERFLASH AND HYPERRAM MULTI<br>CHIP PACKAGE 3 V                                              |

AN5524 - Rev 2 page 34/40

# **Revision history**

**Table 8. Document revision history**

| Date        | Version | Changes                                                                                                                                                |

|-------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 05-Nov-2020 | 1       | Initial release.                                                                                                                                       |

| 05-Mar-2024 | 2       | Updated Table 4. Hold margin according to a DQS delayed by + 0.8 ns; Section 7.3 Delay block length tuning. Added Section 7.3.1 .  Minor text changes. |

AN5524 - Rev 2 page 35/40

## **Contents**

| 1 | Octa | aISPI in | troduction                       |    |

|---|------|----------|----------------------------------|----|

|   | 1.1  | Octals   | SPI protocol and operating modes | 2  |

|   |      | 1.1.1    | Regular command mode             | 2  |

|   |      | 1.1.2    | HyperBUS mode                    | 2  |

|   | 1.2  | Octals   | SPI operating modes              |    |

|   |      | 1.2.1    | Indirect mode                    | 3  |

|   |      | 1.2.2    | Memory-mapped mode               | 3  |

|   |      | 1.2.3    | Status polling mode              | 3  |

| 2 | SPC  | 58EHx    | /SPC58NHx OctalSPI mapping       | 4  |

| 3 | Octa | alSPI cl | lock selection                   | 5  |

| 4 | Hard | dware s  | setup                            | 7  |

| 5 |      |          | multi-chip package               |    |

| 6 |      |          | ignals                           |    |

| 7 |      |          | k overview                       |    |

| • | 7.1  |          | block timing example             |    |

|   | 7.1  |          |                                  |    |

|   |      |          | block enable                     |    |

|   | 7.3  | •        | block length tuning              |    |

|   |      | 7.3.1    | Code/algorithm description       |    |

| 8 |      |          | n overview                       |    |

|   | 8.1  | Hyper    | RAM application                  |    |

|   |      | 8.1.1    | HyperRAM configuration           | 17 |

|   |      | 8.1.2    | Memory map example               | 19 |

|   |      | 8.1.3    | Indirect mode example            | 19 |

|   | 8.2  | Cypre    | ess low level driver             | 20 |

|   |      | 8.2.1    | Cypress S27K HyperRAM            | 20 |

|   |      | 8.2.2    | Cypress S26K HyperFlash          | 21 |

|   | 8.3  | Hyper    | FLASH application                |    |

|   | 8.4  | Hyper    | RAM XIP test                     | 23 |

|   | 8.5  | Interru  | upts handling                    |    |

|   | 8.6  | Auton    | natic polling mode               | 26 |

| 8.7          | Applicat  | tion output |            |        | <br> | <br> | <br> | <br> | <br> | 28 |

|--------------|-----------|-------------|------------|--------|------|------|------|------|------|----|

|              | 8.7.1     | HyperRAM te | st output  |        | <br> | <br> | <br> | <br> | <br> | 29 |

|              | 8.7.2     | HypeFLASH t | est output |        | <br> | <br> | <br> | <br> | <br> | 30 |

| Appendix .   | А Нур     | erBus timin | g          |        | <br> | <br> | <br> | <br> | <br> | 31 |

| Appendix     | B Acre    | onyms and   | abbrevia   | tions. | <br> | <br> | <br> | <br> | <br> | 33 |

| Appendix     | C Refe    | erence docu | ıments     |        | <br> | <br> | <br> | <br> | <br> | 34 |

| Revision h   | nistory . |             |            |        | <br> | <br> | <br> | <br> | <br> | 35 |

| Contents .   |           |             |            |        | <br> | <br> | <br> | <br> | <br> | 36 |

| List of tab  | les       |             |            |        | <br> | <br> | <br> | <br> | <br> | 38 |

| List of fiau | ıres      |             |            |        | <br> | <br> | <br> | <br> | <br> | 39 |

## **List of tables**

| Table 1. | OctalSPI memory map                                | . 4 |

|----------|----------------------------------------------------|-----|

| Table 2. | OctalSPI IO mapping                                | 10  |

| Table 3. | Hold margin according to a DQS delayed by - 0.8 ns | 12  |

| Table 4. | Hold margin according to a DQS delayed by + 0.8 ns | 12  |

| Table 5. | OctalSPI interrupt                                 | 25  |

| Table 6. | Acronyms                                           | 33  |

| Table 7. | Reference documents                                | 34  |

| Table 8. | Document revision history                          | 35  |

# **List of figures**

| Figure 1.  | OCTSPI_CLK GCM selecion                                      | . 5 |

|------------|--------------------------------------------------------------|-----|

| Figure 2.  | Application clock details (SPC5Studio wizard)                | . 5 |

| Figure 3.  | OctalSPI prescaler selection (200 / 2 = 100 MHz)             | . 6 |

| Figure 4.  | SPC58NHADPT302S board                                        | . 7 |

| Figure 5.  | S71KL256SC0BHB000 package                                    | . 8 |

| Figure 6.  | S71KL256SC0BHB000 wiring                                     | . 9 |

| Figure 7.  | DQS and data signals aligned                                 | 11  |

| Figure 8.  | DQS is delayed by -0.8 ns and DLYBLK adds 1/12 as correction | 12  |

| Figure 9.  | Delay block enable procedure                                 | 13  |

| Figure 10. | Delay block tuning                                           | 15  |

| Figure 11. | HyperRAM test simplified block schema                        | 17  |

| Figure 12. | Memory dump                                                  | 19  |

| Figure 13. | HyperFLASH block schema                                      | 23  |

| Figure 14. | XIP block schema                                             | 24  |

| Figure 15. | XIP test result                                              | 25  |

| Figure 16. | Automatic polling mode (generic flow diagram)                |     |

| Figure 17. | Read operation with an initial latency                       | 31  |

| Figure 18. | Write operation with an initial latency                      | 31  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

AN5524 - Rev 2 page 40/40