# Getting started with STM32WL5x MCUs using IAR Embedded Workbench® and MDK-ARM

#### Introduction

This application note provides guidelines on how to used the software toolchains IAR Embedded Workbench® for Arm® (EWARM) and MDK-ARM from Keil®, with the STM32WL5x dual-core microcontrollers (MCUs).

## 1 Prerequisites

The following tools must be installed before starting this tutorial:

- EWARM IDE available for download from the official IAR System<sup>®</sup> web site

- MDK-ARM IDE available for download from the official Arm® Keil® web site

- STM32CubeProgrammer (STM32CubeProg) available for download from the official ST web site

- STM32CubeWL MCU Package available for download from the official ST web site

- ST-LINK server available for download from the official ST web site

The documents listed below may also help:

- STM32WL5x reference manual (RM0453)

- STM32WL55xx STM32WL54xx datasheet (DS13293)

- Cortex®-M4 and M0+ Technical Reference Manuals (available on Arm® web site)

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

AN5556 - Rev 1 page 2/39

#### 2 STM32WL5x architecture

The STM32WL5x dual-core microcontrollers use an heterogeneous core architecture, that is composed of a Cortex-M4 core (named CPU1) and a Cortex-M0+ core (named CPU2).

These two cores boot always separately. The dual-core debug allows a simultaneous debugging of both cores using a single hardware debug probe.

#### 2.1 Access port

The devices contain two access ports (AP):

- AP0: CPU1 debug access port (AHB-AP)

- AP1: CPU2 debug access port (AHB-AP)

#### 2.2 CPU2 boot

The CPU2 boots after the CPU1 has set the C2BOOT bit in the power control register 4 (PWR\_CR4). The C2BOOT value is retained in Standby mode and the CPU2 boots accordingly when exit from Standby. When security is enabled through the option byte, the CPU2 also boots when an illegal access has been detected.

The CPU2 can boot from the system memory (RSS/SFI) or anywhere in the user Flash memory (0x0800 0000), SRAM1 (0x2000 0000) or SRAM2 (0x2000 8000).

#### 2.3 Debug support

The figure below shows the logical partitioning of the debug infrastructure, with two interfaces: serial wire and JTAG debug port.

Trace port TPIU<sup>(1)</sup>  $DWT^{(1)}$ FPB<sup>(1)</sup>  $ITM^{(1)}$ TRACESWO **Debug access** AHB-AP(1) port (DAP) AHB JTAG/Serial-wire port ROM JTMS/SWDIO □ table<sup>(1)</sup> DAPBUS Core JTDI -PPB SWJ-DP JTDO -(1) CPU1 CTI(1) DBG MCU JTCK/SWCLK Cortex-M4 nJTRST□ Cross trigger matrix (CTM) AHB-AP(1) CTI<sup>(1)</sup> AHB ROM1 ROM2 Core table<sup>(1)</sup> table<sup>(1)</sup> CPU<sub>2</sub> BPU<sup>(1)</sup> DWT<sup>(1)</sup> Cortex-M0+ (1) Arm CoreSight<sup>™</sup> components

Figure 1. Block diagram of debug support infrastructure

AN5556 - Rev 1 page 3/39

Table 1. Debug features of Cortex-M cores

| CPU1 (Cortex-M4)                                                                                                                                                                                                                                                               | CPU2 (Cortex-M0+)                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>ROM table</li> <li>System control space (SCS)</li> <li>Breakpoint unit (FPB)</li> <li>Data watchpoint and trace unit (DWT)</li> <li>Instrumentation trace macrocell (ITM)</li> <li>Trace port interface unit (TPIU)</li> <li>Cross trigger interface (CTI)</li> </ul> | <ul> <li>ROM table</li> <li>System control space (SCS)</li> <li>Breakpoint unit (FPB)</li> <li>Data watchpoint and trace unit (DWT)</li> <li>Cross trigger interface (CTI)</li> </ul> |

The device-level debug features are controlled in the DBGMCU registers that are only accessible by the CPU1.

#### 2.4 Cross-trigger interface (CTI)

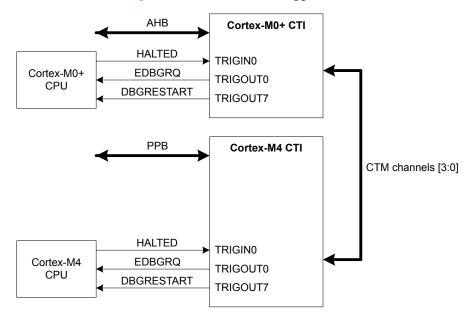

There are two CTI components in the STM32WL5x: one dedicated to the CPU1 and one dedicated to the CPU2. These CTIs are connected to each other via the cross-trigger matrix (CTM) and they enable events from various sources to trigger the debug activity.

For example, a breakpoint reached in one of the processor cores can stop the other processor.

Figure 2. Embedded cross trigger

#### 2.5 Global security controller (GTZC)

The STM32WL5x devices support security with isolation between:

- a secure world managed by the CPU2, where usually security sensitive applications are run and critical resources are located

- a non-secure or public world handled by the CPU1, where non-secure transactions are used

AN5556 - Rev 1 page 4/39

#### 2.6 Secure configuration (ESE/FSD option bits)

All or a part of the Flash memory and SRAM1, SRAM2 memories can be made secure, exclusively accessible for read and write by secured master: CPU2 and DMA channels (that have been configured as secured).

The secure CPU2 can only execute from secure areas, whereas the CPU1 can only execute from non-secure areas

Note:

The CPU2 security is enabled when part or all of the Flash memory is secure (FSD = 0) or when option byte loading fails. In this case, the ESE bit in FLASH OPTR is set.

#### Change the CPU2 security mode

The CPU2 security is easily enabled by loading the user option FSD with 0 (security applied in any RDP level). The CPU2 security start address can be modified by the secure CPU2, by loading a new user option SFSA. To totally disable the security, the CPU2 sets the FSD bit to 1.

Note:

Prior to removing security from part or all of the memory, a good practice consists in page erasing the Flash memory part that becomes non-secure.

Non-secure CPU1 and secure CPU2 can both remove security, by clearing the ESE bit to 0 in FLASH\_OPTR and regressing the RDP level from Level 1 to Level 0. In this case, the main Flash memory backup registers (RTC\_BKPxR), SRAM1, SRAM2 and PKA SRAM are erased.

#### Secure Flash memory area

The secure Flash memory area has a 2-Kbyte granularity sector, and is defined by the secure Flash start-address user option, controlled from the SFSA[6:0] in FLASH\_SFR. In the same register, the FSD bit controls if the Flash memory security is enabled. When enabled, the whole system security framework is activated.

#### Secure SRAM areas

The SRAM1 and SRAM2 areas are only secure when the Flash memory security is enabled (ESE = 1 and FSD = 0).

The secure SRAM1 and SRAM2 areas have a 1-Kbyte granularity. The backup SRAM2 can be configured as secure from the BRSD bit and its start address from SBRSA[4:0] in FLASG\_SRRVR. The non-backup SRAM can be configured as secure from the NBRSD bit and its start address from SNBRSA[4:0] in FLASG\_SRRVR.

#### **Debug access**

The selection for CPU2 debug access is independent from security:

- When the system is non-secure (ESE = 0), CPU1 and CPU2 can enable and disable the CPU2 debug access, via the DDS bit in FLASH\_SFR. In this case, the C2SWDBGEN bit is not writable and its default value is debug enabled. The CPU2 DDS debug is enabled/disabled after restarting OBL.

- When the system is secure (ESE = 1), the CPU2 debug access can only be enabled by the secure CPU2 via DDS and C2SWDBGEN bits. The CPU2 debug can be disabled directly by the CPU2 via the DDS bit, and indirectly by both CPUs when regressing ESE. The CPU2 debug is enabled/disabled after restarting OBL.

AN5556 - Rev 1 page 5/39

#### 3 Using EWARM

The EWARM (IAR Embedded Workbench for Arm) is installed by default in the folder

C:\Program Files (x86)\IAR Systems.

The STM32WL5x dual-core devices are officially supported (without need of ST patches) on EWARM starting from version 8.50.9

In this section, EWARM v8.50.6 with an internal patch for STM32WL5x (EWARMv8\_STM32WLxx\_V4.7), and a project template from STM32Cube FW WL V1.0.0 are used.

#### 3.1 Dual-core debug steps (EWARM)

#### 3.1.1 CM4 project settings (EWARM)

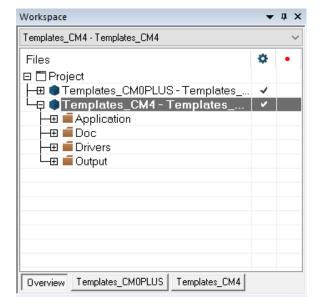

This section outlines the settings of the CM4 project, and uses a project template from STM32Cube\_FW\_WL\_V1.0.0, named *Templates\_CM4*.

1. Open the Template DualCore project under

\STM32Cube FW WL V1.0.0\Projects\NUCLEO-WL55JC\Templates\DualCore\EWARM.

This project is used to work on both cores at the same time. This project appears now in the *Project Explorer* view as shown in the figure below.

Figure 3. EWARM project explorer view

AN5556 - Rev 1 page 6/39

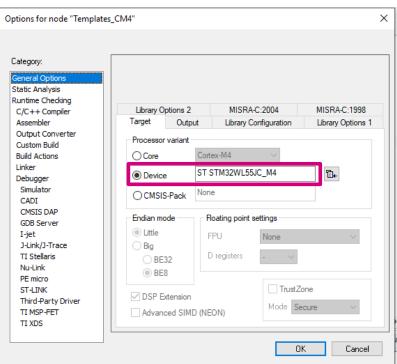

- 2. Set the *Templates\_CM4* project as active, and ensure that the settings are compatible with the project options below.

- Go to Project > Options. On the General Options, select the STM32WL55JC\_M4 device (see the figure below).

Figure 4. STM32WL55JC\_M4 device selection

AN5556 - Rev 1 page 7/39

b. Go to the *Linker* tab -> *Config Linker configuration file editor* section. Click *Edit* to display the *Linker configuration file editor*. Check that the application has been linked to the right address: Boot from main Flash memory at 0x0800 0000 and Boot from SRAM memory at 0x2000 0000.

Options for node "Templates\_CM4" Category: Factory Settings General Options Static Analysis Runtime Checking Diagnostics Extra Options #define Checksum Encodings C/C++ Compiler #define Diagnostics Checksum Encodings Extra Option

Config Library Input Optimizations Advanced Output List Assembler Output Converter Linker configuration file Custom Build Overide default Build Actions \$PROJ\_DIR\$/stm32wl55xx\_flash\_cm4.icf Linker Debugger Simulator Linker configuration file editor CADI CMSIS DAP Vector Table Memory Regions Stack/Heap Sizes GDB Server I-jet Start: 0x08000000 End: 0x0801FFFF J-Link/J-Trace ROM TI Stellaris Nu-Link RAM 0x20000000 0x20003FFF PE micro ST-LINK Third-Party Driver TI MSP-FET Save TI XDS OK Cancel

Figure 5. CM4 project - Linker configuration

AN5556 - Rev 1 page 8/39

c. From *Debugger* tab, select *ST-LINK* as a debugger in the *Driver* field (the NUCLEO-WL55JC board contains an embedded debugger STLINK-V3).

× Options for node "Templates\_CM4" Category: Factory Settings General Options Static Analysis Runtime Checking Setup Download Images Multicore Extra Options Plugins C/C++ Compiler Output Converter Driver ✓ Run to Custom Build ST-LINK **Build Actions** Setup macros Linker Use macro file(s) Simulator CADI CMSIS DAP GDB Server I-jet Device description file J-Link/J-Trace Override default TI Stellaris Nu-Link \$TOOLKIT\_DIR\$\CONFIG\debugger\ST\STM32WL55JC\_M4 ... PE micro ST-LINK Third-Party Driver TI MSP-FET TI XDS ΟK Cancel

Figure 6. Debugger setup

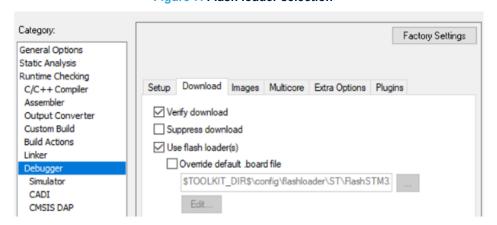

d. Go to Debugger -> Download tab and tick the Use flash loader(s) check box.

Figure 7. Flash loader selection

AN5556 - Rev 1 page 9/39

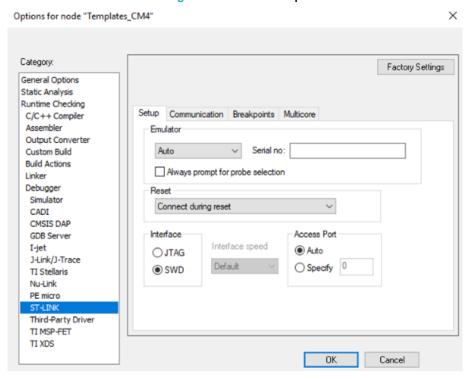

e. Go to Project -> Options -> ST-LINK -> Setup.

Figure 8. ST-LINK setup

- f. Select the Access Port:

- Auto: The access port 0 for Cortex-M4 is automatically used.

- Manually: It is possible to manually select the access port (by putting 0 with CM4, for example).

- g. Select *SWD* in the communication *Interface* to use the serial-wire output (SWO) communication channel (fewer pins than JTAG).

- h. Select the *Reset* type: With *Connect during reset*, the ST-LINK connects to the target while keeping reset active. Reset is pulled low and remains low while connecting to the target.

AN5556 - Rev 1 page 10/39

DK Cancel

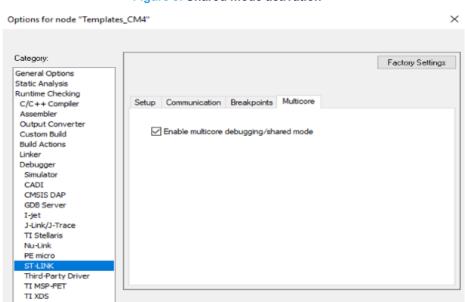

i. Go to the *Multicore* tab to enable the use of the *shared mode* to debug both cores simultaneously.

Figure 9. Shared mode activation

Note: To set up for a multicore debugging using an ST-LINK debug probe, install the latest ST-LINK server version available on www.st.com.

AN5556 - Rev 1 page 11/39

#### 3.1.2 CM0+ project settings (EWARM)

This section outlines the settings of the CM0+ project, and uses a project template from STM32Cube\_FW\_WL\_V1.0.0, named *Templates\_CM0PLUS*.

#### Important:

The CPU2 (Cortex-M0+) boots after the CPU1 (Cortex-M4) has set the C2BOOT bit in the power control register 4 (PWR\_CR4). This allows the CPU1 to initialize the system after a reset or wakeup from system low-power mode, before booting the CPU2.

- Open in another instance the *Templates\_CMOPLUS* project under \STM32Cube\_FW\_WL\_V1.0.0\Projects\NUCLEO-WL55JC\Templates\DualCore\EWARM, and ensure that the settings are compatible with the options below.

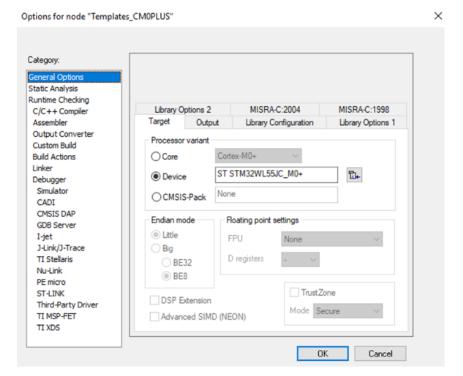

- Go to Project -> Options. On the General Options, select the STM32WL55JC\_M0+ device (see the figure below).

Figure 10. ST32WL55JC\_M0+ device selection

AN5556 - Rev 1 page 12/39

b. Go to the *Linker* tab -> Config *Linker configuration file editor* section. Click *Edit* to display the *linker configuration file editor*. Check that the application has been linked to the right address: Boot from main Flash memory at 0x0802 0000 and Boot from SRAM memory at 0x2000 4000.

Options for node "Templates\_CM0PLUS" Category: Factory Settings General Options Static Analysis Runtime Checking C/C++ Compiler Diagnostics Checksum Encodings Extra Options Config Library Input Optimizations Advanced Output List Assembler Output Converter Linker configuration file Custom Build Override default **Build Actions** \$PROJ\_DIR\$/stm32wl55xx\_flash\_cm0plus.icf Debugger Simulator Linker configuration file editor X CADI CMSIS DAP Vector Table Memory Regions Stack/Heap Sizes GDB Server I-jet J-Link/J-Trace ROM 0x0803FFFF TI Stellaris Nu-Link 0x20004000 0x20007FFF RAM PE micro ST-LINK Third-Party Driver Save TI MSP-FET TI XDS Cancel

Figure 11. CM0+ project - Linker configuration

- c. From Debugger tab, select ST-LINK as a debugger in the Driver field.

- d. Go to Debugger -> Download tab and tick the Use flash loader(s) check box.

AN5556 - Rev 1 page 13/39

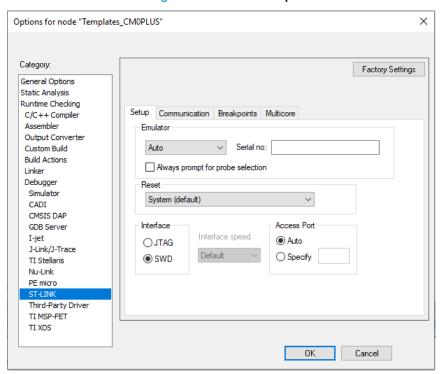

e. Go to Project -> Options -> ST-LINK -> Setup.

Figure 12. ST-LINK setup

- f. Select the Access Port:

- Auto: The access port 1 for Cortex-M0+ is automatically used.

- Manually: It is possible to manually select the access port (by putting 1 with CM0+, for example) .

- g. Select SWD in the communication Interface to use the SWO communication channel.

- h. Change the Reset type from software to system reset (resets the core and peripherals).

Note: This example uses software reset by default as it was developed with an old IDE version that contains some limitation with system reset

Go to the Multicore tab to enable the shared mode by checking the Enable multicore debugging/shared mode option.

AN5556 - Rev 1 page 14/39

#### 3.1.3 Loading and debugging both projects (EWARM)

Before downloading the project, connect to the NUCLEO-WL55JC board:

- Connect the STLINK-V3E programming and debugging tool on the NUCLEO-WL55JC board.

- Plug the USB cable to the CN1 USB STLINK connector of the board.

- LED6 lights up red when the ST-LINK is connected.

Note: This figure is not contractual.

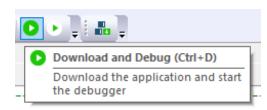

Download the Templates\_CM4 project and start a debug session by pressing the download and debug button

Figure 14. Download and Debug button

AN5556 - Rev 1 page 15/39

2. Execute the code until the instruction that sets the C2BOOT (see the figure below). This project boots the Cortex-M0+ by setting the C2BOOT bit in PWR\_CR4.

Figure 15. Release the CPU2 from holding

```

/* Reset of all peripherals, Initializes the Flash interface and the Systick. 1/

HAL_Init();

/* USER CODE BEGIN Init */

/* USER CODE END Init */

/* Configure the system clock */

SystemClock_Config();

/* Boot CPU2 */

HAL_PWREx_ReleaseCore(PWR_CORE_CPU2);

/* USER CODE BEGIN SysInit */

/* USER CODE END SysInit */

/* Initialize all configured peripherals */

/* USER CODE BEGIN 2 */

/* USER CODE END 2 */

/* Infinite loop */

/* USER CODE BEGIN WHILE */

while (1)

/* USER CODE BEGIN 3 */

/* USER CODE END 3 */

/* USER CODE END WHILE */

```

- 3. Download the Templates\_CM0PPLUS project.

- 4. Start a debug session.

#### 3.2 Known limitations (EWARM)

- When using the software reset option, the first time, to download with the Cortex-M0+ (Flash memory empty), the download is done with success but there is a HardFault message that is displayed all along the debug session.

- The system reset option is not functional from debug session: a HardFault error is generated when applying a system reset from a debug session.

AN5556 - Rev 1 page 16/39

### 4 Using MDK-ARM

The MDK-ARM (from Keil) is installed by default in the C: \Keil directory: the installer creates a start menu  $\mu$ Vision® 5 shortcut.

In this section, MDK-ARM v5.32 with an internal pack for STM32WL5x (Keil.STM32WLxx\_DFP.1.0.8), and a project template from STM32Cube FW WL V1.0.0 are used.

Note: All required packs are available for download from the official Arm Keil web site.

#### 4.1 Dual-core debug steps (MDK-ARM)

#### 4.1.1 CM4 project settings (MDK-ARM)

This section outlines the settings of the CM4 project, and uses a project template from STM32Cube\_FW\_WL\_V1.0.0 named *Templates\_CM4*.

1. Open the *Template DualCore* project under

\STM32Cube FW WL V1.0.0\Projects\NUCLEO-WL55JC\Templates\DualCore\MDK-ARM.

This project is used to work on both cores at the same time. This project appears now in the *Project Explorer* view as shown in the figure below.

Figure 16. Project explorer view

AN5556 - Rev 1 page 17/39

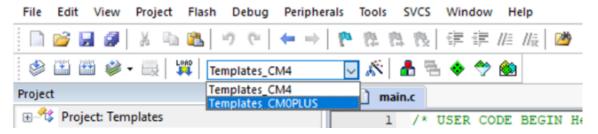

- Set the Templates\_CM4 project as active, and ensure that the settings are compatible with the options below.

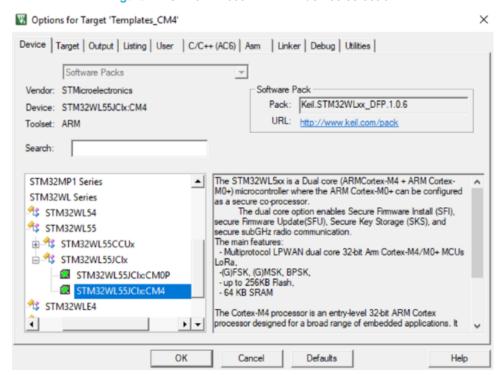

- a. Select the correct device by opening the *Configuration* window and selecting:

\*Project -> Options for Target -> Device then select the STM32WL55JClx:CM4 device from the list.

Figure 17. STM32WL55JClx - CM4 device selection

AN5556 - Rev 1 page 18/39

b. From *Project -> Options for Target -> Target -> Read/Only Memory Areas* section, ensure that the right memory area is selected: Boot from main Flash memory at 0x0800 0000 and Boot from SRAM1 memory at 0x2000 0000.

Options for Target 'Templates\_CM4' Device Target Output Listing User | C/C++ (AC6) | Asm | Linker | Debug | Utilities | Code Generation STMicroelectronics STM32WL55JClx:CM4 ARM Compiler: Use default compiler version 6 ▼ Xtal (MHz): 12.0 Operating system: None System Viewer File: □ Big Endian ✓ Use MicroLIB STM32WL5x\_CM4.svd Use Custom File Read/Write Memory Areas Read/Only Memory Areas Size Startup default off-chip default off-chip Size Nolnit ROM1: RAM1: ROM2: RAM2: ROM3: RAM3: on-chip on-chip IROM1: 0x8000000 IRAM1: 0x20000000 0x40000 **(•**) 0x10000 IROM2: IRAM2: OK Cancel Defaults Help

Figure 18. Memory area selection

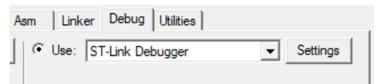

c. Select ST-LINK Debugger as the debugger from Project -> Options for Target -> Debug.

The NUCLEO-WL55JC board contains an embedded debugger ST-LINK V3.

AN5556 - Rev 1 page 19/39

d. Go to Debugger -> Settings and check that the debugger is connected as in the figure below.

Cortex-M Target Driver Setup × Debug Trace | Flash Download | Debug Adapter SW Device Unit: ST-LINK/V3 IDCODE Device Name ▼ Shareable ST-Link **SWDIO** 0x6BA02477 ARM Core Sight SW-DP Up Serial Number 001700343038511234333935 Automatic Detection Version: HW: V3 FW: V3J7M2 C Manual Configuration Check version on start Delete Update IB len: AP: 0 Target Com Port: SW -Clock Req: 4 MHz Selected: 3.300 MHz Performance Profile: High Perf Debug -Connect & Reset Options Cache Options Download Options Connect: under Reset ▼ Reset: HW RESET ✓ Cache Code ▼ Verify Code Download ✓ Cache Memory ▼ Download to Flash Stop after Reset Reset after Connect

OK

Cancel

Figure 20. Debug settings tab

e. Enable the dual-core debug by checking *Shareable ST-Link* in order to be able to debug both cores simultaneously.

Note: To set up a multicore debugging using an ST-LINK debug probe, install the latest ST-LINK server.

- f. Select the Access Port (port 0 for Cortex-M4).

- g. Select the communication *Interface* as SWD to use the serial-wire output (SWO) communication channel (fewer pins than JTAG).

- h. Select the Connect and Reset Options.

- Connect under reset holds the hardware reset (HW RESET) signal active while connecting to the device.

- HW RESET performs a hardware reset by asserting the hardware reset (HW RESET) signal.

- i. Select the Download Options.

- Verify Code Download stops the CPU after the currently executed instruction.

- Download to Flash downloads the code to all memory area.

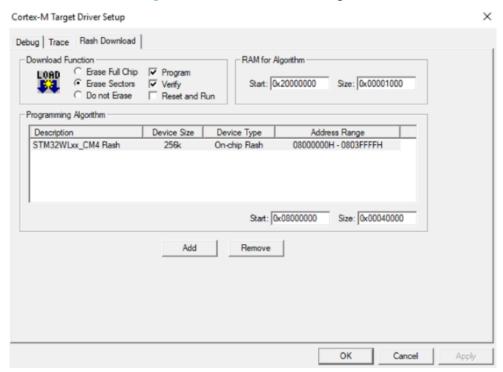

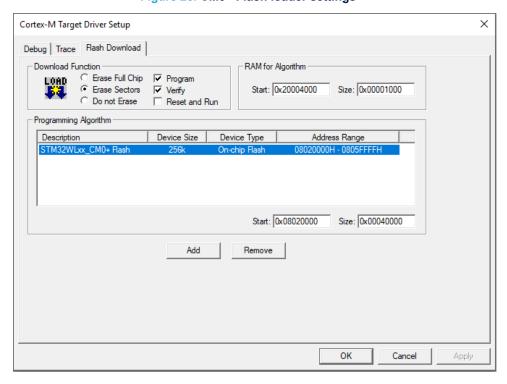

- j. From the Flash Download window shown in the figure below:

- Download Function is used to set the Flash operations.

- RAM for Algorithm defines the address space where programming algorithms are loaded and executed. Usually, the address space is located in the on-chip RAM.

- Program Algorithm contains the definitions for programming the Flash memory.

AN5556 - Rev 1 page 20/39

Figure 21. CM4 Flash loader settings

AN5556 - Rev 1 page 21/39

#### 4.1.2 CM0+ project settings (MDK-ARM)

This section outlines the settings of the CM0+ project, and uses a project template from STM32Cube\_FW\_WL\_V1.0.0 named *Templates\_CM0PLUS*.

- 1. Open the *Templates\_CM0PLUS* project in another instance and ensure that the settings are compatible with the options below.

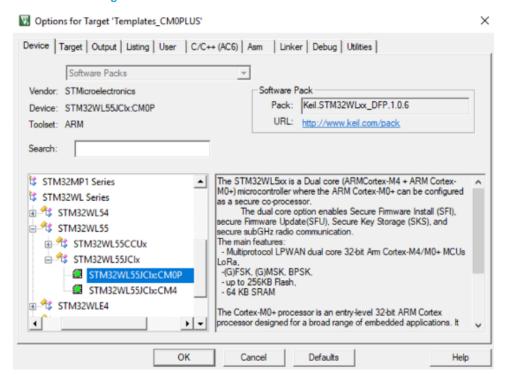

- a. Go to Project -> Options for Target 'Templates\_CM0PLUS'

- Select the correct device by opening the Configuration window and selecting

Project -> Options for Target -> Device then select the STM32WL55JCIx:CM0P device from the list.

Figure 22. STM32WL55JCIx - CM0+ device selection

AN5556 - Rev 1 page 22/39

c. From Project -> Options for Target -> Target -> Read/Only Memory Areas section, ensure that the right memory area is selected: Boot from main Flash memory at 0x0802 0000 and Boot from SRAM1 memory at 0x2000 4000.

Options for Target 'Templates\_CM0PLUS' × Device Target Output Listing User | C/C++ (AC6) | Asm | Linker | Debug | Utilities | STMicroelectronics STM32WL55JClx:CM0P Code Generation ARM Compiler: Use default compiler version 6 Xtal (MHz): 48.0 Operating system: None System Viewer File: ✓ Use MicroLIB ☐ Big Endian STM32WL5x\_CM0P.svd Use Custom File Read/Only Memory Areas Read/Write Memory Areas default off-chip Size Startup default off-chip Size NoInit ROM1: RAM1: ROM2: RAM2: ROM3: RAM3: on-chip on-chip IROM1: 0x8020000 IRAM1: 0x20004000 0x20000 0 0x4000 굣 IROM2: IRAM2: 0x2000C000 0x4000 П OK Cancel Defaults Help

Figure 23. Memory area selection

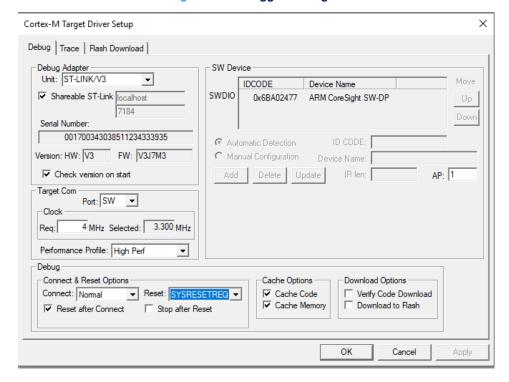

d. Go to Debugger -> Settings and check that the debugger is connected as in the figure below.

Figure 24. Debugger settings

AN5556 - Rev 1 page 23/39

- e. Enable the dual-core debug by checking *Shareable ST-Link* in order to be able to debug both cores simultaneously.

- f. Select the Access Port (port 1 for Cortex-M0+).

- g. Select the communication *Interface* as SWD to use the serial-wire output (SWO) communication channel (fewer pins than JTAG).

- h. Select the Connect and Reset Options.

- Connect Normal stops the CPU at the currently executed instruction after connecting.

- SYSRESETREQ performs a software reset by setting the SYSRESETREQ bit. The Cortex-M0+ core and the on-chip peripherals are reset (the only reset mode supported with Cortex-M0+).

- i. Select the Download Options.

- Verify Code Download stops the CPU after the currently executed instruction.

- Download to Flash downloads the code to all memory area.

- j. From the Flash Download window shown in the figure below:

- Download Function is used to set the Flash operations.

- RAM for Algorithm defines the address space where programming algorithms are loaded and executed. Usually, the address space is located in the on-chip RAM.

- Program Algorithm contains the definitions for programming Flash memory.

Figure 25. CM0+ Flash loader settings

#### 4.1.3 Loading and debugging both projects (MDK-ARM)

Before downloading the project, connect to the NUCLEO-WL55JC board (see Figure 13)

- Connect the STLINK-V3E programming and debugging tool on the NUCLEO-WL55JC board.

- Plug the USB cable to the CN1 USB STLINK connector of the board.

- LED6 lights up red when the ST-LINK is connected.

AN5556 - Rev 1 page 24/39

1. Build and download the *templates\_CM4* project using *Build and Load* button

Figure 26. Build and Load button

2. Start a debug session, then execute the application until the instruction that sets the C2BOOT (see the figure below). This project boots the Cortex-M0+ by setting the C2BOOT bit in PWR\_CR4.

Figure 27. Start debug session

Figure 28. Main.c sample code

```

/* Reset of all peripherals, Initializes the Flash interface and the Systick. |*/

HAL_Init();

/* USER CODE BEGIN Init */

/* USER CODE END Init */

/* Configure the system clock */

SystemClock Config():

Release the CPU2

/* Boot CPU2 */

HAL_PWREx_ReleaseCore(PWR_CORE_CPU2);

from holding

/* USER CODE BEGIN SysInit */

/* USER CODE END SysInit */

/* Initialize all configured peripherals */

/* USER CODE BEGIN 2 */

/* USER CODE END 2 */

/* Infinite loop */

/* USER CODE BEGIN WHILE */

while (1)

/* USER CODE BEGIN 3 */

/* USER CODE END 3 */

/* USER CODE END WHILE */

```

- Build and download the Templates\_CM0PLUS project.

- 4. Launch a debug session.

AN5556 - Rev 1 page 25/39

Note:

- Connect to the two cores simultaneously in shareable mode is only possible if the option "Stop after Reset" is disabled to be sure that the C2BOOT is not reset. The Cortex-M0 only boots after the Cortex-M4 has set C2BOOT in PWR\_CR4.

- It is possible to connect to each core separately (without shared mode), but the C2BOOT bit must be set before connecting to the Cortex-M0+.

AN5556 - Rev 1 page 26/39

#### 5 Debug and programming use cases with EWARM and MDK-ARM

This section details a specific use case by describing the support of the STM32WL5x devices within EWARM and MDK-ARM.

## 5.1 How to connect and download a Cortex-M0+ application while the full Flash memory is empty (EWARM)

Important: Before connecting to the Cortex-M0+ core, ensure that the C2BOOT bit in PWR\_CR4 is enabled.

With the following steps, a Cortex-M0+ application can be downloaded while the full Flash memory is empty.

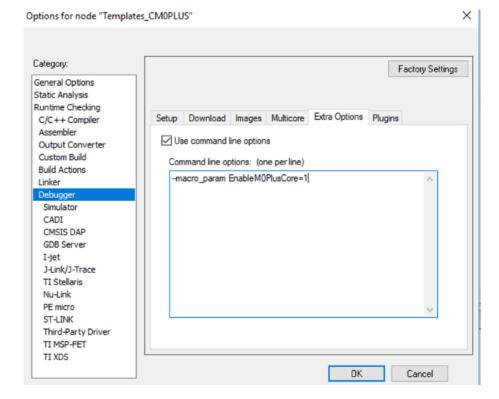

1. The C2BOOT must be automatically set before the AP1 connection for the download step, by adding the extra option --macro\_param EnableM0PlusCore =1 from Project option -> Debugger -> Extra options.

Figure 29. Enable Cortex-M0+ core

- 2. Go to the Project -> Option -> ST-LINK -> Setup and select the reset mode as system reset.

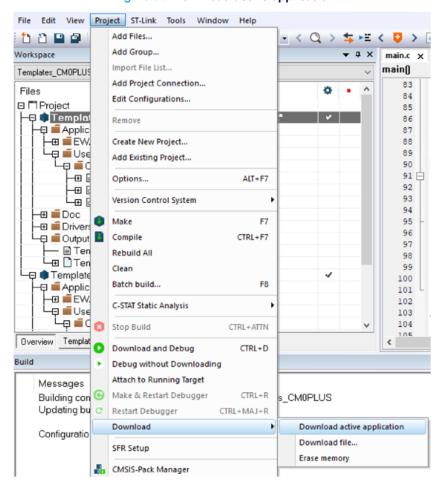

- 3. Build the application and go to *Project -> Download -> Download active application* to program the Cortex-M0+ application within the Flash memory at 0x0802 0000.

AN5556 - Rev 1 page 27/39

4. Download the active application to the target without launching a full debug session by using *Project -> Download -> Download active application*.

Figure 30. Download active application

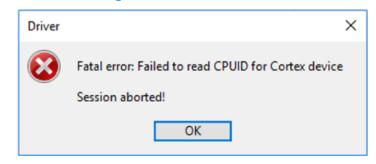

The following error message indicates that the C2BOOT is not set. The IDE tries to connect with several attempts if necessary, until a timeout of 1 s (to wait eventual C2BOOT enabling from the application), else the IDE returns an error to indicate that the AP1 is not accessible.

Figure 31. Error - AP1 not accessible

AN5556 - Rev 1 page 28/39

## How to connect and download a Cortex-M0+ application while the full Flash memory is empty (MDK-ARM)

With the following steps, a Cortex-M0+ application can be downloaded while the full Flash memory is empty.

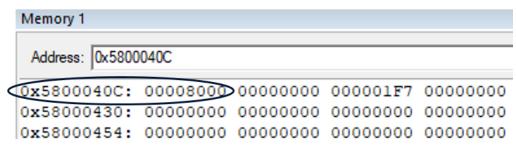

- 1. The C2BOOT must be automatically set before the AP1 connection for the download step.

- Connect to AP0 using MDK-ARM (see Section 4.1.1 ).

- Open the Memory window from View > Memory views.

- Write 0x0000 8000 in PWR CR4 (at the address 0x5800 040C).

Figure 32. Enable CPU2 using MDK-ARM

- 2. Go to the *Debug* tab and check that the debugger is connected like in Figure 24.

- 3. Build the application and go to *Flash -> Download* to program the active application to the target without launching a full debug session.

Figure 33. Download option

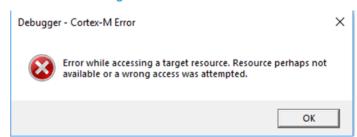

When trying to do the same manipulation before setting C2BOOT, an error message appears that indicates that the AP1 is not accessible.

Figure 34. AP1 not accessible

AN5556 - Rev 1 page 29/39

#### 6 Secure programming

This section describes the steps needed to enable the security in order to protect the memory areas (Flash memory, SRAM1 and SRAM2) from being accessed by any non-authorized bus master.

SRAM1 and SRAM2 areas are only secure when the Flash memory security is enabled (ESE = 1 and FSD = 0).

#### **Secure Flash memory**

The secure Flash memory area:

- starts at Flash memory base address + (SFSA[6:0] x 0x0800) included

where SFSA[6:0] is the secure Flash memory start address and contains the start address of the first 2-Kbyte page of the secure Flash memory area.

- · ends at Flash memory last address

Note: When the CPU2 security is enabled, the minimum CPU2 secure area size is one sector (2 Kbytes).

For example, with a CPU2 secure area from 0x0802 7000 (included) to 0x0803 FFFF (included), FLASH\_SFR must be programmed with SFSA = 0x4E.

The ESE flag in FLASH\_OPTR indicates if the CPU2 security is enabled. Any CPU1 access to a CPU2 security area triggers RDERR or WRPERR flag error.

#### Secure non-backup SRAM1

The secure non-backup SRAM1 area:

- starts at non-backup SRAM1 base address + (SNBRSA[4:0] x 0x0400) included where SNBRSA[4:0] is the secure non-backup SRAM1 start address and contains the start address of the first 1-Kbyte page of the secure non-backup SRAM1 area.

- ends at non-backup SRAM1 last address

For example, with a CPU2 secure SRAM1 area from 0x2000 6C00 (included) to 0x2000 7FFF (included), FLASH\_SRRVR must be programmed with SNBRSA = 0x1B.

Any CPU1 read access returns zero data. A write access to a CPU2 secure SRAM1 area is discarded and generates an illegal access event.

Note: When NBRSD is set to 1, the SRAM1 is non-secure.

#### **Secure SRAM2**

The secure SRAM2 area:

- starts at SRAM2 base address + (SBSRA[4:0] x 0x0400) included where SBSRA[4:0] is the secure SRAM2 start address and contains the start address of the first 1-Kbyte page of the secure SRAM2 area.

- ends at SRAM2 last address

For example, with a CPU2 secure SRAM2 area from 0x2000 A800 (included) to 0x2000 FFFF (included), FLASH SRRVR must be programmed with SBSRA = 0x0A.

Any CPU1 read access returns zero data. A write access to a CPU2 secure SRAM2 area is discarded and generates an illegal access event.

Note: When BRSD is set to 1, the SRAM2 is non-secure.

AN5556 - Rev 1 page 30/39

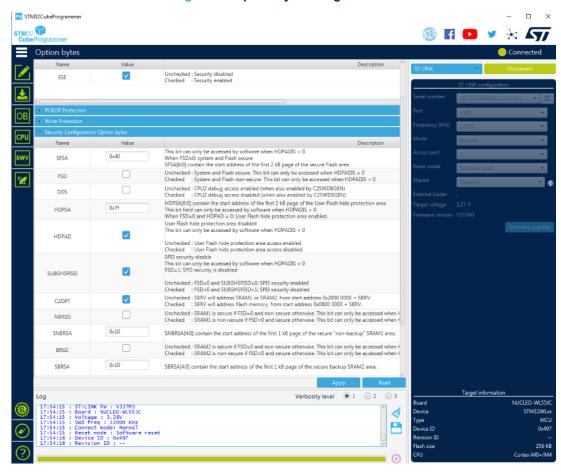

#### **Option-byte setup**

Before securing the system and memories as detailed in the next sections, the option bytes must be configured as follows, using the STM32CubeProgrammer tool:

- FSD = 0 to enable the overall system security

- SFSA[6:0] = 0x40 in FLASH SFR to secure the second half of the Flash memory area

- SNBRSA[4:0] = 0x10 and NBRSD = 0 in FLASH\_SRRVR to secure the second half of the non-backup SRAM1

- SBRSA[4:0] = 0x10 and BRSD = 0 in FLASH SRRVR to secure the second half of the backup SRAM2

Figure 35. Option-byte configuration

#### 6.1 Secure programming using EWARM

The steps below are needed to perform a secure programming using the NUCLEO\_WL55JC board and EWARM:

- 1. Ensure that all option bytes are configured as in the introduction of Section 6 Secure programming.

- 2. Open the CM4 project and ensure that all project options are configured as described in Section 3.1.1 .

- 3. Open the CM0+ project and ensure that all project options are configured as described in Section 3.1.2 .

AN5556 - Rev 1 page 31/39

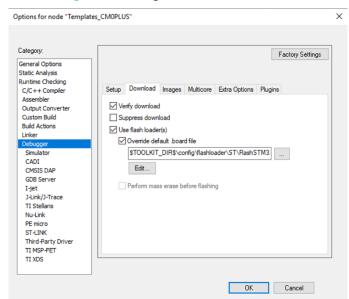

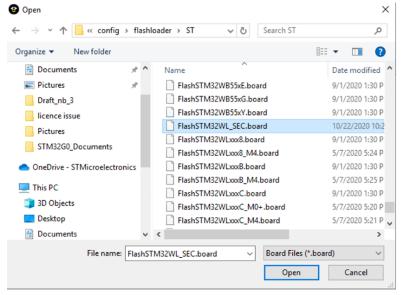

4. Go to *Project options -> Debugger -> Download* tab from the CM0+ project and replace the flashloader selected by *FlashSTM32WL\_SEC.board*, that is available under

C:\Program Files (x86)\IAR Systems\Embedded Workbench  $8.4_3\$ config\flashload er\ST.

Figure 36. Change the default flashloader

Figure 37. Select the secure flashloader

- 5. Build and download the Cortex-M4 application.

- Set the C2BOOT to perform CPU2 (Cortex-M0+) boot in PWR\_CR4.

- 7. Build and download the Cortex-M0+ application: the Flash memory programming is performed using the JTAG interface.

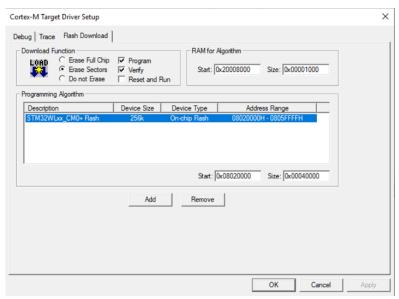

#### 6.2 Secure programming using MDK-ARM

The steps below are needed to perform a secure programming using the NUCLEO\_WL55JC board and MDK-ARM:

1. Ensure that all option bytes are configured as in the introduction of Section 6.

AN5556 - Rev 1 page 32/39

- 2. Open the CM4 project and ensure that all project options are configured as described in Section 4.1.1 .

- 3. Open the CM0+ project and ensure that all project options are configured as described in Section 4.1.2 .

- 4. Go to *Project options -> Debugger > Flash Download* tab and update the flashloader execution address in *RAM for Algorithm* with a secure SRAM address.

Figure 38. Change the flashloader execution address

- 5. Build and download the Cortex-M4 application.

- 6. Set the C2BOOT to perform CPU2 (Cortex-M0+) boot in PWR\_CR4.

- 7. Build and download the Cortex-M0+ application: the Flash memory programming is performed using the JTAG interface.

AN5556 - Rev 1 page 33/39

## **Revision history**

**Table 2. Document revision history**

| Date       | Version | Changes          |

|------------|---------|------------------|

| 2-Dec-2020 | 1       | Initial release. |

AN5556 - Rev 1 page 34/39

### **Contents**

| 1    | Prere  | equisite | 9\$                                                                                | 2    |

|------|--------|----------|------------------------------------------------------------------------------------|------|

| 2    | STM    | 32WL5x   | c architecture                                                                     | 3    |

|      | 2.1    | Access   | s port                                                                             | 3    |

|      | 2.2    | CPU2 I   | boot                                                                               | 3    |

|      | 2.3    | Debug    | support                                                                            | 3    |

|      | 2.4    | Cross-t  | trigger interface (CTI)                                                            | 4    |

|      | 2.5    | Global   | security controller (GTZC)                                                         | 4    |

|      | 2.6    | Secure   | e configuration (ESE/FSD option bits)                                              | 5    |

| 3    | Usin   | g EWAF   | RM                                                                                 | 6    |

|      | 3.1    | Dual-co  | ore debug steps (EWARM)                                                            | 6    |

|      |        | 3.1.1    | CM4 project settings (EWARM)                                                       | 6    |

|      |        | 3.1.2    | CM0+ project settings (EWARM)                                                      | . 12 |

|      |        | 3.1.3    | Loading and debugging both projects (EWARM)                                        | . 15 |

|      | 3.2    | Known    | limitations (EWARM)                                                                | . 16 |

| 4    | Usin   | g MDK-   | ARM                                                                                | .17  |

|      | 4.1    | Dual-co  | ore debug steps (MDK-ARM)                                                          | . 17 |

|      |        | 4.1.1    | CM4 project settings (MDK-ARM)                                                     | . 17 |

|      |        | 4.1.2    | CM0+ project settings (MDK-ARM)                                                    | . 22 |

|      |        | 4.1.3    | Loading and debugging both projects (MDK-ARM)                                      | . 24 |

| 5    | Debu   | ւց and լ | programming use cases with EWARM and MDK-ARM                                       | .27  |

|      | 5.1    |          | connect and download a Cortex-M0+ application while the full Flash memor (EWARM)   | •    |

|      | 5.2    |          | connect and download a Cortex-M0+ application while the full Flash memor (MDK-ARM) | •    |

| 6    | Secu   | ire prog | gramming                                                                           | .30  |

|      | 6.1    | Secure   | e programming using EWARM                                                          | . 31 |

|      | 6.2    | Secure   | e programming using MDK-ARM                                                        | . 32 |

| Rev  | ision  | history  |                                                                                    | .34  |

| Cor  | ntents |          |                                                                                    | .35  |

| List | of tab | oles     |                                                                                    | 37   |

| List of figures. |  | 38 |

|------------------|--|----|

|------------------|--|----|

## **List of tables**

| Table 1. | Debug features of Cortex-M cores | 4 |

|----------|----------------------------------|---|

| Гable 2. | Document revision history        | 4 |

AN5556 - Rev 1 page 37/39

## **List of figures**

| Figure 1.  | Block diagram of debug support infrastructure | . 3 |

|------------|-----------------------------------------------|-----|

| Figure 2.  | Embedded cross trigger                        | . 4 |

| Figure 3.  | EWARM project explorer view                   | . 6 |

| Figure 4.  | STM32WL55JC_M4 device selection               | . 7 |

| Figure 5.  | CM4 project - Linker configuration            | . 8 |

| Figure 6.  | Debugger setup                                | . 9 |

| Figure 7.  | Flash loader selection                        | . 9 |

| Figure 8.  | ST-LINK setup                                 | 10  |

| Figure 9.  | Shared mode activation                        | 11  |

| Figure 10. | ST32WL55JC_M0+ device selection               | 12  |

| Figure 11. | CM0+ project - Linker configuration           | 13  |

| Figure 12. | ST-LINK setup                                 | 14  |

| Figure 13. | STM32WL55JC NUCLEO board in connected status  | 15  |

| Figure 14. | Download and Debug button                     | 15  |

| Figure 15. | Release the CPU2 from holding                 |     |

| Figure 16. | Project explorer view                         |     |

| Figure 17. | STM32WL55JCIx - CM4 device selection          |     |

| Figure 18. | Memory area selection                         | 19  |

| Figure 19. | Debug probe selection                         | 19  |

| Figure 20. | Debug settings tab                            |     |

| Figure 21. | CM4 Flash loader settings                     |     |

| Figure 22. | STM32WL55JCIx - CM0+ device selection         |     |

| Figure 23. | Memory area selection                         |     |

| Figure 24. | Debugger settings                             |     |

| Figure 25. | CM0+ Flash loader settings                    |     |

| Figure 26. | Build and Load button                         |     |

| Figure 27. | Start debug session                           |     |

| Figure 28. | Main.c sample code                            |     |

| Figure 29. | Enable Cortex-M0+ core                        |     |

| Figure 30. | Download active application                   |     |

| Figure 31. | Error - AP1 not accessible                    |     |

| Figure 32. | Enable CPU2 using MDK-ARM                     |     |

| Figure 33. | Download option                               |     |

| Figure 34. | AP1 not accessible                            |     |

| Figure 35. | Option-byte configuration                     |     |

| Figure 36. | Change the default flashloader                |     |

| Figure 37. | Select the secure flashloader                 |     |

| Figure 38. | Change the flashloader execution address      |     |

|            |                                               |     |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2020 STMicroelectronics – All rights reserved

AN5556 - Rev 1 page 39/39