# Current ranges and current setpoint - settings and out of range exceptions

### Introduction

This document is intended to integrate the information provided in the L9305 product datasheet, about how to set current ranges and current setpoint and how to read actual current through AVGCUR register, with a particular focus on out of range values and related device behavior.

### 1 Current setpoint programming and average current reading

The target average current set point is independently programmable for each channel through the dedicated 13-bit long SPI register (Channel\_x.Current\_Set\_Point). The current resolution is programmable in two resolution steps through the HILOAD bit (D[8] in Channel\_x.Configuration1) which will also set the maximum regulated current.

Below is a brief summary for using HILOAD to select current range and resolution:

HILOAD = 0 → Normal current mode - Single bit resolution = 0.25 mA - Max Avg. Current 1.5 A.

Target Average Current = Setpoint[12:0]

$$\times$$

0.25 (1)

HILOAD = 1 → High current mode - Single bit resolution = 0.33 mA - Max Avg. Current 2.0 A.

$$Target\ Average\ Current = Setpoint[12:0] \times 0.33 \tag{2}$$

The maximum guaranteed ripple current for the device's specified accuracy is 0.5 A peak to peak for HILOAD = 0 and 0.66 A peak to peak for HILOAD = 1, so that the max load current for correct current control is:

- 1500 mA + 250 mA = 1750 mA for HILOAD = 0

- 2000 mA + 330 mA = 2330 mA for HILOAD = 1

If the channel is enabled and programmed with 0x0000h current setpoint, the power output is forced with duty cycle 0 (recirculation path fully on) and the current measurement is disabled; Setpoint codes higher than 0x1770h are reserved for calibration and offset compensation purposes: in case such codes are selected, the accuracy is not guaranteed.

The solenoid current, as a result of internal current sensing, calibration correction and final average calculation over an entire PWM period, is available for SPI reading from Channel\_x.AVGCUR register. Independent of HW or SW mode current control selection, the average current calculation cycle starts at each PWM switch ON event and ends at the next PWM switch ON event.

The average current calculated is immediately available to the SPI output register through the dedicated 14-bit field in SPI register Channel x.AVGCUR:

HILOAD = 0 → Normal current mode - Single bit resolution = 0.25 mA

$$Average\ Current = 2\ Complement(AvgCur[13:0]) \times 0.25$$

(3)

HILOAD = 1 → High current mode - Single bit resolution = 0.33 mA

$$Average\ Current = 2\ Complement(AvgCur[13:0]) \times 0.33 \tag{4}$$

In case the Driver input signal is stuck high or low for a time period longer than  $T_{pwm\_max}$ , the TMOUT warning flag is set in Channel\_x.PWMSENSE register and the average current is evaluated only for  $T_{pwm\_max}$ . After timeout, the average current and PWM code calculations restart automatically.

When CHx.SETPOINT = 0000 and channel x is controlled Hardware mode (CONFIGURATION1.D[2] = 0), then current measurement is disabled and AVGCUR always returns all '0', even if channel x is driven full-on.

### 1.1 Involved SPI register

Basically, involved SPI registers are the following ones:

**Configuration 1 - CONFIGURATION1**

Address Channel\_X\_BaseAddress + 0x02

Type Read/Write

Description Configuration register provides information related to channel configuration

Table 1. CONFIGURATION1 register detail

| Register bit | Field name/description | Default values | Туре       |

|--------------|------------------------|----------------|------------|

| [15]         | Unused                 | 0              | Read       |

| [14]         | OFS_CMP_DIS:           | 0              | Read/Write |

AN5668 - Rev 1 page 2/14

| Register bit | Field name/description                        | Default values | Туре       |

|--------------|-----------------------------------------------|----------------|------------|

|              | 0: Current Sense Offset Compensation Active   |                |            |

|              | 1: Current Sense Offset Compensation disabled |                |            |

|              | CALIBRATION_DIS:                              |                |            |

| [13]         | 0: Digital Current Sense Calibration Active   | 0              | Read/Write |

|              | 1: Digital Current Sense Calibration Disabled |                |            |

| [12:11]      | Unused                                        | 0              | Read       |

|              | Solenoid Logic BIST:                          |                |            |

| [10]         | 0: Logic BIST Reset                           | 0              | Read/Write |

|              | 1: Logic BIST Enabled                         |                |            |

|              | Td_Blank:                                     |                |            |

| [9]          | 0: Long Blanking Time                         | 0              | Read/Write |

| [0]          | 1: Short Blanking Time                        |                |            |

|              | HILOAD: Current Sense Scale:                  |                |            |

| [8]          | 0: 1.5 A Max Current Range                    | 0              | Read/Write |

|              | 1: 2.0 A Max Current Range                    |                |            |

| [7]          | Unused                                        | 0              | Read       |

|              | Overcurrent threshold selection:              |                |            |

| [6]          | 0: 4 A Theshold                               | 0              | Read/Write |

|              | 1: 5 A Threshold                              |                |            |

|              | Enable OFF Diagnosis:                         |                |            |

| [5]          | 0: Disabled (OFF)                             | 0              | Read/Write |

| [v]          | 1: Enabled                                    |                |            |

| [4]          | Unused                                        | 0              | Read       |

|              | Solenoid Load Configuration:                  |                |            |

| [3]          | 0: Low Side                                   | 0              | Read/Write |

|              | 1: High Side                                  |                |            |

|              | Current Feedback Control Mode:                |                |            |

| [2]          | 0: HW Feedback                                | 0              | Read/Write |

| [-]          | 1: SW Feedback                                |                |            |

|              | Output Slew Rate:                             |                |            |

|              | 00: 0.4 V/μs                                  |                |            |

| [1:0]        | 01: 1.0 V/µs                                  | 0              | Read/Write |

| -            | 10: 4.0 V/µs                                  |                |            |

|              | 11: 8.0 V/µs                                  |                |            |

In order to avoid thermal power dissipation and device heating, it is better to choose Output Slew Rate "10: 4.0 V/ $\mu$ s" or "11: 8.0 V/ $\mu$ s".

Output Slew Rate must be chosen properly also in relation to the operating PWM switching frequency, in particular when high PWM switching frequencies are required by the driven load:

- At high operating PWM switching frequencies, current accuracy could be affected and degraded by a too slow Output Slew Rate, because high flat duty cycle phase of Load\_solX voltage waveform is too short with respect to the PWM period, so the load ON phase is not effective in driving the load properly.

- At high operating PWM switching frequencies and higher setpoint currents (~1 A, 1.5 A), channel overheating could occur due to a too slow Output Slew Rate, thus causing channel thermal shutdown.

HILOAD = 0/1 sets the regulated current full scale.

AN5668 - Rev 1 page 3/14

#### **Current Setpoint - SETPOINT**

Address Channel\_X\_BaseAddress + 0x06

Type Read/Write

Description Register stores current setpoint code (HW mode current control). Current Control SETPOINT is coded into 13 bits. Current

value depends on HILOAD bit

Table 2. SETPOINT register detail

| Register bit | Field name/description                                       | Default values | Туре       |

|--------------|--------------------------------------------------------------|----------------|------------|

|              | Auto Limit: Activates the transient mode on setpoint change: |                |            |

| [15]         | 0: Inactive                                                  | 0              | Read/Write |

|              | 1: Active                                                    |                |            |

| [14:13]      | Unused                                                       | 0              | Read       |

| [12:0]       | Current Setpoint Code                                        | All "0"        | Read/Write |

Current setpoint formulas: refer to Eq. (1) and Eq. (2).

The maximum guaranteed ripple current for the device's specified accuracy is 0.5 A peak to peak for HILOAD = 0 and 0.66 A peak to peak for HILOAD = 1. If the channel is enabled and programmed with 0x0000h current setpoint, the power output is forced with duty cycle 0 (recirculation path fully on) and the current measurement is disabled; Setpoint codes higher than 0x1770h are reserved for calibration and offset compensation purposes: in case such codes are selected, the accuracy is not guaranteed.

#### **Average Current - AVGCUR**

Address Channel\_X\_BaseAddress + 0x0B

Type RO

Description Stores Average Current Code in 1 PWM period

Table 3. AVGCUR register detail

| Register bit | Field name/description                                | Default values | Type |

|--------------|-------------------------------------------------------|----------------|------|

| [15:14]      | Unused                                                | 0              | Read |

| [13:0]       | AVGCUR: Average current code (signed) in 1 PWM period | All "0"        | Read |

When CHx.SETPOINT = 0000 and channel x is controlled Hardware mode (CONFIGURATION1.D[2] = 0), then current measurement is disabled and AVGCUR always returns all '0', even if channel x is driven full-on.

AN5668 - Rev 1 page 4/14

Note:

## 2 Device behavior for out of range current setpoint

Given a load, a driver HS/LS configuration and a PWM frequency, DUT accepts setpoint values over 0x1770h and current changes accordingly up to the maximum value allowed by VBATP voltage.

In the cases of the following analysis:

- Fixed frequency current control, CTRLCFG, D[11] = 0

- PWM control frequency = 2 KHz, CTRLCFG, D[10:0] = 32h

For VBATP = 13.5 V, maximum current is 2 A both for HILOAD = 0 and for HILOAD = 1

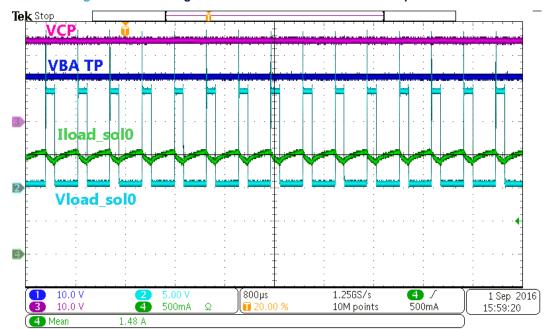

#### Case HILOAD = 0 and setpoint 0x1770h

Current is set to 1.5 A and PWM regulation is executed correctly. Register AVGCUR value is around 1770h.

Figure 1. Current regulation with HILOAD = 0 and Iload setpoint = 1770h

AN5668 - Rev 1 page 5/14

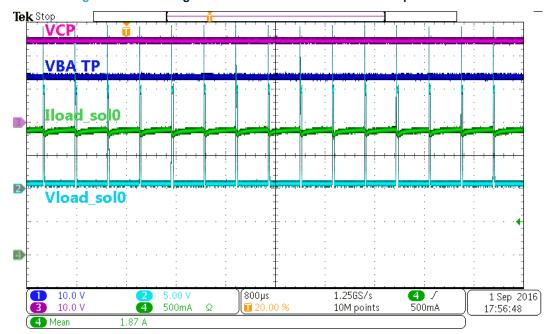

#### Case HILOAD = 0 and setpoint 0x1D4Ch (7500 DEC)

Current is set to 1.875 A and PWM regulation is executed correctly. Register AVGCUR value is around 1D4Ch.

Figure 2. Current regulation with HILOAD = 0 and Iload setpoint = 1D4Ch

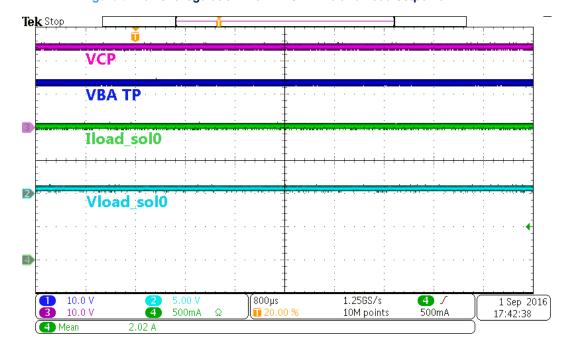

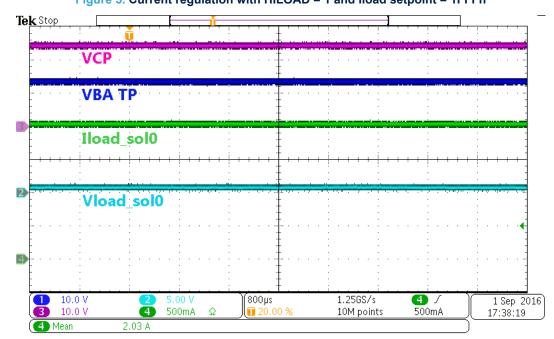

### Case HILOAD = 0 and setpoint 0x1FFFh

Current is set to around 2 A and PWM regulation is full on with 100% duty cycle. Register AVGCUR value is around 1F40h (2 A) and follows load current evolution.

Figure 3. Current regulation with HILOAD = 0 and Iload setpoint = 1FFFh

AN5668 - Rev 1 page 6/14

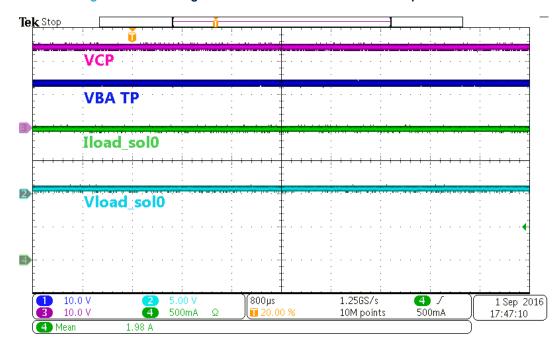

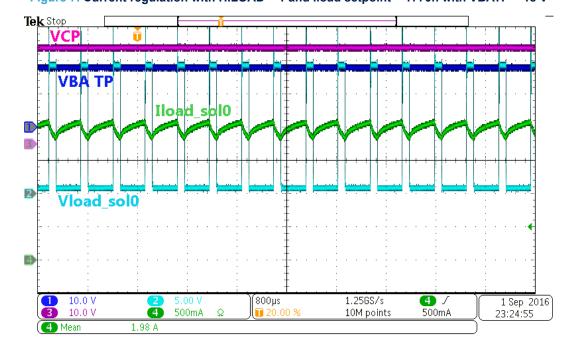

#### Case HILOAD = 1 and setpoint 0x1770h

Current is set to around 2 A and PWM regulation is full on with 100% duty cycle. Register AVGCUR value is around 1770h (2 A) and follows load current evolution.

Figure 4. Current regulation with HILOAD = 1 and Iload setpoint = 1770h

#### Case HILOAD = 1 and setpoint 0x1FFFh

Current is set to around 2 A and PWM regulation is full on with 100% duty cycle. Register AVGCUR value is around 1770h (2 A) and follows load current evolution.

Figure 5. Current regulation with HILOAD = 1 and Iload setpoint = 1FFFh

AN5668 - Rev 1 page 7/14

As a further analysis some of the previous tests have been repeated with VBATP = 18 V

#### Case HILOAD = 0 and setpoint 0x1FFFh

Current is set to around 2.6 A and PWM regulation is full on with 100% duty cycle. Register AVGCUR VALUE is fixed 1E4Dh (1.939 A) and does not follow load current evolution: this is not correct.

VGP V VBA TP

Iload\_sol0

Vload\_sol0

1 10.0 V 2 5.00 V 800μs 1.25GS/s 4 / 1 Sep 2016 3 10.0 V 4 500mA Ω 10M points 500mA 23:15:39

Figure 6. Current regulation with HILOAD = 0 and Iload setpoint = 1FFFh with VBATP = 18 V

#### Case HILOAD = 1 and setpoint 0x1770h

Current is set to around 2 A and PWM regulation is executed correctly. Register AVGCUR value is around 1770h (2 A).

Figure 7. Current regulation with HILOAD = 1 and Iload setpoint = 1770h with VBATP = 18 V

AN5668 - Rev 1 page 8/14

#### Case HILOAD = 1 and setpoint 0x1FFFh

Current is set to around 2.6 A and PWM regulation is full on with 100% duty cycle. Register AVGCUR value is around 1E1Bh (2.569 A) and follows load current evolution.

Tek Stop VCP VBA TP Iload\_sol0 1 3 Vload\_sol0 800µs 1.25GS/s 10.0 V 2 Sep 2016 00:14:29 ð 500mA Ω 10.0 V 10M points 4 Mean 2.61 A

Figure 8. Current regulation with HILOAD = 1 and Iload setpoint = 1FFFh with VBATP = 18 V

AN5668 - Rev 1 page 9/14

# **Revision history**

**Table 4. Document revision history**

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 19-Apr-2021 | 1       | Initial release. |

AN5668 - Rev 1 page 10/14

## **Contents**

| 1  | Curi   | rent setpoint programming and average current reading | 2  |

|----|--------|-------------------------------------------------------|----|

|    | 1.1    | Involved SPI register                                 | 2  |

| 2  | Dev    | ice behavior for out of range current setpoint        | 5  |

| Re | vision | history                                               | 10 |

AN5668 - Rev 1

## **List of tables**

| Table 1. | CONFIGURATION1 register detail | 2  |

|----------|--------------------------------|----|

| Table 2. | SETPOINT register detail       | 4  |

| Table 3. | AVGCUR register detail         | 4  |

| Table 4. | Document revision history      | 10 |

AN5668 - Rev 1 page 12/14

# **List of figures**

| Figure 1. | Current regulation with HILOAD = 0 and Iload setpoint = 1770h                   | 5 |

|-----------|---------------------------------------------------------------------------------|---|

| Figure 2. | Current regulation with HILOAD = 0 and Iload setpoint = 1D4Ch                   | 6 |

| Figure 3. | Current regulation with HILOAD = 0 and Iload setpoint = 1FFFh                   | 6 |

| Figure 4. | Current regulation with HILOAD = 1 and Iload setpoint = 1770h                   | 7 |

| Figure 5. | Current regulation with HILOAD = 1 and Iload setpoint = 1FFFh                   | 7 |

| Figure 6. | Current regulation with HILOAD = 0 and Iload setpoint = 1FFFh with VBATP = 18 V | 8 |

| Figure 7. | Current regulation with HILOAD = 1 and Iload setpoint = 1770h with VBATP = 18 V | 8 |

| Figure 8. | Current regulation with HILOAD = 1 and Iload setpoint = 1FFFh with VBATP = 18 V | 9 |

AN5668 - Rev 1 page 13/14

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

AN5668 - Rev 1 page 14/14