## Getting started with STM32C0 MCU hardware development

### Introduction

This document is intended for system designers requiring an overview of the hardware implementation for development board features (such as power supply, clock management, reset control, boot mode settings, and debug management).

This document shows how to use the STM32C0 series, and describes the minimum hardware resources required to develop an application.

This document also includes detailed reference design schematics with the description of the main components, interfaces, and modes.

### **Reference documents**

- STM32C09xxB/xC devices datasheet (DS14720)

- STM32C011x4/x6 devices datasheet (DS13866)

- STM32C031x4/x6 devices datasheet (DS13867)

- STM32C051x6/x8 devices datasheet (DS14721)

- STM32C071x8/xB devices datasheet (DS14693)

- STM32C0x1 advanced Arm®-based 32-bit MCUs reference manual (RM0490)

- ESD protection of STM32 MCUs and MPUs application note (AN5612)

- STM32 microcontroller system memory boot mode application note (AN2606)

Note: All documents in this list are available on STMicroelectronics website www.st.com.

## 1 Power supplies and reset sources

This section describes the power supply schemes, the reset, and the power supply supervisor available on the STM32C0 series MCUs, which is based on an Arm<sup>®</sup> core.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

## 1.1 Power supplies

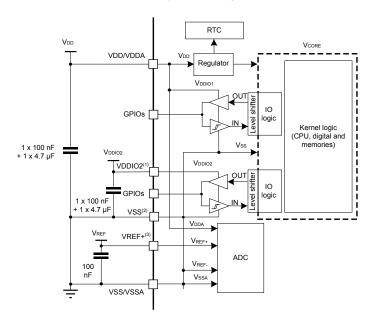

The STM32C0 MCUs require a 2.0 to 3.6 V operating supply voltage (V<sub>DD</sub>). Several different power supplies are provided to specific peripherals:

- $V_{DD} = 2.0 \text{ to } 3.6 \text{ V}$

- $V_{DD}$  is the external power supply for the internal regulator and the system analogs such as reset, power management, and internal clocks. It is provided externally through the VDD/VDDA pin. Note that the power-on reset happens when the  $V_{POR(max)}$  = 1.94 V threshold is crossed by  $V_{DD}$ , and that this value is below 2 V ( $V_{DD}$  recommended minimum value). Once this threshold is crossed, the functionality is guaranteed down to the power-down reset threshold  $V_{PDR(min)}$  = 1.92 V.

- $V_{DDA}$  = 2.0 to 3.6 V  $V_{DDA}$  is the analog power supply for the A/D converter. Its voltage level is identical to the  $V_{DD}$  voltage, as it is provided externally through VDD/VDDA pins ( $V_{DD}$  and  $V_{DDA}$  are shorted due to the low number of pins on the packages proposed for the STM32C0 series).

- $V_{DDIO1} = V_{DD}$  $V_{DDIO1}$  is the power supply for the I/Os. Its voltage level is identical to  $V_{DD}$  voltage as it is provided externally through VDD/VDDA pin ( $V_{DD}$  and  $V_{DDIO1}$  are shorted due to the low number of pins on the packages proposed for the STM32C0 series).

- V<sub>DDIO2</sub> = 1.6 to 3.6 V

V<sub>DDIO2</sub> is the power supply from the VDDIO2 pin for selected I/Os. Although the V<sub>DDIO2</sub> is independent of V<sub>DD</sub> or V<sub>DDA</sub>, it must not be applied without a valid V<sub>DD</sub>. This is available in some of the STM32C071xx MCUs (V<sub>DD</sub> and V<sub>DDIO2</sub> are shorted on the GP package). For further information, refer to the product datasheet.

- V<sub>REF+</sub> is the input reference voltage for the ADC. Its voltage level is identical to the V<sub>DD</sub> voltage as it is

provided externally through a VDD/VDDA pin. Except for the package with a separate VREF+ pin, V<sub>REF+</sub>

must be between 2 V and V<sub>DDA</sub>, or can be grounded when the ADC is not active.

- $V_{REF-}$  is bonded to  $V_{SS}$  and  $V_{SSA}$ , regardless of the package.

- V<sub>CORE</sub> is an embedded linear voltage regulator used to supply the V<sub>CORE</sub> internal digital power, the power supply for digital peripherals, the SRAM, and the flash memory. The flash memory is also supplied by V<sub>DD</sub>.

Table 1. Power supplies of STM32C0 MCUs

| Power supply       | STM32C0 series                                                            |

|--------------------|---------------------------------------------------------------------------|

| $V_{DD}$           | 2.0 to 3.6 V                                                              |

| V <sub>REF+</sub>  | V <sub>REF+</sub> must be between 2 V and V <sub>DDA</sub> <sup>(1)</sup> |

| V <sub>DDIO2</sub> | 1.6 to 3.6 V <sup>(2)</sup>                                               |

- This is only true for the packages where a dedicated VREF+ pin is present. In the other cases, VDD, VDDA, and VREF+ are shortened and correspond to the same voltage.

- This is only true for STM32C071xx devices where a dedicated VDDIO2 pin is present. In other STM32C071xx device V<sub>DD</sub>, V<sub>DDIO1</sub> and V<sub>DDIO2</sub> are shortened and correspond to the same voltage.

AN5673 - Rev 3 page 2/36

RTC VDD VCORE VDD/VDDA Regulator V<sub>DDIO1</sub> shifter Kernel logic Ю 1 x 100 nF (CPU, digital and GPIOs [ logic + 1 x 4.7 µF memories) Vss  $V_{DDA}$  $V_{REF}$ VREF-VREF+(1) VREF-ADC 100 nF VSSA VSS/VSSA

Figure 1. STM32C0 MCUs power supply without V<sub>DDIO2</sub>

Note:

Power supply pin pairs (VDD/VDDA and VSS/VSSA) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

Figure 2. STM32C0 MCUs power supply with V<sub>DDIO2</sub>

(1): Internally connected to  $V_{\text{DD}}$  on packages without VDDIO2 pin.

(1): Internally connected to the  $V_{\text{DDA}}$  on packages without VREF+ pin.

- (2): Internally connected to Vss on packages without VSS pin.

- (3): Internally connected to  $V_{\text{DDA}}$  on packages without VREF+ pin.

DT73921V2

Note:

Power supply pin pairs (VDD/VDDA, VDDIO2, VSS/VSSA, and VSS) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

AN5673 - Rev 3 page 3/36

## 1.2 Power supply supervisor

## 1.2.1 Power-on reset (POR)/power-down reset (PDR)/brownout reset (BOR)

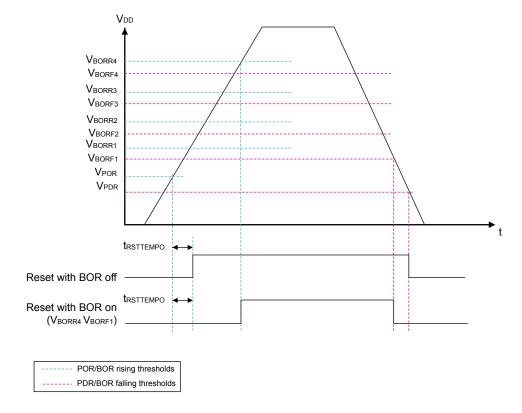

The devices feature an integrated power-on reset (POR)/power-down reset (PDR), coupled with a brownout reset (BOR) circuitry. The POR/PDR is active in all power modes.

The BOR can be enabled or disabled only through option bytes. It is not available in Shutdown mode.

When the BOR is enabled, four BOR levels can be selected through option bytes, with independent configuration for rising and falling thresholds. During power-on, the BOR keeps the device under reset until the  $V_{DD}$  supply voltage reaches the specified BOR rising threshold ( $V_{BORRx}$ ). At this point, the device reset is released and the system can start.

During power-down, when  $V_{DD}$  drops below the selected BOR falling threshold ( $V_{BORFx}$ ), the device is put under reset again.

Note: It is not allowed to configure the BOR falling threshold ( $V_{BORFx}$ ) to a value higher than the BOR rising threshold ( $V_{BORRx}$ ).

Figure 3. POR, PDR, and BOR thresholds

Note:

The reset temporization  $t_{RSTTEMPO}$  starts when  $V_{DD}$  crosses the  $V_{POR}$  threshold, indifferently from the configuration of the BOR option bits.

For more details on the brownout reset thresholds, refer to the electrical characteristics section in the corresponding datasheet.

### 1.3 Reset

This section describes the three types of reset on microcontrollers of the STM32C0 series, namely power reset, system reset, and RTC domain reset.

AN5673 - Rev 3 page 4/36

#### 1.3.1 Power reset

A power reset is generated when one of the following events occurs:

- Power-on reset (POR) or brownout reset (BOR).

- Exit from Standby mode.

- Exit from Shutdown mode.

Power and brownout reset set all registers to their reset values.

When exiting Standby mode, all registers in the  $V_{CORE}$  domain are set to their reset value. Registers outside the  $V_{CORE}$  domain (back up register, WKUP, IWDG, and Standby/Shutdown mode control) are not impacted.

When exiting Shutdown mode, the brownout reset is generated, resetting all registers.

### 1.3.2 System reset

System reset sets all registers to their reset values, except for the reset flags in the RCC control/status register 2 (RCC\_CSR2) and the registers in the RTC domain.

A system reset is generated when one of the following events occurs:

- Low level on the NRST (external reset).

- Window watchdog event (WWDG reset).

- Independent watchdog event (IWDG reset).

- Software reset (SW reset).

- Low-power mode security reset.

- Option byte loader reset.

- Power-on reset.

The reset source can be identified by checking the reset flags in the RCC CSR2 register.

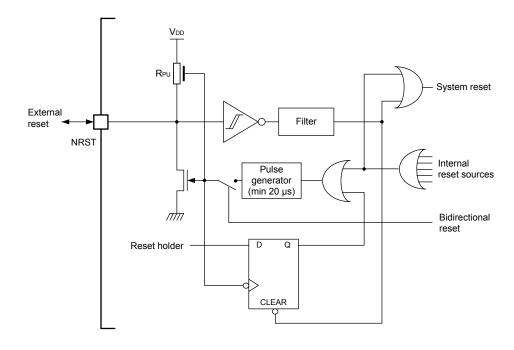

### NRST (external reset)

Through specific option bits, the PF2-NRST pin is configurable to operate as:

Reset input/output (default at device delivery)

A valid reset signal on the pin is propagated to the internal logic. Each internal reset source is led to a pulse generator, whose output drives this pin. The GPIO functionality (PF2) is not available. The pulse generator guarantees a minimum reset pulse duration of 20  $\mu$ s for each internal reset source to be output on the NRST pin. An internal reset holder option can be used, if enabled in the option bytes, to ensure that the pin is pulled low until its voltage meets the V<sub>IL</sub> threshold. This function makes possible the detection of internal reset sources by external components when the line faces a significant capacitive load. The BOOT0 pin sampling is done on any NRST rising edge that is caused by internal or external resets.

#### Reset input

In this mode, any valid reset signal on the NRST pin is propagated to the device internal logic. Resets generated internally by the device are not visible on the pin. The GPIO functionality (PF2) is not available. The BOOT0 pin sampling is done on POR, and on any subsequent NRST rising edge that is caused by external resets. Other internal resets do not trigger a new BOOT0 sampling.

#### • GPIO

In this mode, the pin can be used as PF2 standard GPIO. The reset function of the pin is not available. Reset is only possible from device internal reset sources and it is not propagated to the pin. The BOOT0 pin sampling is done on POR NRST rising edge only. Subsequent internal resets or transitions on PF2 GPIO do not trigger a new BOOT0 sampling.

AN5673 - Rev 3 page 5/36

Figure 4. Simplified diagram of the reset circuit

Note:

Upon power reset or wake up from shutdown mode, the NRST pin is configured as Reset input/output and driven low by the system until it is reconfigured to the expected mode when the option bytes are loaded, in the fourth clock cycle after the end of  $t_{rstempo}$ .

#### Software reset

The SYSRESETREQ bit in the Cortex<sup>®</sup>-M0+ application interrupt and the reset control register must be set to force a software reset on the device (refer to the programming manual PM0223).

#### Low-power mode security reset

To prevent critical applications from mistakenly enter a low-power mode, three low-power mode security resets are available. If enabled in option bytes, the resets are generated in the following conditions:

#### Entering Standby mode

This type of reset is enabled by resetting the nRST\_STDBY bit in user option bytes. In this case, whenever a Standby mode entry sequence is successfully executed, the device is reset instead of entering Standby mode.

### Entering Stop mode

This type of reset is enabled by resetting the nRST\_STOP bit in user option bytes. In this case, whenever a Stop mode entry sequence is successfully executed, the device is reset instead of entering Stop mode.

## Entering Shutdown mode

This type of reset is enabled by resetting the nRST\_SHDW bit in user option bytes. In this case, whenever a Shutdown mode entry sequence is successfully executed, the device is reset instead of entering Shutdown mode.

### Option byte loader reset

The option byte loader reset is generated when the OBL\_LAUNCH bit (bit 27) is set in the FLASH\_CR register. This bit is used to launch the option of byte loading by software.

AN5673 - Rev 3 page 6/36

## 1.3.3 RTC domain reset

The RTC domain has two specific resets. An RTC domain reset is generated when one of the following events occurs:

- Software reset, triggered by setting the RTCRST bit in the RCC\_CSR1 register.

- V<sub>DD</sub> power on.

An RTC domain reset only affects the LSE oscillator, the RTC, and the register RCC\_CSR1.

AN5673 - Rev 3 page 7/36

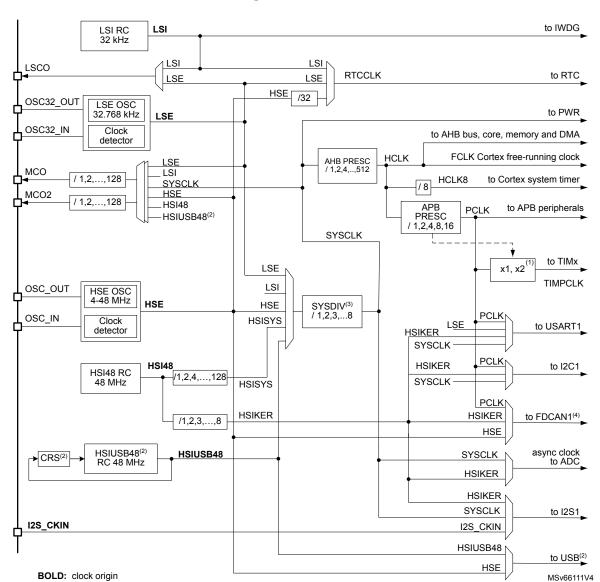

## 2 Clocks

The microcontrollers of the STM32C0 series provide the following clock sources producing primary clocks:

- HSI48 RC, a high-speed fully integrated RC oscillator producing HSI48 clock (48 MHz)

- HSIUSB48 RC, a high-speed fully integrated RC oscillator producing HSIUSB48 clock for USB (about 48 MHz). Only available for STM32C071xx devices.

- HSE OSC, a high-speed oscillator with external crystal/ceramic resonator or external clock source, producing HSE clock (4 to 48 MHz)

- LSI RC, a low-speed fully integrated RC oscillator producing LSI clock (about 32 kHz)

- LSE OSC, a low-speed oscillator with external crystal/ceramic resonator or external clock source, producing LSE clock (accurate 32.768 kHz or external clock up to 1 MHz)

- I2S\_CKIN, a pin for direct clock input for the I2S1 peripheral

When not in use, each oscillator can be switched on or off independently to optimize power consumption. For functional details, check the following subsections. For electrical characteristics of the internal and external clock sources, refer to the device datasheet.

The device produces secondary clocks by dividing or/and multiplying the primary clocks:

- HSISYS, a clock derived from HSI48 through division by a factor programmable from 1 to 128.

- SYSCLK, a clock obtained through selecting one of the LSE, LSI, HSE, and HSISYS clocks.

- HSIKER, a clock derived from HSI48 through division by a factor programmable from 1 to 8.

- HCLK, a clock derived from SYSCLK through division by a factor programmable from 1 to 512.

- HCLK8, a clock derived from HCLK through division by eight.

- PCLK, a clock derived from HCLK through division by a factor programmable from 1 to 16.

- TIMPCLK, a clock derived from PCLK, running at PCLK frequency if the APB prescaler division factor is set to 1, or at twice the PCLK frequency otherwise.

Fixed division of HSE, HSI48, and HCLK clocks generate secondary clocks.

The HSISYS is used as a system clock source after startup from reset, with the division by four (producing a 12 MHz frequency).

The HCLK clock and PCLK clock are used for clocking the AHB and the APB domains, respectively. Their maximum allowed frequency is 48 MHz.

The peripherals are clocked with the clocks from the bus that they are attached to (HCLK for AHB, PCLK for APB) except:

- TIMx, with:

- TIMPCLK running at PCLK frequency if the APB prescaler division factor is set to 1, or at twice the PCLK frequency otherwise.

- USARTx, with these clock sources to select from:

- SYSCLK (system clock)

- HSIKER

- LSE

- PCLK (APB clock)

The wake-up from Stop mode is supported only when the clock is HSI48 or LSE.

- ADC, with these clock sources to select from:

- SYSCLK (system clock)

- HSIKER

The wake-up from Stop mode is supported only when the clock is HSI48.

- I2Cx, with these clock sources to select from:

- SYSCLK (system clock)

- HSIKER

- PCLK (APB clock)

The wake-up from Stop mode is supported only when the clock is HSI48.

AN5673 - Rev 3 page 8/36

- **I2Sx**, with these clock sources to select from:

- SYSCLK (system clock)

- HSIKER

- I2S\_CKIN pin

- RTC, with these clock sources to select from:

- LSE

- LSI

- HSE clock divided by 32

The functionality in Stop mode (including wake-up) is supported only when the clock is LSI or LSE.

- IWDG, always clocked with the LSI clock.

- USB, with these clock sources to select from:

- HSE

- HSIUSB48

- FDCAN1, with these clock sources to select from:

- PCLK

- HSIKER

- HSE

The selection is done through the SysTick control and status register.

- SysTick (Cortex® core system timer), with these clock sources to select from:

- HCLK (AHB clock)

- HCLK clock divided by 8

The selection is done through the SysTick control and status register.

HCLK is used as Cortex® -M0+ free-running clock (FCLK). For further information, refer to the PM0223 programming manual.

AN5673 - Rev 3 page 9/36

Figure 5. Clock tree

Note:

- 1. TIMPCLK runs at PCLK frequency if the APB prescaler division factor is set to 1, or at twice the PCLK frequency otherwise.

- 2. Only applies to STM32C071xx.

- 3. Only applies to STM32C051xx, STM32C071xx, and STM32C091xx/92xx.

- 4. Only applies to STM32C092xx.

### 2.1 HSE clock

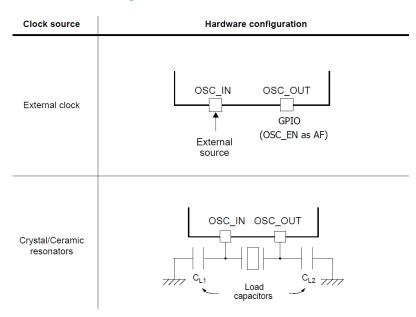

The high speed external clock signal (HSE) can be generated from two possible clock sources:

- HSE external crystal/ceramic resonator

- HSE user external clock

The resonator and the load capacitors must be placed as close as possible to the oscillator pins to minimize output distortion and startup stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

AN5673 - Rev 3 page 10/36

Note:

Figure 6. HSE / LSE clock sources

## External crystal/ceramic resonator (HSE crystal)

The 4 to 48 MHz external oscillator has the advantage of producing a very accurate rate on the main clock. The associated hardware configuration is shown in Figure 6. Refer to the electrical characteristics section of the datasheet for more details.

The HSERDY flag in the clock control register (RCC\_CR) indicates if the HSE oscillator is stable or not. At startup, the clock is not released until this bit is set by hardware. An interrupt can be generated if enabled in the clock interrupt enable register (RCC\_CIER).

The HSE crystal can be switched on and off using the HSEON bit in the clock control register (RCC\_CR).

### **External source (HSE bypass)**

In this mode, an external clock source must be provided. It can have a frequency of up to 48 MHz. This mode is selected by setting the HSEBYP and HSEON bits in the clock control register (RCC\_CR). The external clock signal (square, sinus, or triangle) with around 40 to 60% duty cycle depending on the frequency (refer to the datasheet) must drive the OSC\_IN pin, on devices where OSC\_IN and OSC\_OUT pins are available (see Figure 6).

The OSC\_OUT pin can be used as a GPIO or it can be configured as an OSC\_EN alternate function, to provide an enable signal to the external clock synthesizer. It makes it possible to stop the external clock source when the device enters low power modes.

For details on pin availability, refer to the pinout section in the corresponding device datasheet.

To minimize the consumption, it is recommended to use the square signal.

AN5673 - Rev 3 page 11/36

### 2.2 HSI48 clock

The HSI48 clock signal is generated from an internal 48 MHz RC oscillator.

The HSI48 RC oscillator has the advantage of providing a clock source at low cost (no external components). It also has a startup time faster than the HSE crystal oscillator. However, even after calibration, it is less accurate than an oscillator using a frequency reference such as a quartz crystal or ceramic resonator.

The HSISYS clock derived from HSI48 can be selected as the system clock after wake up from Stop mode. It can also be used as a backup clock source (auxiliary clock) if the HSE crystal oscillator fails.

#### Calibration

RC oscillator frequencies can vary from one chip to another due to manufacturing process variations. To compensate for this variation, each device is factory calibrated at  $T_A = 25$ °C.

After reset, the factory calibration value is loaded in the HSICAL[7:0] bits in the Internal clock source calibration register (RCC\_ICSCR).

Voltage or temperature variations in the application may affect the HSI48 frequency of the RC oscillator. It can be trimmed using the HSITRIM[6:0] bits in the Internal clock source calibration register (RCC ICSCR).

The HSIRDY flag in the Clock control register (RCC\_CR) indicates if the HSI48 RC is stable or not. At startup, the HSI48 RC output clock is not released until this bit is set by the hardware.

The HSI48 RC can be switched on and off using the HSION bit in the Clock control register (RCC\_CR).

The HSI48 signal can also be used as a backup source (auxiliary clock) if the HSE crystal oscillator fails.

### 2.3 HSIUSB48 clock

Available on the STM32C071xx devices only, the HSIUSB48 clock signal is generated from an internal 48 MHz RC oscillator. It can be used as a clock source for the USB peripheral or system clock.

The HSIUSB48 clock is of high-precision thanks to the clock recovery system (CRS). The CRS uses the USB SOF signal, the LSE clock, or an external signal as timing reference, to precisely adjust the HSIUSB48 RC oscillator frequency.

The HSIUSB48 RC oscillator is disabled as soon as the system enters Stop or Standby mode.

When the CRS is not used, the HSIUSB48 RC oscillator runs on its free-run frequency that is subject to manufacturing process variations. The devices are factory-calibrated for about 3 % accuracy at TA = 25°C.

Refer to the CRS section for more details on how to configure and use it. The HSIUSB48RDY flag in the RCC\_CR register indicates if HSIUSB48 is stable or not. At startup, the HSIUSB48 clock is not released until the hardware sets this flag.

The HSIUSB48 RC oscillator is enabled/disabled through the HSIUSB48ON bit of the RCC\_CR register. It is automatically enabled (by hardware setting the HSIUSB48ON bit) when selected as the clock source for the USB peripheral, as long as the USB peripheral is enabled.

Furthermore, it is possible to output the HSIUSB48 clock on the MCO and MCO2 outputs and use it as a clock source for other application components.

### 2.4 LSE clock

The LSE crystal is a 32.768 kHz crystal or ceramic resonator. It has the advantage of providing a low-power but highly accurate clock source to the real-time clock peripheral (RTC) for clock/calendar or other timing functions.

The LSE crystal is switched on and off using the LSEON bit in the Control register 1 (RCC\_CSR1). The crystal oscillator driving strength can be changed. It can be changed at runtime using the LSEDRV bit in the Control register 1 (RCC\_CSR1) to obtain the best compromise between low-power-consumption on one side, and robustness and short startup time on the other side. The LSE drive can be decreased to its lower capability (LSEDRV cleared) when the LSE is ON. However, once LSEDRV is selected, the drive capability cannot be increased if LSEON = 1.

The LSERDY flag in the Control register 1 (RCC\_CSR1) indicates whether the LSE crystal is stable or not. At startup, the LSE crystal output clock signal is not released until this bit is set by the hardware. An interrupt can be generated if enabled in the clock interrupt enable register (RCC\_CIER).

AN5673 - Rev 3 page 12/36

Clocks

### **External source (LSE bypass)**

In this mode, an external clock source must be provided. It can have a frequency of up to 1 MHz. This mode is selected by setting the LSEBYP and LSEON bits in the AHB peripheral clock enable in the Sleep/Stop mode register (RCC\_AHBSMENR). The external clock signal (square, sinus, or triangle) with around 50% duty cycle has to drive the OSCX\_IN pin while the OSCX\_OUT pin can be used as GPIO. See Figure 6.

### 2.5 LSI clock

The LSI RC acts as a low-power clock source that can be kept running in Stop and Standby mode for the independent watchdog (IWDG) and RTC. The clock frequency is 32 kHz. For more details, refer to the electrical characteristics section of the datasheets.

The LSI RC can be switched on and off using the LSION bit in the Control/status register 2 (RCC\_CSR2). The LSIRDY flag in the Control/status register 2 (RCC\_CSR2) indicates if the LSI oscillator is stable or not. At startup, the clock is not released until this bit is set by hardware. An interrupt can be generated if enabled in the clock interrupt enable register (RCC\_CIER).

AN5673 - Rev 3 page 13/36

## 2.6 System clock (SYSCLK) selection

One of the following clocks can be selected as a system clock (SYSCLK):

- LSI

- LSE

- HSISYS

- HSE

- HSIUSB48 (only available for STM32C071xx devices)

The maximum frequency of the system clock is 48 MHz. Upon system reset, the HSISYS clock derived from the HSI48 oscillator is selected as the system clock. When a clock source is used as a system clock, it is not possible to stop it.

A switch from one clock source to another occurs only if the target clock source is ready (clock stable after startup delay). If a clock source that is not yet ready is selected, the switch occurs when the clock source becomes ready. Status bits in the internal clock source calibration register (RCC\_ICSCR) indicate which clock is ready and which clock is currently used as a system clock.

## 2.7 Clock security system (CSS)

Software can activate the clock security system. In this case, the clock detector is enabled after the HSE oscillator startup delay. It is disabled when this oscillator is stopped.

If a failure is detected on the HSE clock:

- The HSE oscillator is automatically disabled.

- A clock failure event is sent to the break input of TIM1, TIM16, and TIM17 timers.

- CSSI (clock security system interrupt) is generated.

The CSSI is linked to the Cortex®-M0+ NMI (nonmaskable interrupt) exception vector. It makes the software aware of an HSE clock failure to allow it to perform rescue operations.

Note:

If the CSS is enabled and the HSE clock fails, the CSSI occurs and an NMI is automatically generated. The NMI is executed infinitely unless the CSS interrupt pending bit is cleared. It is therefore necessary that the NMI ISR clears the CSSI by setting the CSSC bit in the clock interrupt clear register (RCC\_CICR).

If HSE is selected directly or indirectly as the system clock, and a failure of the HSE clock is detected, the system clock switches automatically to HSISYS, and the HSE oscillator is disabled.

### 2.8 Clock security system for LSE clock (LSECSS)

A clock security system on LSE can be activated by setting the LSECSSON bit in the Control register 1 (RCC\_CSR1). This bit can be cleared only by a hardware reset or RTC software reset, or after LSE clock failure detection. LSECSSON must be written after LSE and LSI are enabled (LSEON and LSION enabled) and ready (LSERDY and LSIRDY flags set by hardware), and after selecting the RTC clock by RTCSEL.

The LSECSS works in all modes except Standby and Shutdown. It keeps working also under system reset (excluding power-on reset). If a failure is detected on the LSE oscillator, the LSE clock is no longer supplied to the RTC, but its registers are not impacted.

Note:

If the LSECSS is enabled and the LSE clock fails, the LSECSSI occurs and an NMI is automatically generated. The NMI is executed infinitely unless the LSECSS interrupt pending bit is cleared. It is therefore necessary that the NMI ISR clears the LSECSSI by setting the LSECSSC bit in the clock interrupt clear register (RCC\_CICR).

If LSE is used as a system clock, and a failure of the LSE clock is detected, the system clock switches automatically to LSI. In low-power modes, an LSE clock failure generates a wake-up. The interrupt flag must then be cleared within the RCC registers.

The software must then disable the LSECSSON bit, stop the defective 32 kHz oscillator (by clearing LSEON), and change the RTC clock source (no clock, LSI or HSE, with RTCSEL), or take any appropriate action to secure the application.

The frequency of the LSE oscillator must exceed 30 kHz to avoid false positive detections.

AN5673 - Rev 3 page 14/36

### 2.9 ADC clock

The ADC clock (refer to the device datasheet for maximum frequency) is derived from the system clock or from the kernel clock output. It can be prescaled by 1, 2, 4, 6, 8, 10, 12, 16, 32, 64, 128 or 256, by configuring the ADC1\_CCR register. This clock is asynchronous to the AHB clock. Alternatively, the ADC clock can be derived from the AHB clock of the ADC bus interface, divided by a programmable factor (1, 2 or 4). This programmable factor is configured using the CKMODE bitfields in the ADC1\_CCR.

If the programmed factor is 1, the AHB prescaler must be set to 1.

### 2.10 RTC clock

The RTCCLK clock source can be either the HSE/32, LSE or LSI clock. It is selected by programming the RTCSEL[1:0] bits in the Control register 1 (RCC\_CSR1). This selection cannot be modified without resetting the RTC domain. The system must always be configured so as to get a PCLK frequency greater than or equal to the RTCCLK frequency for proper RTC operation.

RTC does not operate if the  $V_{DD}$  supply is powered off or if the internal voltage regulator is powered off (removing power from the  $V_{CORE}$  domain). When the RTC clock is LSE or LSI, the RTC remains clocked and functional under system reset.

When the RTC clock is LSE or LSI, the RTC remains clocked and functional under system reset.

### 2.11 Timer clock

The timer clock TIMPCLK is derived from PCLK, which is used for APB. If the APB prescaler is set to 1, the TIMPCLK frequency is equal to the PCLK frequency. Otherwise, the TIMPCLK frequency is set to twice the PCLK frequency.

## 2.12 Watchdog clock

If a hardware option or software access starts the independent watchdog (IWDG), the LSI oscillator is forced ON, and cannot be disabled. After the LSI oscillator temporization, the clock is provided to the IWDG.

## 2.13 Clock-out capability

### MCO and MCO2

These pins output, independently of each other, the clock selected from:

- LSI

- LSE

- SYSCLK

- HSI48

- HSE

- HSIUSB48 (Only available for STM32C071xx device)

The multiplexers for MCO and MCO2 are controlled, respectively, by the MCOSEL[2:0] and MCO2SEL[2:0] bitfields of the Clock configuration register (RCC\_CFGR). Their outputs are further divided by a factor set through the MCOPRE[2:0] and MCO2PRE[2:0] bitfields of the Clock configuration register (RCC\_CFGR).

### LCO

The LSCO pin allows outputting of low-speed clocks:

- LSI

- LSE

The selection is controlled by the LSCOSEL bit, and enabled with the LSCOEN bit of the Control register 1 (RCC\_CSR1). The configuration registers of the corresponding GPIO port must be programmed in alternate function mode. This function remains available in Stop mode.

AN5673 - Rev 3 page 15/36

### 2.14 Internal / external clock measurement with TIM14 / TIM16 / TIM17

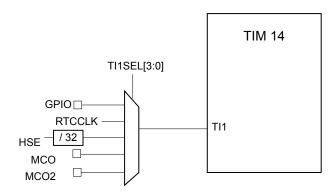

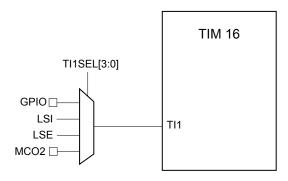

It is possible to indirectly measure the frequency of all on-board clock sources with the TIM14, TIM16, and TIM17 channel 1 input capture, as shown in the figures in each of the corresponding subsections.

#### **TIM14**

By setting the TI1SEL[3:0] field of the TIM14\_TISEL register, the clock selected for the input capture channel1 of TIM14 can be one of the following:

- GPIO (refer to the alternate function mapping in the device datasheets)

- RTC clock (RTCCLK)

- HSE clock divided by 32

- MCO (MCU clock output)

- MCO2 (MCU clock output)

MCO and MCO2 are controlled, respectively, by the MCOSEL[3:0] and MCO2SEL[3:0] bitfields of the clock configuration register (RCC\_CFGR). All clock sources can be selected for the MCO and MCO2 pins.

Figure 7. Frequency measurement with TIM14 in capture mode

### TIM16

By setting the TI1SEL[3:0] field of the TIM16\_TISEL register, the clock selected for the input capture channel1 of TIM16 can be one of the following:

- GPIO (refer to the alternate function mapping in the device datasheets)

- LSI clock

- LSE clock

- MCO2

MCO2 is controlled by the MCO2SEL[3:0] bitfield of the clock configuration register (RCC\_CFGR). All clock sources can be selected for the MCO2 pin.

AN5673 - Rev 3 page 16/36

Figure 8. Frequency measurement with TIM16 in capture mode

#### **TIM17**

By setting the TI1SEL[3:0] field of the TIM17\_TISEL register, the clock selected for the input capture channel1 of TIM17 can be one of the following:

- GPIO (refer to the alternate function mapping in the device datasheets)

- HSE divided by 32

- HSIUSB48/256 (only available on STM32C071xx devices)

- MCO (MCU clock output)

- MCO2 (MCU clock output)

MCO and MCO2 are controlled, respectively, by the MCOSEL[3:0] and MCO2SEL[3:0] bitfields of the clock configuration register (RCC\_CFGR). All clock sources can be selected for the MCO and MCO2 pins.

Figure 9. Frequency measurement with TIM17 in capture mode

### Calibration of the HSI48 oscillator

For TIM14, TIM16 and TIM17, the primary purpose of connecting the LSE to the channel 1 input capture is to be able to precisely measure the HSISYS clock (derived from HSI48) selected as system clock. Counting HSISYS clock pulses between consecutive edges of the LSE clock (the time reference) allows measuring the HSISYS (and HSI48) clock period. Such measurement can determine the HSI48 oscillator frequency with nearly the same accuracy as the accuracy of the 32.768 kHz quartz crystal used with the LSE oscillator (typically a few tens of ppm). The HSI48 oscillator can then be trimmed to compensate for deviations from the target frequency, due to manufacturing, process, temperature and/or voltage variation.

The HSI48 oscillator has dedicated user-accessible calibration bits for this purpose.

The basic concept consists in providing a relative measurement (for example, the HSISYS/LSE ratio): the measurement accuracy is therefore closely related to the ratio between the two clock sources. Increasing the ratio improves the measurement accuracy.

AN5673 - Rev 3 page 17/36

Generated by the HSE oscillator, the HSE clock (divided by 32) used as a time reference is the second best method for reaching a good HSI48 frequency measurement accuracy. It is recommended in the absence of the LSE clock.

To further improve the precision of the HSI48 oscillator calibration, it is advised to employ one, or a combination of the following measures, to increase the frequency measurement accuracy:

- Set the HSISYS divider to 1 for HSISYS frequency to be equal to HSI48 frequency.

- Average the results of multiple consecutive measurements.

- Use the input capture prescaler of the timer (one capture every up to eight periods).

#### Calibration of the LSI oscillator

The calibration of the LSI oscillator uses the same principle as that for calibrating the HSI48 oscillator. TIM16 channel1 input capture must be used for LSI clock, and HSE selected as the system clock source. The number of HSE clock pulses between consecutive edges of the LSI signal, counted by TIM16, is then representative of the LSI clock period.

## 2.15 Peripheral clock enable registers

The clock to each peripheral can individually be enabled by the corresponding enable bit of the RCC\_AHBENR register or one of the RCC\_APBENRx registers.

The clocks to I/O ports can individually be enabled through the RCC\_IOPENR register.

When the clock to a peripheral or I/O port is not active, the read and write accesses to its registers are not effective.

#### Caution:

The enable bits have a synchronization mechanism to create a glitch-free clock for the corresponding peripheral or I/O port. After an enable bit is set, there is a 2-clock-cycle delay before the clock becomes active, which the software must take into account.

AN5673 - Rev 3 page 18/36

## 3 Boot configuration

Three different boot modes can be selected through the BOOT0 pin, the BOOT\_LOCK bit in the FLASH\_SECR register, and the boot configuration bits nBOOT1, BOOT\_SEL, and nBOOT0 in the user option byte, as shown in the following table.

**Boot mode configuration** Selected boot area BOOT\_LOCK nBOOT1 bit **BOOT0** pin nBOOT\_SEL bit nBOOT0 bit 0 Main flash memory 0 0 1 1 Х System memory 0 0 1 0 Х Embedded SRAM 0 Χ Χ 1 1 Main flash memory 0 1 Χ 1 0 System memory 0 0 Χ 1 0 **Embedded SRAM** 1 Χ Χ Х Χ Main flash memory

Table 2. Boot modes

The boot mode configuration is latched on the fourth rising edge of SYSCLK after a reset. It is up to the user to set the boot mode configuration related to the required boot mode.

The boot mode configuration is also resampled when exiting from Standby mode. Consequently, they must be kept in the required Boot mode configuration in Standby mode.

After this startup delay has elapsed, the CPU fetches the top-of-stack value from address 0x0000 0000, then starts code execution from the boot memory at 0x0000 0004.

Depending on the selected boot mode, main flash memory, system memory or SRAM is accessible as follows:

- Boot from main flash memory: the main flash memory is aliased in the boot memory space (0x0000 0000). But it is still accessible from its original memory space (0x0800 0000). In other words, the flash memory content can be accessed starting from address 0x0000 0000 or 0x0800 0000.

- Boot from system memory: the system memory is aliased in the boot memory space (0x0000 0000), but still accessible from its original memory space 0x1FFF 0000.

- Boot from the embedded SRAM: the SRAM is aliased in the boot memory space (0x0000 0000), but it is still accessible from its original memory space (0x2000 0000).

### Caution:

The BOOT0 pin shares the same GPIO with the serial wire clock (SWCLK) that is used by the debugger to connect with the device as these functionalities can be considered almost completely disjoint. Nevertheless, to ensure system robustness, the STM32C0 series devices provide a hardware mechanism to force BOOT0 low (boot from user flash memory) if a debugger access is detected (and BOOT0 information is taken from the pin). This is done to use the SWCLK clock for debugger serial communications, and at the same time have a safe boot configuration for the device itself. This configuration is kept until the next power-on after the debugger

## Caution:

The BOOT0 pin sampling is done on the NRST (external reset) rising edge. Refer to the NRST (external reset) description in section Section 1.3.2: System reset for details on how the PF2-NRST pin mode impacts the BOOT0 sampling.

### Forcing boot from the user flash memory

The BOOT\_LOCK bit enables forcing a unique entry point in the main flash memory for boot, regardless of the other boot mode configuration bits and the EMPTY flag.

AN5673 - Rev 3 page 19/36

## **Empty check**

The internal empty check flag (the EMPTY bit of the FLASH access control register (FLASH\_ACR)) is implemented to allow easy programming of virgin devices by the bootloader. This flag is checked when the boot configuration defines the main flash memory as the target boot area and the BOOT\_LOCK bit is not set. When the EMPTY flag is set, the device is considered empty and system memory (bootloader) is selected instead of the main flash memory as a boot area, to allow the user to program the device.

Refer to *STM32 microcontroller system memory boot mode* (AN2606) for further details on the bootloader and the GPIO configuration in the system memory boot mode (some of the GPIOs are reconfigured from the high-Z state).

The EMPTY flag is updated by hardware only during the loading of option bytes: it is set when the 64-bit content of the address 0x0800 0000 is read as 0xFFFF FFFF FFFF, otherwise it is cleared. It means after programming of a virgin device, a power on reset or setting of OBL\_LAUNCH bit in the FLASH\_CR register is needed to clear the EMPTY flag (system reset has no impact on this flag). Software can also modify the EMPTY flag directly in the FLASH\_ACR register.

Note:

If the device is programmed for the first time but the EMPTY flag is not updated, the device still selects system memory as a boot area after a system reset.

#### Physical remap

Once the boot mode is selected, the application software can modify the memory accessible in the code area. This modification is performed by programming the MEM\_MODE bits in the SYSCFG configuration register 1 (SYSCFG\_CFGR1).

#### **Embedded bootloader**

The embedded bootloader is located in the system memory, programmed by STMicroelectronics during production. It is used to reprogram the flash memory using one of the following serial interfaces:

- USART

- I2C

- SPI (only on STM32C051xx, STM32C071xx, and STM32C091xx/92xx devices)

- USB DFU (only on STM32C071xx devices)

- FDCAN (only on STM32C092xx devices)

For further details, refer to application note *STM32 microcontroller system memory boot mode* (AN2606 available on https://www.st.com/).

AN5673 - Rev 3 page 20/36

## 4 Debug management

### 4.1 Introduction

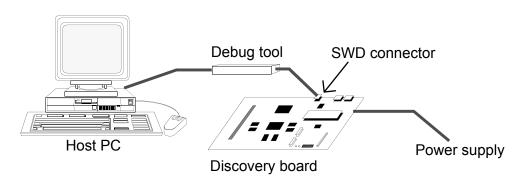

The host/target interface is the hardware equipment that connects the host to the application board. This interface is made of three components: a hardware debug tool, an SWD connector, and a cable connecting the host to the debug tool.

Figure 10 shows the connection of the host to the discovery board (STM32C0316-DK), which embeds the debug tools (ST-LINK). Consequently, it can be directly connected to the PC through a USB cable.

Figure 10. Host-to-board connection

## 4.2 SWD (serial wire debug) port

The STM32C0 series core integrates the serial wire debug port (SW-DP), an Arm<sup>®</sup> standard CoreSight<sup>™</sup> debug port with a 2-pin (clock + data) interface to the debug access port.

## 4.3 Pinout and debug port pins

The microcontrollers of the STM32C0 series are offered in packages with varying numbers of pins.

## 4.3.1 Serial wire debug (SWD) pin assignment

The same SWD pin assignment is available on all STM32C0 MCU packages.

Table 3. SWD port pins

| SWD pin name |      | Pin assignment                |                    |

|--------------|------|-------------------------------|--------------------|

| piii fiame   | Type | Debug assignment              | riii assiyiiiieiit |

| SWDIO        | I/O  | Serial wire data input/output | PA13               |

| SWCLK I      |      | Serial wire clock             | PA14               |

After reset (SYSRESETn or PORESETn), the pins used for the SWD are assigned as dedicated pins, immediately usable by the debugger host.

The MCU offers the possibility to disable the SWD, therefore releasing the associated pins for general-purpose I/O (GPIO) usage. For more details on how to disable SWD port, refer to the RM0490 section on I/O pin alternate function multiplexer and mapping.

AN5673 - Rev 3 page 21/36

## 4.3.2 Internal pull-up and pull-down on SWD pins

Once the SWD I/O is released by the user software, the GPIO controller takes control of these pins. The reset states of the GPIO control registers put the I/Os in the equivalent states:

- SWDIO: alternate function pull-up

- SWCLK: alternate function pull-down

Having embedded pull-up and pull-down resistors removes the need to add external resistors.

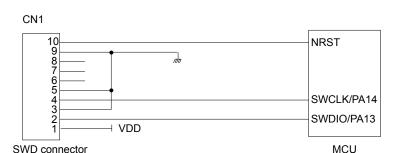

### 4.3.3 SWD port connection with standard SWD connector

Figure 11 shows the connection between the MCU and a standard SWD connector.

Figure 11. SWD port connection

## 4.3.4 Multi bonding on small packages

A multi-bonding approach is used on the small packages to offer a maximum of alternate functions and analog inputs. This approach results in multiple die pads connected internally to a single package pin. As an example, in Figure 12 there are four pads bonded to each of the pins 1, 4, 5 and 8. Multi bonding for pin 1 means that each of the alternate functions (PB7 and PC14) is accessible on this pin if respectively configured at I/O port level.

PB7/PC14-OSCX\_IN

1

8

PA14-BOOT0/PB6/PC15-OSCX\_OUT

VDD/VDDA

2

7

PA13

VSS/VSSA

3

6

PA12[PA10]

PA0/PA1/PA2/PF2-NRST

4

5

PA8/PA11[PA9]

Figure 12. Multi bonding example

A design protection is implemented to avoid pad interferences due to multi-bonding. This protection is achieved through a dedicated SYSCFG\_CFGR3 register in the System controller, which makes possible to select which IO of a multi-bonding group is active. For STM32C011xx, STM32C031xx, and STM32C071xx devices the other GPIOs connected to the same pin are forced into digital input (passive) mode regardless of their corresponding GPIOx\_MODER register settings. For STM32C051xx and STM32C091xx/92xx, the output buffer of the other GPIOs connected to the same pin are disabled regardless of their corresponding GPIOx\_MODER register settings. This register is taken into account if SECURE\_MUXING\_EN bit of the FLASH\_OPTR register is set to 1.

This protection can be deactivated by resetting the bit SECURE\_MUXING\_EN in the FLASH\_OPTR register. In this case, to ensure correct functionalities and avoid electrical damages, software must cautiously program all pads bonded to the same package pin. If the SECURE\_MUXING\_EN bit in the FLASH\_OPTR register is reset (protection bypassed), all the pads linked to one pin are active and can be set in the mode specified by the corresponding GPIOx\_MODER register. The user has to ensure that there are no conflicts between GPIOs.

By default, all GPIOs (except PA14 in this example) are configured in analog input; this must be taken into consideration before modifying the analog input configuration for another configuration state.

AN5673 - Rev 3 page 22/36

The multi bonding approach offers not only more versatility for the product configuration, but also offers an extended drive strength on the multi bonded pads. By configuring multiple devices pad in output mode (with the same output level), the transistor drive resistance is decreased and consequently the voltage drop ( $V_{OL}$  and  $V_{OH}$ ) at the device pin is reduced. The transition from high to low level must be done with caution to guarantee that no short circuits are produced between the internal die pads.

AN5673 - Rev 3 page 23/36

## 5 Recommendations

### 5.1 Printed circuit board

For technical reasons, it is best to use a multilayer printed circuit board (PCB) with a separate layer dedicated to ground ( $V_{SS}$ ) and another dedicated to the  $V_{DD}$  supply. This provides good decoupling and a good shielding effect. For many applications, economical reasons prohibit the use of this type of board. In this case, the major requirement is to ensure a good structure for the ground and for the power supply.

## 5.2 Component position

A preliminary layout of the PCB must make separate circuits:

- · High-current circuits

- Low-voltage circuits

- · Digital component circuits

- Circuits separated according to their EMI contribution. This reduces cross-coupling on the PCB that introduces noise.

## 5.3 Ground and power supply (V<sub>DD</sub>)

Every block (noisy, low-level sensitive, or digital) must be grounded individually and all ground returns must be to a single point. Loops must be avoided or their area has to be minimized. To improve analog performance, the decoupling capacitors must be placed as close as possible to the device.

The power supply must be implemented close to the ground line to minimize the area of supply loops. This is because the supply loop acts as an antenna, and is therefore the main transmitter and receiver of EMI. All component-free PCB areas must be filled with additional grounding to create a shield (especially when using single-layer PCBs).

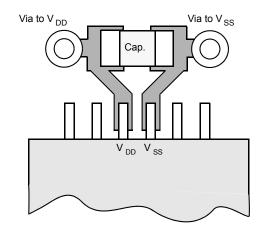

## 5.4 Decoupling

All power supplies and ground pins must be properly connected to the power supplies. These connections, including pads, tracks, and vias must have the lowest possible impedance. This is typically achieved with thick track widths and, preferably, with the use of dedicated power supply planes in multilayer PCBs.

In addition, each power supply pair must be decoupled with 100 nF filtering ceramic capacitor and a chemical capacitor of about 4.7  $\mu$ F connected between the supply pins of the device. These capacitors need to be placed as close as possible to or below the appropriate pins on the underside of the PCB. Typical values are 10 nF to 100 nF, but the exact values depend on the application needs. Figure 13 shows the typical layout of such a pair.

Figure 13. Typical layout for VDD/VSS pair

AN5673 - Rev 3 page 24/36

## 5.5 Other signals

When designing an application, the EMC performance can be improved by closely studying:

- Signals for which a temporary disturbance affects the running process permanently. Such as interrupts and handshaking strobe signals, but not LED commands. For these signals, a surrounding ground trace, shorter lengths, and the absence of noisy and sensitive traces nearby (the crosstalk effect) improve the EMC performance.

- Digital signals: the best possible electrical margin must be reached for the two logical states and slow Schmitt triggers are recommended to eliminate parasitic states.

- Noisy signals (such as clock)

- Sensitive signals (such as high-Z)

## 5.6 Unused I/O and features

All microcontrollers are designed for a variety of applications and often a particular application does not use 100% of the MCU resources.

To increase EMC performance and avoid extra power consumption, unused clocks, counters, or I/Os, should not be left free. I/Os should be connected to a fixed logic level of 0 or 1 by an external or internal pull-up or pull-down on the unused I/O pin. The other option is to configure the GPIO as the output mode using software. Unused features should be frozen or disabled, which is their default value.

AN5673 - Rev 3 page 25/36

## 6 Reference design

## 6.1 Reference design description

The reference design described in the following sections is based on STM32C0 MCUs and the LQFP48 package.

This reference design can be tailored to any STM32C0 device with a different package, using the pin correspondence provided in Section 6.2: Reference design for STM32C0 MCUs without VDDIO2 and Section 6.3: Reference design for STM32C0 MCUs with VDDIO2.

### 6.1.1 Clock

Two clock sources are used:

- LSE: X1, a 32.768 kHz crystal for the embedded RTC

- HSE: X2, a 24 MHz crystal for the microcontroller

Refer to Section 2: Clocks.

For more information about oscillator design, refer to the Oscillator design guide for STM8AF/AL/S, STM32 MCUs and MPUs (AN2867).

#### 6.1.2 Reset

The reset signal in Figure 1 is active low. The reset sources include the reset button (B1) and the debugging tools via the connector CN1. Refer to Section 1.3: Reset.

Note: By de

By default the reset holder is activated on STM32C0 series devices. Any internal reset results in pulling down the NRST pin until it reaches its  $V_{IL}$  threshold, ensuring that the capacity on this line is fully discharged.

#### 6.1.3 Boot mode

The boot option is configured by default through option bytes. BOOT0 pin can be used if the user wants to have a physical control on the boot entry point after reprogramming the option byte.

### 6.1.4 SWD interface

The reference design shows the connection between an MCU of the STM32C0 series and a standard SWD connector. Refer to Section 4: Debug management.

Note: It is recommended to connect the reset pin to be able to reset the application from the tool.

### 6.1.5 Power supply

Refer to Section 1.1: Power supplies.

### 6.1.6 Pinouts and pin description

Refer to the datasheets available on www.st.com for the pinout information and pin description of each device.

## 6.1.7 ESD protection

U2, U3, and U4 are TVS ESD protection. It is recommended for pins connected to the outside world to be protected.

For more information about ESD protection, refer to ESD protection of STM32 MCUs and MPUs (AN5612).

## 6.2 Reference design for STM32C0 MCUs without VDDIO2

The reference design shown in the figure below is based on STM32C031, a highly integrated microcontroller running at 48 MHz, combining the Cortex®-M0+ 32-bit RISC CPU core with 32 Kbytes of embedded flash memory and 12 Kbytes of SRAM. It can be applied to all STM32C0 devices without VDDIO2 power supply.

AN5673 - Rev 3 page 26/36

Figure 14. STM32C0 device without VDDIO2 reference schematic

JT73922

The values of capacitors used in combination with X1 and X2 must be chosen according to crystal specifications (the values indicated for C1, C2, C3, and C4 are given only as an example). To keep a stable NRST signal, the PCB layout must feature C5 as close as possible to pin PF2\_NRST.

VDD/VDDA VREF+

Note:

On packages where both OSC\_IN/OSC\_OUT and OSCX\_IN/OSCX\_OUT are available, if both LSE and HSE need to be implemented, the HSE\_NOT\_REMAPPED bit of the FLASH\_OPTR register must be set (default case).

AN5673 - Rev 3 page 27/36

## **Component references**

Table 4. Mandatory component references

| Component       | Reference | Value        | Quantity | Comments                            |

|-----------------|-----------|--------------|----------|-------------------------------------|

| Microcontroller | U1        | STM32C031CxT | 1        | 48-pin package                      |

| Capacitor       | C7        | 100 nF       | 1        | Ceramic capacitors (for decoupling) |

| Capacitor       | C6        | 4.7 μF       | 1        | Used for VDD                        |

**Table 5. Optional components**

| Component      | Reference | Value              | Quantity | Comments                                                       |

|----------------|-----------|--------------------|----------|----------------------------------------------------------------|

| Capacitor      | C5        | 100 nF             | 1        | Ceramic capacitor for RESET button                             |

| Capacitor      | C8        | 100 nF             | 1        | Ceramic capacitors (for decoupling)                            |

| Capacitor      | C1/C2     | 8.2 pF             | 2        | Used for LSE, the value depends on the crystal characteristics |

| Capacitor      | C3/C4     | 5.2 pF             | 2        | Used for HSE, the value depends on the crystal characteristics |

| Quartz         | X1        | 32.768 kHz         | 1        | Used for LSE                                                   |

| Quartz         | X2        | 24 MHz             | 1        | Used for HSE                                                   |

| Push-button    | B1        | -                  | 1        | Used as a reset button                                         |

| SWD connector  | CN1       | FTSH-105-01-L-DV   | 1        | Used for programming/debug                                     |

| ESD protection | U2/U3/U4  | TVS ESD protection | 3        | Used to protect the MCU against the ESD                        |

AN5673 - Rev 3 page 28/36

## 6.3 Reference design for STM32C0 MCUs with VDDIO2

SWD connector

The reference design shown in the figure below is based on STM32C071, a highly integrated microcontroller running at 48 MHz, combining the Cortex<sup>®</sup>-M0+ 32-bit RISC CPU core with 128 Kbytes of embedded flash memory and 24 Kbytes of SRAM. It can be applied to all STM32C0 MCUs with VDDIO2 power supply.

Figure 15. STM32C0 MCUs with VDDIO2 reference schematic

Ω

The values of capacitors used in combination with X1 and X2 must be chosen according to crystal specifications (the values indicated for C1, C2, C3, and C4 are given only as an example). To keep a stable NRST signal, the PCB layout must feature C5 as close as possible to pin PF2\_NRST.

MCU PWR

VDD/VDDA

VDDIO2 STM32C071RBTxN 40

Note:

On packages where both OSC\_IN/OSC\_OUT and OSCX\_IN/OSCX\_OUT are available, if both LSE and HSE need to be implemented, the HSE\_NOT\_REMAPPED bit of the FLASH\_OPTR register must be set (default case).

AN5673 - Rev 3 page 29/36

## **Component references**

**Table 6. Mandatory components**

| Component       | Reference | Value        | Quantity | Comments                            |

|-----------------|-----------|--------------|----------|-------------------------------------|

| Microcontroller | U1        | STM32C071CxT | 1        | 48-pin package                      |

| Capacitor       | C7/C10    | 100 nF       | 2        | Ceramic capacitors (for decoupling) |

| Capacitor       | C6/C9     | 4.7 µF       | 2        | Used for VDD and VDDIO2             |

**Table 7. Optional components**

| Component      | Reference | Value              | Quantity | Comments                                                       |

|----------------|-----------|--------------------|----------|----------------------------------------------------------------|

| Capacitor      | C5        | 100 nF             | 1        | Ceramic capacitor for RESET button                             |

| Capacitor      | C8        | 100 nF             | 1        | Ceramic capacitors (for decoupling)                            |

| Capacitor      | C1/C2     | 8.2 pF             | 2        | Used for LSE, the value depends on the crystal characteristics |

| Capacitor      | C3/C4     | 5.2 pF             | 2        | Used for HSE, the value depends on the crystal characteristics |

| Quartz         | X1        | 32.768 kHz         | 1        | Used for LSE                                                   |

| Quartz         | X2        | 24 MHz             | 1        | Used for HSE                                                   |

| Push-button    | B1        | -                  | 1        | Used as a reset button                                         |

| SWD connector  | CN1       | FTSH-105-01-L-DV   | 1        | Used for programming/<br>debug                                 |

| ESD protection | U2/U3/U4  | TVS ESD protection | 3        | Used to protect the MCU against the ESD                        |

AN5673 - Rev 3 page 30/36

# **Revision history**

Table 8. Document revision history

| 14-Dec-2022  2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Date        | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Updated the Figure 1. STM32C0 MCUs power supply without VDDId Updated the Section 2: Clocks Updated the Figure 5. Clock tree • Generated a public version of the document.  Updated: • Document title and cover page • Section 1.1: Power supplies • Figure 1. STM32C0 MCUs power supply without VDDIO2 • Figure 2. STM32C0 MCUs power supply without VDDIO2 • Section 1.3.2: System reset • Section 2: Clocks • Figure 5. Clock tree • Section 2.14: Internal / external clock measurement with TIM14 / TIM16 / TIM17 including Figure 9 • Section 2.15: Peripheral clock enable registers • Section 3: Boot configuration (embedded bootloader) • Section 4.3.4: Multi bonding on small packages • Section 6: Reference design • Section 6: Reference design • Section 6.1: Clock • Minor terminology updates  Added: • Section 6.3: Reference design for STM32C0 MCUs without VDDIO2 | 06-Jun-2022 | 1       | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Document title and cover page Section 1.1: Power supplies Figure 1. STM32C0 MCUs power supply without VDDIO2 Figure 2. STM32C0 MCUs power supply with VDDIO2 Section 1.3.2: System reset Section 2: Clocks Figure 5. Clock tree Section 2.14: Internal / external clock measurement with TIM14 / TIM16 / TIM17: TIM17 including Figure 9 Section 2.15: Peripheral clock enable registers Section 3: Boot configuration (embedded bootloader) Section 4.3.4: Multi bonding on small packages Section 6: Reference design Section 6.1.1: Clock Minor terminology updates  Added: Section 6.2: Reference design for STM32C0 MCUs without VDDIO Section 6.3: Reference design for STM32C0 MCUs with VDDIO2                                                                                                                                                                                  | 14-Dec-2022 | 2       | Updated the Figure 1. STM32C0 MCUs power supply without V <sub>DDIO2</sub> Updated the Section 2: Clocks Updated the Figure 5. Clock tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Removed:  • Component references                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28-Jun-2024 | 3       | <ul> <li>Document title and cover page</li> <li>Section 1.1: Power supplies</li> <li>Figure 1. STM32C0 MCUs power supply without V<sub>DDIO2</sub></li> <li>Figure 2. STM32C0 MCUs power supply with V<sub>DDIO2</sub></li> <li>Section 1.3.2: System reset</li> <li>Section 2: Clocks</li> <li>Figure 5. Clock tree</li> <li>Section 2.14: Internal / external clock measurement with TIM14 / TIM16 / TIM17: TIM17 including Figure 9</li> <li>Section 2.15: Peripheral clock enable registers</li> <li>Section 3: Boot configuration (embedded bootloader)</li> <li>Section 4.3.4: Multi bonding on small packages</li> <li>Section 6: Reference design</li> <li>Section 6.1.1: Clock</li> <li>Minor terminology updates</li> <li>Added:</li> <li>Section 6.2: Reference design for STM32C0 MCUs without VDDIO2</li> <li>Section 6.3: Reference design for STM32C0 MCUs with VDDIO2</li> <li>Section 6.1.7: ESD protection</li> <li>Removed:</li> </ul> |

AN5673 - Rev 3 page 31/36

# **Contents**

| 1 | Pow  | er supp                                                          | olies and reset sources                                          | 2  |  |  |  |

|---|------|------------------------------------------------------------------|------------------------------------------------------------------|----|--|--|--|

|   | 1.1  | Power                                                            | supplies                                                         | 2  |  |  |  |

|   | 1.2  | Power                                                            | supply supervisor                                                | 4  |  |  |  |

|   |      | 1.2.1                                                            | Power-on reset (POR)/power-down reset (PDR)/brownout reset (BOR) | 4  |  |  |  |

|   | 1.3  | Reset                                                            |                                                                  | 4  |  |  |  |

|   |      | 1.3.1                                                            | Power reset                                                      | 5  |  |  |  |

|   |      | 1.3.2                                                            | System reset                                                     | 5  |  |  |  |

|   |      | 1.3.3                                                            | RTC domain reset                                                 | 7  |  |  |  |

| 2 | Cloc | Clocks                                                           |                                                                  |    |  |  |  |

|   | 2.1  | HSE c                                                            | ock                                                              | 10 |  |  |  |

|   | 2.2  | HSI48                                                            | clock                                                            | 12 |  |  |  |

|   | 2.3  | HSIUS                                                            | SB48 clock                                                       | 12 |  |  |  |

|   | 2.4  | LSE cl                                                           | lock                                                             | 12 |  |  |  |

|   | 2.5  | LSI clo                                                          | ock                                                              | 13 |  |  |  |

|   | 2.6  | Systen                                                           | m clock (SYSCLK) selection                                       | 14 |  |  |  |

|   | 2.7  | Clock security system (CSS)14                                    |                                                                  |    |  |  |  |

|   | 2.8  | Clock security system for LSE clock (LSECSS)                     |                                                                  |    |  |  |  |

|   | 2.9  | ADC clock                                                        |                                                                  |    |  |  |  |

|   | 2.10 | RTC c                                                            | slock                                                            | 15 |  |  |  |

|   | 2.11 | Timer clock1                                                     |                                                                  |    |  |  |  |

|   | 2.12 | Watchdog clock                                                   |                                                                  |    |  |  |  |

|   | 2.13 | Clock-out capability                                             |                                                                  |    |  |  |  |

|   | 2.14 | Internal / external clock measurement with TIM14 / TIM16 / TIM17 |                                                                  |    |  |  |  |

|   | 2.15 | Peripheral clock enable registers                                |                                                                  |    |  |  |  |

| 3 | Boot | config                                                           | juration                                                         | 19 |  |  |  |

| 4 |      |                                                                  | agement                                                          |    |  |  |  |

|   | 4.1  | Introdu                                                          | uction                                                           | 21 |  |  |  |

|   | 4.2  | SWD (serial wire debug) port                                     |                                                                  |    |  |  |  |

|   | 4.3  |                                                                  | and debug port pins                                              |    |  |  |  |

|   |      | 4.3.1                                                            | Serial wire debug (SWD) pin assignment                           |    |  |  |  |

|   |      | 4.3.2                                                            | Internal pull-up and pull-down on SWD pins                       |    |  |  |  |

|   |      | 4.3.3                                                            | SWD port connection with standard SWD connector                  | 22 |  |  |  |

|   |      | 4.3.4                                                            | Multi bonding on small packages                                  | 22 |  |  |  |

| 5 | Reco | ommen                                                            | dations                                                          | 24 |  |  |  |

|     | 5.1    | Printe  | d circuit board                             | 24 |

|-----|--------|---------|---------------------------------------------|----|

|     | 5.2    | Comp    | onent position                              | 24 |

|     | 5.3    | Groun   | nd and power supply (V <sub>DD</sub> )      | 24 |

|     | 5.4    | Decou   | upling                                      | 24 |

|     | 5.5    | Other   | signals                                     | 25 |

|     | 5.6    | Unuse   | ed I/O and features                         | 25 |

| 6   | Refe   | rence   | design                                      | 26 |

|     | 6.1    | Refere  | ence design description                     | 26 |

|     |        | 6.1.1   | Clock                                       | 26 |

|     |        | 6.1.2   | Reset                                       | 26 |

|     |        | 6.1.3   | Boot mode                                   | 26 |

|     |        | 6.1.4   | SWD interface                               | 26 |

|     |        | 6.1.5   | Power supply                                | 26 |

|     |        | 6.1.6   | Pinouts and pin description                 | 26 |

|     |        | 6.1.7   | ESD protection                              | 26 |

|     | 6.2    | Refere  | ence design for STM32C0 MCUs without VDDIO2 | 26 |

|     | 6.3    | Refere  | ence design for STM32C0 MCUs with VDDIO2    | 29 |

| Rev | vision | historv | /                                           |    |

# **List of tables**

| Table 1. | Power supplies of STM32C0 MCUs |

|----------|--------------------------------|

| Table 2. | Boot modes                     |

| Table 3. | SWD port pins                  |

| Table 4. | Mandatory component references |

| Table 5. | Optional components            |

| Table 6. | Mandatory components           |

| Table 7. | Optional components            |

| Table 8. | Document revision history      |

# **List of figures**

| Figure 1.  | STM32C0 MCUs power supply without V <sub>DDIO2</sub> | . 3 |

|------------|------------------------------------------------------|-----|

| Figure 2.  | STM32C0 MCUs power supply with V <sub>DDIO2</sub>    | . 3 |

| Figure 3.  | POR, PDR, and BOR thresholds                         | . 4 |

| Figure 4.  | Simplified diagram of the reset circuit              | . 6 |

| Figure 5.  | Clock tree                                           |     |

| Figure 6.  | HSE / LSE clock sources                              | 11  |

| Figure 7.  | Frequency measurement with TIM14 in capture mode     | 16  |

| Figure 8.  | Frequency measurement with TIM16 in capture mode     | 17  |

| Figure 9.  | Frequency measurement with TIM17 in capture mode     | 17  |

| Figure 10. | Host-to-board connection                             |     |

| Figure 11. | SWD port connection                                  |     |

| Figure 12. | Multi bonding example                                |     |

| Figure 13. | Typical layout for VDD/VSS pair                      | 24  |

| Figure 14. | STM32C0 device without VDDIO2 reference schematic    | 27  |

| Figure 15. | STM32C0 MCUs with VDDIO2 reference schematic         | 29  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.