Application note

# L9396 Configuration and layout

## Introduction

This document describes how to configure the L9396 regulators for addressing different system scenarios. The L9396-EVAL board is referenced.

Layout hints and recommendations for improving EMC performances will also be discussed.

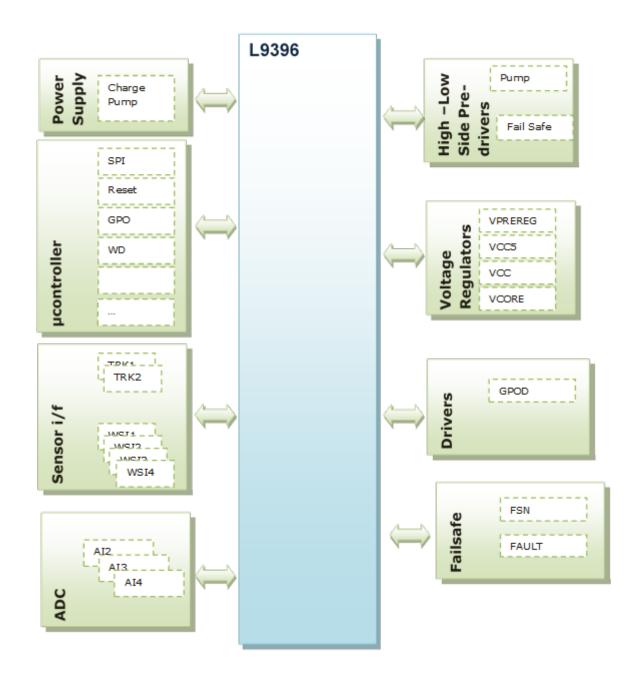

# 1 Block diagram

Figure 1. Application block diagram

AN5702 - Rev 2 page 2/26

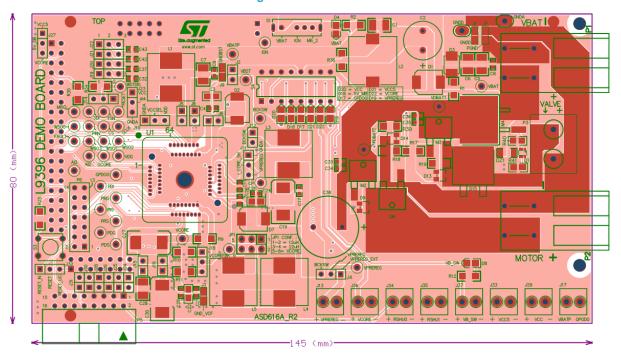

## 2 Device configuration

The L9396 device provides several configurable blocks in order to fit many application scenarios. The present paragraph is intended to help application engineer to properly setup the application when a particular scenario is needed.

As reference the L9396 demo board will be used.

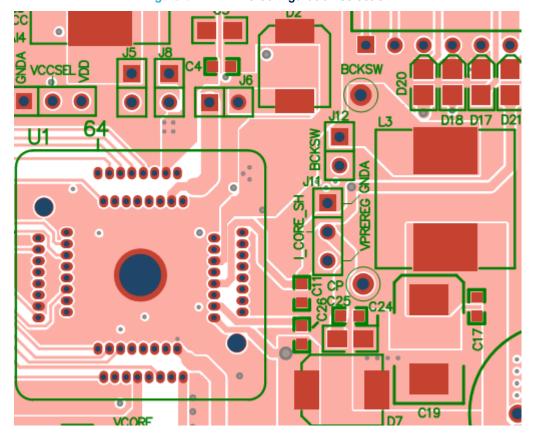

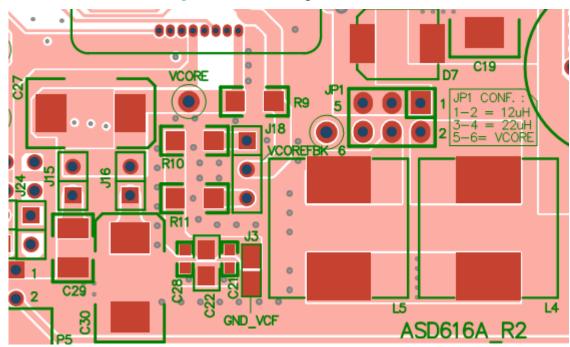

Figure 2. Demo board

## 2.1 Input voltage regulator setup

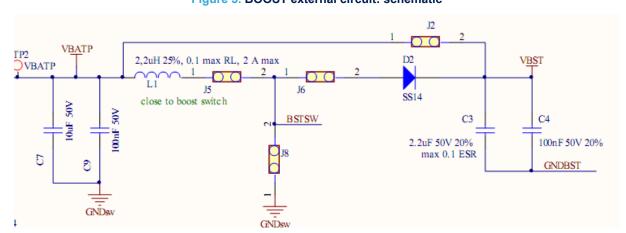

### 2.1.1 BOOST

BOOST is used to guarantee operation at low battery (especially during cranking condition).

The block is capable of 300 mA @ VBST with VBATP = 4,5 V in order to avoid reset during the low battery event. The overall consumption from VBST should not exceed this value.

Figure 3. BOOST external circuit: schematic

AN5702 - Rev 2 page 3/26

life.augmented

WWW.st.com

C43

C42

C7

J2

C37

WDTDIS

VBST

C32

VCC

AIA

J5

J8

C4

J6

CNDA

Figure 4. BOOST external circuit: layout

In case BOOST is needed components can be placed following the Table 1.

In case the BOOST is not needed, VBST could be simple shorted to VBATP and BSTSW must be tied to GND. Without BOOST the input battery can be still lowered until 6 V without getting RESET.

Name Condition Setup Open VBST to be BOOSTED J2 Close VBST directly connected to VBST Open Inductor not used J5 Close **BOOST** inductor connected Open Diode not connected J6 BOOST diode used Close Open BSTSW connected to external LD J8 Close BSTSW to GND to disable BOOST

Table 1. BOOST jumper configuration

AN5702 - Rev 2 page 4/26

## 2.2 Output voltage regulators setup

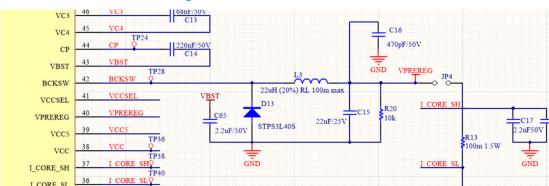

#### 2.2.1 VPREREG

VPREREG is the regulated voltage used as supply for other regulators (WSS, tracking, VCC, VCC5, and VCORE).

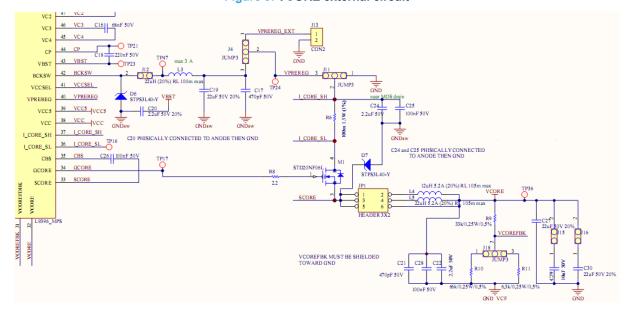

In the Figure 5 and the Figure 6 the application circuit with reference to application board snapshot is shown.

Figure 5. VPREREG external circuit

The regulator default value is 6.5 V and is restored in reset condition.

If needed, the MCU can adjust the value to 7.2 V after RESET is released by setting via SPI the LSB in the register SYS\_CONFIG\_1.

VPREREG BUCK can be also completely disabled if not needed (see next dedicated section), but in this case also VCORE will be disabled.

AN5702 - Rev 2 page 5/26

The regulator was designed, qualified and validated to start the power-up sequence assuming that the VPREREG residual bias is close to 0 V. The effect of a residual voltage on VPREREG pin on the start-up sequence was not assessed during the device development.

To ensure that the VPREREG pin is close to 0 V, it is recommended to insert a pull-down resistor on the VPREREG pin (see R20, Figure 5).

The value suggested by ST for the pull-down resistor is 10k ohms, a value that comes from two considerations:

- The regulator can have two output values, 6.5 V or 7.2 V. With a 10k ohm pull-down resistor connected to the VPREREG node, there will be a current constantly flowing to ground equal to  $650 \mu \text{A}$  (VPREREG = 6.5 V) or  $720 \mu \text{A}$  (VPREREG = 7.2 V).

- The pull-down resistor (R20) is in parallel with the output capacitor of the regulator (C15, see Figure 5), causing a delay in the device's power-up.

To evaluate the power-on time of the regulator, it is necessary to calculate the time constant of the parallel R20// C15. C16 is in parallel with C15, but since its value is much smaller than C15, it can be ignored. The time constant considering R20 = 10 k $\Omega$  with the capacitor C15 = 22  $\mu$ F is (R20 x C15) 0.22s.

Each customer can size the resistance value in according to their needs.

AN5702 - Rev 2 page 6/26

#### 2.2.2 VCC

VCC is linear regulator with selectable output voltage between 3.3 V and 5 V and 2% tolerance.

At device power up VCCSEL is latched and if VCCSEL is less than 0.75~V then VCC works as a liner 3.3~V voltage regulator; while if VCCSEL is grater than 1.75~V then VCC has 5~V output.

In case 5 V is needed it is recommended to connect VCCSEL to VPREREG.

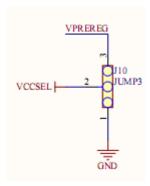

Figure 7. VCC external circuit and configuration selection

Note: VCC is also used internally as the reference voltage for microcontroller IO pin.

#### 2.2.3 **VCORE**

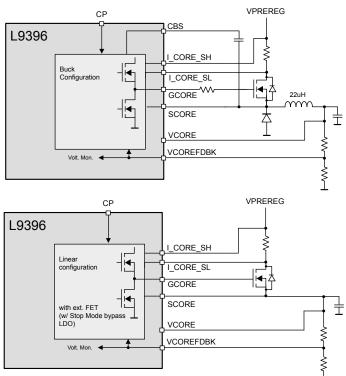

VCORE is a voltage regulator that can work as linear, if SCORE is directly connected to VCORE, or buck, when external inductor is present. VCOREFDBK voltage level is regulated to  $0.8 \text{ V} \pm 2\%$  (or  $\pm 3\%$  in case of buck configuration); as shown in the Figure 9 and the Figure 10 on the Application Board, the external feedback network values are chosen to generate a VCORE = 1.2 V or VCORE = 5 V depending on J18 jumper configuration.

CASE #1

$$VCORE = \frac{R_9 + R_{11}}{R_{11}} \times VCOREFDBK \cong 5V$$

(1)

CASE #2

$$VCORE = \frac{R_9 + R_{10}}{R_{10}} \times VCOREFDBK \cong 1.2V$$

(2)

AN5702 - Rev 2 page 7/26

Figure 8. VCORE external circuit in linear and buck mode

Figure 9. VCORE external circuit

AN5702 - Rev 2 page 8/26

Figure 10. VCORE configuration selection

Table 2. VCORE configuration based on jumpers

| Name | Setup           | Condition                        | Note                                                    |

|------|-----------------|----------------------------------|---------------------------------------------------------|

| J4   | P1 to P2        | VPREREG connected to ext. source |                                                         |

| J4   | P2 to P3        | VPREREG connected to buck        | -                                                       |

| J11  | P1 to P2        | I_CORE_SH to GND                 | See buck regs disabled paragraph                        |

| JII  | P2 to P3        | VCORE buck connected to VPREREG  | -                                                       |

| J15  | Open            | No C load                        | -                                                       |

| 313  | Close           | Additional 10 µF load on VCORE   | To be used in linear mode                               |

| J16  | Open            | No C load                        | To be used in buck mode when VCORE = 1.2 V              |

| 310  | Close           | Additional 22 µF load on VCORE   | To be used in buck mode when VCORE - 1.2 V              |

|      | P5 to P6 closed | No Inductor                      | To be used in linear regulator mode                     |

|      | Others open     | No inductor                      | To be used in inteal regulator mode                     |

|      | P1 to P2 closed | Inductor = 12 µH                 | To be used when buck regulator configured and VCORE =   |

|      | Others open     | πιααστοί – 12 μπ                 | 1.2 V                                                   |

| JP1  | P3 to P4 closed | Inductor = 22 µH                 | To be used when buck regulator configured and VCORE = 5 |

|      | Others open     | middeler 22 pri                  | V                                                       |

|      | P1 to P2 close  |                                  |                                                         |

|      | P3 to P4 close  | Inductor ≈ 8 µH                  | Not used                                                |

|      | P5 to P6 open   |                                  |                                                         |

| J18  | P1 to P2        | VCORE = 1.2 V                    |                                                         |

| 010  | P2 to P3        | VCORE = 5 V                      |                                                         |

Once the VCORE voltage is selected, the Al0 an Al1 inputs need to be configured according to the Table 3.

AN5702 - Rev 2 page 9/26

| Table 3. VCOR | E voltage | configuration | selection |

|---------------|-----------|---------------|-----------|

|---------------|-----------|---------------|-----------|

| N | VCORE voltage | Pin setup <sup>(1)</sup> |      |

|---|---------------|--------------------------|------|

| - | Nominal Value | AI0                      | Al1  |

| 1 | 3.3 V         | Low                      | Low  |

| 2 | 5 V           | Low                      | High |

| 3 | 0.8 V to 5 V  | High                     | Low  |

<sup>1.</sup> Connection to VPREREG is recommended when a "High" is present inside this table.

A minimum load of 10 mA should be placed when VCORE is used in BUCK mode and 70 mA in linear mode. Besides if VCORE is configured as BUCK with output voltage at 3.3 V or 5 V, and a fast switch off / switch ON is applied for example through IGN, the automatic detection of BUCK circuit could not work when VCORE and SCORE pins have not time to discharge; if this happens, then VCORE MODE is latched as LINEAR and not as BUCK. The corresponding bit in the CONTROL\_SUPPLY\_1 is updated accordingly.

In case the application could face such case, it is recommended to apply a minimum load so that VCORE drops under 2.6 V before a new power up is present

$$Iload_{MIN} = \frac{C_{VCORE}(VCORE - 2.6)}{\Delta t_{MIN}}$$

(3)

Where  $\Delta t_{MIN}$  is the minimum time so that a new power up is needed. Besides MCU must always check the CONTROL\_SUPPLY\_1 bit in order to check the correctness of configured regulators and take proper actions (safe state) in case of issue.

There is also the possibility to completely disable VCORE regulator as shown in the following paragraph.

AN5702 - Rev 2 page 10/26

## 2.2.4 Unused regulators and VCORE configuration mode

In order to provide flexibility for the power management, the IC provides several voltage regulators.

In some applications, VPREREG and/or VCORE are not needed. In order to save money by reducing BOM, L9396 allow a useful mode in which no external component need to be connected to BUCK regulators.

The available setups are shown in the Table 4.

At device power up, regulator configuration is detected through pins state and applied; it is also latched inside IC in the registers SUPPLY\_CONTROL\_2, bit 16 VCORE\_MONITOR TYPE and SUPPLY\_CONTROL\_2, bit 17 (VCORE OFF LATCHED) and bit 18 (BUCK OFF LATCHED).

Table 4. Unused regulator configuration

| N | R             | egulators Configura |                               | Pin setup <sup>(1)</sup> |            |           |

|---|---------------|---------------------|-------------------------------|--------------------------|------------|-----------|

| - | VPREREG state | VCORE state         | VCORE monitor                 | AI0                      | Al1        | I_CORE_SH |

| 1 | Enabled       | Enabled             | VCORE_UV_L,<br>VCORE_OV_L     | Low                      | Low        | High      |

| 2 | Enabled       | Enabled             | VCORE_UV_H,<br>VCORE_OV_H     | Low                      | High       | High      |

| 3 | Enabled       | Enabled             | VCOREFDBK_UV,<br>VCOREFDBK_OV | High                     | Low        | High      |

| 4 | Enabled       | Disabled            | NA                            | High                     | High       | High      |

| 5 | Disabled      | Disabled            | NA                            | Don't care               | Don't care | Low       |

<sup>1.</sup> Connection to VPREREG is recommended when a "High" is present inside this table.

For example, if only VCORE needs to be disabled and BUCK VPREREG must be active, the following configuration can be used:

Table 5. VCORE unused configuration

| Pin Name                 | Condition                 |

|--------------------------|---------------------------|

| AI0, AI1                 | Connected to high voltage |

| I_CORE_SH, I_CORE_SL     | Connected to high voltage |

| GCORE, SCORE, CBS, VCORE | OPEN                      |

| VCOREFDBK                | OPEN                      |

When both VPREREG are not needed in the application, in order to have the minimum BOM cost, the following conditions described below should be used:

Table 6. VPREREG/VCORE unused configuration

| Pin Name                 | Condition         |

|--------------------------|-------------------|

| BCKSW                    | OPEN              |

| VPREREG                  | Connected to VBST |

| I_CORE_SH, I_CORE_SL     | Connected to GND  |

| GCORE, SCORE, CBS, VCORE | OPEN              |

| VCOREFDBK                | OPEN              |

AN5702 - Rev 2 page 11/26

## 2.3 Other configurations setup

#### 2.3.1 Device pin configuration

The L9396 offers functional configurability for the following device pin:

- FAULT pin is a useful output which can be set as lamp driver or as interrupt (active high) through SPI

- GPOD0 is a LS driver which can be used for different purpose

- FSN pin is a very smart configurable output for failsafe usage

Device can be configured by writing the specific SPI registers associated with those outputs. After setting the relative bits, application may lock the writing of SAFE registers by WRITE PROTECTION register writing.

#### Example 1:

Suppose we need the following configurations: FAULT as lamp driver, GPOD0 as an ON/OFF driver.

After MCU startup and reset release, the following SPI registers should be written:

- ADV CONFIG, bit 12 = 1

- SYS\_CONFIG2, bit 11 = 1 , bit 13:12 = "10"

- DRV\_CONTROL, bit 18 = 1 (accepted only with WD Q&A served)

Note: WD PRN should be configured as described in the dedicated section in order to correctly execute the sequence.

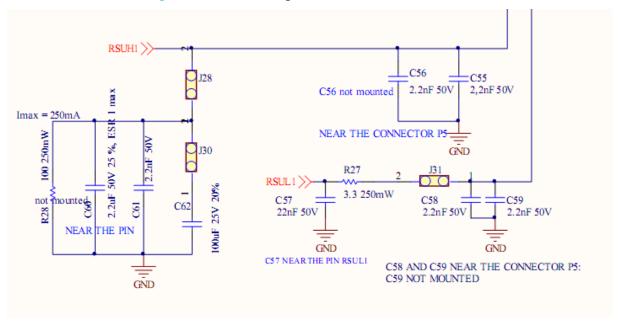

#### 2.3.2 Tracking regulator/WSS interface configuration

Tracking regulator or WSS interface can be selected by properly setting jumpers as shown in the Table 7 and the Table 8.

Tracking regulator configuration is possible only on RSU0/RSU1 as described in the following figure.

C46 J24 2.2nF 50V 2,2nF 50V max C46 not mounted Imax = 250mAESE 100 250mW 25 % GND NEAR THE CONNECTOR P5 200 3.3 250mW J26 2.2uF C53 not mounted 000 RSULO\ 25V R23 C48 NEAR THE PIN 100mF 2.2nF 50V 22nF 50V 2.2nF 50V GND GND GND

Figure 11. WSS/Track regulators schematic for channel 0

AN5702 - Rev 2 page 12/26

Figure 12. WSS/Track regulators schematic for channel 1

Table 7. Tracking regulator channel 0 configuration based on jumpers

| Name | Setup                                  | Condition                                                                                                                  | Note |  |  |

|------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|--|--|

| J24  | Open                                   | No RC external Network on RSUH0 pin                                                                                        |      |  |  |

| J24  | Close RC external Network on RSUH0 pin |                                                                                                                            |      |  |  |

| 125  | DOLLING Sin                            | External Network on RSUHx pin to be used when device is set as Tracking regulator. In this case RSULx is left unconnected. |      |  |  |

| J25  |                                        |                                                                                                                            |      |  |  |

| 126  | Open                                   | RSUL0 not connected                                                                                                        |      |  |  |

| J26  | Close                                  | RSUL0 connected to WSS                                                                                                     |      |  |  |

Table 8. Tracking regulator channel 1 configuration based on jumpers

| Name | Setup                                  | Condition                           | Note                                                                                                                       |  |  |  |

|------|----------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| J28  | Open                                   | No RC external Network on RSUH1 pin |                                                                                                                            |  |  |  |

| 320  | Close RC external Network on RSUH1 pin |                                     |                                                                                                                            |  |  |  |

| J30  | Open                                   | No Additional load on RSUH1 pin     | External Network on RSUHx pin to be used when device is set as Tracking regulator. In this case RSULx is left unconnected. |  |  |  |

| 330  | Close                                  | Additional load on RSUH1 pin        |                                                                                                                            |  |  |  |

| J31  | Open                                   | RSUL1 not connected                 |                                                                                                                            |  |  |  |

| 331  | Close                                  | RSUL1 connected to WSS              |                                                                                                                            |  |  |  |

If tracking regulators are needed, after RESET is released MCU should write SPI register CONFIGURATION 1 in order to enable the tracking regulators. In the same register it must also be written the reference tracking voltage between VCC/VCC5.

AN5702 - Rev 2 page 13/26

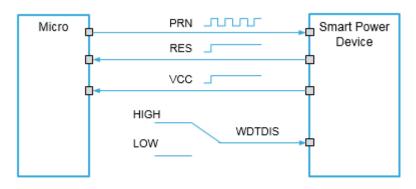

#### 2.3.3 WD configuration

The L9396 have 2 configurable watchdogs in order to adapt to several safety levels:

- WD Q & A based on SPI

- WD PRN controlled by pin

The first watchdog is always needed in order to control drivers (pump motor, GPOD, FS driver, VBAT switch) while the second one can be disabled by setting WDTDIS to a voltage greater than 1.75 V.

After power up the device need WD2 (if enabled) but not WD1; WD1 monitoring is activated after the first access to WD\_SEED\_ANSW register and from this point the device check for WD protocol.

Figure 13. WD2 connection diagram

The device gives the possibility to adjust the WD2 PRN frequencies according the application need. In case the desired values are different from the default ones, the MCU should adjust the ADV\_CONFIG register (bit WD2 T OFF and bit WD2 MAX FREQ) before the TWAIT time (see the Figure 14).

RESET

UC STARTUP NORMAL OPERATION

WDTDIS Logic Hi TWAIT

Logic Lo

PRN

Figure 14. WD2 timing diagram

#### 2.3.4 ADC configuration

The L9396 integrates a 10 bit analog to digital converter which can be used to monitor both internal and external voltages and also device temperature.

The ADC operate outside reset and can be configured through ADC CONFIG register in order to average the input voltage before storing the value on device registers.

The setting of this feature to 8/16 samples is strongly recommended above all when BOOST regulator is used.

AN5702 - Rev 2 page 14/26

#### 2.3.5 GPO

The GPO output is an integrated LS with different possible configurations depending on programmed values in GPO\_DRIVER\_CONFIG[1:0] bits in SYS\_CONFIG\_2 register.

The GPO COMMAND bit of DRV\_CONTROL 1 register is used in ON/OFF mode, while for other configurations (eg. in PWM mode) is ignored because the driver command is generated automatically by a PWM generator.

The GPO DRIVER ENABLE bit of SYS\_CONFIG2 works for all the configurations.

## 2.3.6 Unused configuration for RSUx, PUMP

In case RSU are not used the following settings need to be applied:

- RSUHx = OPEN

- RSULx = OPEN

- WSOx = OPEN

When PUMP is not needed the following setup is advised:

- PRI = PDI = GND

- PDG = PRG = OPEN

- PDS = PRS = GND

- PDBATT = OPEN

AN5702 - Rev 2 page 15/26

## Note and suggestions on layout

## 3.1 PCB layout guideline

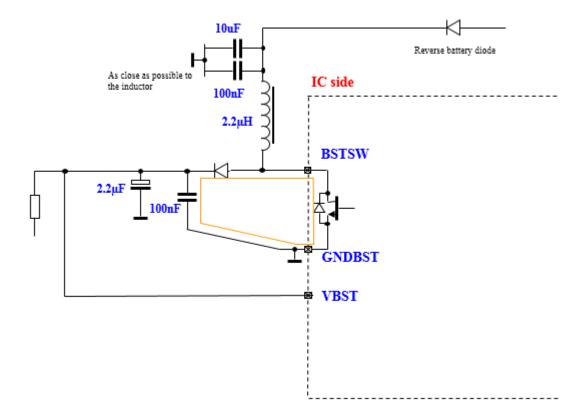

## 3.1.1 BOOST regulator

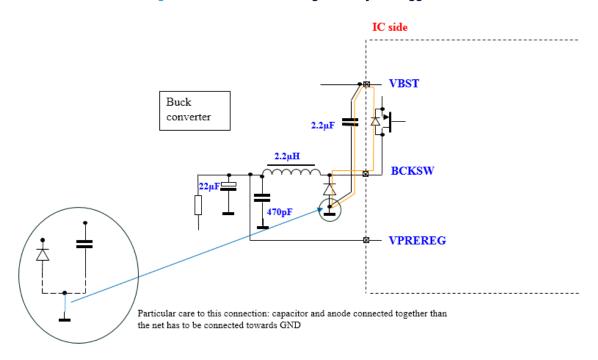

The BOOST regulator has a 2 MHz operating frequency and allow the usage of a  $2.2~\mu H$  inductor. In order to improve EMC performances, the external components should be placed to make the area of the loop highlighted in orange as small as possible.

Figure 15. BOOST regulator layout indication

AN5702 - Rev 2 page 16/26

#### 3.1.2 BUCK pre-regulator

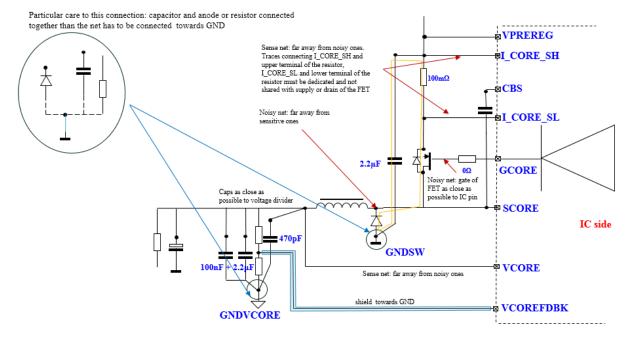

Particular care should be put on the routing of the connection between the anode of the recirculation diode, the terminal of the noise bypass capacitor and the ground.

The connection should be realized not through independent paths but following the rule showed in the Figure 16.

Figure 16. VPREREG buck regulator layout suggestions

### 3.1.3 VCORE voltage regulator

In order to have high flexibility, VCORE has been implemented with an architecture compatible with both linear and buck configuration where the regulated voltage can be fully configurable through R1 and R2, external feedback resistors, in (0.8-5 V) range; the following guidelines refers to buck configuration which is the most critical from layout point of view; layout for linear case can be extrapolated as well.

In order to guarantee the performances reported in the datasheet for these regulators, particular attention should be done on managing external components placement and path routing.

Particular care should be put on the routing of the connection between the anode of the recirculation diode, the terminal of the noise bypass capacitor and the ground. The connection should be realized not through independent paths but following the rule showed in the Figure 17.

In order to improve EMC performances, the external components should be placed to make the area of the loop highlighted in orange as small as possible.

In order to minimize parasitic effect of the path which connects GCORE to the gate terminal of the external FET, the FET should be placed as near as possible to IC pins.

Being the value of the regulated voltage depending on the voltage on VCOREFDBK, any accidental coupling effect on this net strongly affects the behavior of the regulator output. For this reason, ST recommends a dedicated ground connection for the external voltage divider, and to shield towards GND the path which connects the VCOREFDBK to the middle point of the voltage divider. For further improvements, a capacitor in parallel to the voltage divider can be mounted: the connection towards ground should be realized not through independent paths but following the rule showed below.

AN5702 - Rev 2 page 17/26

Figure 17. VCORE buck regulator layout suggestions

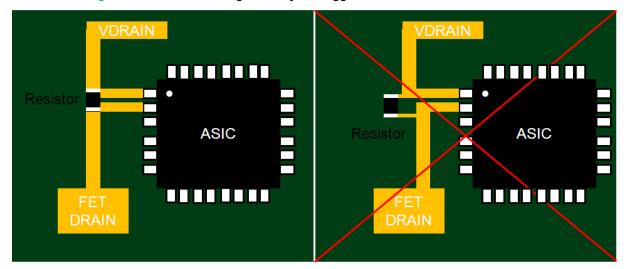

In order to achieve good performance in terms of precision, some rules should be followed for the placement and routing of the 100mohm resistor between I\_CORE\_SH and I\_CORE\_SL: these are sense nets and must be far away from noisy ones. Besides, traces connecting I\_CORE\_SH and upper terminal of the resistor, I\_CORE\_SL and lower terminal of the resistor must be dedicated and not shared with regulator supply (VDRAIN) and drain of the external FET.

For sake of clarification, an example is reported in the Figure 18: on the left side the connection is realized as per ST recommendation while in the right side isn't.

Figure 18. VCORE buck regulator layout suggestions for external sense resistor

AN5702 - Rev 2 page 18/26

### 3.1.4 Battery operating ranges

As specified in DS, L9396 is capable of operate up to 19 V of VB; however the device has been analyzed in order to understand the behavior during load dump and jump start pulses with the following result:

- For 18 V < VS < 28 V, device in jump start condition, all functions are guaranteed, parameter "ton/toff high side" degradated to 80 ns;

- For 28 V < VS < 35 V, device in load dump condition w/o application fault violating device AMR, functions

are guaranteed and no damage.</li>

#### 3.1.5 STM8 microcontroller connector cross reference

The L9396 Demo Board provides the connection to the STM8 Evaluation board through the U2. On the Table 9 the cross reference connection table between L9396 Demo Board and the STM8 Evaluation board is shown. Note that not all the signals are physically connected.

Table 9. L9396 to STM8 cross connection

| J27 L9396 to STM8 cross connection |          |                    |          |                          |            |            |

|------------------------------------|----------|--------------------|----------|--------------------------|------------|------------|

| DIN #                              | Α        |                    | В        |                          | С          | D          |

| PIN#                               | L9396    | STM8               | L9396    | STM8                     | L9396 STM8 | L9396 STM8 |

| 1                                  | 5V_DB    | 5V_DB              | RESET_UC | NRESET                   | n.c.       | n.c.       |

| 2                                  | 5V_MB    | 5V_Perm            |          | n.c.                     | n.c.       | n.c.       |

| 3                                  | FSN      | PB0/AIN0/TIM1_NCC1 |          | n.c.                     | n.c.       | n.c.       |

| 4                                  | RESET_IN | PB1/AIN1/TIM1_NCC2 |          | n.c.                     | n.c.       | n.c.       |

| 5                                  |          | n.c.               |          | n.c.                     | n.c.       | n.c.       |

| 6                                  |          | n.c.               |          | n.c.                     | n.c.       | n.c.       |

| 7                                  | WDIS_AN  | PB4/ <u>AIN4</u>   |          | n.c.                     | n.c.       | n.c.       |

| 8                                  | VCORE    | PB5/ <u>AIN5</u>   |          | n.c.                     | n.c.       | n.c.       |

| 9                                  | VCC      | PB6/ <u>AIN6</u>   | CS       | PE5/SPI_NSS              | n.c.       | n.c.       |

| 10                                 | VDD      | PB7/ <u>AIN7</u>   | SCLK     | PC5/SPI_SCK              | n.c.       | n.c.       |

| 11                                 |          | n.c.               | MOSI     | PC6/SPI_MOSI             | n.c.       | n.c.       |

| 12                                 |          | n.c.               | MISO     | PC7/SPI_MISO PIU20 PIU20 | n.c.       | n.c.       |

| 13                                 |          | n.c.               | ALT_CS   | PE1/I2C_SCL              | n.c.       | n.c.       |

| 14                                 | n.c.     |                    |          | n.c.                     | n.c.       | n.c.       |

| 15                                 |          | n.c.               | n.c.     |                          | n.c.       | n.c.       |

| 16                                 |          | n.c.               |          | n.c.                     | n.c.       | n.c.       |

| 17                                 |          | n.c.               |          | n.c.                     | n.c.       | n.c.       |

| 18                                 |          | n.c.               |          | n.c.                     | n.c.       | n.c.       |

| 19                                 | PRN      | PA3/TIM2_CC3       |          | n.c.                     | n.c.       | n.c.       |

| 20                                 |          | n.c.               |          | n.c.                     | n.c.       | n.c.       |

| 21                                 | WSO0     | PC1(HS)/TIM1_CC1   |          | n.c.                     | n.c.       | GND        |

| 22                                 | WSO1     | PC2(HS)/TIM1_CC2   |          | n.c.                     | n.c.       | GND        |

| 23                                 | WSO2     | PC3(HS)/TIM1_CC3   |          | n.c.                     | n.c.       | GND        |

| 24                                 | WSO3     | PC4(HS)/TIM1_CC4   |          | n.c.                     | n.c.       | GND        |

| 25                                 | PRI      | PD0(HS)/TIM3_CC2   |          | n.c.                     | n.c.       | GND        |

| 26                                 | PDI      | PD2(HS)/TIM3_CC1   |          | n.c.                     | n.c.       | GND        |

| 27                                 | AI1_UC   | PD3(HS)/TIM2_CC2   |          | n.c.                     | n.c.       | GND        |

| 28                                 | AI0_UC   | PD4(HS)TIM2_CC1    |          | n.c.                     | n.c.       | GND        |

AN5702 - Rev 2 page 19/26

| J27 L9396 to STM8 cross connection |           |               |       |      |       |           |       |      |    |

|------------------------------------|-----------|---------------|-------|------|-------|-----------|-------|------|----|

| DIN #                              | A         |               |       | В    |       | С         |       | D    |    |

| PIN#                               | L9396     | STM8          | L9396 | STM8 | L9396 | STM8      | L9396 | STM8 |    |

| 29                                 |           | n.c.          |       | n.c. | n     | .C.       | GN    | 1D   |    |

| 30                                 |           | n.c.          |       | n.c. | n     | .C.       | GN    | 1D   |    |

| 31                                 |           | n.c.          |       | n.c. | n     | .C.       | n.e   | c.   |    |

| 32                                 | WK_INT    | PE4           |       | n.c. |       | n.c. n.c. |       | n.e  | c. |

| 33                                 | GATE3/IGN | PH7/TIM1_NCC1 | n.c.  |      | n     | .C.       | n.e   | c.   |    |

| 34                                 |           | n.c.          | n.c.  |      | n     | .C.       | n.e   | c.   |    |

| 35                                 | n.c.      |               | n.c.  |      | n     | .C.       | n.e   | c.   |    |

| 36                                 |           | n.c.          |       | n.c. |       | .C.       | n.e   | c.   |    |

| 37                                 | FAULT     | PH3           | n.c.  |      | n     | .C.       | n.e   | c.   |    |

| 38                                 | n.c.      |               | n.c.  |      | n     | .C.       | n.e   | c.   |    |

| 39                                 | n.c.      |               |       | n.c. | n     | .C.       | n.e   | c.   |    |

| 40                                 |           | n.c.          |       | n.c. | n     | .C.       | n.e   | c.   |    |

## 3.1.6 Test point list

Table 10. Test point list

| Name | Description |

|------|-------------|

| TP1  | VBAT        |

| TP2  | VBATP       |

| TP3  | GND         |

| TP4  | FAULT       |

| TP5  | WSO3        |

| TP6  | WSO2        |

| TP7  | WS01        |

| TP8  | CS          |

| TP9  | PRN         |

| TP10 | SCLK        |

| TP11 | MOSI        |

| TP12 | MISO        |

| TP13 | FSN         |

| TP14 | RESET       |

| TP15 | WSO0        |

| TP16 | I_CORE_SL   |

| TP17 | GCORE       |

| TP18 | VDG         |

| TP19 | Al1         |

| TP20 | AlO         |

| TP21 | CP          |

| TP22 | VDBATT      |

AN5702 - Rev 2 page 20/26

| Name | Description |

|------|-------------|

| TP23 | VBST        |

| TP24 | VPREREG     |

| TP25 | WDTDIS      |

| TP26 | Al3         |

| TP27 | Al2         |

| TP28 | IGN         |

| TP34 | GPOD0       |

| TP35 | PDI         |

| TP36 | VCORE       |

| TP37 | PRI         |

| TP38 | PRG         |

| TP39 | PRS         |

| TP40 | PDG         |

| TP41 | PDS         |

| TP42 | PDBATT      |

| TP47 | BCKSW       |

| TP48 | GNDD        |

AN5702 - Rev 2 page 21/26

## **Revision history**

**Table 11. Document revision history**

| Date        | Version | Changes               |

|-------------|---------|-----------------------|

| 09-Sep-2021 | 1       | Initial release.      |

| 22-Sep-2025 | 2       | Update Section 2.2.1. |

AN5702 - Rev 2 page 22/26

## **Contents**

| 1  | Bloc   | k diagr | ram                                            | 2  |

|----|--------|---------|------------------------------------------------|----|

| 2  | Devi   | ice con | figuration                                     | 3  |

|    | 2.1    | Input v | voltage regulator setup                        | 3  |

|    |        | 2.1.1   | BOOST                                          | 3  |

|    | 2.2    | Outpu   | t voltage regulators setup                     | 5  |

|    |        | 2.2.1   | VPREREG                                        | 5  |

|    |        | 2.2.2   | VCC                                            | 7  |

|    |        | 2.2.3   | VCORE                                          | 7  |

|    |        | 2.2.4   | Unused regulators and VCORE configuration mode | 11 |

|    | 2.3    | Other   | configurations setup                           | 12 |

|    |        | 2.3.1   | Device pin configuration                       | 12 |

|    |        | 2.3.2   | Tracking regulator/WSS interface configuration | 12 |

|    |        | 2.3.3   | WD configuration                               | 14 |

|    |        | 2.3.4   | ADC configuration                              | 14 |

|    |        | 2.3.5   | GPO                                            | 15 |

|    |        | 2.3.6   | Unused configuration for RSUx, PUMP            | 15 |

| 3  | Note   | and su  | uggestions on layout                           | 16 |

|    | 3.1    |         | ayout guideline                                |    |

|    |        | 3.1.1   | BOOST regulator                                | 16 |

|    |        | 3.1.2   | BUCK pre-regulator                             | 17 |

|    |        | 3.1.3   | VCORE voltage regulator                        | 17 |

|    |        | 3.1.4   | Battery operating ranges                       | 19 |

|    |        | 3.1.5   | STM8 microcontroller connector cross reference | 19 |

|    |        | 3.1.6   | Test point list                                | 20 |

| Re | vision | history | ,                                              | 22 |

## **List of tables**

| Table 1.  | BOOST jumper configuration                                  | 4  |

|-----------|-------------------------------------------------------------|----|

| Table 2.  | VCORE configuration based on jumpers                        | Ĉ  |

| Table 3.  | VCORE voltage configuration selection                       | 10 |

| Table 4.  | Unused regulator configuration                              | 11 |

| Table 5.  | VCORE unused configuration                                  | 11 |

| Table 6.  | VPREREG/VCORE unused configuration                          | 11 |

| Table 7.  | Tracking regulator channel 0 configuration based on jumpers | 13 |

| Table 8.  | Tracking regulator channel 1 configuration based on jumpers | 13 |

|           | L9396 to STM8 cross connection                              |    |

| Table 10. | Test point list                                             | 20 |

| Table 11. | Document revision history                                   | 22 |

# **List of figures**

| Figure 1.  | Application block diagram                                           | . 2 |

|------------|---------------------------------------------------------------------|-----|

| Figure 2.  | Demo board                                                          | . 3 |

| Figure 3.  | BOOST external circuit: schematic                                   | . 3 |

| Figure 4.  | BOOST external circuit: layout                                      | . 4 |

| Figure 5.  | VPREREG external circuit                                            | . 5 |

| Figure 6.  | VPREREG configuration selection                                     | . 5 |

| Figure 7.  | VCC external circuit and configuration selection                    | . 7 |

| Figure 8.  | VCORE external circuit in linear and buck mode                      | . 8 |

| Figure 9.  | VCORE external circuit                                              | . 8 |

| Figure 10. | VCORE configuration selection                                       | . 9 |

| Figure 11. | WSS/Track regulators schematic for channel 0                        | 12  |

| Figure 12. | WSS/Track regulators schematic for channel 1                        | 13  |

| Figure 13. | WD2 connection diagram                                              | 14  |

| Figure 14. | WD2 timing diagram                                                  | 14  |

| Figure 15. | BOOST regulator layout indication                                   | 16  |

| Figure 16. | VPREREG buck regulator layout suggestions                           |     |

| Figure 17. | VCORE buck regulator layout suggestions                             | 18  |

| Figure 18. | VCORE buck regulator layout suggestions for external sense resistor | 18  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

AN5702 - Rev 2 page 26/26