# How to implement low-power modes on the STM32MP2 MPUs

### Introduction

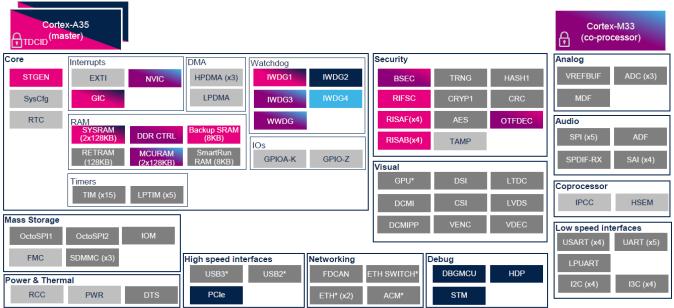

The STM32MP21x, STM32MP23x and STM32MP25x microprocessor devices are built on an Arm<sup>®</sup> Cortex<sup>®</sup>-A35 with single or dual-core CPU subsystem, called CPU1 combined with an Arm<sup>®</sup> Cortex<sup>®</sup>-M33 MCU, called CPU2.

The STM32MP21x, STM32MP23x and STM32MP25x microprocessor devices are referred to as STM32MP2 devices from now on

The STM32MP2 devices are dynamically configurable to adapt the power consumption to the most appropriate power mode. The objective is to maintain the power consumption to the most efficient level.

This application note explains:

- The various low-power modes of STM32MP2 devices

- How to configure them

- How to exit from them.

This document gives guidelines on how to use low-power modes at the system level. It also presents guidelines when using an external STPMIC2x power-regulator component.

The full list of applicable products is given in Table 2, Table 3, and Table 4.

# 1 General information

This document applies to the STM32MP2 Series microprocessor.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

# 1.1 Glossary

The following table contains a non-exhaustive list of terms used in this document.

**Table 1. Glossary**

| Term    | Meaning                                          |

|---------|--------------------------------------------------|

| AHB     | Advanced high-performance bus                    |

| AVD     | Analog voltage detector                          |

| BKPSRAM | Backup SRAM                                      |

| BOR     | Brownout reset                                   |

| BUCK    | Step-down switched-mode power-supply converter   |

| CSS     | Clock security system                            |

| DDR     | Double data rate (SRAM)                          |

| DDRCTRL | DDR controller                                   |

| DDRPHYC | DDR physical interface control                   |

| ETH     | Ethernet controller                              |

| EMMC    | Embedded multi-media card                        |

| EXTI    | Extended interrupts and event controller         |

| FDCAN   | Controller area network with flexible data rate. |

| I DOAN  | Could also support time-triggered CAN (TT)       |

| GPIO    | General-purpose input/output                     |

| GPU     | Graphics processing unit                         |

| HDP     | Hardware debug port                              |

| IRQ     | Interrupt request                                |

| IWDG    | Independent watchdog                             |

| LDO     | Low dropout regulator                            |

| LpDDR   | Low-power DDR                                    |

| LPSRAM  | Low-power SRAM                                   |

| LSE     | Low-speed external quartz oscillator             |

| LSI     | Low-speed internal oscillator                    |

| LVDS    | Low Voltage Differential Signaling               |

| MCU     | Microcontroller                                  |

| MPU     | Microprocessor                                   |

| MLAHB   | Multilayer AHB/AHB-based interconnect            |

| MPU     | Microprocessor                                   |

| OP-TEE  | Open portable trusted execution environment      |

| PLL     | Phase-locked loop                                |

AN5726 - Rev 2 page 2/50

| Term      | Meaning                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PVD       | Programmable voltage detector                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PWR       | Power control block                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PSCI      | Power state and coordination interface                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| OCTOSPI   | Octal data lanes serial peripheral interface                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RCC       | Reset and clock control                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RETRAM    | Retention RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RIF       | Resource isolation framework                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RTC/TAMP  | Real time clock/tamper management                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SDMMC     | Secure digital and multimedia card interface.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| SDIVIIVIC | Supports SD, MMC, eMMC, and SDIO protocols                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SMPS      | Switched mode power supply converter                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SRAM      | Static random-access memory                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| STPMIC2   | Power management-integrated circuit. An external circuit that provides a platform with extensive control over the power supplies through signals and serial interface.  STPMIC25A (for 3.3 V on V <sub>DD</sub> application) and STPMIC25B (for 1.8 V on V <sub>DD</sub> application) are available on STM32MP2 devices.  STPMIC2LA (for 3.3 V on V <sub>DD</sub> application) and STPMIC2LB (for 1.8 V on V <sub>DD</sub> application) are available on all STM32MP2 devices. |

| SYSRAM    | System SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SW        | Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TEMP      | Temperature sensor                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TEMPH-L   | Temperature sensor high-low monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TF-A      | Trusted firmware for Cortex®-A                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| USART     | Universal synchronous/asynchronous receiver transmitter                                                                                                                                                                                                                                                                                                                                                                                                                        |

| USB OTG   | Universal serial bus (USB) on-the-go (OTG).                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 000010    | A standard USB interface able to become a host or device                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VBATH-L   | VBAT high-low monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VTT       | DDR termination resistance power-supply                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WFE       | Wait for event                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| WFI       | Wait for interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### 1.2 Reference documents

For further information on STM32MP2 MPUs, refer to the following documents and deliverables available on www.st.com.

- STM32MP2 product line reference manuals (see Table 2, Table 3 and Table 4 for details)

- STM32MP2 product line datasheets

- STPMIC2x datasheet

- Getting Started with STM32MP25x lines hardware development (AN5489)

- Getting Started with STM32MP21x lines hardware development (AN6055)

- How to use STPMIC25 for a wall adapter powered application on STM32MP25x MPUs (AN5727)

- How to use STPMIC2L for a wall adapter powered application on STM32MP21x MPUs (AN6303)

AN5726 - Rev 2 page 3/50

### 2 Overview

This application note is applicable to all the devices that are defined in the introduction. The tables below describe their main characteristics.

Depending on the device part number, the system includes a Cortex<sup>®</sup>-M33, and a Cortex<sup>®</sup>-A35 with either a single-core or a dual-core. In the whole document:

- The Cortex®-A35 is also called CPU1.

- The Cortex<sup>®</sup>-M33 is also called CPU2 or MCU.

- The Cortex<sup>®</sup>-M0+ is also called CPU3.

- The full featured system, as defined in the table below, is partitioned into:

- One CPU1 subsystem: single or dual Cortex<sup>®</sup>-A35 with L2 cache

- One CPU2 subsystem: Cortex<sup>®</sup>-M33 with associated peripherals clocked according to CPU activity

The present document assumes a full featured device, for example the STM32MP257.

Note: The CPU and domain configuration depends on product and are as follows:

- The STM32MP25x has a Cortex®-M0+ also called CPU3. The CPU3 is included in a D3 power domain.

- The STM32MP23x has a D3 power domain but without the Cortex<sup>®</sup>-M0+ CPU3.

- The STM32MP21x has no Cortex®-M0+ CPU3, nor D3 power domain.

So in the rest of this document all information related to CPU3 and associated D3 domain must be considered for the relevant devices only.

| Lines      | Reference manual | Cortex <sup>®</sup> -A35 configuration | Cortex <sup>®</sup> -M33/<br>Cortex <sup>®</sup> -M0+ | GPU | LVDS | FDCAN | ЕТН |

|------------|------------------|----------------------------------------|-------------------------------------------------------|-----|------|-------|-----|

| STM32MP251 |                  | Single-core                            | Yes/Yes                                               | No  | No   | No    | x1  |

| STM32MP253 | RM0457           | Dual-core                              | Yes/Yes                                               | No  | No   | Yes   | x2  |

| STM32MP255 | RIVI0457         | Dual-core                              | Yes/Yes                                               | Yes | Yes  | Yes   | x2  |

| STM32MP257 |                  | Dual-core                              | Yes/Yes                                               | Yes | Yes  | Yes   | хЗ  |

Table 2. STM32MP25x device configuration

Table 3. STM32MP23x device configuration

| Lines      | Reference manual | Cortex <sup>®</sup> -A35 configuration | Cortex <sup>®</sup> -M33/<br>Cortex <sup>®</sup> -M0+ | GPU | LVDS | FDCAN | ЕТН |

|------------|------------------|----------------------------------------|-------------------------------------------------------|-----|------|-------|-----|

| STM32MP231 |                  | Single-core                            | Yes/No                                                | No  | No   | No    | x1  |

| STM32MP233 | RM0457           | Dual-core                              | Yes/No                                                | No  | No   | Yes   | x2  |

| STM32MP235 |                  | Dual-core                              | Yes/No                                                | Yes | Yes  | Yes   | x2  |

Table 4. STM32MP21x device configuration

| Devices    | Reference manual | Cortex <sup>®</sup> -A35 configuration | Cortex <sup>®</sup> -M33/<br>Cortex <sup>®</sup> -M0+ | GPU | DISPLAY | FDCAN | ЕТН |

|------------|------------------|----------------------------------------|-------------------------------------------------------|-----|---------|-------|-----|

| STM32MP211 |                  | Single-core                            | Yes/No                                                | No  | No      | No    | x1  |

| STM32MP213 | RM0506           | Single-core                            | Yes/No                                                | No  | No      | Yes   | x2  |

| STM32MP215 |                  | Single-core                            | Yes/No                                                | No  | Yes     | Yes   | x2  |

AN5726 - Rev 2 page 4/50

The STPMIC2x has several part numbers. The following part numbers are recommended for use with the STM32MP2 series devices:

- STPMIC25APQR for application using V<sub>DD</sub> = 3.3 V

- STPMIC25BPQR for application using V<sub>DD</sub> = 1.8 V

- STPMIC2LAQR for application using V<sub>DD</sub> = 3.3 V

- STPMIC2LBQR for application using  $V_{DD} = 1.8 \text{ V}$

The generic part number "STPMIC2x" is used in the rest of the document. For a specific part number, refer to the above paragraph.

AN5726 - Rev 2 page 5/50

## 3 Power management concept

This section describes the high-level power management concept of STM32MP2 devices. Refer to the corresponding reference manual for more details.

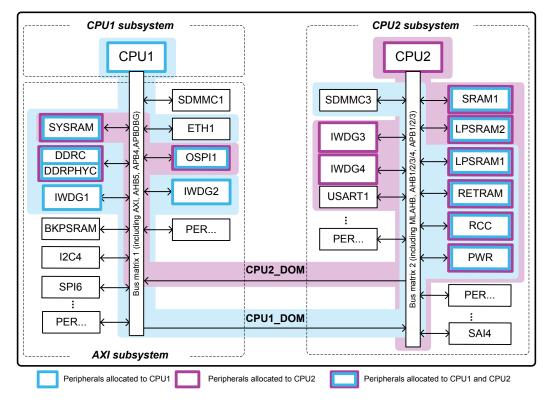

### 3.1 STM32MP2 device system architecture

The STM32MP2 devices are based on:

- a main single or dual-core CPU1 subsystem

- a CPU2 subsystem.

- an optional CPU3 subsystem having mostly system independent power modes.

The multiple core architecture requires specific power modes both at system and at individual subsystem level. Internal digital logic is supplied by the STPMIC2 dedicated for the STM32MP2 devices. The latter has an internal regulator (such as an LDO or SMPS) for such purpose. This key difference results in a different power-supply management for the STM32MP2 devices which requires the use of external signals and STPMIC2x to control the desired voltage supplies.

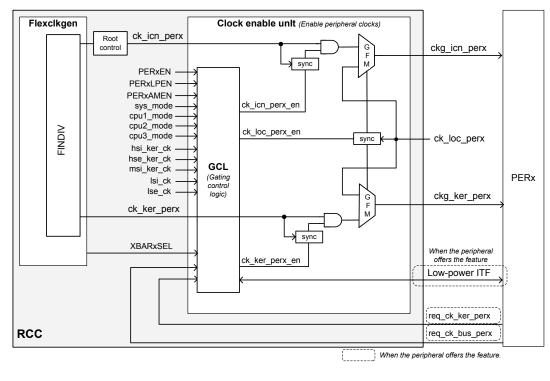

The power management features are spread between the reset clock control (RCC), and the power (PWR) blocks of the STM32MP2 devices.

- The RCC block ensures the clock tree handling, such as PLLs, multiplexers, dividers, clock gating are reset.

- The RCC block manages the resets: the local peripheral, the Cortex<sup>®</sup>-A35, the Cortex<sup>®</sup>-M33, and the

platform.

- The RCC and PWR blocks allow the power mode selection based on the respective power states of the CPU1 and CPU2 subsystems.

- The PWR block is responsible for low-power entry and exit. It drives the control pins (PWR\_ON, PWR\_CPU\_ON, PWR\_LP) to the external regulator based on the power mode.

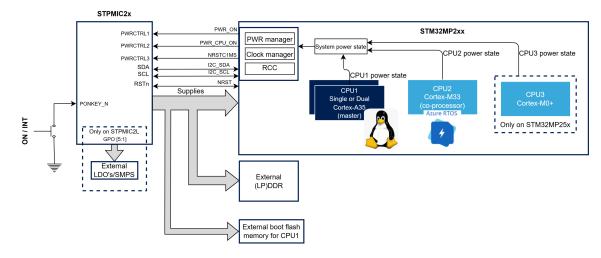

The figure below shows the high-level system architecture of STM32MP2 devices.

Figure 1. STM32MP2 device high-level system architecture

DT74955

AN5726 - Rev 2 page 6/50

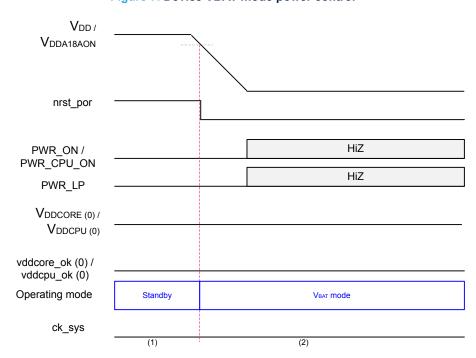

### 3.2 System supplies (V<sub>DD</sub>, V<sub>DDCPU</sub>, and V<sub>DDCORE</sub>)

The STM32MP2 devices require several power supplies. Among these power supplies,  $V_{DD}$ ,  $V_{DDA18AON}$ ,  $V_{DDCPU}$ , and  $V_{DDCORE}$  play a key role in the low-power mode configuration.

- V<sub>DD</sub>, V<sub>DDA18AON</sub>: power supply input for I/Os and system analog such as reset, power management oscillators, and PLLs.

- V<sub>DDCPU</sub>: CPU1 subsystem digital supply

- V<sub>DDCORE</sub>: digital core domain supply.

Note:  $V_{DD}$ , and  $V_{DDA18AON}$  must be present before  $V_{DDCPU}$  and  $V_{DDCORE}$ .

The various power pins of STM32MP2 devices can be supplied by using STPMIC2x. The STPMIC2x usage for this purpose is detailed in the reference design section of the application notes:

- How to use STPMIC25 for a wall adapter powered application on STM32MP25x MPUs (AN5727).

- How to use STPMIC2L for a wall adapter powered application on STM32MP21x lines (AN6303).

### 3.3 Power management description

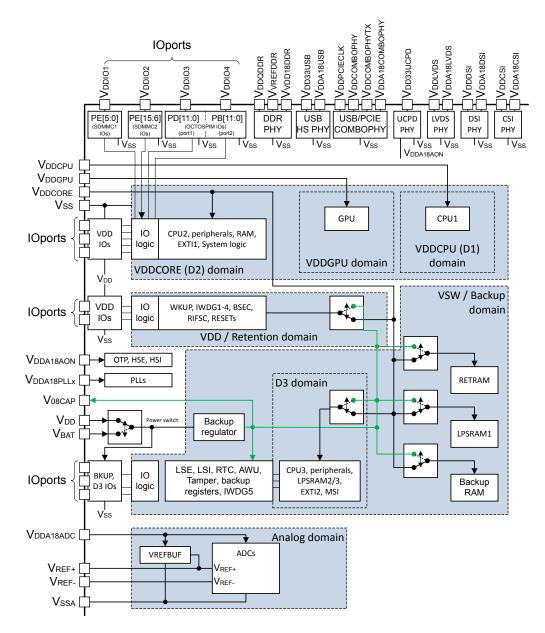

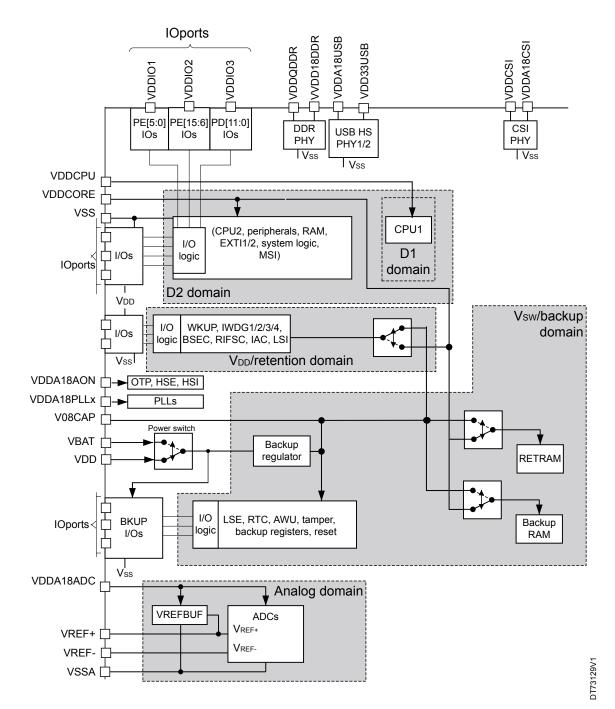

The power management controls  $V_{DDCPU}$  and  $V_{DDCORE}$  supplies in accordance with the system operation modes (see Section 4: Operating modes). The system is split into three domains:

- D1 domain supplied by V<sub>DDCPU</sub>, containing the Cortex<sup>®</sup>-A35 (CPU1).

- D2 system domain, which is the system domain supplied by V<sub>DDCORE</sub>, contains the Cortex<sup>®</sup>-M33 (CPU2), a large part of the peripherals and the system control.

- D3 domain supplied by V<sub>DDCORE</sub> or an internal backup regulator, containing the Cortex<sup>®</sup>-M0+ (CPU3), some peripherals able to work in autonomous mode, and a small part of the system control.

The power supply scheme is given in Figure 2 and Figure 3 the illustration below.

AN5726 - Rev 2 page 7/50

Figure 2. STM32MP23x/STM32MP25x power supply scheme

F68353V3

Figure 3. STM32MP21x power supply scheme

AN5726 - Rev 2 page 9/50

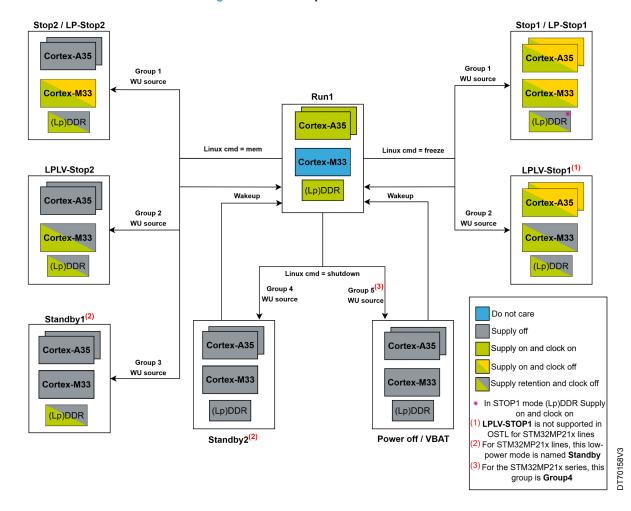

# 4 Operating modes

This section describes the STM32MP2 device power modes and the ways of activating them.

Note: There are no CPU3, D3 domain in the STM32MP21x. Only the single Standby mode is supported. Standby1 and Standby2 are only available on the STM32MP23x and the STM32MP25x.

### 4.1 Operating modes description

The operating modes control the clock distribution to the different parts of the system and the system power. The system operating mode is driven by the CPU1 subsystem and CPU2 subsystem, and by D3 domain in Standby mode. A CPU subsystem can include multiple domains depending on its peripheral allocation.

The table below presents the operating modes for the different systems.

Table 5. Operating modes

| Domain                   | Power mode                | D1 domain      | D3 domain <sup>(6)</sup>                          | Description                                                                                                                                                                  |

|--------------------------|---------------------------|----------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Run1                      | DRun<br>DStop1 | SRun1 <sup>(7)</sup>                              | V <sub>DDCORE</sub> , V <sub>DDCPU</sub> power on, clock on                                                                                                                  |

|                          | Run2                      | DStandby       |                                                   | V <sub>DDCORE</sub> power on, V <sub>DDCPU</sub> power off, clock on                                                                                                         |

|                          | Stop1                     | DStop1         | SRun2 or                                          | V <sub>DDCORE</sub> , V <sub>DDCPU</sub> power on, clock off                                                                                                                 |

|                          | Stop2                     | DStandby       | SStop1 <sup>(7)</sup>                             | V <sub>DDCORE</sub> power on, V <sub>DDCPU</sub> power off, clock off                                                                                                        |

|                          | LP-Stop1(1)(2)            | DStop2         |                                                   | V <sub>DDCORE</sub> , V <sub>DDCPU</sub> power on, clock off                                                                                                                 |

|                          | LP-Stop2(1)(2)            | DStandby       |                                                   | V <sub>DDCORE</sub> power on, V <sub>DDCPU</sub> power off, clock off                                                                                                        |

| D2 system domain         | LPLV-Stop1 <sup>(1)</sup> | DStop3         | SRun3 or<br>SStop2 <sup>(8)</sup>                 | V <sub>DDCORE</sub> reduced power-level, and supply load, clock off                                                                                                          |

|                          | LPLV-Stop2 <sup>(1)</sup> | DStandby       | ·                                                 | $V_{\text{DDCORE}}$ reduced power level, and supply load, $V_{\text{DDCPU}}$ power off, clock off                                                                            |

|                          | Standby1 <sup>(9)</sup>   |                |                                                   | V <sub>DDCORE</sub> , V <sub>DDCPU</sub> power off, clock off                                                                                                                |

|                          | Standby2 <sup>(9)</sup>   | DStandby       | SStandby                                          | V <sub>DDCORE</sub> , V <sub>DDCPU</sub> power off, clock off                                                                                                                |

|                          | VBAT <sup>(3)</sup>       | DStandby       | SRun3 or<br>SStop2 or<br>SStandby <sup>(10)</sup> | VSW is supplied by battery.  All power supplies are off except V <sub>BAT</sub> .  RTC/TAMP is still active clocked by LSE crystal                                           |

|                          | Power off                 | DStandby       | SStandby                                          | All power supplies off                                                                                                                                                       |

|                          | DRun                      | -              | -                                                 | V <sub>DDCPU</sub> power on, CPU1 clock on, CPU1 subsystem is in CRun or CSleep mode                                                                                         |

| D4 domain                | DStop1/<br>DStop2         | -              | -                                                 | V <sub>DDCPU</sub> power on, CPU1 clock off, CPU1 subsystem is in CStop mode                                                                                                 |

| D1 domain                | DStop3                    | -              | -                                                 | V <sub>DDCPU</sub> reduced power-level, CPU1 clock off, CPU1 subsystem is in CStop mode                                                                                      |

|                          | DStandby                  | -              | -                                                 | V <sub>DDCPU</sub> power off, CPU1 clock off, CPU1 subsystem is in CStop mode                                                                                                |

| D3 domain <sup>(6)</sup> | SRun1                     | -              | -                                                 | V <sub>DDCORE</sub> power on, the domain bus matrix is clocked by system clocks, CPU3 subsystem is in CRun or CSleep mode, and the D2 system domain is in Run1 or Run2 mode  |

|                          | SRun2                     | -              | -                                                 | V <sub>DDCORE</sub> power on, the domain bus matrix is clocked by a local clock, CPU3 subsystem is in CRun or CSleep mode and the D2 system domain is in Stop1 or Stop2 mode |

AN5726 - Rev 2 page 10/50

| Domain                                                              | Power mode             | D1 domain | D3 domain <sup>(6)</sup> | Description                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------|------------------------|-----------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                     | SRun3                  | -         | -                        | V <sub>DDCORE</sub> power on/reduced power-level, the domain bus matrix is clocked by a local clock, CPU3 subsystem is in CRun or CSleep mode and the D2 system domain is in LP-Stop1 or LP-Stop2, LPLV-Stop1 or LPLV-Stop2, or Standby mode                                |

| D3 domain <sup>(6)</sup>                                            | SStop1                 | -         | -                        | V <sub>DDCORE</sub> power on, the domain bus matrix may be stalled if clock is not requested by autonomous peripherals, CPU3 subsystem is in CStop mode and the D2 system domain is in Stop1 or Stop2 mode                                                                  |

| Do domain*                                                          | SStop2                 | -         | -                        | V <sub>DDCORE</sub> power on/reduced power-level, the domain bus matrix may be stalled if clock is not requested by autonomous peripherals, CPU3 subsystem is in CStop mode and the system D2 domain is in LP-Stop1 or LP-Stop 2, LPLV-Stop1 or LPLV-Stop2, or Standby mode |

|                                                                     | SStandby               | -         | -                        | V <sub>DDCORE</sub> power off, CPU3 clock off, All CPUs subsystems are in Cstop, the D2 system domain is in Standby, and the PDDS_D3 in PWR_D3CR selects SStandby                                                                                                           |

| 0.5114                                                              | CRun                   | -         | -                        | CPU and CPU subsystem peripherals clock on                                                                                                                                                                                                                                  |

| <ul> <li>CPU1</li> <li>CPU2</li> <li>CPU3<sup>(11)</sup></li> </ul> | CSleep <sup>(4)</sup>  | -         | -                        | CPU clock OFF and CPU subsystem peripheral clock on/off                                                                                                                                                                                                                     |

| 0.00                                                                | CStop                  | -         | -                        | CPU and CPU subsystem peripherals clock off                                                                                                                                                                                                                                 |

| CPU1                                                                | eCSleep <sup>(5)</sup> | -         | -                        | CPU clock OFF and CPU subsystem peripheral clock on/off                                                                                                                                                                                                                     |

- 1. There is no difference in the PWR\_ON, PWR\_CPU\_ON and PWR\_LP output control pins between LP-Stop1/2 and LPLV-Stop1/2 modes (see Section 4.3: External control signals PWR\_ON, PWR\_CPU\_ON, PWR\_LP pins). The user must ensure the STPMIC2x is correctly configured before entering any low power mode.

- The main difference between Stop1 and Stop2, and LP-Stop1 and LP-Stop2 modes is that in LP-Stop1 and LP-Stop2

modes, the PWR\_ON output signal is toggling to 0 when using STPMIC2x external power regulator. This means that when

in LP-Stop1 or LP-Stop2 mode, STPMIC2x actions such as powering off DDR termination resistance power supply are

possible.

- 3. To retain the content of the VSW domain when V<sub>DD</sub> is turned off, the VBAT pin can be connected to an optional standby voltage supplied from a battery or from another source. The VSW domain is composed of:

- RTC/TAMP

- Backup registers

- BKPSRAM

- RFTRAM

- The CPU subsystems allocated peripheral clock operates according to RCC PERxLPEN. When the CPU1 enters CSIeep

with wait for event (WFE), the CPU1 subsystem allocated peripheral clock operates as in CPU1 CRun mode, irrespective

of RCC PERxLPEN

- 5. The CPU1 can go in an enhanced CSleep when the ESLPREQ is set in RCC\_C1SREQSETR register. When this bit is set and STPREQ\_Px (x = 0, 1) bits combination is 0, PLL1 is powered down and bypassed.

- 6. The following conditions apply:

- D3 domain SRunx modes is not applicable for the STM32MP23x.

- D3 domain is not applicable for STM32MP21x.

- 7. SStop1 for STM32MP23x

- 8. SStop2 for STM32MP23x

- 9. Refer to Section 4: Operating modes.

- 10. SStop2 or SStandby for STM32MP23x

- 11. CPU3 not applicable for STM32MP23x and STM32MP21x

Important:

The condition where  $V_{DDCORE}$  is OFF while  $V_{DDCPU}$  is ON is forbidden and not supported.

The choice of which low-power mode to use depends on the power saving target and it must be chosen according to which wakeup interrupts are needed and available in the chosen low-power mode and the expected wakeup time duration.

AN5726 - Rev 2 page 11/50

The user must always make sure that the chosen low-power mode is consistent with the available wakeup sources. For instance, Standby1 and Standby2 modes have very limited wakeup source capabilities.

Also, the wakeup duration is longer if power supply voltages have been reduced or switched off by reducing  $V_{DDCORE}$ , switching off DDR resistance termination supply with DDR in self-refresh or completely switching off the DDR. This last action may require reloading the firmware from the flash memory. The system low-power mode wakeup capabilities are presented in the table below.

Table 6. Low-power mode wake-up capabilities of the system on STM32MP23x and STM32MP25x lines

| System power mode                 | Wake-up sources                                                                                                                                                                                                     |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stop1/Stop2 LP-<br>Stop1/LP-Stop2 | Group1 : Group2 + HPDMAx (x = 1, 2, 3), HSI frequency monitoring, USB (USBH & USB3DRD), UCPD1, ETHx (x = 1,2), USARTx (x = 1 to 9), I2Cx (x = 1 to 7), I3Cx (x = 1 to 3), SPIx (x = 1 to 7), DTS, LPTIMx (x = 1, 2) |

| LPLV-Stop1/2                      | Group2 : Group3 + PVD, PVM, GPIOs                                                                                                                                                                                   |

| Standby1 <sup>(1)</sup>           | Group3 : Group4 + CPU3, DBG, LPDMA, LPUART1 <sup>(2)</sup> , I2C8 <sup>(2)</sup> , I3C4 <sup>(2)</sup> , SPI8 <sup>(2)</sup> , ADF1 <sup>(2)</sup> , LPTIMy (y = 3, 4, 5), WWDG2, MBOX2, IPCC2, HSEM, GPIOZ         |

| Standby2 <sup>(1)</sup>           | Group4 : Group5 + 6 x WKUP pins                                                                                                                                                                                     |

| VBAT                              | Group5 : BOR, VBATH/VBATL, TEMPH/TEMPL, LSE CSS, RTC/auto wake-up, tamper pins, IWDGx                                                                                                                               |

- 1. Refer to Section 4: Operating modes.

- 2. The wake-up associated to autonomous mode is not managed in OpenSTLinux.

Table 7. Low-power mode wake-up capabilities of the system on STM32MP21x lines

| System power mode                 | Wake-up sources                                                                                                                                                                                                              |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stop1/Stop2 LP-<br>Stop1/LP-Stop2 | Group1: Group2 + DBG + HPDMAx (x = 1, 2, 3), HSI/MSI frequency monitoring, USB (USBH & OTG), ETHx (x = 1,2), USARTx (x = 1 to 7), LPUART1, I2Cx (x = 1 to 3), I3Cx (x = 1 to 3), SPIx (x = 1 to 6), DTS, LPTIMx (x = 1 to 5) |

| LPLV-Stop1/2                      | Group2 : Group3 + PVD, PVM, GPIOs                                                                                                                                                                                            |

| Standby                           | Group3 : Group4 + BOR, IWDGx, 6 x WKUP pins                                                                                                                                                                                  |

| VBAT                              | Group4: VBATH/VBATL, TEMPH/TEMPL, LSE CSS, RTC/auto wake-up, tamper pins                                                                                                                                                     |

AN5726 - Rev 2 page 12/50

### 4.2 Low-power mode control

### 4.2.1 Low-power mode control registers

The control register bits presented below are related to the low-power modes. For more information on low-power modes see Section 4.1: Operating modes description.

The low-power modes control register bits are presented in the table below.

Table 8. Low-power modes control register bits

| Register bit setting                   | Bit value                                                                                                                             | Description                                                                |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| PDDS_D1 bit of the                     | 0: DStop mode kept when CPU1 enters CStop                                                                                             | This bit allows CPU1 to define the                                         |

| PWR_CPU1CR register <sup>(1)</sup>     | 1: DStandby mode allowed when CPU1 enters CStop                                                                                       | Deepsleep mode for the D1 domain.                                          |

| PDDS_D2 bit of the                     | 0: Stop mode kept when CPU2 enters CStop                                                                                              | This bit allows CPU1 to define the Deepsleep mode for the D2 domain/       |

| PWR_CPU1CR register <sup>(1)</sup>     | 1: Standby mode allowed when CPU2 enters CStop                                                                                        | system.                                                                    |

| PDDS_D2 bit of the                     | 0: Stop mode kept when CPU2 enters CStop                                                                                              | This bit allows CPU2 to define the Deepsleep mode for the D2 domain/       |

| PWR_CPU2CR register (2)                | 1: Standby mode allowed when CPU2 enters Cstop                                                                                        | system.                                                                    |

| PDDS_D3 bit of the PWR_D3CR            | 0: SStop mode kept when system enters CStop                                                                                           | This bit allows CPU3 to define the                                         |

| register (3)                           | 1: SStandby mode allowed when system enters CStop                                                                                     | Deepsleep mode for the D3 domain.                                          |

| STPREQ_P0 bit of the                   | 0: Writing 0 has no effect. Reading 0 means that the CPU1 processor core 0 does not allow the CPU1 subsystem to go to CStop           | RCC CPU1 stop request set register                                         |

| RCC_C1SREQSETR register <sup>(4)</sup> | 1: Writing 1 sets the STPREQ_P0 bit.<br>Reading 1 means that the CPU1 processor<br>core 0 allows the CPU1 subsystem to go to<br>CStop | defines whether the CPU1 subsystem is allowed to enter CStop.              |

| STPREQ_P1 bit of the                   | 0: Writing 0 has no effect. Reading 0 means that the CPU1 processor core 1 does not allow the CPU1 subsystem to go to CStop           | RCC CPU1 stop request set register defines whether the CPU1 subsystem is   |

| RCC_C1SREQSETR register <sup>(4)</sup> | 1: Writing 1 sets the STPREQ_P0 bit.<br>Reading 1 means that the CPU1 processor<br>core 1 allows the CPU1 subsystem to go to<br>Cstop | allowed to enter CStop.                                                    |

| ESLPREQ bit of the                     | 0: Writing 0 has no effect. Reading 0 means that enhanced CSleep for CPU1 subsystem is not requested                                  | RCC CPU1 stop request set register defines whether the enhanced CSleep has |

| RCC_C1SREQSETR <sup>(4)</sup>          | 1: Writing 1 sets the ESLPREQ bit.<br>Reading 1 means that enhanced CSleep<br>for CPU1 subsystem is requested                         | been requested for CPU1.                                                   |

- 1. PWR CPU1 control register

- 2. PWR CPU2 control register

- 3. PWR D3 control register not applicable to STM32MP21x

- 4. RCC CPU1 stop request set register

The table below summarizes the relationship between the system and the CPUx (where x = 1, 2, or 3) low-power modes

AN5726 - Rev 2 page 13/50

| System                        | CPU1                                                            | CPU2                                                                            | CPU3 <sup>(1)</sup> | System clock | D3<br>oscillator | V <sub>DDCPU</sub> | V <sub>DDCORE</sub> |    |  |

|-------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------|--------------|------------------|--------------------|---------------------|----|--|

| Run1                          | CRun or Csleep or eCSleep ESLPREQ = 1 <sup>(2)</sup>            | CRun, CSleep, or<br>Cstop                                                       |                     | ON           | ON               | ON                 |                     |    |  |

|                               | Cstop                                                           | CRun or Csleep                                                                  |                     |              |                  |                    | ON                  |    |  |

| Run2                          | CStop and PDDS_D1=1                                             | CRun or Csleep                                                                  |                     |              |                  | OFF                |                     |    |  |

| Stop1                         | Cstop                                                           |                                                                                 |                     |              |                  | ON                 | (nominal)           |    |  |

| Stop2                         | CStop and PDDS_D1 = 1                                           | Cstop  CRun, CSleep Cstop  CStop and LPDS_D2 = 1(5)  CStop and LPDS_D2=1(4) and | CRun, CSleep, or    |              |                  | OFF                |                     |    |  |

| LP-Stop1 <sup>(3)</sup>       | CStop and LPDS_D1=1 <sup>(4)</sup>                              |                                                                                 | CStop and           | ·            | Ostop            |                    |                     | ON |  |

| LP-Stop2                      | CStop and PDDS_D1=1                                             |                                                                                 |                     | OFF          | ON/OFF           | OFF                |                     |    |  |

| LPLV-<br>Stop1 <sup>(3)</sup> | CStop and LPDS_D1=1 <sup>(4)</sup> and LVDS_D1=1 <sup>(6)</sup> |                                                                                 |                     |              |                  | ON                 | ON<br>(reduced)     |    |  |

| LPLV-Stop2                    | LVDS_D2=1(/)                                                    | LVDS_D2=1 <sup>(7)</sup>                                                        |                     |              |                  |                    |                     |    |  |

| Standby1 <sup>(8)</sup>       | CStop and                                                       | CCton and                                                                       |                     |              |                  | OFF                |                     |    |  |

| Standby2 <sup>(8)</sup>       | PDDS_D1=1                                                       | =1 CStop and PDDS_D2=1                                                          | CStop and PDDS_D3=1 |              | OFF              |                    | OFF                 |    |  |

Table 9. System low-power modes summary

- 1. No CPU3 on STM32MP23x and STM32MP21x

- 2. ESLPREQ in RCC\_C1SREQSETR selects enhanced CSleep for CPU1.

- 3. At least one PDDS\_Dn (n = 1, 2) in PWR\_CPU1CR and PWR\_CPU2CR selects Stop.

- 4. LPDS\_D1 in PWR\_CPU1CR selects LP-Stop.

- 5. LPDS\_D2 in PWR\_CPU2CR selects LP-Stop.

- 6. LVDS\_D1 in PWR\_CPU1CR selects LPLV-Stop.

- 7. LVDS D2 in PWR CPU2CR selects LPLV-Stop.

- 8. Refer to Section 4: Operating modes.

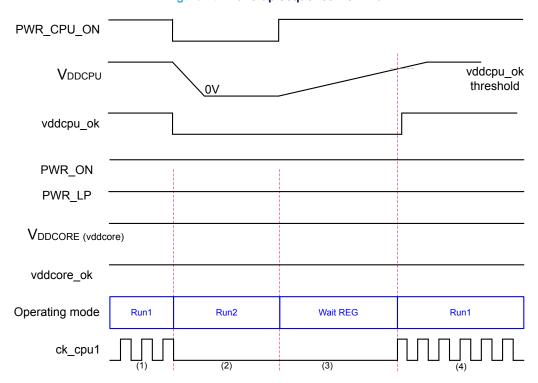

## 4.3 External control signals PWR\_ON, PWR\_CPU\_ON, PWR\_LP pins

The three output pins PWR\_ON, PWR\_CPU\_ON, and PWR\_LP are related to the  $V_{DDCORE}$  and  $V_{DDCPU}$  supplies. They are used by external components or regulators to identify which voltage level must be applied on  $V_{DDCORE}$  and  $V_{DDCPU}$ .

- PWR\_ON: V<sub>DDCORE</sub> supply request (active high):

It is automatically generated by the hardware depending on the state of the STM32MP2 device and on the value of LPCFG\_D2 (PWR\_ON pin configuration) bit of the PWR D2 control register (PWR\_D2CR).

- PWR\_CPU\_ON: V<sub>DDCPU</sub> supply request (active high):

It is automatically generated by the hardware depending on the state of the STM32MP2xx device and on the value of LPCFG\_D1 (PWR\_ CPU\_ON pin configuration) bit of the PWR D1 control register (PWR\_D1CR).

- PWR\_LP: V<sub>DDCORE</sub> low-power mode control (active low):

It is automatically generated by the hardware depending on the state of the STM32MP2 device and the value of LPDS\_D1, LPDS\_D2, LVDS\_D1 and LVDS\_D2 bits of the PWR CPU1 and CPU2 control register (PWR CPU1CR) and (PWR CPU2CR). This pin is not used with STPMIC2x.

AN5726 - Rev 2 page 14/50

Table 10. Register bit settings

| Register bit setting | Bit value                                                                                                                                                                                                        | Description                                                                           |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| LDDC D4              | 0: Stop mode selected, external regulator kept in main power mode.                                                                                                                                               | This is bit 16 of the PWR CPU1 control register (PWR_CPU1CR).                         |

| LPDS_D1              | 1: LP/LPLV-Stop mode selected, the external regulator may enter low-power mode.                                                                                                                                  | It controls Low-Power Deep Sleep Stop mode selection for the D1 domain. (1)           |

|                      | 0: Stop mode selected, external regulator kept in main power mode (PWR_LP = 1).                                                                                                                                  | This is bit 16 of the PWR CPU2 control register (PWR CPU2CR).                         |

| LPDS_D2              | 1: LP/LPLV-Stop mode selected, the external regulator may enter low-power mode (PWR_LP = 0).                                                                                                                     | It controls Low-Power Deep Sleep Stop mode selection for the D2 domain/system. (2)    |

|                      | 0: LP-Stop mode V <sub>DDCPU</sub> domain supply reset level at same level as Run mode.                                                                                                                          | This is bit 17 of the PWR CPU1 control register (PWR_CPU1CR).                         |

| LVDS_D1              | V <sub>DDCPU</sub> domain supply level in LP-Stop mode must be kept at same level as Run mode.                                                                                                                   | It controls Low-Voltage Deep Sleep LPLV-Stop mode selection for the D1 domain.        |

|                      | 1: LPLV-Stop mode V <sub>DDCPU</sub> domain supply reset level at lower level than Run mode.                                                                                                                     | VDDCPU supply can be lowered in LPLV-Stop mode (see datasheet for voltage levels).    |

|                      | 0: LP-Stop mode V <sub>DDCORE</sub> domain supply reset level at same level as Run mode.                                                                                                                         | This is bit 17 of the CPU2 control register (PWR_CPU2CR).                             |

| LVDS_D2              | V <sub>DDCORE</sub> domain supply level in LP-Stop mode must be kept at same level as Run mode.                                                                                                                  | It controls Low-Voltage Deep Sleep LPLV-Stop mode selection for the D2 domain/system. |

|                      | 1: LPLV-Stop mode V <sub>DDCORE</sub> domain supply reset level at lower level than Run mode.                                                                                                                    | VDDCORE supply can be lowered in LPLV-Stop mode (see datasheet for voltage levels).   |

|                      | 0: PWR_CPU_ON pin signals DStandby mode (PWR_CPU_ON = 1 in DRun, DStop1, DStop2, DStop3, and = 0 in DStandby).                                                                                                   | This is bit 0 of the PWR D1 control register (PWR D1CR)                               |

| LPCFG_D1             | 1: PWR_CPU_ON pin signals DStandby and DStop2, DStop3 modes (PWR_CPU_ON = 1 in DRun, DStop1, and = 0 in DStop2, DStop3, and DStandby).                                                                           | It controls the PWR_ON pin configuration                                              |

|                      | 0: PWR_ON pin signals Standby (PWR_ON = 1 in Run, Stop1, Stop2, LP-Stop1, LP-Stop2, LPLV-Stop1, LPLV-Stop2, and = 0 in Standby1 $^{(3)}$ , and Standby2 $^{(3)}$ ).                                              | This is bit 0 of the PWR D2 control register (PWR_D2CR)                               |

| LPCFG_D2             | 1: PWR_ON pin signals Standby, LP-Stop, and LPLV-Stop modes (PWR_ON = 1 in Run, Stop1, Stop2, and = 0 in LP-Stop1, LP-Stop2, LPLV-Stop1, LPLV-Stop2 and Standby1 <sup>(3)</sup> , and Standby2 <sup>(3)</sup> ). | It controls the PWR_ON pin configuration                                              |

- 1. Further low-power mode selection is provided by LVDS\_D1.

- 2. Further low-power mode selection is provided by LVDS\_D2.

- 3. Refer to Section 4: Operating modes.

#### The table below indicates:

- The PWR\_ON, PWR\_CPU\_ON, and PWR\_LP output pin values. These values depend on the various power mode configurations and LPDS\_Dn, LPCFG\_Dn, and LVDS\_Dn bits (n= 1, 2).

- Shows the different way of using pins:

- PWR\_CPU\_ON

- PWR\_ON

- PWR LP

This is determined by how the STM32MP2 device is used with STPMIC2x. The power modes are detailed in the PWR section of the appropriate reference manual.

AN5726 - Rev 2 page 15/50

Table 11. PWR\_LP, PWR\_ON, PWR\_CPU\_ON levels according to power modes, LPDS, LVDS, and LPCFG bits

|                                                     | LPDS_D1/ LPDS_D2/ PWR_ON |                 | R_ON   | PWR_C          | PU_ON                         |                               |                |

|-----------------------------------------------------|--------------------------|-----------------|--------|----------------|-------------------------------|-------------------------------|----------------|

| System                                              | LVDS_D1<br>bits          | LVDS_D2<br>bits | PWR_LP | LPCFG_D2<br>=0 | LPCFG_D2 <sup>(1)</sup><br>=1 | LPCFG_D1 <sup>(2)</sup><br>=0 | LPCFG_D1<br>=1 |

| Startup                                             |                          |                 |        |                |                               |                               |                |

| (until V <sub>DD</sub> reaches POR threshold level) | X/X                      | X/X             | 0      | 0              | 0                             | 0                             | 0              |

| Dund                                                | X/X                      | 0/X             |        |                |                               | 4                             | 4              |

| Run1                                                | 0/X                      | X/X             |        |                | 1                             | 1                             | 1              |

| Run2                                                | 0/X                      | X/X             | 1      |                |                               | 0                             | 0              |

| Stop1                                               | 0/X                      | 0/X             |        |                |                               | 1                             | 1              |

| Stop2                                               | 0/X                      | 0/X             |        | 1              |                               | 0                             | 0              |

| LP-Stop1                                            | 1/0                      | 1/0             |        |                |                               | 1                             |                |

| LP-Stop2                                            | 1/0                      | 1/0             |        |                |                               | 0                             |                |

| LPLV-Stop1                                          | 1/1                      | 1/1             | 0(3)   |                | - (0)                         | 1                             |                |

| LPLV-Stop2                                          | 1/1                      | 1/1             | 0(3)   |                | 0(3)                          |                               |                |

| Standby1 <sup>(4)</sup>                             | X/X                      | X/X             |        |                |                               | 0                             |                |

| Standby2 <sup>(4)</sup>                             | X/X                      | X/X             |        | 0              |                               |                               |                |

| V <sub>BAT</sub> (V <sub>DD</sub> powered down)     | X/X                      | X/X             | High-Z | High-Z         | High-Z                        | High-Z                        | High-Z         |

- 1. Configuration used with STPMIC25x PWRCTRL1 pin connected to PWR\_ON.

- 2. Configuration used with STPMIC25x PWRCTRL2 pin connected to PWR\_CPU\_ON.

- There is no difference between LP-Stop1/2, LPLV-Stop1/2, and Standby1/2 mode on the PWR\_ON, PWR\_LP output values '00' with LPCFG\_D2 bit=1.

- 4. Refer to Section 4: Operating modes.

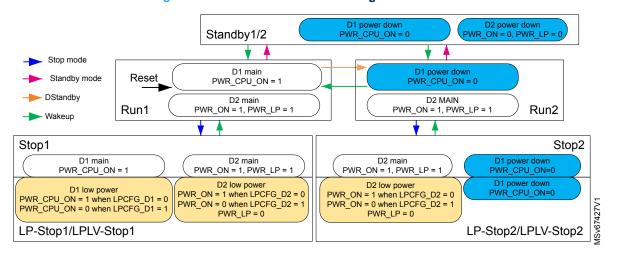

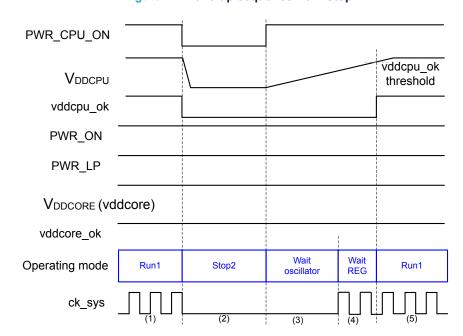

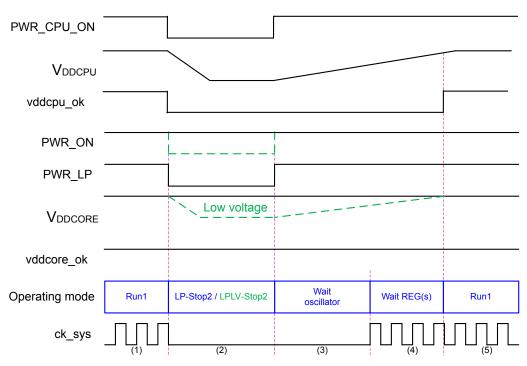

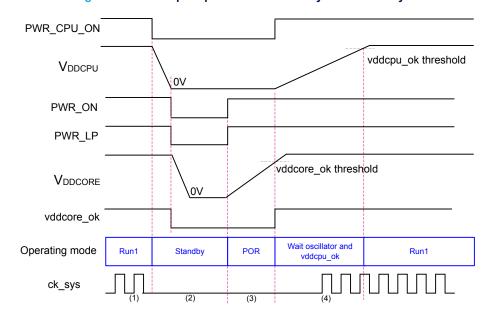

The figure below illustrates the relation between the system states and the PWR\_ON, PWR\_CPU\_ON, PWR\_LP output pins of regulator control for STM32MP2 devices.

Figure 4. Power states and external regulator control

AN5726 - Rev 2 page 16/50

#### 4.3.1 Using the STPMIC2x power regulator

Note:

For references to the Standby modes, refer to Section 4: Operating modes

Refer to Figure 1. STM32MP2 device high-level system architecture for high-level system architecture when using the STPMIC2x power regulator.

The following pins from the STM32MP2 are needed to interface and control the STPMIC2x power modes:

Table 12. STM32MP2 / STPMIC2x connections

| STM32MP2 pins | STPMIC2x pins |

|---------------|---------------|

| PWR_ON        | PWRCTRL1      |

| PWR_CPU_ON    | PWRCTRL2      |

| NRSTC1MS      | PWRCTRL3      |

In that case, the user must set the LPCFG\_D1 bit of the PWR\_D1CR register to 0, and LPCFG\_D2 bit of the PWR\_D2CR to 1.

Table 11 shows that there is no difference between the LP-Stop1 and LP-Stop2, LPLV-Stop1 and LPLV-Stop2, and Standby1 and Standby2 modes on the output values of the control signals PWR\_ON and PWR\_LP which are 0 if the bit LPCFG\_D2 is set to 1.

The STPMIC2x differentiates between the LP-Stop1 and LP-Stop2, LPLV-Stop1 and LPLV-Stop2, and Standby1/2 low-power modes and applies the correct  $V_{DDCORE}$  and  $V_{DDCPU}$  value thanks to the STPMIC2x internal registers. The programming of these registers is done via the I2C interface and not through the PWR\_ON, PWR\_CPU\_ON, nor PWR\_LP pins values.

When using the STM32MPU OpenSTLinux distribution, the secure monitor TF-A or OP-TEE handles this programming. Before entering into LP-Stop1 and LP-Stop2, LPLV-Stop1 and LPLV-Stop2, or Standby1/2 mode, the application must configure the STPMIC2x internal registers to the correct system power-supplies level. These are  $V_{DDCORE}$ ,  $V_{DDCPU}$ ,  $V_{DD}$ ,  $V_{DDQ\_DDR}$ , and others. When entering LP-Stop1, and LP-Stop2 mode, it is still possible to program the STPMIC2x even though the  $V_{DDCORE}$  level is not decreased. This applies only in LPLV-Stop1, and LPLV-Stop2. This results in other power supplies being shut down if not needed. This is, for example, the case for the power supply of the DDR termination resistances.

AN5726 - Rev 2 page 17/50

- Control signals between STPMIC2x and STM32MP25x (see Table 2 for more details of the devices).

This paragraph describes how the STM32MP25x microprocessor communicates with the STPMIC2x device. There are several interface choices that can be used depending on the application requirements.

Some interfaces are described below. Refer to AN5727 for more information.

- I<sup>2</sup>C Interface:

The STPMIC2x can be controlled by the STM32MP2 via the I<sup>2</sup>C interface. This interface controls advanced low power features such as:

- Enable or disable a regulator

- Set a regulator voltage and mode (low-power mode)

- Switch between nominal mode and overdrive mode.

- ON / INT push button:

STPMIC2x PONKEY\_N digital input pin (active low) is connected to the user "ON / INT" push button on the application. This button has three actions:

- Powers up the STPMIC2x

- Sends an interrupt to the STM32MP2

- Forces a Turn on/off condition (see section Application turn-on / turn-off conditions on AN5727 for more information).

- NRST signal

The STM32MP2 NRST pin is linked to the STPMIC2x RSTn digital input active low pin. It can also be connected to a "RESET" push button. The RSTn signal is a bidirectional reset pin for the STPMIC2x:

- When the STPMIC2x asserts an RSTn, such as during the power-up or the power-down sequence, it drives the NRST signal low: the STM32MP2 is forced into a reset status until the STPMIC2x releases the RSTn.

- When the STM32MP2 asserts an NRST signal, such as a watchdog event, low voltage on V<sub>DD</sub> and so on, or on a press of the "RESET" button, the STPMIC2x immediately asserts a reset with the RSTn pin and performs a non-interruptible power cycle: the STPMIC2x performs a power down sequence followed by a power up sequence and finally releases the RSTn.

- At the end of the power-cycle sequence, the STPMIC2x waits for the STM32MP2 NRST signal to go high before rearming the reset to avoid an infinite reset loop.

- PWRCTRL1. PWRCTRL2. PWRCTRL3

Power controls are STPMIC2x digital input signal controlled from the STM32MP2, all STPMIC2x power control pins are connected to a power control pin of the STM32MP2 as described below:

- The PWR\_ON signal is driven by the STM32MP2 PWR\_ON pin to control the PWRCTRL1 pin of STPMIC2x. The PWR\_ON signal is also used to control the V<sub>DDCORE</sub> power supply for the STM32MP2 D2 domain. When the PWR\_ON signal is low, it enables the STPMIC2x to switch to a low-power mode, such as LP-Stop1, LP-Stop2, LPLV-Stop1, LPLV-Stop2, or Standby. This reduces the power consumption of the system by turning off or reducing the power to non-essential components.

- The PWR\_CPU\_ON signal is driven by the STM32MP2 PWR\_CPU\_ON pin to control the PWRCTRL2 pin of STPMIC2x. The PWR\_CPU\_ON signal is also used to control the  $V_{DDCPU}$  power supply for the STM32MP2 D1 domain. When the PWR\_CPU\_ON signal is low, it enables the STPMIC2x to switch to a low-power mode, such as LP-Stop1, LP-Stop2, LPLV-Stop1, LPLV-Stop2, or Standby. This reduces the power consumption of the system by turning off or reducing the power to non-essential components.

- The NRSTC1MS signal is driven by the STM32MP2 NRSTC1MS pin to control PWRCTRL3 pin of the STPMIC2x. The NRSTC1MS pin is active when a system reset is generated. The NRSTC1MS pin can be used to control supplies of external flash required for first level boot of CPU1 and which needs a power cycle to ensure a platform reboot (eMMC, SD-Card).

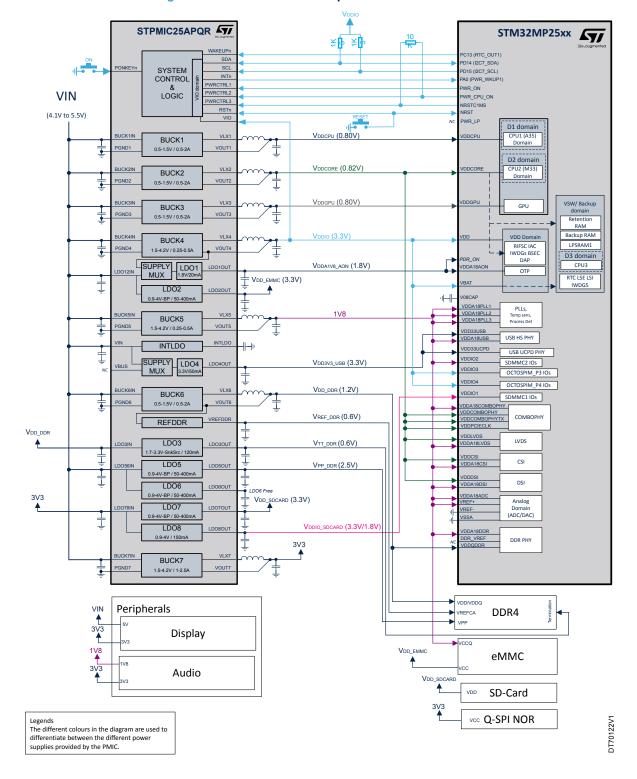

### 4.3.2 STPMIC2x supplies example 3.3 V I/Os with DDR4

The following reference design examples target a complex 3.3 V I/Os platform with DDR4 and high integration with the STPMIC25APQR and STPMIC2LAPQR. The design examples are illustrated in Figure 5 and Figure 6. Usually, all platform components can be powered by the STPMIC2x. Full power supply control is supported with the STPMIC25APQR I²C and side band signals. The STPMIC2L devices require additional external LDO or SMPS to supply the full application. All low power modes are supported. See the STPMIC25 and STPMIC2L documentation for details of STPMIC25APQR and STPMIC2LAPQR components.

AN5726 - Rev 2 page 18/50

Figure 5. STPMIC25APQR example 3.3 V I/Os with DDR4

AN5726 - Rev 2 page 19/50

STPMIC2Lx STM32MP2xx VBAT **X** LDO5OU™ LDO25IN VDD DD\_FLASH (3.3 LPF VDDA1V8 (1.8V) VDDA18ADC LDO2OUT vss PDR\_ON(1) VREF+ VDDA1V8 AON (1.8V) ADC VDDA18AON VREF-雪雪 XT\_EN1 GPIO[5:1 SDA **VDDCSI** VDDCORE (0.82V) Pxx (I2C7 SDA) VDD (3.3V) -VSS SCL Pxx (I2C7\_SCL) only use if VBAT is supplied separately than VDD PC13 (RTC\_OUT1) VDDA18CSI VDDA1V8 (1 8V) up during VBAT mode is required ONKEYn INTr PA0 (PWR WKUP1) PWRCTRL1 PWR\_ON PWRCTRI 2 PWR CPU ON PWRCTRL3 NRSTC1MS NC PWR\_LP ire (see text) RST I NRST VIC RESET VDDCORE (0.82V) BUCK1IN VLX VDDCORE (0.82 V) PGND1 VOUT VSS VDDCPU (0.8V / 0.9V) VLX • PGND3 VOUT vss VSS VDDA1V8 (1.8V) DO67 LDO6OU VDDA18PLLx VDDIO3 LDO7OU1 VSS VSS VDD3V3\_USB (3.3V) VDDIO2 VDDA1V8 LDO4OU VDD33USB VSS vss VIN VDDIO1 /DDIO 3V3 VDDA18USB SDMMC1 (4.5 - 5.5V) LDO10UT VSS Additional VIN AGND VDDA18DDR **₩** vss DDR VDD DDR (1.2V) BUCK2IN VLX2 ·II-1240 GND2 VOUT V<sub>DD</sub> / V<sub>DDQ</sub> (2 x) VREECA ╫ VDD\_DDR (1.2V) LDO3IN Vss / Vssq DDR4 memory ZQ GNDLDO VPP DDR (2.5) LD030UT VTT\_DDR (0.6V) Vpp (ZQ) VREF (0.6 V) Note: Alternatively, to ease routing and avoid long VREF lines,  $V_{REF}$  could be generated locally by a  $1K\Omega/1K\Omega$  1% resistor divider on  $V_{DDQ}$  close to each  $V_{REF}$  pins VDD3V3 (3.3V) PMIC sunnlies example 3.3V I/Os with DDR4

Figure 6. STPMIC2LAPQR example 3.3 V I/Os with DDR4

3.3V supply -- D

Low power modes are managed by the STM32MP2. The external STM32MP2 control signals controls the STPMIC2x PWRCTRLx signals assigned to manage the STPMIC2x regulators behavior. Depending on PWRCTRLx status, the STM32MP2 enters into one low power mode or another (see Table 11).

Before entering in any low-power mode, the STM32MP2 must set the STPMIC2x PWRCTRL xxxx\_ALT\_CR register in line with the expected STPMIC2x regulator settings for low-power mode behavior. If needed, the STM32MP2 must set the STPMIC2x PWRCTRL xxxx\_MAIN\_CR control registers to guarantee that the application leaves the low-power mode.

The following table shows how the STPMIC2x can be programmed in Run1 mode and before entering any LP-Stop, any LPLV-Stop, and any Standby modes respectively. The table below lists all the power supplies and not only those relates to the  $V_{DDCORE}$ . The settings used on them are in line with the example presented in Figure 5 and Figure 6.

AN5726 - Rev 2 page 20/50

Table 13. STPMIC25 and STPMIC2L configuration depending on operating modes

|                          | . STPMIC25 STPMIC2L |                                                    |                        | Configuration                       |                                                    |                                        |                                                    |                                      |  |  |

|--------------------------|---------------------|----------------------------------------------------|------------------------|-------------------------------------|----------------------------------------------------|----------------------------------------|----------------------------------------------------|--------------------------------------|--|--|

| Supply name              | regulators          | regulators                                         | PWRCTRLx<br>assignment | RUN1/STOP1                          | RUN2/STOP2                                         | LP-STOP1/<br>LPLV-STOP1                | LP-STOP2/<br>LPLV-STOP2                            | STANDBY1/<br>STANDBY2 <sup>(1)</sup> |  |  |

| V <sub>DDCPU</sub>       | BUCK1               | BUCK3                                              | PWR_CPU_ON             | ON HP <sup>(2)</sup> (xxxx_MAIN_CR) | OFF<br>(xxxx_ALT_CR)                               | ON HP <sup>(2)</sup> (xxxx_MAIN_CR)    | OFF<br>(xxxx_ALT_CR)                               | OFF<br>(xxxx_ALT_CR)                 |  |  |

| V <sub>DDCORE</sub>      | BUCK2               | BUCK1                                              | PWR_ON                 | ON HP <sup>(2)</sup> (xxxx_MAIN_CR) | ON HP <sup>(2)</sup> (xxxx_MAIN_CR)                | ON HP <sup>(2)</sup> (xxxx_ALT_CR) (3) | ON HP <sup>(2)</sup> (xxxx_ALT_CR ) <sup>(3)</sup> | OFF<br>(xxxx_ALT_CR)                 |  |  |

| V <sub>DDA18</sub>       | BUCK5               | LDO6                                               |                        |                                     |                                                    |                                        |                                                    |                                      |  |  |

| V <sub>DD_DDR</sub>      | BUCK6               | BUCK2                                              |                        |                                     |                                                    | ,                                      | ON HP <sup>(2)</sup> (xxxx_ALT_CR)                 | 055                                  |  |  |

| V <sub>REF_DDR</sub>     | VREFDDR             | Resistor<br>bridge on<br>BUCK2                     | PWR_ON                 | (xxxx_MAIN_CR)                      | ON (HP <sup>(2)</sup> for BUCKs)<br>(xxxx_MAIN_CR) |                                        |                                                    | OFF<br>(xxxx_ALT_CR)                 |  |  |

| V <sub>PP_DDR</sub>      | LDO5                | LDO7                                               |                        |                                     |                                                    |                                        |                                                    |                                      |  |  |

| V <sub>DD_EMMC</sub>     | LDO2                | LDO6 (1V8)                                         |                        |                                     |                                                    |                                        |                                                    |                                      |  |  |

| VDD_EMMC                 | LDO2                | LDO2 (3V3)                                         |                        |                                     |                                                    |                                        |                                                    |                                      |  |  |

| V <sub>DD_SDCARD</sub>   | LDO7                | LDO5 (3V3)                                         | NRSTC1MS               | ON                                  | ON                                                 | ON                                     | OFF (RESET)                                        | OFF (RESET)                          |  |  |

| V <sub>DDIO_SDCARD</sub> | LDO8                | LDO5 (3V3) or<br>external<br>BUCK/LDO for<br>UHS-I |                        | (xxxx_MAIN_CR)                      |                                                    |                                        | , , ,                                              | or (NEOLI)                           |  |  |

| V <sub>TT_DDR</sub>      | LDO3                | LDO3                                               | PWR_ON                 | ON<br>(xxxx_MAIN_CR)                | ON<br>(xxxx_MAIN_CR)                               | OFF<br>(xxxx_ALT_CR)                   | OFF<br>(xxxx_ALT_CR)                               | OFF<br>(xxxx_ALT_CR)                 |  |  |

| V <sub>DD3V3_USB</sub>   | LDO4                | LDO4                                               | -                      | ON or OFF (xxxx_MAIN_CR)            | OFF<br>(xxxx_MAIN_CR)                              | ON or OFF<br>(xxxx_MAIN_CR)            | OFF<br>(xxxx_MAIN_CR)                              | OFF<br>(xxxx_MAIN_CR)                |  |  |

<sup>1.</sup> Refer to Section 4: Operating modes

BUCK4 on STPMIC25x and LDO2 on STPMIC2Lx ( $V_{DDIO}$ ) and LDO1 ( $V_{DDA1V8\_AON}$ ) are always ON. Application note AN5727 and AN6303 provides more details on how to use STPMIC25 and STPMIC2L.

<sup>2.</sup> HP stands for high power. Ref to Section 4.6.6: Exit from LP-Stop2 and LPLV-Stop2 mode

<sup>3.</sup> VDDCORE supply lowered to 670 mV (for LPLV-Stop1 or LPLV-Stop2 mode) (xxxx\_ALT\_CR)

### 4.4 Low-power mode entry sequence

The STM32MP2 devices have dedicated power-modes at subsystem level (CPU1, CPU2 and CPU3), at D1 domain level and at system level (see Section 4: Operating modes). This section details how to enter those power modes at subsystem and at system level.

Table 14. Subsystem low-power mode entry sequence definition