# How to use STPMIC25 for a wall adapter powered application on STM32MP25x lines MPUs

#### Introduction

This application note applies to the STM32MP25x MPU devices as detailed in the table below. The devices are referred to as STM32MP25x in the rest of the document. It is powered by the STPMIC25 power management IC companion chip, which is fully featured to supply complete applications.

This document provides an example of a hardware reference design based on a STM32MP25x device. The STM32MP25x is powered by an external 5 V power supply via the STPMIC25APQR power management IC. The STPMIC25APQR peripheral I/O voltage runs at 3.3 V.

This document is intended for product architects and designers who require information about the power management and STPMIC25 settings. This document focuses on:

- · Reference design block diagram

- Power distribution topology

- · Power on/off and low power management

- · User reset and crash recovery management

- · Safety management and PMIC tuning.

#### Table 1. Applicable products

| Reference  | Applicable products                             |

|------------|-------------------------------------------------|

| STM32MP25x | STM32MPD251, STM32MP253, STM32MP255, STM32MP257 |

## 1 General information

This document applies to STM32MP25x  $Arm^{\$}$ -based MPUs and STPMIC25x power management IC Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

AN5727 - Rev 1 page 2/65

### 2 Overview

This application note describes the interaction between the STM32MP25x and the STPMIC25APQR including the management of the following peripherals:

- DC input power source from main power supply: 5 V typical (4.1 V to 5.5 V).

- DDR4 memory.

- Peripheral I/O interface voltage (V<sub>DD</sub>) at 3.3 V powered by the STPMIC25.

- USB 3.0 superspeed port supporting power delivery to supply a USB device.

- eMMC flash memory (HS200) as boot device.

- SD card (UHS-I) which is not used as a boot device in this reference design.

Not covered in this application note:

- DDR3L and lpDDR4

- Peripheral interface with I/O voltage (V<sub>DD</sub>) of 1.8 V

The battery-powered application using the STPMIC25 is addressed in [4].

In this document, MPU terminology refers to the STM32MP25x.

#### 2.1 Reference documents

Table 2. Reference documents

| -   | Reference                                  | Title                                                                   |  |  |  |  |  |  |

|-----|--------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|

| STM | STMicroelectronics document <sup>(1)</sup> |                                                                         |  |  |  |  |  |  |

| [1] | AN5489                                     | Getting started with STM32MP25x MPUs hardware development               |  |  |  |  |  |  |

| [2] | DS14278                                    | Highly integrated power management IC for microprocessor unit           |  |  |  |  |  |  |

| [3] | RM0457                                     | STM32MP25x advanced Arm®-based 32/64-bit MPUs                           |  |  |  |  |  |  |

| [4] | AN5728                                     | How to use STPMIC2x for a battery powered application on STM32MP25 MPUs |  |  |  |  |  |  |

| [5] | AN5726                                     | Guidline for using low power modes on STM32MP2 MPUs                     |  |  |  |  |  |  |

<sup>1.</sup> Refer to www.st.com

AN5727 - Rev 1 page 3/65

## 3 Glossary

Table 3. Glossary

| Term | Meaning                             |

|------|-------------------------------------|

| BUCK | Step down regulator                 |

| GPU  | Graphics processing unit            |

| LDO  | Low drop out linear regulator       |

| MPU  | Microprocessor unit                 |

| NPU  | Neural processing unit              |

| NVM  | Nonvolatile memory                  |

| PMIC | Power management integrated circuit |

| SMPS | Switching mode power supply         |

| SW   | Software                            |

AN5727 - Rev 1 page 4/65

## 4 5 V power supply application reference design

This reference design targets an application powered by a 5 V power supply with 2 x DDR4, an eMMC, and an SD card.

The boot flash memory on eMMC. Other peripherals like audio and display are added to illustrate the application. A reference design with a USB high speed Type C power deliver is available on [1].

The main peripheral interfaces function with an I/O voltage of 3V3. The overall system is illustrated in Figure 1.

AN5727 - Rev 1 page 5/65

STM32MP25xx STPMIC25APQR 素口 素口 D14 (I2C7\_SDA SYSTEM CONTROL D15 (I2C7\_SCL) A0 (PWR\_WKUP VRCTRL1 & LOGIC RCTRL2 WR CPU ON VIN (4.1V to 5.5V) D1 domair VDDCPU (0.80V) VLX1 BUCK1IN BUCK1 0.5-1.5V / 1A ₹ PGND1 VOUT1 D2 domain VDDCORE (0.82V) CPU2 (M33) BUCK2 0.5-1.5V / 2A ₹ VDDGPU (0.80V) BUCK3 0.5-1.5V / 2A Retention RAM VDDIO (3.3V) Backup RAM LPSRAM1 VDD Domain BUCK4 1.5-4.2V / 0.5/ RIFSC IAC IWDGs BSEC DAP Ŧ D3 domain VDDA1V8\_AON (1.8V) LDO1 VDD EMMC (3.3V) LDO2 4 PLLs, BUCK5 1.5-4.2V / 0.5A ⇟ INTLDO INTLDO ţ SUPPLY LDO4 VDD3V3\_USB (3.3V) SDMMC2 IOs OCTOSPIM\_P4 IOs VDD\_DDR (1.2V) VLX6 BUCK6 0.5-1.5V / 1.5A Ŧ VOUT6 VREF\_DDR (0.6V) REFDDR LVDS VTT\_DDR (0.6V) LDO3 Ţ LDO5 VPP\_DDR (2.5V) Ţ DSI LDO6 3V3 VDD\_SDCARD (3.3V) LDO7 .9-4V-BP / 40 Domain (ADC/DAC) Ţ VDDIO\_SDCARD (3.3V/1.8V) LDO8 VLX7 BUCK7 1.5-4.2V / 2.5A Ť VOUT7 VDD/VDDQ VIN Peripherals DDR4 /REFCA Display VDD EMMC eMMC Audio SD-Card vcc Q-SPI NOR Legends digital signals power signals

Figure 1. STM32MP25x and STPMIC25APQR with 2xDDR4, eMMC, SD card

Note: The following are not shown in the diagram:

- STM32MP25x decoupling scheme (see [1])

- STPMIC25APQR discrete components value (see [2])

- V<sub>IN</sub> source and related protection, such as ESD, EMI filtering, overvoltage.

AN5727 - Rev 1 page 6/65

#### 4.1 Power distribution

The STPMIC25APQR integrates the regulators that supply:

- The STM32MP25x power domains

- The application peripherals.

#### 4.1.1 V<sub>DDCPU</sub> power domain (800 mV/910 mV)

V<sub>DDCPU</sub> supplies the dual Arm<sup>®</sup> Cortex<sup>®</sup>-A35 platform (CPU1), called the D1 domain.

$V_{\text{DDCPU}}$  is powered from the very efficient STPMIC25 BUCK1 step-down SMPS. The SMPS has an excellent *load transient response* across all operating conditions.

At power-up, the  $V_{DDCPU}$  is automatically enabled by the STPMIC25 at 800 mV, which corresponds to the "nominal mode" voltage. (See Section 5.2.1: Power-up triggered main supply ( $V_{IN}$ ) plugin/power-down by software shutdown).

V<sub>DDCPU</sub> is enabled in:

- Run1 mode

- Low power LP-Stop1 mode

- Low power LPLV-Stop1 mode.

V<sub>DDCPU</sub> is disabled in the following modes:

- Run2 mode

- Low power LP-Stop2 mode

- Low power LPLV-Stop2 mode

- Low power Standby mode

- V<sub>BAT</sub> mode and OFF mode.

In low-power modes, the PWR\_CPU\_ON output of the MPU manages the STPMIC25  $V_{DDCPU}$  regulator. The PWR\_CPU\_ON is connected to the PWRCTRL2 input of the STPMIC25.

At runtime, the CPU1 can operate in *nominal mode* or in *overdrive mode*. The  $V_{DDCPU}$  voltage is then adjusted to the chosen mode. The MPU manages the transition between *nominal mode* voltage and *overdrive mode* voltage by sending I²C commands to the STPMIC25. The  $V_{DDCPU}$  voltage is increased to the "overdrive mode" voltage value (910 mV) when the CPU1 frequency (Fcpu1\_overdrive) operates above 1200 MHz. When the CPU1 operates in "nominal mode" at 1200 MHz or below, the  $V_{DDCPU}$  must be set back to "nominal mode" voltage value (800 mV).

#### 4.1.2 V<sub>DDCORE</sub> power domain (670 mV/ 820 mV)

V<sub>DDCORE</sub> is the main STM32MP25x digital power domain, and is called the D2 domain.

V<sub>DDCORE</sub> supplies all the digital circuits, which include:

- The Arm<sup>®</sup> Cortex<sup>®</sup>-M33 platform (CPU2)

- Some analog IP of the MPU such as:

- COMBOPHY

- LVDS

- CSI

- DSI, and so on.

V<sub>DDCORE</sub> is powered from the high efficiency STPMIC25 BUCK2 step-down SMPS. This SMPS has an excellent *load transient response* across operating conditions.

At power-up,  $V_{DDCORE}$  is automatically enabled by the STPMIC25 at 820 mV. (See Section 5.2.1: Power-up triggered main supply  $(V_{IN})$  plugin/power-down by software shutdown)

AN5727 - Rev 1 page 7/65

V<sub>DDCORF</sub> is enabled in:

- Run1 mode

- Run2 mode

- Low power LP-Stop1 mode

- Low power LP-Stop2 mode.

The voltage is lowered to 670 mV in:

- Low power LPLV-Stop1 mode

- Low power LPLV-Stop2 mode.

V<sub>DDCORE</sub> is disabled in:

- Low power Standby mode

- V<sub>BAT</sub> mode

- OFF mode.

In low power mode, the PWR\_ON output of the MPU manages the STPMIC25  $V_{DDCORE}$  regulator. The PWR\_ON output is connected to the PWRCTRL1 input of the STPMIC25.  $V_{DDCORE}$  also supplies the D3 backup domain and the retention domain in Run1 and Run2, and Stop1 and Stop 2 modes. (See Section 4.1.10: MPU backup domain and retention domain).

Note: D3 domain integrates all peripherals that must be functional in low power mode.

#### 4.1.3 V<sub>DDGPU</sub> power domain (800 mV/ 900 mV)

V<sub>DDGPU</sub> supplies the graphic processing unit (GPU) and neural processing unit (NPU).

V<sub>DDGPU</sub> is powered from the very efficient STPMIC25 BUCK3 step-down SMPS. This SMPS has an excellent load transient response across operating conditions.

At power-up, V<sub>DDGPU</sub> is not automatically enabled by the STPMIC25.

At runtime, the MPU manages the  $V_{DDGPU}$  regulator by sending I²C commands to the STPMIC25. By default, the  $V_{DDGPU}$  regulator is set at 800 mV in "nominal mode" when the GPU frequency operates at 800 MHz or below.  $V_{DDGPU}$  regulator is set at 900 mV to run in "overdrive mode" when the GPU frequency ( $f_{gpu\_overdrive}$ ) operates above 800 MHz. The  $V_{DDGPU}$  regulator is disabled during low power modes.

#### 4.1.4 V<sub>DDIO</sub> and V<sub>DDA1V8</sub> AON power domains

$V_{DDIO}$  is the power supply for the following independent MPU I/Os:

- V<sub>DD</sub>

- V<sub>DDIO1</sub>

- V<sub>DDIO2</sub>

- V<sub>DDIO3</sub>

- V<sub>DDIO4</sub>.

$V_{DDIO}$  is also the power supply of the MPU  $V_{DD}$  for the retention domain (see Section 4.1.10: MPU backup domain and retention domain for more details). These separate/dedicated I/O supplies can be set to different voltages or be shut down independently.

V<sub>DDA1V8</sub> AON domain supplies the MPU V<sub>DDA1V8</sub> AON system analog such as:

- Reset block

- Power management (POR/PDR)

- Oscillators (HSE, HSI)

- OTP controller (BSEC)

V<sub>DDIO</sub> is powered from the STPMIC25 BUCK4 step-down SMPS, which is dedicated to the supply of sensitive powers domains and has a low output voltage ripple across all operating conditions. V<sub>DDA1V8\_AON</sub> is powered by the dedicated STPMIC25 LDO1 linear regulator, which has a very low quiescent current to reduce power consumption during low power mode.

At power-up,  $V_{DDIO}$  and  $V_{DDA1V8\_AON}$  are automatically enabled to 3.3 V and 1.8 V respectively by the STPMIC25. They are the first regulators switched on at power-up (see Section 5.2.1: Power-up triggered main supply  $(V_{IN})$  plugin/power-down by software shutdown).

AN5727 - Rev 1 page 8/65

The STPMIC25 LDO1 ( $V_{DDA1V8\_AON}$ ) has a built-in power supply multiplexor, which is either powered by LDO12IN (connected to  $V_{IN}$  supply at application level) or by the STPMIC25 BUCK4 output (VOUT4). By default, when the STPMIC25 is powered-up, the LDO12IN is selected as the LDO1 power source. Once the MPU is powered on and initialized, the software switches the LDO1 input source from LDO12IN to BUCK4 output (VOUT4) via an I²C command to the STPMIC25. This improves the power efficiency of the LDO1 from 36% (when the LDO4 input source is at 5 V from the LDO12IN) to 54% (when the LDO4 input source is at 3.3 V from the BUCK4 VOUT4).

Note:

To set LDO1 input source from LDO12IN to VOUT4, the MPU software reprograms the STPMIC25 LDO1\_MAIN\_CR[INPUT\_SRC] and LDO1\_ALT\_CR[INPUT\_SRC] registers bit to 1 via an I<sup>2</sup>C commands (see document [2] for details).

In Standby mode, the BUCK4 step-down SMPS is set to low power mode. The MPU sets the STPMIC25 to Standby mode via the PWR\_ON output connected to the PWRCTRL1 input of the STPMIC25 (see document [2] for details).  $V_{DDIO}$  and  $V_{DDA1V8\_AON}$  are ON in all modes except in OFF or  $V_{BAT}$  mode; when the main power source ( $V_{IN}$ ) of the application is removed (see Section 4.1.10: MPU backup domain and retention domain for details).

#### 4.1.5 V<sub>DD3V3 USB</sub> power domain

$V_{DD3V3\_USB}$  power domain supplies the USB2 HS PHY ( $V_{DD3V3\_USB}$ ) and the USB PD (power delivery) PHY ( $V_{DD33UCPD}$ ) of the MPU.

Note:

Examples of USB implementations with the STM32MP25x are provided in this document [1].

V<sub>DD3V3</sub> USB is powered from the dedicated STPMIC25 LDO4 with a fixed output voltage of 3.3 V.

Note:

The STPMIC25 LDO4 has a built-in power supply multiplexor powered either from STPMIC25 VIN pin or VBUS pin, which automatically selects the highest input voltage. It is designed specifically for battery-powered applications to keep both the MPU USB PHY and PD PHY working when the battery is discharged. This feature is not applicable to this application note and the STPMIC25 VBUS pin must be left floating (unconnected).

At power-up, the  $V_{DD3V3\_USB}$  regulator is automatically enabled to 3.3 V by the STPMIC25 (See Section 5.2.1: Power-up triggered main supply ( $V_{IN}$ ) plugin/power-down by software shutdown).

If a USB peripheral is connected to the application,  $V_{DD3V3}$  USB can be kept enabled in the following modes:

- Run1 mode

- Run2 mode

- Low power LP-Stop1 mode

- Low power LP-Stop2 mode

- Low power LPLV-Stop1 mode

- Low power LPLV-Stop2 mode.

$V_{DD3V3\_USB}$  is disabled in Standby and OFF mode. In this mode, the USB protection device (TCPP0x) must be shut down, so the USB CC lines are disconnected. In low power mode, MPU software controls the  $V_{DD3V3\_USB}$  using I²C controls and it can be either switched ON/OFF.

#### 4.1.6 DDR power domain (V<sub>DD DDR</sub>, V<sub>TT DDR</sub>, V<sub>PP DDR</sub>, V<sub>REF DDR</sub>)

Several power domains are dedicated to supplying the DDR types supported by the MPU: DDR3L, DDR4, and IpDDR4.

This application focuses on DDR4 topology.

$V_{DD\_DDR}$  (1.2 V) is powered from the STPMIC25 BUCK6 step-down SMPS to power the DDR4 memory ICs ( $V_{DDR}$  and  $V_{DDQ}$ ) and MPU DDR PHY ( $V_{DDQDDR}$ ) domains.

$V_{REF\_DDR}$  (0.6 V) is powered from the STPMIC25 REFDDR sink source LDO. The supply source of the REFDDR LDO is internally connected to the BUCK6 output ( $V_{OUT6}$ ) and provides a voltage equal to  $V_{OUT6}$ /2 to power the DDR4 memory  $V_{REFCA}$ .

Note:

- The MPU DDR\_VREF must remain unconnected.

- If BUCK6 is disabled but REFDDR is enabled, V<sub>REF\_DDR</sub> follows the output voltage of BUCK6 with an output voltage equal to V<sub>OUT6</sub>/2.

AN5727 - Rev 1 page 9/65

$V_{TT\_DDR}$  (0.6 V) is powered from the STPMIC25 LDO3 multipurpose LDO. When set in sink-source mode, the LDO3 provides voltage equal to  $V_{REF\_DDR}$  (implicitly  $V_{OUT6}$  / 2). The LDO3 sink-source mode is dedicated to power the DDR4 memory bus terminations.

Note:

To optimize power efficiency, the supply source of LDO3 (LDO3IN) is powered from BUCK6 output (V<sub>DD DDR</sub>).

V<sub>PP DDR</sub> (2.5 V) is powered from the STPMIC25 general purpose LDO5 to power the DDR4 memory V<sub>PP</sub>.

At power-up, the STPMIC25 does not automatically start the following regulators:

- V<sub>DD DDR</sub>

- V<sub>TT DDR</sub>

- V<sub>PP\_DDR</sub>

- V<sub>REF DDR</sub>

The regulators are powered up sequentially by the software bootloader by sending I<sup>2</sup>C commands to the STPMIC25. This is detailed in the following section and in Section 5.2.1: Power-up triggered main supply (V<sub>IN</sub>) plugin/power-down by software shutdown.

At runtime, the PWR\_ON output of the MPU, connected to the PWRCTRL1 input of the STPMIC25, manages the DDR4 power domains as follows:

- $V_{TT\_DDR}$  (LDO3) is switched OFF, and the DDR4 is set in self-refresh in the following modes:

- Low power LP-Stop1 mode

- Low power LP-Stop2 mode

- Low power LPLV-Stop1 mode

- Low power LPLV-Stop2 mode.

- In Standby mode, there are two possible scenarios:

- DDR4 in self-refresh: similarly to low power modes, is detailed in Section 5.3.4: Standby mode (DDR4 in self-refresh).

- DDR4 OFF: all DDR regulators are powered OFF and detailed in Section 5.3.5: Standby mode (DDR4 OFF).

At power down, and before the software turns OFF the STPMIC25, a power-down sequence must be applied on DDR4 power domains to comply with the JEDEC DDR4 specification (see details in Section 4.1.7:  $V_{DD\_EMMC}$  power domain (3.3 V)).

Note:

The STPMIC25 embeds configurable pull-down discharge resistors on each of the regulator outputs that allow all of regulator output voltages to discharge in less than 1.5 ms. For BUCK regulators, two pull-down values are configurable in NVM to either: slow pull-down and fast pull-down. Depending on the pull-down configuration, the discharge delay is set as follows: Slow PD =1.5 ms and Fast PD=0.3 ms. The "fast pull-down" configuration is used to switch off a power supply quickly than another one. The configuration is used on the DDR uncontrolled power down sequence

#### Software DDR4 power-up sequence:

- Power-on event (or standby DDR-OFF mode exit): STPMIC25 power up (or standby DDR-OFF mode recovery)

- 2. The software bootloader executes DDR4 initialization.

- 3. The software bootloader sets the STPMIC25 internal pull-down for each DDR regulator as described in the note below:

- a. LDO5 ( $V_{PP\_DDR}$ ) pull down is disabled when LDO5 is disabled: LDOS\_PD\_CR1[LDO5\_PD] = 0

- BUCK6 (V<sub>DD\_DDR</sub>) fast pull down is activated when BUCK6 is disabled:

BUCKS PD CR2[BUCK6 PD]=10

- REFDDR (V<sub>REF\_DDR</sub>) pull down is activated when REFDDR is disabled: LDOS\_PD\_CR2[REFDDR\_PD] = 1

- d. LDO3 ( $V_{TT\_DDR}$ ) pull down is activated when LDO3 is disabled: LDOS\_PD\_CR1[LDO5\_PD] = 1

Note:

It is necessary to set this pull down every time the STM32MP25x is powered up to prevent a "DDR4 uncontrolled power OFF sequence" (see DDR4 uncontrolled power off sequence:)

AN5727 - Rev 1 page 10/65

- 4. The software bootloader enables the DDR regulators:

- a. Enable LDO5 (V<sub>PP DDR</sub>) at 2.5 V

- b. Wait 1 ms tempo

- c. Enable LDO3 in sink-source mode (V<sub>TT DDR</sub>)

- d. Enable REFDDR (VREF DDR)

- e. Enable BUCK6 (V<sub>DD DDR</sub>) at 1.2 V

- f. Wait 1 ms tempo

- 5. Software initializes the MPU DDR4 memory controller and DDR4 ICs

Note:

The above sequence aims to fulfill the JEDEC DDR4 where  $V_{PP\_DDR}$  must ramp at the same time or before  $V_{DD\_DDR}$ , and  $V_{PP\_DDR}$  must always be equal to or higher than  $V_{DD\_DDR}$ . Refer to the latest JEDEC DDR4 specification for more details.

#### Software DDR4 power down sequence:

- 1. Software receives an event to enter OFF mode or standby DDR-OFF mode.

- 2. Assert DDR CKE low

- 3. Disable BUCK6 (V<sub>DD DDR</sub>)

- 4. Wait 1 ms tempo

- 5. Disable V<sub>REF DDR</sub>

- 6. Disable LDO3 (V<sub>TT DDR</sub>)

- 7. Disable LDO5 (V<sub>PP DDR</sub>)

Note:

V<sub>PP DDR</sub> voltage falls slowly as LDO5 pull-down discharge when disabled

#### DDR4 uncontrolled power off sequence:

An uncontrolled power off sequence occurs typically when the main power supply voltage is removed or when a reset occurs.

Then the STPMIC25 manages the power off sequence:

Note:

To ensure this uncontrolled power down sequence. At software boot, the STPMIC25 pull-down settings are set (see Software DDR4 power-up sequence:)

- V<sub>IN</sub> is removed.

- 2. V<sub>IN</sub> crosses the VINOK\_fall: STPMIC25 is in turn off condition.

- STPMIC25 starts the power off sequence.

- a. STPMIC25 asserts a reset (NRST): STM32MP25x stops the DDRPHYC especially the DRAM differential clocks (DDRA\_CKP/N and DDRB\_CKP/N)

- b. STPMIC25 disables Rank0 regulators:

- LDO5 (V<sub>PP DDR</sub>)

- BUCK6 (V<sub>DD DDR</sub>)

- LDO3 (V<sub>TT DDR</sub>)

- V<sub>REF DDR</sub>

- 4. The voltages of the following regulators are discharged through their respective regulator pulldown resistors:

- BUCK6 (V<sub>DD\_DDR</sub>)

- LDO3 (V<sub>TT DDR</sub>)

- V<sub>REF\_DDR</sub>.

- 5. LDO5 (V<sub>PP DDR</sub>) falls slowly as it discharges through the LDO5 pull-down discharge when LDO5 is disabled.

AN5727 - Rev 1 page 11/65

#### 4.1.7 V<sub>DD EMMC</sub> power domain (3.3 V)

V<sub>DD\_EMMC</sub> supplies the *eMMC flash memory core domain* (V<sub>CC</sub>). The eMMC interface (V<sub>CCQ</sub>) with the related MPU interface (VDDIO2) are powered by the 1V8 power domain to work in high speed mode (HS200)

$V_{DD\ EMMC}$  is powered from the STPMIC25 LDO2 general purpose linear regulator.

At power-up, the  $V_{DD\_EMMC}$  regulator is enabled automatically by the STPMIC25 to 3.3 V (see Section 5.2.1: Power-up triggered main supply ( $V_{IN}$ ) plugin/power-down by software shutdown).

V<sub>DD EMMC</sub> enables the MPU to have read/write access in the following modes:

- Run1 mode

- Run2 mode

- Low power LPLV-Stop1 mode.

When no read/write access is expected, the MPU software can disable  $V_{DD\_EMMC}$ .  $V_{DD\_EMMC}$  is disabled in the following modes:

- Stop mode

- LPLV-Stop2 mode,

- Standby mode

- OFF mode.

The MPU PWRCTRL pin can manage  $V_{DD\_EMMC}$ . In low power mode, the  $V_{DD\_EMMC}$  can be either switched ON or OFF by the application software.

#### eMMC as boot device

If the eMMC device is the boot flash peripheral, the application software must program the STPMIC25 as follows:

- 1. Power OFF the eMMC in Standby mode

- 2. Power ON the eMMC in Run1 mode before the application goes into Standby mode. In this case, V<sub>DD\_EMMC</sub> is required for the first level boot of CPU1 and needs a power cycle to ensure a platform reboot. To carry out a power recycle, the V<sub>DD\_EMMC</sub> of the STPMIC25 regulator is managed by the NRSTC1MS output of the MPU. The NRSTC1MS output is connected to the PWRCTRL3 input of the STPMIC25 (see PWRCTRL1, PWRCTRL2, PWRCTRL3 for details).

AN5727 - Rev 1 page 12/65

## 4.1.8 SD card power domains (V<sub>DD\_SDCARD</sub>, V<sub>DDIO\_SDCARD</sub>)

$V_{DD\_SDCARD}$  supplies the SD card memory device ( $V_{DD}$ ). The  $V_{DDIO\_SDCARD}$  is dedicated to power the built-in MPU level shifter ( $V_{DDIO1}$ ) and consequently to support SD card UHS-I mode.

V<sub>DD\_SDCARD</sub> (3.3 V) is powered from the STPMIC25 BUCK7 step-down SMPS (3V3 node) via the STPMIC25 LDO7 acting as a power switch (bypass mode).

V<sub>DDIO\_SDCARD</sub> (3.3 V/1.8 V) is powered from the STPMIC25 BUCK7 step-down SMPS (3V3 node) via the STPMIC25 LDO8 acting as a power switch (LDO8 set in bypass mode) for 3.3 V output voltage or acting as an LDO (LDO8 set in LDO mode at 1.8 V) for 1.8 V output voltage.

Note:

The STPMIC25 LDO7 and LDO8 input (LDO78IN) are powered from BUCK7 output (3V3 node). LDO7 or LDO8 are set in bypass mode when  $V_{DD\_SDCARD}$  or  $V_{DDIO\_SDCARD}$  respectively are enabled and set in OFF mode when  $V_{DD\_SDCARD}$  or  $V_{DDIO\_SDCARD}$  respectively are disabled. The STPMIC25 bypass mode feature allows excellent power efficiency operation (close to 100%), compared to LDO mode where power efficiency is reaches 66% at best ( $V_{OUT}/V_{IN}$  = 3.3 V/5 V).

At power-up, V<sub>DD SDCARD</sub> and V<sub>DDIO SDCARD</sub> regulators are not started automatically by the STPMIC25APQR.

Note:

If the SD card is a boot flash peripheral, then the STPMIC25APQR NVM must be reprogrammed to start LDO7 and LDO8 automatically.

The voltage of the SD card data interface (V<sub>DDIO\_SDCARD</sub>) is changed at runtime depending on the speed settings of the SD card bus:

- Default bus speed (V<sub>DDIO SDCARD</sub> = 3.3 V):

- V<sub>DD\_SDCARD</sub> is powered by LDO7 set in bypass mode (3.3 V)

- V<sub>DDIO</sub> SDCARD is powered by LDO8 set in bypass mode (3.3 V)

- UHS-I bus speed (V<sub>DDIO SDCARD</sub> = 1.8 V):

- V<sub>DD\_SDCARD</sub> is powered by LDO7 set in bypass mode (3.3 V)

- V<sub>DDIO</sub> SDCARD is powered by LDO8 set in LDO mode at 1.8 V

#### SD card as boot device

As already mentioned in this section, the STPMIC25APQR does not automatically start at power up to the following:

- LDO7

- LDO8.

The SD card is not used as a boot device as described in the Overview.

Note:

If the SD card device requires to be a boot flash peripheral, the production test software (used in mass production to test and to tune the end-product) must reprogram the STPMIC25 NVM to start LDO7 and LDO8 automatically at power-up. For example, to start automatically the LDO7 and LDO8 in bypass mode in STPMIC25 RANK4 (see document [2] for details).

In addition, as eMMC boot flash, the signal NRSTC1MS connected to PWRCTRL3 is used to power cycle the SD card regulators (LDO7 and LDO8) in case of D1 crash. See Section 5.4.2: CPU1 crash recovery management.

#### 4.1.9 1V8 power domain

1V8 is an analog power supply domain for the MPU, which are:

- PLLs (V<sub>DDA18PLLx</sub>)

- USB2 PHY (V<sub>DDA18USB</sub>)

- COMBOPHY (V<sub>DDA18COMBOPHY</sub>)

- LVDS (V<sub>DDA18LVDS</sub>)

- CSI (V<sub>DDA18CSI</sub>)

- DSI (V<sub>DDA18DSI</sub>)

- ADC/DAC (V<sub>DDA18ADC</sub>)

- DDR PHY(V<sub>DDA18DDR</sub>).

The 1V8 power domain is also used to supply power to peripherals such as eMMC (V<sub>CCQ</sub>).

AN5727 - Rev 1 page 13/65

The 1V8 power domain is powered from the STPMIC25 BUCK5 step-down SMPS, which has reduced output voltage ripple across operating conditions.

At power-up, the 1V8 regulator is automatically enabled by the STPMIC25 (See Section 4.2.2: STPMIC25APQR digital control interface ).

At runtime, 1V8 is:

- Enabled in:

- Run1 mode

- Run2 mode

- Low power LP-Stop1 mode

- Low power LP-Stop2 mode

- Low power LPLV-Stop1 mode

- Low power LPLV-Stop2 mode

- Disabled in:

- Standby mode

- V<sub>BAT</sub>/OFF modes.

AN5727 - Rev 1 page 14/65

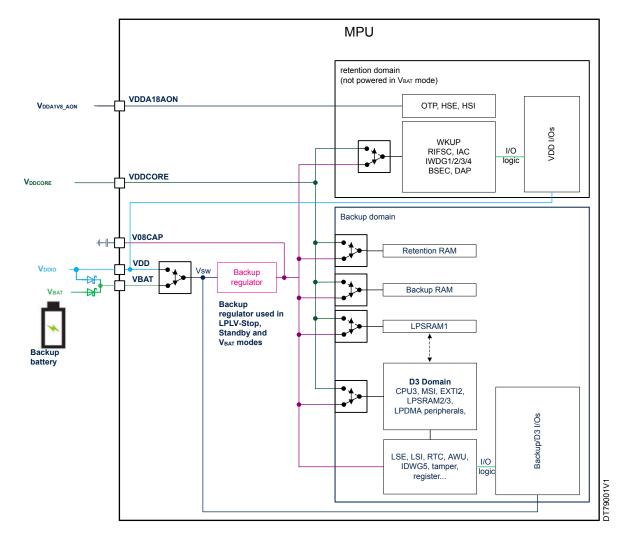

#### 4.1.10 MPU backup domain and retention domain

The MPU has two internal power domains to keep critical data and security data in memory (see Figure 2):

- The backup domain supplies:

- RTC

- Watchdogs

- LSE

- LSI

- LPSRAM1

- Retention RAM

- Backup RAM

- D3 domain.

They must be retained when  $V_{DDIO}$  is turned off to keep critical data or security. The backup domain is powered in all operating modes, including  $V_{BAT}$  mode where  $V_{BAT}$  is typically powered from a coin cell backup battery.

- The retention domain supplies:

- Boot

- Security

- OTP controller (BSEC)

- Independent watchdog (IWDG)

- Resource isolation framework controller (RIFSC and IAC)

- Debug access port (DAP).

The retention domain is powered in all operating modes, excluding V<sub>BAT</sub> mode.

These two domains are powered by either:  $V_{DDCORE}$ ,  $V_{DD}$ , or  $V_{BAT}$  depending on which supply is available and the operating mode of the MPU:

- The backup domain and the retention domain are powered from the V<sub>DDCORE</sub> supply in the following modes:

- Run1 mode

- Run2 mode

- Low power LP-Stop1 mode

- Low power LP-Stop2 mode.

- The backup domain and the retention domain are powered from the  $V_{DD}$  supply via the internal backup regulator (decoupling capacitor on V08CAP pin) in the following modes:

- Low power LPLV-Stop1 mode

- Low power LPLV-Stop2 mode

- Standby mode.

- In V<sub>BAT</sub> mode, where V<sub>BAT</sub> is powered from a backup battery, the internal backup domain is powered from the V<sub>BAT</sub> supply via the backup regulator.

Note: The retention domain is not powered in  $V_{BAT}$  mode.

AN5727 - Rev 1 page 15/65

Figure 2. Backup and retention domain

For more details on the constraints on V<sub>BAT</sub> rise time, refer to the document [1].

#### 4.1.11 3V3 external peripherals power domain

The 3V3 power domain is used to power peripherals around the MPU, such as the display, audio, and so on. It is also used to supply the STPMIC25 LDO7 and STPMIC25 LDO8 set in bypass mode in this application to power the SD card.

3V3 is powered from the STPMIC25 BUCK7 step-down general purpose SMPS. This regulator is designed to allow high current consumption.

### 4.2 Control signals between STPMIC25APQR and STM32MP25x

This section outlines the way the STM32MP25x microprocessor communicates with the STPMIC25APQR device. Several interfaces are available depending on the application requirements.

#### 4.2.1 STPMIC25APQR default behavior with STM32MP25x

The STPMIC25APQR NVM settings are configured to boot the MPU application from flash memory such as eMMC or to boot the MPU from the USB interface. In production, it is used for flashing and then executing the software. The default NVM configuration is available in [2] and summarized in the following table.

AN5727 - Rev 1 page 16/65

| Table 4. | Default | NVM | configuration |

|----------|---------|-----|---------------|

|----------|---------|-----|---------------|

| Regulator | Name                     | Rank  | Default output voltage | Default configuration |

|-----------|--------------------------|-------|------------------------|-----------------------|

| BUCK1     | V <sub>DDCPU</sub>       | RANK3 | 0.8 V                  | ON_HP                 |

| BUCK2     | V <sub>DDCORE</sub>      | RANK2 | 0.82 V                 | ON_HP                 |

| BUCK3     | V <sub>DDGPU</sub>       | RANK0 | NA                     | Software management   |

| BUCK4     | V <sub>DDIO</sub>        | RANK1 | 3.3 V                  | ON_HP                 |

| BUCK5     | 1V8                      | RANK3 | 1.8 V                  | ON_HP                 |

| BUCK6     | V <sub>DD_DDR</sub>      | RANK0 | NA                     | ON_HP                 |

| BUCK7     | 3V3                      | RANK4 | 3.3 V                  | Software management   |

| LDO1      | V <sub>DDA1V8</sub> _AON | RANK1 | 1.8 V                  | ON                    |

| LDO2      | V <sub>DD_EMMC</sub>     | RANK4 | 3.3 V                  | Software management   |

| LDO3      | V <sub>TT_DDR</sub>      | RANK0 | N/A                    | ON                    |

| LDO4      | V <sub>DD3V3_USB</sub>   | RANK5 | 3.3 V                  | Software management   |

| LDO5      | V <sub>PP_DDR</sub>      | RANK0 | N/A                    | ON                    |

| LDO6      | Free (not used)          | RANK0 | N/A                    | OFF                   |

| LDO7      | V <sub>DD_SDCARD</sub>   | RANK0 | N/A                    | OFF                   |

| LDO8      | V <sub>DDIO_SDCARD</sub> | RANK0 | N/A                    | OFF                   |

| REFDDR    | V <sub>REF_DDR</sub>     | RANK0 | N/A                    | ON                    |

In order to start the application, the STPMIC25 regulator start up is spread across five ranks. This is to comply with the MPU power-up sequence constraints and to avoid current peaks on the main power supply. The voltage value of each regulator is defined to fit with the MPU optimum voltage requirements.

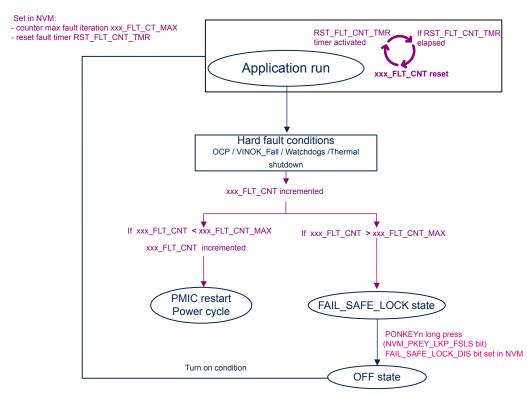

#### For safety management

By default, when a fault occurs the STPMIC25APQR safety management features systematically restarts the application. The STPMIC25 performs a power cycling to systematically restart the application when a fault is detected by the STPMIC25, such as:

- V<sub>IN</sub> undervoltage

- Over temperature

- Regulator OCP, and so on.

## **PMIC tuning (optional)**

The STPMIC25 NVM can be reprogrammed by the customer to fine-tune the regulator settings, and the safety management behavior to fit with the MPU based application requirements. This action can be done with the STM32CubeProgrammer.

#### 4.2.2 STPMIC25APQR digital control interface

The STPMIC25APQR integrates an I<sup>2</sup>C interface, five digital input control pins: PONKEYn, PWRCTRL1/2/3, WAKEUPn; a digital output interrupt pin (INTn), and a bidirectional digital reset pin (RSTn).

#### I<sup>2</sup>C interface

The MPU is controls the STPMIC25APQR via the I<sup>2</sup>C interface to:

- Enable/disable, set the voltage, and operating mode of the regulators.

- Dynamic voltage scaling to switch the MPU in nominal or overdrive modes.

- Set regulators external control for low power mechanisms (PWRCTRLx).

- Set the interrupt controller or read interrupt status.

- Set the protection for the watchdog, overcurrent, undervoltage, or read protection status.

AN5727 - Rev 1 page 17/65

Tune the STPMIC25APQR NVM default configuration for the end-product (power-up sequence, safety management) see Section 5.3: Low power mode management for details

#### **PONKEYn pin (optional)**

The STPMIC25APQR PONKEYn pin is a digital active low input signal. It is usually connected to a user push button "ON/INT" to power on the application. Thanks to the STPMIC25 built-in pullup resistor, there is no need for a discrete pullup resistor on this signal.

The PONKEYn signal allows the following operations:

- Turns on the STPMIC25APQR (from PMIC OFF state)

- Wakes up the application from a low-power mode (typically from Standby mode).

- Forces a switch-off or a power cycling condition with a long press. This duration is programmable as described in section Section 5.1.1: Application turn-on/turn-off conditions.

Note:

The use of a push "ON/INT" button connected to the PONKEYn is optional as the STPMIC25APQR is automatically turned on when the application is powered (see section Section 4.2.1: STPMIC25APQR default behavior with STM32MP25x).

#### RSTn pin

The STPMIC25APQR RSTn pin must be connected to the MPU NRST pin. It can also be connected to a "RESET" push button. This is achieved by using the STPMIC25 built-in pullup resistor, and no additional discrete pullup resistor is needed on this signal. Nevertheless, a 10 nF capacitor is fixed to the ground and placed as close as possible to the MPU. This is specifically required on this signal to avoid EMI/coupling as there is no debounce circuitry in neither the MPU, nor the STPMIC25.

The STPMIC25APQR RSTn pin is a digital active low bidirectional signal with a built-in pullup resistor:

- When STPMIC25APQR asserts an RSTn (such as during the power-up or the power-down sequence), it drives the MPU NRST signal low (open drain). The MPU is forced into a system reset until the STPMIC25APQR releases the RSTn.

- When the MPU asserts an NRST signal such as an MPU watchdog event, or by pressing the "RESET" button, the STPMIC25APQR immediately asserts the RSTn pin and performs a noninterruptible power cycle. The STPMIC25APQR performs a power down sequence, followed by a power-up sequence and releases the RSTn.

At the end of the power-cycle sequence, the STPMIC25APQR waits for the MPU NRST signal to go high before rearming the reset detection mechanism to avoid infinite loop reset.

#### INTn signal

The STPMIC25APQR INTn pin is a digital output (open drain) active low interrupt line connected to the MPU PA0 input pin. Thanks to the STPMIC25 built-in pullup resistor, a discrete pullup resistor is not required on this signal. PA0 has both interrupt and wake-up capability:

- To manage an interrupt from the STPMIC25APQR when the MPU operates in either run mode or a low power mode (except Standby mode).

- To wake up the MPU when, it operates in Standby mode.

#### PWRCTRL1, PWRCTRL2, PWRCTRL3

The STPMIC25APQR has three power control digital input signals connected to dedicated MPU control signals. Each STPMIC25APQR regulator can be controlled from a single PWRCTRL signal; typically to switch on or off, or depending on the PWRCTRL signal state to change the regulator output voltage. Alternatively, a PWRCTRL signal can be configured to reset a regulator at a value defined in STPMIC25APQR NVM (see document [2] for details)

MPU power control connection to STPMIC25APQR:

AN5727 - Rev 1 page 18/65

- The MPU PWR\_ON output pin controls the STPMIC25APQR PWRCTRL1 input pin. In this application illustrated in Figure 1, the MPU PWR\_ON is multiplexed with the MPU PWR\_LP signal. To do this, PWR\_D2CR.[LPCFG\_D2] must be set to 1 by the software after a system reset.

In this application, the multiplexing is selected so the MPU PWR\_ON signal manages:

- LPLV-Stop1 mode

- LPLV-Stop2 mode

- Standby mode

When the multiplexing is not selected, the MPU PWR\_ON signal only manages the Standby mode.

- The MPU PWR\_CPU\_ON output pin controls the STPMIC25APQR PWRCTRL2 pin. In the application illustrated in Figure 1, the MPU PWR\_CPU\_ON controls the MPU D1 domain (V<sub>DDCPU</sub>) when this domain is in DStandby (see [3] for more details) set in LPLV-Stop2 mode and Standby low power mode. The internal SOC pwr\_cpu\_on signal can also be multiplexed with the internal SOC pwr\_cpu\_lp signal. To do this, the PWR\_D1CR[LPCFG\_D1] must be set to 0 by the software after a system reset. This keeps the PWR\_CPU\_ON = 1 in LP-Stop1 mode and LPLV-Stop1 mode.

- The MPU NRSTC1MS pin controls the STPMIC25APQR PWRCTRL3 pin. NRSTC1MS pin is used to control the power supplies of the external flash. This power is required for first level boot of CPU1 and needs a power cycle to ensure a platform reboot (eMMC). The NRSTC1MS pin is activated when a system reset is generated. In this application, the NRSTC1MS is linked to MPU PWR\_CPU\_ON by a 10 k $\Omega$  pull-up resistor. This is illustrated in Figure 1.

See Section 5.1.2: STPMIC25APQR power control management (PWRCTRLx) for more details about STPMIC25APQR PWRCTRL settings.

#### WAKEUPn (optional)

The WAKEUPn signal is driven by the MPU PC13 (RTC\_OUT1) pin to control the STPMIC25APQR WAKEUP pin. It allows the MPU to power up the STPMIC25APQR, from STPMIC25APQR OFF state, or in MPU  $V_{BAT}$  mode, typically when the real-time clock timer elapses.

This is done by using the STPMIC25APQR built-in pullup resistor, therefore a discrete pullup resistor is not required on this signal.

AN5727 - Rev 1 page 19/65

## 5 Power management

## 5.1 Operating modes

The application can switch to different operating modes depending on the system activity. The MPU manages the operating modes and they control the power management. The operating modes are described in the table below.

Table 5. Operating modes

| Operating mode | PMIC state        | PWR_ON | PWR_CPU_ON | NRSTC1MS | Description                                                        | Notes                                                               |  |

|----------------|-------------------|--------|------------|----------|--------------------------------------------------------------------|---------------------------------------------------------------------|--|

|                |                   |        |            |          | V <sub>DDIO</sub> power on                                         |                                                                     |  |

|                |                   |        |            |          | V <sub>DDCORE</sub> power on                                       |                                                                     |  |

|                | POWER_ON          |        |            |          | V <sub>DDCPU</sub> power on<br>(in normal or<br>overdrive voltage) |                                                                     |  |

| Run1           | (RUN)             | 1      | 1          | 1        | V <sub>DDGPU</sub> controlled by software                          |                                                                     |  |

|                |                   |        |            |          | System clock on                                                    |                                                                     |  |

|                |                   |        |            |          | Peripherals power on/off                                           | The difference between Run1/2 and Stop1/2 mode is only based on the |  |

|                |                   |        |            |          | DDR4 active                                                        | STM32MP25x clock management and they have no impact on power        |  |

|                |                   |        |            |          | V <sub>DDIO</sub> power on                                         | management.                                                         |  |

|                | POWER_ON<br>(RUN) |        |            |          | V <sub>DDCORE</sub> power on                                       |                                                                     |  |

|                |                   | 1      | 0          | 0        | V <sub>DDCPU</sub> power off                                       |                                                                     |  |

| Run2           |                   |        |            |          | V <sub>DDGPU</sub> controlled by software                          |                                                                     |  |

|                |                   |        |            |          | System clock on                                                    |                                                                     |  |

|                |                   |        |            |          | Peripherals power on/off                                           |                                                                     |  |

|                |                   |        |            |          | DDR4 active                                                        |                                                                     |  |

|                |                   |        |            |          | V <sub>DDIO</sub> power on                                         |                                                                     |  |

|                |                   |        |            |          | V <sub>DDCORE</sub> power on                                       |                                                                     |  |

|                |                   |        |            |          | V <sub>DDCPU</sub> power on (in normal voltage)                    |                                                                     |  |

| LP-Stop1 mode  | POWER_ON          | 0      | 1          | 1        | V <sub>DDGPU</sub> controlled by software                          | -                                                                   |  |

|                | (RUN)             |        |            |          | System clock on                                                    |                                                                     |  |

|                |                   |        |            |          | Peripherals power on/off                                           |                                                                     |  |

|                |                   |        |            |          | DDR4 self-refresh with V <sub>TT_DDR</sub> power off               |                                                                     |  |

|                |                   |        |            |          | V <sub>DDIO</sub> power on                                         |                                                                     |  |

| LP-Stop2 mode  | POWER_ON          | 0      | 0          | 0        | V <sub>DDCORE</sub> power on                                       | -                                                                   |  |

|                | (RUN)             | (UN)   |            |          | V <sub>DDCPU</sub> power off                                       |                                                                     |  |

AN5727 - Rev 1 page 20/65

| Operating<br>mode            | PMIC state        | PWR_ON | PWR_CPU_ON | NRSTC1MS | Description                                                       | Notes                                                                                           |

|------------------------------|-------------------|--------|------------|----------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|                              |                   |        |            |          | V <sub>DDGPU</sub> controlled by software                         |                                                                                                 |

|                              | 504/55 04/        | 0      | 0          | 0        | System clock on                                                   |                                                                                                 |

| LP-Stop2 mode                | POWER_ON<br>(RUN) |        |            |          | Peripherals power on/off                                          | -                                                                                               |

|                              |                   |        |            |          | DDR4 self-refresh with V <sub>TT_DDR</sub> power off              |                                                                                                 |

|                              |                   |        |            |          | V <sub>DDIO</sub> power on                                        |                                                                                                 |

|                              |                   |        |            |          | V <sub>DDCORE</sub> power on at lower voltage.                    |                                                                                                 |

|                              |                   |        |            |          | V <sub>DDCPU</sub> power on at nominal voltage                    |                                                                                                 |

| LPLV-Stop1 mode              | POWER_ON (RUN)    | 0      | 1          | 1        | V <sub>DDGPU</sub> controlled by software                         | -                                                                                               |

|                              | (11011)           |        |            |          | System clock off                                                  |                                                                                                 |

|                              |                   |        |            |          | Peripherals power on/off                                          |                                                                                                 |

|                              |                   |        |            |          | DDR4 self-refresh with V <sub>TT_DDR</sub> power off              |                                                                                                 |

|                              |                   |        |            |          | V <sub>DDIO</sub> power on                                        | In the application specified in Figure 1,                                                       |

|                              |                   |        |            |          | V <sub>DDCORE</sub> power on at lower voltage.                    | the MPU PWR_ON signal is internally muxed with the MPU PWR_LP signals so PWR_ON is low in:      |

|                              |                   |        |            |          | V <sub>DDCPU</sub> power off                                      | LPLV-Stop1 mode                                                                                 |

| LPLV-Stop2                   | POWER_ON          | 0      | 0          |          | V <sub>DDGPU</sub> power off                                      | <ul><li>LPLV-Stop2 mode</li><li>Standby mode.</li></ul>                                         |

| mode                         | (RUN)             |        | U          | 0        | System clock off                                                  | If this multiplexing does not occur, the                                                        |

|                              |                   |        |            |          | Peripherals power on/off                                          | PWR_ON signal is high in:                                                                       |

|                              |                   |        |            |          | DDR4 self-refresh with V <sub>TT_DDR</sub> power off              | <ul> <li>LPLV-Stop1 mode</li> <li>LPLV-Stop2 mode</li> <li>low only in Standby mode.</li> </ul> |

|                              |                   |        |            |          | V <sub>DDIO</sub> power on                                        |                                                                                                 |

|                              |                   |        |            |          | V <sub>DDCORE</sub> power off                                     |                                                                                                 |

| Standby                      |                   |        |            |          | V <sub>DDCPU</sub> power off                                      |                                                                                                 |

| (Standby mode (DDR4 in self- | POWER_ON          |        |            |          | V <sub>DDGPU</sub> power off                                      |                                                                                                 |

| refresh)                     | (Standby)         | 0      | 0          | 0        | System clock off                                                  | -                                                                                               |

| Standby mode (DDR4 OFF))     |                   |        |            |          | Peripheral power-<br>off                                          |                                                                                                 |

|                              |                   |        |            |          | DDR4 self-refresh<br>or off with V <sub>TT_DDR</sub><br>power off |                                                                                                 |

| V <sub>BAT</sub>             | NO_SUPPLY         | -      | -          | -        | Backup domain powered from backup battery                         | -                                                                                               |

| OFF                          | OFF               | -      | -          | -        | All regulators are powered off                                    | -                                                                                               |

AN5727 - Rev 1 page 21/65

| Operating<br>mode | PMIC state | PWR_ON | PWR_CPU_ON | NRSTC1MS | Description                                                   | Notes |

|-------------------|------------|--------|------------|----------|---------------------------------------------------------------|-------|

|                   |            |        |            |          | Backup domain<br>powered from<br>backup battery if<br>present |       |

<sup>1.</sup> In this application, the NRSTC1MS is linked to MPU PWR\_CPU\_ON by a pull-up. When the MPU PWR\_CPU\_ON is low, the NRSTC1MS is also low.

#### **5.1.1** Application turn-on/turn-off conditions

The STPMIC25 autonomously manages the power-up and the power-down sequence when respectively a turn-on or a turn-off condition occurs.

The STPMIC25APQR automatically powers up when the application is powered from a valid power source: When  $V_{IN}$  rises above the  $V_{INOK\_rise}$ , it triggers an STPMIC25 turn-on condition as the "AUTO turn-on" bit is set by default in the STPMIC25APQR NVM. The  $V_{INOK\_rise}$  is the STPMIC25 internal threshold (see [2] for the values).

#### **Turn-on conditions**

When the application is in OFF mode (STPMIC25 in the OFF state with  $V_{IN}$  present), a turn-on condition is required to power up the STPMIC25, and then to run the application. Similarly, if the application needs to go into power-off mode, a turn-off condition is required to power-down the STPMIC25.

If the STPMIC25 is in OFF state, it is powered up by one of three external triggers described in the the table below and two internal ones:

| Condition                                                        | Trigger  | Description                                                                                                                                                                                          |  |  |  |

|------------------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| AUTO turn-on                                                     | Internal | The STPMIC25APQR starts automatically when $V_{\text{IN}}$ rises above $V_{\text{INOK\_rise}}$ . This feature is set by default in the STPMIC25APQR. (see "AUTO turn-ON" section in [2] for details) |  |  |  |

| PONKEY user button                                               | External | PONKEYn pin voltage falling edge                                                                                                                                                                     |  |  |  |

| Wake-up events from the<br>STM32MP25x to STPMIC25<br>WAKEUPn pin | External | WAKE-UPn pin voltage falling edge                                                                                                                                                                    |  |  |  |

Table 6. STPMIC25 turn-on conditions

After a turn-on condition, the STPMIC25 carries out a transitional power-up sequence as describes in Section 5.2: Application Power-up/Power-down sequence.

#### **Turn-off conditions**

A turn-off condition leads the STPMIC25 to perform a power-down sequence to go into one of the following states:

- The OFF state

- The FAIL\_SAFE\_LOCK state (see [2] for the definition).

- Automatic restart (power cycle).

This depends on whether the source is a software switch-off or a hard fault that has triggered the turn-off condition (see detailed about hard fault is Section 6: Safety management). The turn-off conditions are described in the table below.

AN5727 - Rev 1 page 22/65

Note:

| Iablo | 7 Lurn | Off COL | nditions |

|-------|--------|---------|----------|

|       |        |         |          |

| Condition                     | Hard<br>fault | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Software switch OFF           | NO            | I²C commands "SWOFF" sent by the MPU to the STPMIC25                                                                                                                                                                                                                                                                                                                          |

| PONKEY user button long press | YES           | If the PONKEYn signal is low for 10 s, an application reset is triggered by the user and is treated by the STPMIC25 as a hard fault condition. For practical implementation reasons, the mechanism management for this condition is the same as for hard fault condition. The STPMIC25 triggers a turn-off condition. The STPMIC25 powers down then powers up. <sup>(1)</sup> |

| V <sub>INOK_fall</sub>        | YES           | If $V_{IN}$ falls below the $V_{INOK\_fall}$ threshold, the STPMIC25 triggers a turn-off hard-fault condition. The STPMIC25 powers down and waits for $V_{IN}$ to rise above the $V_{INOK\_rise}$ threshold again. At this point, the STPMIC25 powers up. <sup>(1)</sup>                                                                                                      |

| Thermal shutdown              | YES           | If the STPMIC25 overheating occurs, the STPMIC25 triggers a turn-off hard fault condition: The STPMIC25 powers down and waits for the temperature to decrease, then the STPMIC25 powers up once again. <sup>(1)</sup>                                                                                                                                                         |

| Overcurrent protection        | YES           | If an overcurrent or a short-circuit appears on predefined regulators (see Section 6: Safety management section), the STPMIC25 triggers a turn-off hard-fault condition. The STPMIC25 powers down then powers up. <sup>(1)</sup>                                                                                                                                              |

| Watchdog                      | YES           | If the software enables the watchdog, and the watchdog timer has elapsed, the STPMIC25 triggers a turn-off hard-fault condition. The STPMIC25 powers down then powers up. (1)                                                                                                                                                                                                 |

<sup>1.</sup> This is the default STPMIC25APQR behavior set in NVM (see [2] and Section 5.1.1: Application turn-on/turn-off conditions for details).

After a turn-off condition, the STPMIC25 carries out a transitional power down sequence, starting by asserting the RSTn (MPU NRST), then turning off the regulators in reverse sequence to the power-up state. Once the STPMIC25 ends the power-down sequence, it restarts, or it goes to OFF state or in FAIL\_SAFE\_LOCK state depending on the turn-off condition source and occurrence. See Section 6: Safety management for details

#### 5.1.2 STPMIC25APQR power control management (PWRCTRLx)

STPMIC25 PWRCTRLx signals are dedicated to managing MPU power modes or special regulator reset features. These signals must be correctly configured, and this before entering into low power mode, to ensure proper MPU low power mode entry and exit transitions.

The STPMIC25 PWRCTRLx signals are all independently controlled and each signal controls an STPMIC25 regulator by setting the appropriate registers as described in [2]. As such, it is possible to define:

- The control source selection of the regulator (PWRCTRL1/2/3)

- The polarity of the respective PWRCTRLx signals, which are used to define if the signals are active low or active high.

One of these power controls can be used to switch the STPMIC25 state machine from Run1 or Run2 (Run) to Standby mode and another one can be used to suspend the STPMIC25 watchdog (typically when the application is in low power mode).

An STPMIC25 PWRCTRL signal aims to switch between two regulator control registers xxxx\_MAIN\_CR and xxxx\_ALT\_CR.

Typically, when a PWRCTRL signal goes to a low state, the STPMIC25 internally switches from the main control register (MAIN) content to the alternate (ALT) control register content and vice versa.

#### STPMIC25APQR power control management for Standby mode

When the Standby mode is requested, the STPMIC25 state machine must switch to Standby to reach the minimum quiescent current consumption. For this operation, the STPMIC25 uses the PWRCTRL, which is dedicated to ensure the state machine transition from Standby to Run and vice versa. The STANBY PWRCTRL SEL[1:0] bit sets the PWRCTRL selection.

When the MPU runs in Standby mode, the consumption must be drastically reduced. The BUCK4 (V<sub>DDIO</sub>) must be set to low power mode (LP) instead of the high power mode (HP) (see [2] chapter 4.3.1 for details). When this feature is set to a BUCK step down regulator, its performance is reduced, meaning the accepted BUCK rated output current is lowered, and clock synchronization is internally disabled.

AN5727 - Rev 1 page 23/65

Else in other MPU low power modes, the BUCK step down regulator works in high power mode (HP mode). See [2] chapter 4.3.1 for details.

#### STPMIC25APQR power control management independent reset source

The PWRCTRL\_RST bit is used to enable the regulator independent reset source. When this bit is set, it behaves in either of the conditions below:

- If PWRCTRL is deassearted, the regulator operates according to xxxx MAIN CR.

- If PWRCTRL is asserted, the regulator is disabled and the xxxx\_MAIN\_CR and xxx\_ALT\_CR are reset to

the default value defined in the NVM. On PWRCTRL deassertion, the regulator operates according to

xxxx\_MAIN\_CR\_NVM reset content.

This feature is specifically suitable to reset application with flash memories in case of D1 crash (see Section 5.4: System and CPU1 crash recovery management). In this application, the regulator independent reset source is activated by the PWRCTRL3 (MPU NRSTC1MS) and mapped to:

- LDO2 (V<sub>DD EMMC</sub>)

- LDO7 (V<sub>DD</sub> SDCARD)

- LDO8 (V<sub>DDIO\_SDCARD</sub>)

#### 5.1.3 STPMIC25APQR mask-reset option

If the application needs to have one or several STPMIC25 regulators enabled while the STPMIC25 performs a reset sequence, the MPU bootloader software must program the STPMIC25 mask reset option by setting the STPMIC25 BUCK\_MRST\_CR register to target BUCK converters, and LDO\_MRST\_CR register to target LDOs. A reset sequence is triggered after the STPMIC25 RSTn signal asserted by the MPU or the user reset push button. Refer to [2] for details on the STPMIC25 mask-reset option.

This is typically the case for the BUCK4 powering the MPU  $V_{DDIO}$  power domains and the LDO1 powering the MPU  $V_{DDA1V8\_AON}$  power domain. The power cycle on  $V_{DDIO}$  and on  $V_{DDA1V8\_AON}$  must be masked by setting these two STPMIC25 registers:

- BUCKS MRST CR [3] = 1

- LDOS\_MRST\_CR [0] = 1

This prevents losing the content in:

- The MPU backup RAM

- The MPU retention RAM

- The MPU backup register content

- The JTAG debug interface (included in the OTP controller see Figure 2)

Note:

The MPU software bootloader must program these settings using the I<sup>2</sup>C command to the STPMIC25, following each application power-up. The content of the BUCKS\_MRST\_CR, and LDOS\_MRST\_CR are reset at the end of an STPMIC25 reset cycle.

#### 5.2 Application Power-up/Power-down sequence

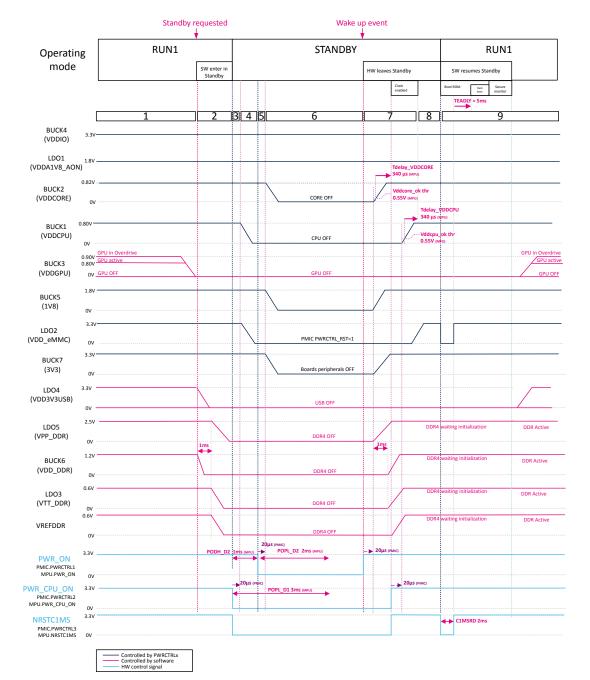

The power up sequence is the transition managed by the STPMIC25APQR between power-off and Run mode. The application power-up and power-down sequence shown in Figure 3 is based on the reference designed in Figure 1.

#### 5.2.1 Power-up triggered main supply (V<sub>IN</sub>) plugin/power-down by software shutdown

When the application is connected to an external power supply from a power-off state, the application starts automatically when  $V_{IN}$  rises above the  $V_{INOK\_rise}$  threshold. This assumes that the STPMIC25 has the AUTO\_TURN\_ON enabled by default in NVM settings.

When the STPMIC25 is powered-up, the PWRCTRLx signals have no effect (not initialized), the RSTn signal (MPU NRST signal) is released if no hard fault appears, then the application boots (including the DDR4 initialization). Finally, the system reaches Run mode and the MPU is operational.

When a turn-off condition occurs, the STPMIC25 powers down and goes into the OFF mode and the application goes into power-off mode. The whole process is detailed below and illustrated in Figure 3:

1. The application has no power or the MPU is powered by the onboard coin cell  $V_{BAT}$ . The  $V_{BAT}$  supplies the MPU backup domain.

AN5727 - Rev 1 page 24/65

- 2. A power supply is connected to the application. V<sub>IN</sub> voltage rises.

- 3. Once  $V_{IN}$  supply is above  $V_{INPOR\ Rise}$  (STPMIC25APQR  $V_{INPOR\ Rise}$  = 2.3 V typ.)

- a. The STPMIC25 preloads its NVM contents and checks its integrity.

- b. If the STPMIC25 NVM integrity is valid, the STPMIC25 initializes, and its states machine goes directly in CHECK&LOAD state as the AUTO\_TURN\_ON bit is set in the NVM. This is defined in the Turn-on conditions section.

- c. Once the STPMIC25 is initialized, it waits for a valid  $V_{IN}$  voltage to power up. This means waiting for  $V_{IN}$  to rise above the  $V_{INOK\ rise}$  threshold (STPMIC25APQR  $V_{INOK\ rise}$  = 4 V typ).

Note:

The STPMIC25 PRELOAD and CHECK&LOAD has a typical duration of approximately 6 ms.

- 4. Once the V<sub>IN</sub> supply rises above V<sub>INOK\_rise</sub>, the STPMIC25 starts a power-up sequence. The STPMIC25 regulators follow the power-up sequence described below:

- a. RANK1: The following voltage domains are enabled:

- V<sub>DDIO</sub> (BUCK4) to 3.3 V.

- V<sub>DDA1V8</sub> AON (LDO1) to 1.8 V.

A threshold is applied to these supplies that is based on the MPU internal power-on reset threshold (MPU POR). This is described in [3]. Once this threshold is reached the MPU PWR\_ON signal goes high, and the MPU enters in system reset. The MPU NRST signal is released at this time (following the  $T_{RSTTEMPO}$ = 500  $\mu$ s). But in the application, the STPMIC25 RSTn signal asserts the MPU NRST signal and takes the lead to control the MPU NRST signal.

- b. RANK2: The  $V_{DDCORE}$  (BUCK2) assigned to RANK2 is enabled at 0.82 V. An MPU threshold named Vddcore\_ok set to 660 mV allows the MPU to enable the MPU PWR\_CPU\_ON signal and the MPU NRSTC1MS signal. The MPU NRSTC1MS is linked to the MPU PWR\_CPU\_ON by a 10 k $\Omega$  pull-up resistor. The MPU waits for the HSI oscillators to be available. At this point, the STPMIC25 has reached RANK2 and a delay of 1.5 ms is applied.

- c. RANK3: The following power domains are enabled:

- V<sub>DDCPU</sub> (BUCK1) to 0.80 V.

- 1V8 (BUCK5) to 1.8 V.

An MPU threshold named Vddcpu\_ok set at 660 mV is applied on  $V_{DDCPU}$  (BUCK1), which allows the MPU to enter in hardware system initialization. At this point, the STPMIC25 has reached RANK3 and a delay of 1.5 ms is applied.

- d. RANK4: Enable both to 3.3 V:

- 3V3 (BUCK7)

- V<sub>DD EMMC</sub> (LDO2)

A delay of 1.5 ms is applied.

- e. RANK5: V<sub>DD3V3</sub> <sub>USB</sub> (LDO4) is enabled. A 1.5 ms delay is applied.

- f. When all regulators are ON, the STPMIC25 releases the RSTn signal linked to the MPU NRST signal.

- 5. As both the MPU and the STPMIC25 release their respective reset pins, then the MPU NRST signal rises:

- The NRSTC1MS here asserted by NRST, signal rises.

- b. The MPU EADLY timer starts. Refer to EADLY timer for more information.

- c. The boot ROM starts accessing the external flash memory peripherals (eMMC) when the EADLY timer elapses. The objective is to load, to check, and to execute the bootloader software.

- d. The software controls the V<sub>DDGPU</sub> (BUCK3), V<sub>DD\_SDCARD</sub> (LDO7), V<sub>DDIO\_SDCARD</sub> (LDO8) regulators once the peripheral boots are completed.

AN5727 - Rev 1 page 25/65

- 6. The bootloader initializes the DDR then loads and executes the kernel:

- The bootloader controls any STPMIC25 regulator.

- b. The V<sub>PP DDR</sub> (LDO5) is enabled at 2.5 V.

- c. The software waits for 1 ms.

- d. The software enables the following once the delay has elapsed:

- i. V<sub>REF\_DDR</sub> (REFDDR)

- ii. V<sub>TT DDR</sub> (LDO3 in sink-source mode)

- iii. V<sub>DD DDR</sub> (BUCK6 at 1.2 V)

- e. The software waits for 1 ms.

- f. The MPU software initializes the DDR4 controller and DDR memory ICs.

- g. The bootloader loads the kernel into DDR4 and executes it. The kernel initializes.

- h. The system is now running.

- 7. When a shutdown request occurs, the software prepares to power-off properly:

- a. The software shuts down the DDR4 regulators in the following sequence:

- i. Disable in sequence:

- 1. V<sub>DD DDR</sub> (BUCK6)

- 2. V<sub>TT DDR</sub> (LDO3)

- 3. V<sub>REF DDR</sub> (REFDDR).

- ii. Then the software waits 1 ms.

- iii. Disable V<sub>PP DDR</sub> (LDO5).

- b. The DDR4 is off, and the MPU is ready to power down, once this sequence is done

- 8. The software sends the SWOFF set to 1 command to the STPMIC25 by I<sup>2</sup>C to trigger an STPMIC25 turn-off condition .

- 9. The STPMIC25 performs a power-down sequence:

- a. The STPMIC25 asserts the RSTn, asserting the MPU NRST signal.

- b. RANK0: The STPMIC25 disables the V<sub>DDGPU</sub> (BUCK3), V<sub>DD\_SDCARD</sub> (LDO7), and V<sub>DDIO\_SDCARD</sub> (LDO8) regulator that is not enabled at power-up.

The system then waits for 1.5 ms.

- c. RANK5: V<sub>DD3V3</sub> <sub>USB</sub> (LDO4) is disabled and waits for 1.5 ms.

- d. RANK4: The power domains are disabled:

- 3V3 (BUCK7).

- V<sub>DD</sub> EMMC (LDO2).

The system waits 1.5 ms.

- e. RANK3: The following power domains are disabled:

- V<sub>DDCPU</sub> (BUCK1)

- 1V8 (BUCK5).

The system then waits for 1.5 ms.

- f. Rank2: V<sub>DDCORE</sub> (BUCK2) is disabled, the system waits for 1.5 ms.

- Once the  $V_{\text{DDCORE}}$  voltage goes below an internal MPU threshold, the MPU PWR\_CPU\_ON signals go low

- g. RANK1: The following power domains are disabled:

- V<sub>DDIO</sub> (BUCK4)

- V<sub>DDA1V8</sub> AON (LDO1).

The system waits 1.5 ms once the  $V_{DDIO}$  or  $V_{DDA1V8\_AON}$  goes below the power-down reset threshold (PDR 1.63 V see [3] for details). The MPU enters in reset mode, the PWR \_ON and the PWR\_CPU\_ON I/Os go in high-Z pull-down.

10. The STPMIC25 is now in OFF mode: the application is powered off.

AN5727 - Rev 1 page 26/65

Turn-OFF condition MPU operating System HW system init Reset DDR DOR Ready CHECK PMIC Power-up Power-down NO-SUPPLY & LOAD Power-ON OFF operating mode ANK1 RANK2 RANK3 RANK4 RANK5 RST RST RANKO RANKS RANK4 RANK3 RANK2 RANK1 1 2 3 7 8 10 VIN\_POR\_Rise = 2.3V 5V\_VIN MPU PDR = 1.63V LDO1 (VDDA1V8\_AON) POR = 1.67V MPU BUCK2 (VDDCORE) BUCK3 (VDDGPU) BUCK7 (3V3) LDO2 (VDD\_eMMC) LDO7 (VDD\_SDCARD) LDO8 (VDDIO\_SDCARD) LDO4 (VDD3V3USB) LDO5 (VPP\_DDR) BUCK6 (VDD\_DDR) REFDDR (VREF\_DDR) LDO3 (VTT\_DDR) PWR\_CPU\_ON

PMIC.PWRCTRL2

MPU.PWR\_CPU\_ON

PWR\_ON

PMIC.PWRCTRL1

MPU.PWR\_ON 2 NRST PMIC.RSTn NRST released by PMIC NRST asserted by PMIC Controlled by PWRCTRLx

SW choice ontrolled by PWRCTRLx

Software choice

Controlled by software

HW control signal

Figure 3. Power up and power-down sequence of the MPU with PMIC

page 27/65

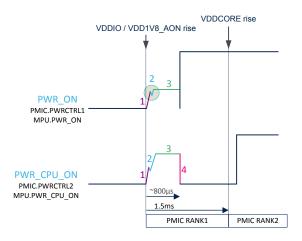

#### PWR\_ON and PWR\_CPU\_ON signals behavior during the power-up sequence

During the power-up sequence, the STPMIC25 PWRCTRL1/2 internal pull-up resistors, and the MPU PWR\_ON and the MPU PWR\_CPU\_ON internal pull-down resistors induce a particular artifact on the PWR\_ON and PWR\_CPU\_ON signals of the application. See Figure 4 for details.

This artifact has no impact on the system behavior as PWRCTRLx signals are only probed by STPMIC25 once the application software is initialized and the STPMIC25 PWRCTRLx signals are allocated to regulators.

Note:

The following sequence is to be read with the following figure. The numbers between brackets correspond to the number in the Figure 4

- 1. The STPMIC25 PWRCTRL1 and PWRCTRL2 internal pull-ups (80 k $\Omega$  typical) are active until the V<sub>DDIO</sub> and V<sub>DDA1V8</sub> AON start. (1)

- After few μs, the MPU.PWR\_ON/PWR\_CPU\_ON IOs are in high-Z and internal pull-down resistor (40 kΩ typical) is activated on both signals. A resistor divider is formed by the two 80 kΩ pull-up resistors in the STPMIC25 and 40 kΩ pull-down in the MPU. This resistor divider applies to the PWR\_ON and PWR\_CPU\_ON application signals respectively. Both voltages follow the V<sub>DDIO</sub> rising voltage driven by STPMIC25 PWRCTRLx pull-up resistors. (2)

- 3. During approximately 800 µs (time for the internal MPU initialization), the MPU internal pull-down and the STPMIC25 internal pull-up are still active, so the V<sub>DDIO</sub> voltage is divided by the resistor divider ratio. (3)

- 4. The MPU internal resistors on PWR\_ON and PWR\_CPU\_ON are deactivated and MPU PWR\_ON and PWR\_CPU\_ON pads are internally set in push-pull mode. PWR\_ON and PWR\_CPU\_ON signals are immediately driven by the MPU to the expected level: PWR\_ON goes high and PWR\_CPU\_ON is kept low until the VDDCORE raises. (4)

Note:

STPMIC25 PWRCTRLx pull-up resistors remain active and must be disabled by the bootloader software, after each the application powered-up to avoid extra power consumption in low power mode. This is when the PWR\_ON and/or PWR\_CPU\_ON level is low.

Figure 4. Application PWR\_ON and PWR\_CPU\_ON behavior during the power-up sequence

DT79903V1

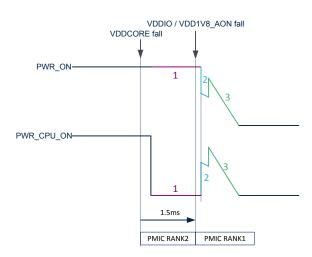

#### PWRCTRLs behavior during the power down sequence

During the power down sequence, the STPMIC25 PWRCTRL1/2 internal pull-up resistor and the MPU.PWR\_ON and MPU.PWR\_CPU\_ON internal pull-down resistors induce a particular artifact on the PWR\_ON and PWR\_CPU\_ON signals of the application. The whole process is illustrated in Figure 5.

Note:

This artifact has no impact on the system behavior as PWRCTRLx signals are not probed by STPMIC25 until the application software initializes and allocates the STPMIC25 PWRCTRLx signals to regulators.

The following sequence is to be read with the following figure. The numbers between brackets correspond to the number in Figure 5.

1. Once the V<sub>DDCORE</sub> voltage goes below vddcore\_ok thresholds, the MPU.PWR\_CPU\_ON is deactivated and the MPU.PWR ON remains active. MPU PWR ON and PWR CPU ON pads are kept in push-pull mode. (1)

AN5727 - Rev 1 page 28/65

- 2. Once  $V_{DDIO}$  and  $V_{DDA1V8\_AON}$  fall, the MPU.PWR\_ON/PWR\_CPU\_ON internal pull-down resistor (40 k $\Omega$  typ.) are activated and the STPMIC25.PWRCTRL1/PWRCTRL2 internal pull-up (80 k $\Omega$  typ) are still present. (2). A resistor divider is formed by the two 80 k $\Omega$  pull-up resistors in STPMIC25 and 40 k $\Omega$  pull-down in MPU and applies to the respective PWR\_ON and PWR\_CPU\_ON application signals. Both voltages follow  $V_{DDIO}$  falling voltage driven by STPMIC25 PWRCTRLx pull-up resistors.

- 3. In this state the STPMIC25 pull-up resistors are still present, but the MPU pull-down resistors are deactivated. Both PWR\_ON and PWR\_CPU\_ON voltages follow V<sub>DDIO</sub> falling voltage driven by STPMIC25 PWRCTRLx pull-up resistors. (3).

Figure 5. Application PWR\_ON and PWR\_CPU\_ON behavior during power down sequence

T79904V

### 5.2.2 Power-down triggered by STPMIC25APQR hard fault (safety management)

The following events trigger:

- A harmful overcurrent

- V<sub>IN</sub> fall

- An overtemperature

- A watchdog

- PONKEY long key press.

When the STPMIC25 detects a hard fault, it triggers a turn-off condition followed by a power-down sequence. Once the power-down sequence ends, the STPMIC25 can either restart (power up sequence) or it can go in FAIL\_SAFE\_LOCK state. The STPMIC25 safety management is detailed in Section 6: Safety management.

AN5727 - Rev 1 page 29/65

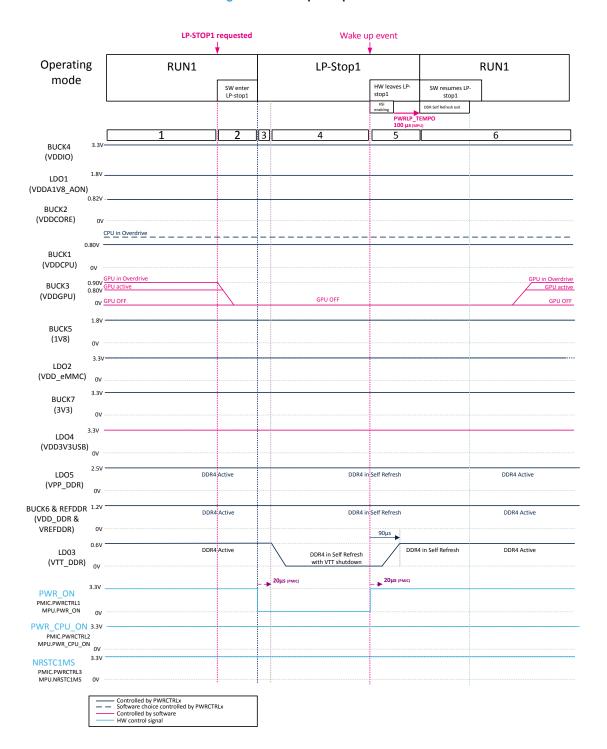

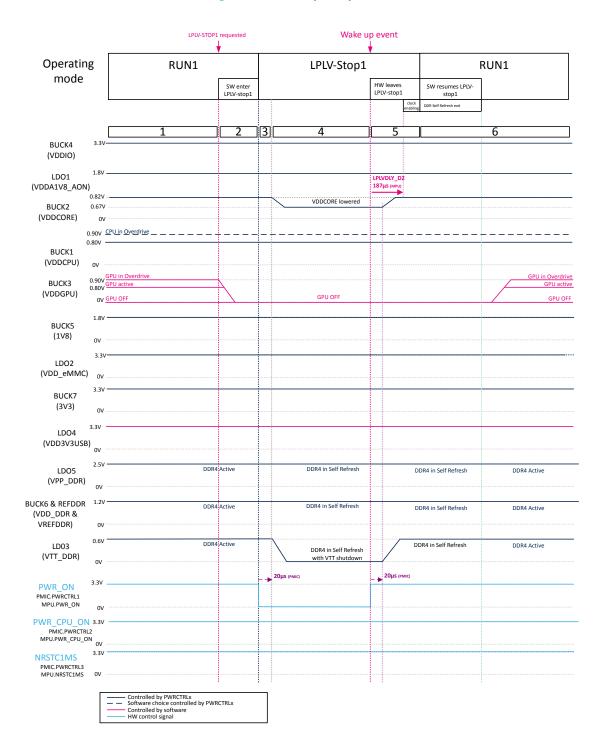

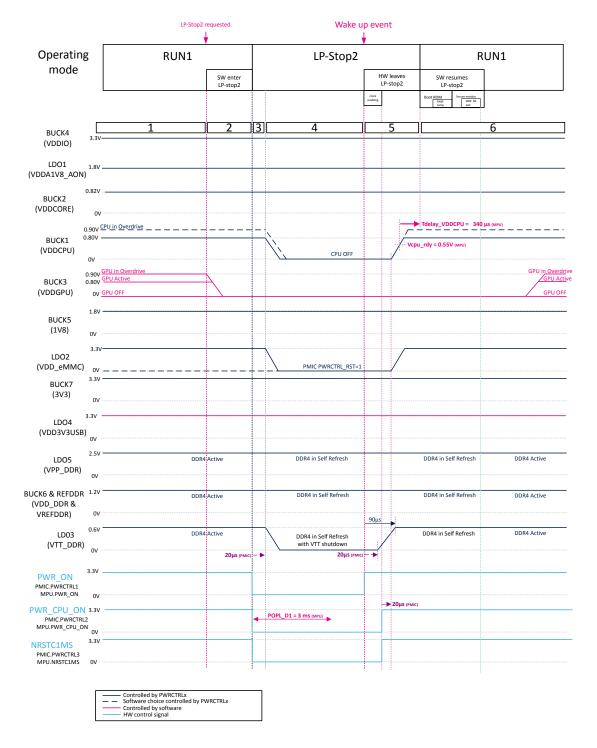

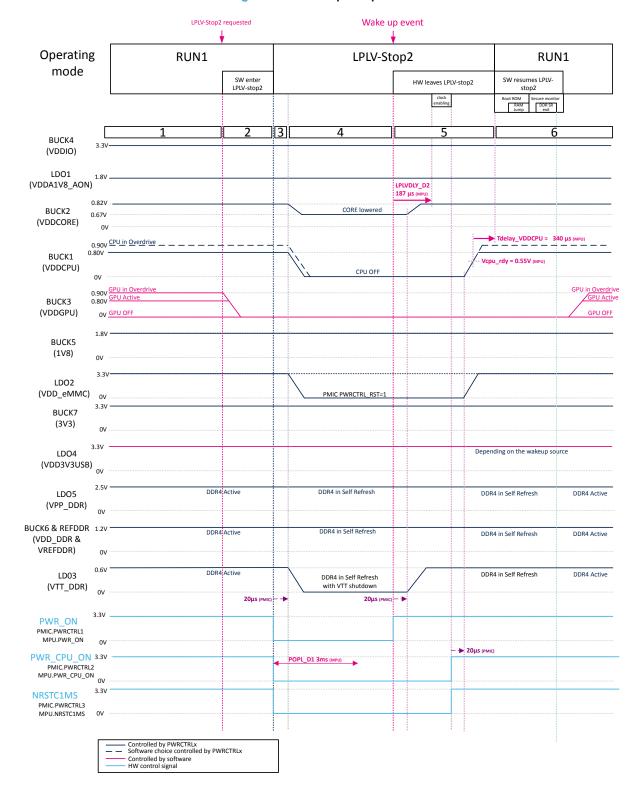

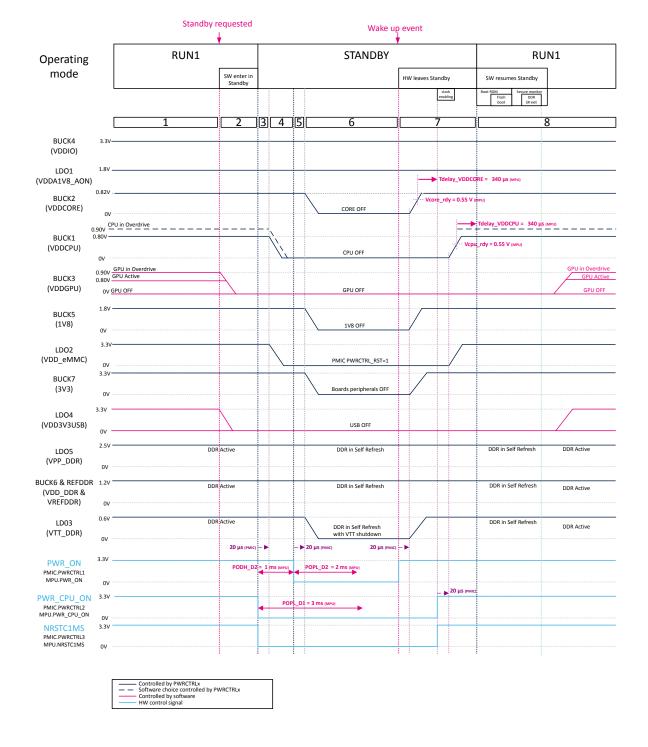

#### 5.3 Low power mode management