# L9678 Cut-off Battery and Pyro Fuse

### Introduction

This document explains the features and benefits of the L9678 device in order to be used in the Pyro Fuse application: the device activates the Pyro Fuse that disconnects a battery from an electrical system, so that the battery will not become a source of ignition.

The main features are the flexible configuration, availability of different voltage regulators, two PSI-5 sensor interfaces, four DC sensors interfaces, two GPOs, high or low level diagnostic test, arming procedure following both internal or external safing engine, deployment profile selectable, 32 bits SPI communication.

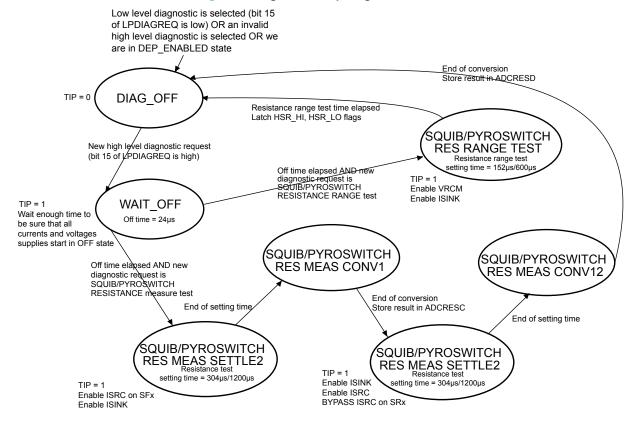

Note:

The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

# 1 Description

The L9678 IC is a system chip solution targeted for emerging market applications.

#### 1.1 Main features

The main features are:

- Energy reserve voltage power supply

- High frequency boost regulator, 1.875 MHz

- Output voltage user selectable, 23 V or 33 V ± 5%

- User configurable linear power supplies

- 5.0 V and 7.2 V ± 4% output voltages

- External pass transistor

- Fully integrated 3.3 V ± 4% linear regulator

- Battery voltage monitor and shutdown control with wake-up control

- System voltage diagnostics with integrated ADC

- Crossover switch

- Crossover performance, max 3 Ω, 250 mA max.

- Squib deployment drivers

- 4 channel HSD/LSD

- 25 V maximum deployment voltage

- 1.2 A @ 2 ms and 1.75 A @ 0.5/0.7 ms deployment profiles

- Integrated safing FET linear regulator, 20 V nominal

- Current monitoring

- Resistance measure, STB, STG and leakage diagnostics

- High and Low Side driver FET tests

- Safing FET test

- User customizable safing logic

- Two-channel PSI-5 remote sensor interface with SPI selectable switched/regulated output voltage (asynchronous mode)

- Four-channel hall-effect, resistive or switch sensor interface

- ISO9141 transceiver

- Dual channel configurable High-Side/Low-Side LED driver

- Watchdog timer

- Two integrated oscillators: 7.5/16 MHz

- COVRACT function to connect externally of IC VIN to reserve capacitor

- Temperature sensor

- 32 bits SPI communications

- Minimum operating voltage = 6 V

- Operating temperature, -40 °C to 95 °C

- Packaging: 64 pin

AN5739 - Rev 5 page 2/79

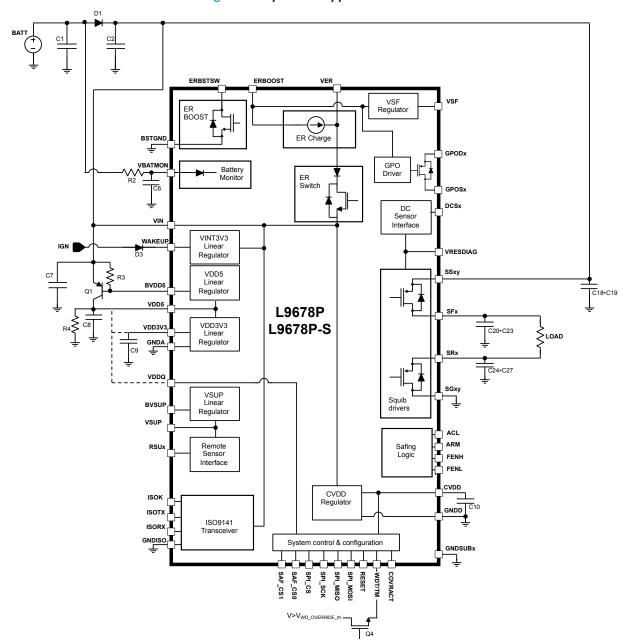

# 1.2 Application overview

The device has been designed for Airbag Application, but if correctly configured it can be used also for Pyro Fuse Application, i.e. to cut-off the battery from an electrical system.

In fact, in case of a crash, a short circuit on the battery due to damaged cables can lead to sparks and dangerous ignition or heat and moldering fires. Thus it is important to disconnect the electrical system from the battery using pyrotechnical safety battery terminals.

These special Pyro Fuses have electrical characteristics like those of Airbag detonators. Some Pyro Fuses can require a bigger current to be triggered. In this case some deployment channels can be shorted and connected to the same load in order to obtain a total current higher than 2 A.

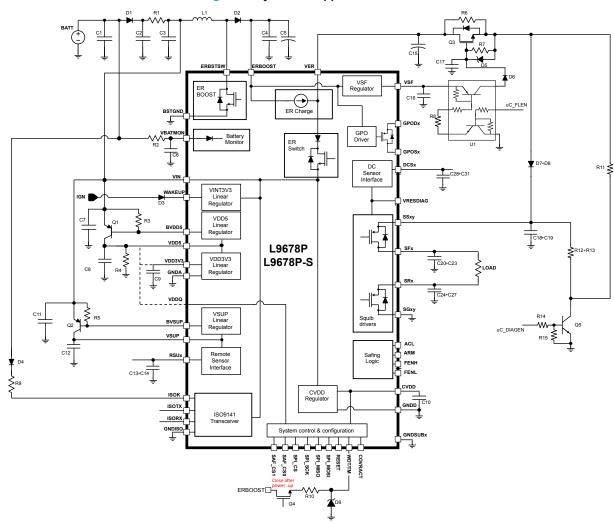

Figure 1. Pyro Fuse application circuit

AN5739 - Rev 5 page 3/79

# 2 Device configuration

The user shall configure the device following the Application Note AN4437, in particular about:

- Voltage Regulators

- Safing Logic

- Deployment

- Remote Sensor Interface (L9678-S only)

- DC Sensor Interface

- GPO Drivers

Furthermore, the user could use the same document to know about:

- ISO9141 Transceiver

- System Voltage Diagnostic

- Temperature Sensor

In the following section a deployment example will be shown.

### 2.1 Unused functions

In case some functions are not used, the correspondent pins have to be managed as in the Table 1.

Table 1. Unused functions management

| Pin                        | Action                                |  |  |  |  |

|----------------------------|---------------------------------------|--|--|--|--|

| RSU0, RSU1                 | Open (by default they are off)        |  |  |  |  |

| DCS0, DCS1, DCS2, DSCS3    | Open (weak pull-down integrated)      |  |  |  |  |

| GPOD0, GPOS0, GPOD1, GPOS1 | Open (by default they are off)        |  |  |  |  |

| ISOTX                      | Connect to VDDQ                       |  |  |  |  |

| ISOK, ISORX                | Open                                  |  |  |  |  |

| VSUP                       | Open (not to be enabled by SPI)       |  |  |  |  |

| BVSUP                      | Open (not to be enabled by SPI)       |  |  |  |  |

| SAF_CS0, SAF_CS1           | Connect to VDDQ (they are active low) |  |  |  |  |

| ACL                        | Connect to GND                        |  |  |  |  |

AN5739 - Rev 5 page 4/79

# 3 Deployment

#### Features:

- 4 independent loops composed by 4 independent High Side and 4 independent Low Side.

- All 4 squibs, connected to the same load, can deploy at the same time.

- Deployment granted in case of short to ground of the Low Side SRx.

- Firing voltage capability across SSxy and SFi is maximum 25 V.

- Max resistance of High Side and Low Side FETs is 10 Ω.

- Each loop can sustain 50 deployment min, waiting at least 10s between each of them.

- 2 supply pins, SS01 and SS23, directly connected to the High Side for each channel.

- 2 dedicated power ground, SG01 and SG23, each of them able to sustain the current of two channels simultaneously.

- SGxy is connected to GNDSUB through a diode so that the device is able to fire in case of SGxy lost.

### 3.1 Deployment requirement

Deployment features are deployment current, deployment time and deployment expiration time. The deployment expiration time is the duration time in which the deploy command remains valid, once it is received, waiting for the arming signal.

These parameters are defined in the DCR x registers, one per each channel.

Here are explained the commands to configure the IC deployment.

Deployment configuration is done through the four registers DCR\_x, with x=0-3, configurable in the DIAG, SAFING, SCRAP, and ARMING state, as shown in the Table 2:

- \$06 DCR 0 → channel 0

- \$07 DCR 1 → channel 1

- \$08 DCR 2 → channel 2

- \$09 DCR 3 → channel 3

All deployment configuration registers are reset by SSM reset.

(1) (2) 19:16 15:8 7:6 5:4 3:2 1:0 Deploy\_time \$06 DCR 0 Deploy current Deploy\_expire\_time 00 = 500 ms 00 = no deploy \$07 DCR 1 00, 11 = not used01 = 250 msW Χ 01 = 0.5 msΧ (I) \$08 DCR 2 01 = 1.75 A min 10 = 125 ms10 = 0.7 ms\$09 DCR\_3 10 =1.2 A min 11 = 0 ms11 = 2 ms

Table 2. DCR x register

The DWELL time is defined in SAFING configuration: it is the period of time in which the ARMING signal, once asserted, is valid waiting for a deployment command.

DEPLOY EXPIRE TIME is defined in deployment configuration: it is the period of time in which the deployment command, once received, is valid waiting for the ARMING signal asserted.

The combination  $1.75 \, \text{A/2} \, \text{ms}$  is <u>not</u> allowed. If this case should happen, the IC changes the set-up into 1.2 A/500 µs and flags the bit CHxDD in the DSR\_x register (Deployment Status Register), one per each channel, as shown in the Table 3:

- \$13 DSR\_0 register → channel 0

- \$14 DSR 1 register → channel 1

- \$15 DSR 2 register → channel 2

- \$16 DSR\_3 register → channel 3

AN5739 - Rev 5 page 5/79

<sup>1.</sup> I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, - = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

<sup>2.</sup> R = READ, W = WRITE

|            | (1) | (2) | 19:16 | 15                                           | 14                                                 | 13 | 12                              | 11:6 | 5:0              |

|------------|-----|-----|-------|----------------------------------------------|----------------------------------------------------|----|---------------------------------|------|------------------|

| \$13 DSR_0 |     |     |       | CLINDOV                                      | CULCTAT                                            |    | DCRxERR                         |      |                  |

| \$14 DSR_1 |     | R   | 0     | CHxDSX 0 depl not succesful 1 depl succesful | CHxSTAT  0 depl not in progress 1 depl in progress | 0  | 0 depl conf accepted and stored | 0    | DEP_CHx_EXP_TIME |

| \$15 DSR_2 |     |     |       |                                              |                                                    |    | 1 depl conf change not accepted |      | 8 ms/count       |

| \$16 DSR 3 |     |     |       |                                              |                                                    |    | because deploy is in progress   |      |                  |

Table 3. DSR x register

- 1. I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

- 2. R = READ, W = WRITE

In order to perform deployment, all the deploy configurations registers (DCR\_x registers) have to be accessed, also if the default values have just to be confirmed. In the opposite case the IC inhibits deployment, setting DRCxERR bit in the DSR x register to 1, as shown in the Table 3.

For each channel, the deploy requires:

- High Side and Low Side enabling.

- High Side and Low Side switching.

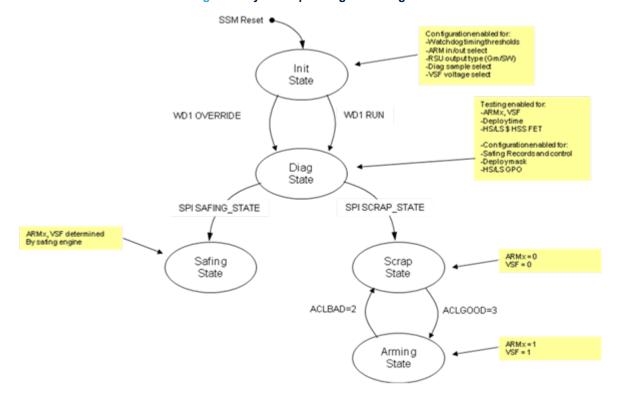

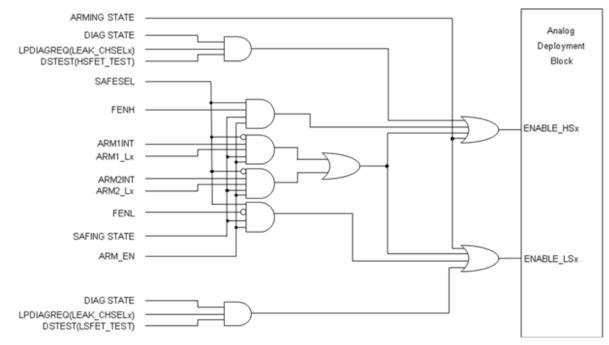

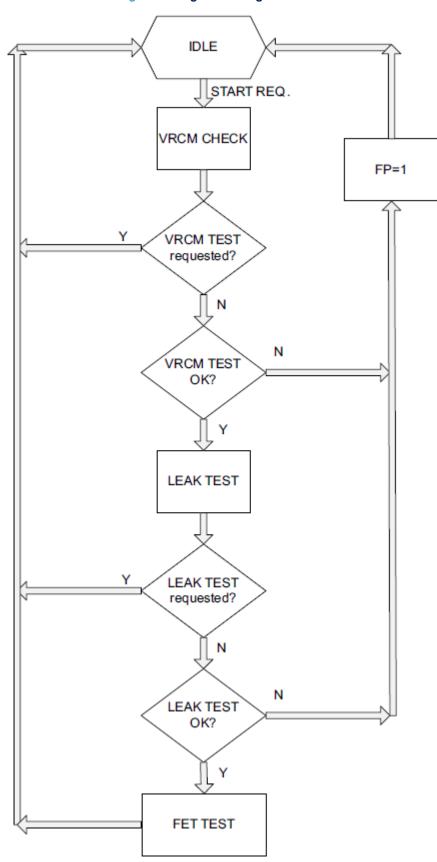

The Figure 2 and Figure 3 show the states of the IC and the signal paths which enable the High Side and Low Side MOSFETs.

Figure 2. System operating state diagram

AN5739 - Rev 5 page 6/79

Figure 3. High Side and Low Side squib enable

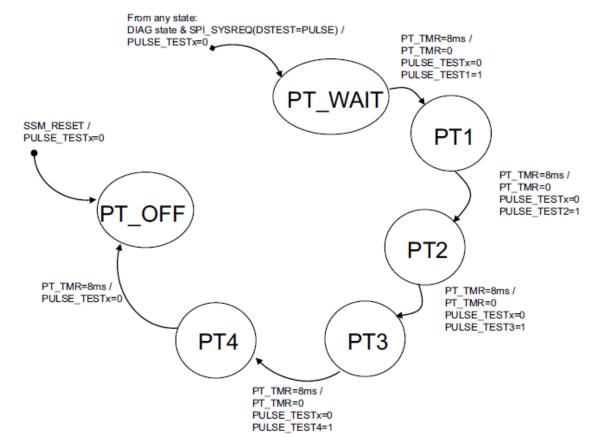

# 3.1.1 Diagnostic state

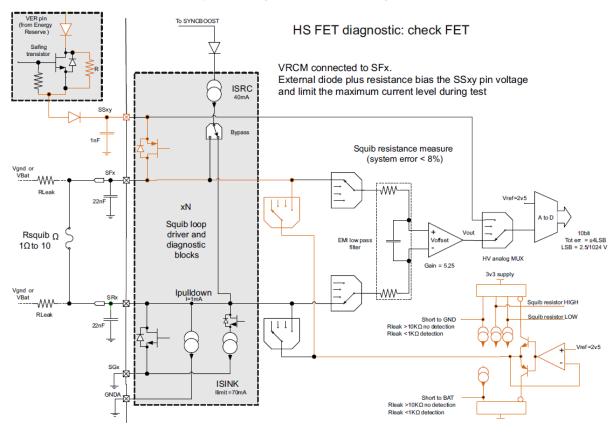

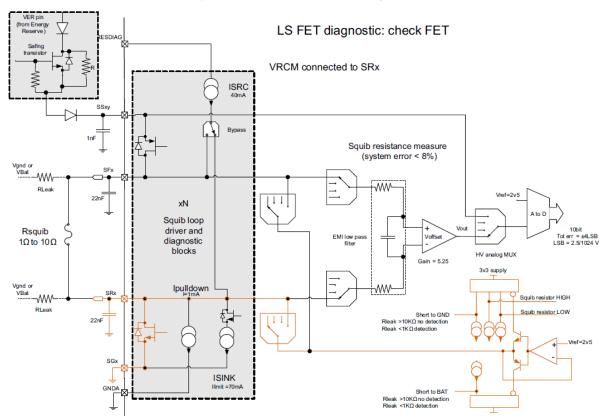

In DIAGNOSTIC state it is possible to perform the High Side FET test and Low Side FET test.

These tests require a sequence of steps:

- 1. Select the channel (refer to the Table 4);

- 2. Select High Side FET test or Low Side FET test (refer to the Table 5).

Table 4. LPDIAGREQ register - LEAK\_CHSEL bits

| \$38 LPDIAGREQ       | Config in DIAG, SAFING, SCRAP, ARMING state |

|----------------------|---------------------------------------------|

| LEAK_CHSEL, bit[3:0] | 0000 = CHANNEL 0                            |

|                      | 0001 = CHANNEL 1                            |

|                      | 0010 = CHANNEL 2                            |

|                      | 0011 = CHANNEL 3                            |

Table 5. SYSDIAGREQ register - DSTEST bits

| \$36 SYSDIAGREQ  | Config in DIAG state             |  |  |

|------------------|----------------------------------|--|--|

| DSTEST, bit[3:0] | 0111 = High Side FET test active |  |  |

| 7 7 4 1          | 1000 = Low Side FET test active  |  |  |

AN5739 - Rev 5 page 7/79

#### 3.1.2 Safing state

If WD\_LOCKOUT is not set (that is ARM\_EN = 1 in the Figure 3), High Side and Low Side enables depend on the safing engine machine, internal or external, according to SAFESEL bit (see the Table 6).

Table 6. SYS CSF register - SAFESEL bit

| \$01 SYS_CFG    | Config in INIT state                                               |

|-----------------|--------------------------------------------------------------------|

| SAFESEL, bit[3] | 0 = internal safing engine<br>1 = external safing engine (default) |

If the external safing engine is chosen (SAFESEL = 1), the signals to be considered are:

- FENH that is active high.

- FENL that is active low.

The two signals FENH and FENL directly drive the output. So, if their status changes during a deployment, passing from their active state to their inactive state, the deployment is immediately interrupted.

If the **internal safing engine** is chosen (SAFESEL = 0), FENH and FENL are ignored. In this case it is recommended keeping FENH and FENL in their inactive status (FENH low, FENL high) to prevent that, in case of safing internal engine fault, the arming signal is set. The signals to be considered are ARM1INT, ARM2INT, ARM1\_Lx, ARM2\_Lx.

The internal arming signals (ARM1INT, ARM2INT) drive, at the same time, the High Side and the Low Side. Instead, the external arming signals (FENH, FENL) drive the High Side and the Low Side separately.

ARM1\_Lx and ARM2\_Lx signals are used to link the ARM signals to the deployment loop through \$6E LOOP\_MATRIX\_ARM1 and \$6F LOOP\_MATRIX\_ARM2 registers, as shown in the Table 7.

Table 7. LOOP\_MATRIX\_ARMx registers

| \$6E LOOP_MATRIX_ARM1<br>\$6F LOOP_MATRIX_ARM2 | Config in DIAG state                                               |  |  |

|------------------------------------------------|--------------------------------------------------------------------|--|--|

| ARMx_L3 bit[3]                                 | 0 = ARMx not associated to loop 3 1 = ARMx associated to loop 3    |  |  |

| ARMx_L2 bit [2]                                | 0 = ARMx not associated to loop 2 1 = ARMx associated to loop 2    |  |  |

| ARMx_L1 bit[1]                                 | 0 = ARMx not associated to loop 1 1 = ARMx associated to loop 1    |  |  |

| ARMx_L0 bit[0]                                 | 0 = ARMx not associated to loop 0<br>1 = ARMx associated to loop 0 |  |  |

#### 3.1.3 Arming state

This state corresponds to the disposal of the vehicle. In this state the High Side and Low Side are enabled.

AN5739 - Rev 5 page 8/79

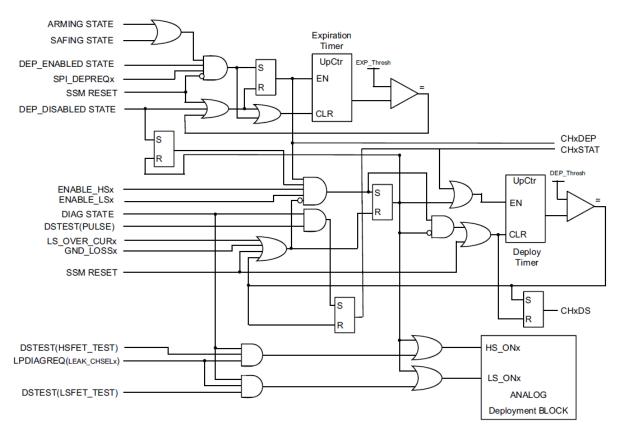

### 3.1.4 Deployment driver

Figure 4. Deployment driver control logic

List of the requirements to deploy:

- 1. High Side and Low Side are enabled (ENABLE\_HS & ENABLE\_LS = 1).

- 2. No problem on SSM reset, i.e. internal voltage references are at their correct value (POR = 0), VDD5 and VDD3V3 voltage regulators at their correct value too (WSM\_reset = 0) and WD asserted or overridden (SSM\_reset = 0).

- 3. Device in the ARMING or SAFING state.

- 4. The deployment request is sent writing CHxDEPREQx bits in the DEPCOM register (refer to the Table 8)

- 5. The unlock command is sent writing DEPEN\_WR bits in the SPIDEPEN register (refer to the Table 9).

Table 8. DEPCOM register - CHxDEPREG bit

| \$12 DEPCOM       | Config in SAFING and ARMING state                                                |

|-------------------|----------------------------------------------------------------------------------|

| CHxDEPREG, bit[x] | 0 = no change to deployment control channel x                                    |

|                   | 1 = clear and start the expiration timer in ARMING, SAFING and DEP_ENABLED state |

Table 9. SPIDEPEN register

| \$25 SPIDEPEN       | Config in SAFING and ARMING state                                                  |

|---------------------|------------------------------------------------------------------------------------|

| DEPEN_WR, bit[15:0] | 0x0FF0 = LOCK enter deploy disable state 0xF00F = UNLOCK enter deploy enable state |

|                     |                                                                                    |

As the SSM\_Reset is released, to perform the deployment the microcontroller has to write the UNLOCK code (0xF00F) in the DEPEN\_WR bits of the SPIDEPEN register.

AN5739 - Rev 5 page 9/79

After a deploy, the next deployment requires a toggle LOCK (0x0FF0) - UNLOCK (0xF00F). The same is necessary in case of a multiple deployment request, as shown in the Figure 5.

SPI\_SPIDEPEN(DEPEN\_WR)

UNLOCK

DEP\_ENABLED

SPI\_SPIDEPEN(DEPEN\_WR)

LOCK

Figure 5. Deployment Enable/Disable

Once the 5 points above are satisfied, the Expiration Time Counter starts.

This counter considers the feature of the IC to accept a deploy command even if the arming is not yet serviced. If the arm command occurs inside the expiration time, the deployment takes place otherwise the deployment command is discharged.

Dep\_exp\_time is defined in the DCR\_x registers, together with the Deploy\_timer and Dep\_current.

Once the deployment is started, any DEP\_EN = 0x0FF0 (i.e., deploy disable) is ignored. If the same command arrives before the deployment has been started, the deployment is really disabled and the deploy command ignored.

Once the deployment is started, it can be interrupted by:

- Over-current in the Low Side.

- GND loss.

- SSM reset.

- End of deployment time.

The status of the deployment is reported in the DSR\_x registers:

- \$13 DSR\_0 register → channel 0

- \$14 DSR\_1 register → channel 1

- \$15 DSR\_2 register → channel 2

- \$16 DSR\_3 register → channel 3

Two bits are available (see the Table 3):

- CHxSTAT bit reports if the deployment is in progress or not.

- CHxDS bit reports if the deployment lasts for the programmed deploy time (deploy success).

The event is also reported in the GSW field (see the Table 10), DEPOK bit, that is the "OR" of the deployment success of all the four channels (see the Table 11).

Table 10. Global Status Word (GSW)

| MISO bit | 31     | 30    | 29    | 28       | 27      | 26       | 25  | 24       | 23       | 22      | 21      |

|----------|--------|-------|-------|----------|---------|----------|-----|----------|----------|---------|---------|

| MISO     | SPIFLT | DEPOK | RSFLT | WDTDIS_S | ERSTATE | POWERFLT | FLT | CONVRDY2 | CONVRDY1 | ERR_WID | ERR_RID |

| GSW bit  | 10     | 9     | 8     | 7        | 6       | 5        | 4   | 3        | 2        | 1       | 0       |

AN5739 - Rev 5 page 10/79

#### Table 11. DEPOK bit in GSW

| GSW | MISO b[30] DEPOK = GSW b[9]                                                        |

|-----|------------------------------------------------------------------------------------|

|     | 0 = all DSR_x/CHxDS bits are equal to zero (no deployment success on all channels) |

|     | 1 = at least a deployment successful on the channels                               |

In case DEPOK = 1, this does not mean that the current is really passed through the squib for the programmed time. This bit means only that no inhibition of deployment has been received (in external safing engine FENH/FENL could have disabled the High Side or the Low Side).

#### 3.2 Deployment driver protection

In order to avoid damaging the IC due to eventual free-wheeling, two protections are implemented:

- After a deployment, once the High Side is switched off, the Low Side is kept on for t<sub>DEL\_SD\_LS</sub> (50 μs min.) in order to allow fly-back.

- Once Low Side is switched off, a protection against the overvoltage through a clamp structure is implemented.

On the Low Side there is a current limitation and overcurrent protection circuit that attends limiting the current at  $I_{LIM\_SR}$  (2.2 A ÷ 4 A) and  $I_{OC\_SR}$  (2.2 A ÷ 4 A) respectively, avoiding, in case of pin short to battery, any damage. If the malfunction lasts over  $t_{FLT\_ILIM\_LS}$  (100  $\mu$ s typ), the whole channel (High and Low Side) is switched off until a new deployment command (via SPI\_DEPEN register) occurs.

The squib driver can stand the short to ground of the pins during the deployment, because the High Side current is limited by the High Side itself.

It can also manage the case of SRx short to ground after an open circuit, because it is able to detect the open circuit condition and then limiting the current overshoot as the open circuit disappears.

In case of squib's intermittence during deployment phase, current limitation is ensured by the Low Side current limitation,  $I_{LIM\_SR}$ . If the condition lasts longer than  $t_{FLT\_OS\_LS}$  (20  $\mu s$  max), the High Side is switched off for  $t_{OFF\_OS\_HS}$  (4  $\mu s$  ÷ 12  $\mu s$ ) and then on again.

This allows distinguish Open Load and Low Side short to battery cases and then properly manage them.

#### 3.3 Deployment driver examples

Since the external safing engine is used (SAFESEL = 1), the FENH pin is connected to 5 V (high level) and the FENL pin is connected to ground (low level).

In low-cost applications the external Safing FET could be removed. In this case the application has a lower Safety level. To be sure not to damage the High Side MOSFETs it is suggested to set the ERBOOST and the ER cap charging voltage to 24 V.

AN5739 - Rev 5 page 11/79

### 3.3.1 With Watchdog Service routine disabled

The Table 12 reports a simple example showing the minimum SPI frames needed to configure the device and enable the deployment on all the channels when the Watchdog Service routine is disabled.

If the Watchdog function is useless, it can be disabled in two steps:

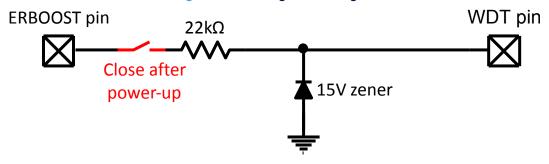

- 1. After power-up, pull the WDT pin to a voltage higher than 14 V ( $V_{WD\_OVERRIDE\_th}$ ), for example as in the Figure 6.

- 2. Write the frame 0x3C00 in the \$35 WD1 Test Command register.

Figure 6. Watchdog override signal

Table 12. Deployment SPI sequence without Watchdog routine

| Register        | State | R/W | Data   | Notes                                         |

|-----------------|-------|-----|--------|-----------------------------------------------|

|                 |       |     |        | Bit 15: 0 = Auto switch off disabled          |

|                 |       |     |        | Bit 14: 0 = OV/UV generate reset              |

|                 |       |     |        | Bit 13: X = Don't care                        |

|                 |       |     |        | Bit 12: 0 = ER Boost is disabled in ER state  |

|                 |       |     |        | Bit 11: X = Don't care                        |

|                 |       |     |        | Bit 10: 0 = Short time                        |

| \$01 SYS_CFG    | Init  | W   | 0x000D | Bit 9: X = Don't care                         |

|                 |       |     |        | Bits 8-7: 00 = 8 sample DC-squib-temp measure |

|                 |       |     |        | Bits 6-5: 00 = 4 sample other measure         |

|                 |       |     |        | Bit 3: 1 = external safing engine             |

|                 |       |     |        | Bit 2: 1 = VSF set to 25 V                    |

|                 |       |     |        | Bit 1: X = Don't care                         |

|                 |       |     |        | Bit 0: 1 = timeout disable                    |

| POA CVC CTATE   | Init  | Б   | -      | Bits 10÷8000 = INIT                           |

| \$04 SYS_STATE  | Init  | R   |        | Bits 2÷0: 010 = RUN                           |

| \$35 WD_TEST    | Init  | W   | 0x3C00 | Non-latched WD1 Test Command                  |

| 00.4.0\\0.0TATE |       | R   | -      | Bits 10÷8: 001 = DIAG                         |

| \$04 SYS_STATE  | Diag  |     |        | Bits 2÷0: 010 = RUN                           |

|                 |       |     |        | Bits 15÷13: X = Don't care                    |

|                 |       |     |        | Bit 12: 0 = VIN th set to 5.5 V               |

|                 |       |     |        | Bit 11÷10: 00 = VBATMON th set to 6 V         |

|                 |       |     |        | Bit 9: 1 = ER Boost set to 33 V               |

| \$02 SYS_CTL    | Diag  | W   | 0x02E0 | Bit 8: X = Don't care                         |

|                 |       |     |        | Bit 7: 1 = ER Charge on                       |

|                 |       |     |        | Bit 6: 1 = ER Boost On                        |

|                 |       |     |        | Bit 5: 1 = VSUP On                            |

|                 |       |     |        | Bit 4: 0 = no POWER OFF from SHUTDOWN         |

AN5739 - Rev 5 page 12/79

| Register State R/W Da |       |   | Data   | Notes                                        |

|-----------------------|-------|---|--------|----------------------------------------------|

| <b>g</b>              |       |   |        | Bits 3÷0: X = Don't care                     |

|                       |       |   |        | Bit 19: 1 = WAKEUP>WU on                     |

|                       |       |   |        | Bit 18: 0 = VBATMON > VBBAD                  |

|                       |       |   |        | Bit 17: 0 = VBATMON>VBGOOD                   |

|                       |       |   |        | Bit 16: 0 = VIN > VINBAD                     |

|                       |       |   |        | Bit 15: 0 = VIN > VINGOOD                    |

|                       |       |   |        | Bit 14: 0 = VDD3V3 > VDD3V3_UV               |

|                       |       |   |        | Bit 13: 0 = VDD3V3 < VDD3V3_OV               |

|                       |       |   |        | Bit 12: 0 = V_ERBOOST > ERBOOST_OK           |

| AGE BOWER OTATE       | D:    |   |        | Bit 11: 0 = VDD5 > VDD5_UV                   |

| \$05 POWER STATE      | Diag  | R | -      | Bit 10: 0 = VDD5 < VDD5_OV                   |

|                       |       |   |        | Bit 9: 0 = VSUP > VSUP_OK                    |

|                       |       |   |        | Bit 8: 1 = ER Boost on                       |

|                       |       |   |        | Bit 7: 1 = ER Charge on                      |

|                       |       |   |        | Bit 4: 0 = ER Switch off                     |

|                       |       |   |        | Bit 3: 1 = VDD5 ramp up or on                |

|                       |       |   |        | Bit 2: 1 = VSUP ramp up or on                |

|                       |       |   |        | Bit 1: 1 = VDD3V3 on                         |

|                       |       |   |        | Bit 0: 0 = VSF_EN off                        |

| \$00 FLTSR            | Diag  | R | -      | Verify there are not faults                  |

| AOE LOOP MATRIX ARMA  | D.    | W | 0x000F | Bits 15÷4: X = Don't care                    |

| \$6E LOOP_MATRIX_ARM1 | Diag  |   |        | Bits 3÷0: ARM1 assigned to 0÷3 loops         |

|                       |       |   |        | Bits 15÷8: X = Don't care                    |

|                       |       |   |        | Bits 7÷6: 01 = 0.5 ms deploy time            |

| \$06 DCR_0            | Diag  | W | 0x0050 | Bits 5÷4: 01 = 1.75 A deploy current         |

|                       |       |   |        | Bits 3÷2: 00 = 500 ms deploy expiration time |

|                       |       |   |        | Bits 1÷0: X = Don't care                     |

|                       |       |   |        | Bits 15÷8: X = Don't care                    |

|                       | Diag  | W | 0x0050 | Bits 7÷6: 01 = 0.5 ms deploy time            |

| \$07 DCR_1            |       |   |        | Bits 5÷4: 01 = 1.75 A deploy current         |

|                       |       |   |        | Bits 3÷2: 00 = 500 ms deploy expiration time |

|                       |       |   |        | Bits 1÷0: X = Don't care                     |

|                       |       |   |        | Bits 15÷8: X = Don't care                    |

|                       |       |   |        | Bits 7÷6: 01 = 0.5 ms deploy time            |

| \$08 DCR_2            | Diag  | W | 0x0050 | Bits 5÷4: 01 = 1.75 A deploy current         |

|                       |       |   |        | Bits 3÷2: 00 = 500 ms deploy expiration time |

|                       |       |   |        | Bits 1÷0: X = Don't care                     |

|                       |       |   |        | Bits 15÷8: X = Don't care                    |

|                       |       | W | 0x0050 | Bits 7÷6: 01 = 0.5 ms deploy time            |

| \$09 DCR_3            | Diag  |   |        | Bits 5÷4: 01 = 1.75 A deploy current         |

|                       |       |   |        | Bits 3÷2: 00 = 500 ms deploy expiration time |

|                       |       |   |        | Bits 1÷0: X = Don't care                     |

| ¢42 DCD - 0           | Dia - | Б |        | Bit 15: 0 = deployment successful            |

| \$13 DSR_0            | Diag  | R | _      | Bit 14: 0 = deployment not in progress       |

AN5739 - Rev 5 page 13/79

| Register          | State | R/W | Data   | Notes                                                           |

|-------------------|-------|-----|--------|-----------------------------------------------------------------|

|                   |       |     |        | Bits 13: 0 = correct time/current combination                   |

|                   |       |     |        | Bits 12: 0 = deployment configuration accepted                  |

|                   |       |     |        | Bits 5÷0: deployment expiration timer value                     |

|                   |       |     |        | Bit 15: 0 = deployment successful                               |

|                   |       |     |        | Bit 14: 0 = deployment not in progress                          |

| \$14 DSR_1        | Diag  | R   | -      | Bits 13: 0 = correct time/current combination                   |

|                   |       |     |        | Bits 12: 0 = deployment configuration accepted                  |

|                   |       |     |        | Bits 5÷0: deployment expiration timer value                     |

|                   |       |     |        | Bit 15: = deployment successful                                 |

|                   |       |     |        | Bit 14: 0 = deployment not in progress                          |

| \$15 DSR_2        | Diag  | R   | -      | Bits 13: 0 = correct time/current combination                   |

|                   |       |     |        | Bits 12: 0 = deployment configuration accepted                  |

|                   |       |     |        | Bits 5÷0: deployment expiration timer value                     |

|                   |       |     |        | Bit 15: 0 = deployment successful                               |

|                   | Diag  | R   |        | Bit 14: 0 = deployment not in progress                          |

| \$16 DSR_3        |       |     | -      | Bits 13: 0 = correct time/current combination                   |

|                   |       |     |        | Bits 12: 0 = deployment configuration accepted                  |

|                   |       |     |        | Bits 5÷0: deployment expiration timer value                     |

| \$31 SAFING_STATE | Diag  | W   | 0xACAC | Frame to pass from DIAG to SAFING                               |

| #04 0\/O OTATE    |       | _   |        | Bits 10÷8: 010 = SAFING                                         |

| \$04 SYS_STATE    | S     | R   | -      | Bits 2÷0: 010 = RUN                                             |

| \$25 SPIDEPEN     | S, A  | W   | 0x0FF0 | Lock Code                                                       |

| \$25 SPIDEPEN     | S, A  | W   | 0xF00F | Unlock Code                                                     |

| \$12 DEPCOM       | S, A  | W   | 0x000F | Bits 3÷0: 1111 = send deploy requests for all the four channels |

| \$25 SPIDEPEN     | S, A  | W   | 0x0FF0 | Lock Code                                                       |

| \$13 DSR_0        | S, A  | R   | -      | Bit 15: 1 = deployment successful                               |

| \$14 DSR_1        | S, A  | R   | -      | Bit 15: 1 = deployment successful                               |

| \$15 DSR_2        | S, A  | R   | -      | Bit 15: 1 = deployment successful                               |

| \$16 DSR_3        | S, A  | R   | -      | Bit 15: 1 = deployment successful                               |

AN5739 - Rev 5 page 14/79

# 3.3.2 With Watchdog Service routine enabled

The Table 13 reports a simple example showing the minimum SPI frames needed to configure the device and enable the deployment on all the channels when the Watchdog Service routine is enabled.

Table 13. Deployment SPI sequence with Watchdog routine

| Register         | State | R/W | Data   | Notes                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|-------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| \$01 SYS_CFG     | Init  | W   | 0x000D | Bit 15: 0 = Auto switch off disabled  Bit 14: 0 = OV/UV generate reset  Bit 13: X = Don't care  Bit 12: 0 = ER Boost is disabled in ER state  Bit 11: X = Don't care  Bit 10: 0 = Short time  Bit 9: X = Don't care  Bits 8-7: 00 = 8 sample DC-squib-temp measure  Bits 6-5: 00 = 4 sample other measure  Bit 3: 1 = external safing engine  Bit 2: 1 = VSF set to 25 V  Bit 1: X = Don't care  Bit 0: 1 = timeout disable |

| \$04 SYS_STATE   | Init  | R   | -      | Bits 10÷8000 = INIT<br>Bits 2÷0: 010 = RUN                                                                                                                                                                                                                                                                                                                                                                                  |

| \$2A WDTCR       | Init  | W   | 0x3219 | Bit 14: WD1_MODE = FAST  Bits 13÷7: WDTMIN = 400 μs  Bits 6÷0: WDT DELTA = 200 μs                                                                                                                                                                                                                                                                                                                                           |

| \$2C WD_STATE    | Init  | R   | -      | Bits 10÷8: WD1_STATE = INITIAL (000)                                                                                                                                                                                                                                                                                                                                                                                        |

| \$2B WDIT        | Init  | W   | -      | Service watchdog following A/B/Asequence                                                                                                                                                                                                                                                                                                                                                                                    |

| \$04 SYS_STATE   | Diag  | R   | -      | Bits 10÷8: 001 = DIAG<br>Bits 2÷0: 010 = RUN                                                                                                                                                                                                                                                                                                                                                                                |

| \$02 SYS_CTL     | Diag  | W   | 0x02E0 | Bits 15÷13: X = Don't care  Bit 12: 0 = VIN th set to 5.5 V  Bit 11÷10: 00 = VBATMON th set to 6 V  Bit 9: 1 = ER Boost set to 33 V  Bit 8: X = Don't care  Bit 7: 1 = ER Charge on  Bit 6: 1 = ER Boost On  Bit 5: 1 = VSUP On  Bit 4: 0 = no POWER OFF from SHUTDOWN  Bits 3÷0: X = Don't care                                                                                                                            |

| \$05 POWER STATE | Diag  | R   | -      | Bit 19: 1 = WAKEUP > WU_on  Bit 18: 0 = VBATMON > VBBAD  Bit 17: 0 = VBATMON > VBGOOD  Bit 16: 0=VIN>VINBAD  Bit 15: 0 = VIN > VINGOOD  Bit 14: 0 = VDD3V3 > VDD3V3_UV  Bit 13: 0 = VDD3V3 < VDD3V3_OV                                                                                                                                                                                                                      |

AN5739 - Rev 5 page 15/79

| Dominton                  | Ctoto | D/M | Doto    | Notes                                          |

|---------------------------|-------|-----|---------|------------------------------------------------|

| Register                  | State | R/W | Data    | Notes                                          |

|                           |       |     |         | Bit 12: 0 = V_ERBOOST > ERBOOST_OK             |

|                           |       |     |         | Bit 11: 0 = VDD5 > VDD5_UV                     |

|                           |       |     |         | Bit 10: 0 = VDD5 < VDD5_OV                     |

|                           |       |     |         | Bit 9: 0 = VSUP > VSUP_OK                      |

|                           |       |     |         | Bit 8: 1 = ER Boost on                         |

|                           |       |     |         | Bit 7: 1 = ER Charge on                        |

|                           |       |     |         | Bit 4: 0 = ER Switch off                       |

|                           |       |     |         | Bit 3: 1 = VDD5 ramp up or on                  |

|                           |       |     |         | Bit 2: 1 = VSUP ramp up or on                  |

|                           |       |     |         | Bit 1: 1 = VDD3V3 on                           |

|                           |       |     |         | Bit 0: 0 = VSF_EN off                          |

| \$00 FLTSR                | Diag  | R   | -       | Verify there are not faults                    |

| \$6E LOOP_MATRIX_ARM1     | Diag  | W   | 0x000F  | Bits 15÷4: X = Don't care                      |

| φου LOOF_WATRIX_ARWIT     | Diag  | VV  | 0.00001 | Bits 3÷0: ARM1 assigned to 0÷3 loops           |

|                           |       |     |         | Bits 15÷8: X = Don't care                      |

|                           |       |     |         | Bits 7÷6: 01 = 0.5 ms deploy time              |

| \$06 DCR_0                | Diag  | W   | 0x0050  | Bits 5÷4: 01 = 1.75 A deploy current           |

|                           |       |     |         | Bits 3÷2: 00 = 500 ms deploy expiration time   |

|                           |       |     |         | Bits 1÷0: X = Don't care                       |

|                           |       |     |         | Bits 15÷8: X = Don't care                      |

|                           |       |     |         | Bits 7÷6: 01 = 0.5 ms deploy time              |

| \$07 DCR_1                | Diag  | W   | 0x0050  | Bits 5÷4: 01 = 1.75 A deploy current           |

| <b>40. 20.</b> <u>2</u> . | 2.03  |     | CAGGGG  | Bits 3÷2: 00 = 500 ms deploy expiration time   |

|                           |       |     |         | Bits 1÷0: X = Don't care                       |

|                           |       |     |         | Bits 15÷8: X = Don't care                      |

|                           |       |     |         | Bits 7÷6: 01 = 0.5 ms deploy time              |

| \$08 DCR_2                | Diag  | W   | 0x0050  | Bits 5÷4: 01 = 1.75 A deploy current           |

| Ψ00 DOI\_2                | Diag  | VV  | 0.0000  | Bits 3÷2: 00 = 500 ms deploy expiration time   |

|                           |       |     |         | Bits 1÷0: X = Don't care                       |

|                           |       |     |         |                                                |

|                           |       |     |         | Bits 15÷8: X = Don't care                      |

| #00 DOD 0                 | D:    | 101 | 0,,0050 | Bits 7÷6: 01 = 0.5 ms deploy time              |

| \$09 DCR_3                | Diag  | W   | 0x0050  | Bits 5÷4: 01 = 1.75 A deploy current           |

|                           |       |     |         | Bits 3÷2: 00 = 500 ms deploy expiration time   |

|                           |       |     |         | Bits 1÷0: X = Don't care                       |

|                           |       |     |         | Bit 15: 0 = deployment successful              |

|                           |       |     |         | Bit 14: 0 = deployment not in progress         |

| \$13 DSR_0                | Diag  | R   | -       | Bits 13: 0 = correct time/current combination  |

|                           |       |     |         | Bits 12: 0 = deployment configuration accepted |

|                           |       |     |         | Bits 5÷0: deployment expiration timer value    |

|                           |       |     |         | Bit 15: 0 = deployment successful              |

|                           |       |     |         | Bit 14: 0 = deployment not in progress         |

| \$14 DSR_1                | Diag  | R   | -       | Bits 13: 0 = correct time/current combination  |

|                           |       |     |         | Bits 12: 0 = deployment configuration accepted |

|                           |       |     |         | Bits 5÷0: deployment expiration timer value    |

AN5739 - Rev 5 page 16/79

| Register          | State    | R/W | Data   | Notes                                                           |  |  |  |  |  |  |  |  |

|-------------------|----------|-----|--------|-----------------------------------------------------------------|--|--|--|--|--|--|--|--|

|                   |          |     |        | Bit 15: 0 = deployment successful                               |  |  |  |  |  |  |  |  |

|                   |          |     |        | Bit 14: 0 = deployment not in progress                          |  |  |  |  |  |  |  |  |

| \$15 DSR_2        | Diag     | R   | -      | Bits 13: 0 = correct time/current combination                   |  |  |  |  |  |  |  |  |

|                   |          |     |        | Bits 12: 0 = deployment configuration accepted                  |  |  |  |  |  |  |  |  |

|                   |          |     |        | Bits 5÷0: deployment expiration timer value                     |  |  |  |  |  |  |  |  |

|                   |          |     |        | Bit 15: 0 = deployment successful                               |  |  |  |  |  |  |  |  |

|                   |          |     |        | Bit 14: 0 = deployment not in progress                          |  |  |  |  |  |  |  |  |

| \$16 DSR_3        | Diag     | R   | -      | Bits 13: 0 = correct time/current combination                   |  |  |  |  |  |  |  |  |

|                   |          |     |        | Bits 12: 0 = deployment configuration accepted                  |  |  |  |  |  |  |  |  |

|                   |          |     |        | Bits 5÷0: deployment expiration timer value                     |  |  |  |  |  |  |  |  |

| \$31 SAFING_STATE | Diag     | W   | 0xACAC | Frame to pass from DIAG to SAFING                               |  |  |  |  |  |  |  |  |

| \$04 SYS STATE    | S        | R   | _      | Bits 10÷8: 010 = SAFING                                         |  |  |  |  |  |  |  |  |

| ψ04 313_31A1L     | 3        | IX. | _      | Bits 2÷0: 010 = RUN                                             |  |  |  |  |  |  |  |  |

| \$25 SPIDEPEN     | S, A     | W   | 0x0FF0 | Lock Code                                                       |  |  |  |  |  |  |  |  |

| \$25 SPIDEPEN     | S, A     | W   | 0xF00F | Unlock Code                                                     |  |  |  |  |  |  |  |  |

| \$12 DEPCOM       | S, A     | W   | 0x000F | Bits 3÷0: 1111 = send deploy requests for all the four channels |  |  |  |  |  |  |  |  |

| \$25 SPIDEPEN     | S, A     | W   | 0x0FF0 | Lock Code                                                       |  |  |  |  |  |  |  |  |

| \$13 DSR_0        | S, A     | R   | -      | Bit 15: 1 = deployment successful                               |  |  |  |  |  |  |  |  |

| \$14 DSR_1        | S, A R - |     |        | Bit 15: 1 = deployment successful                               |  |  |  |  |  |  |  |  |

| \$15 DSR_2        | S, A     | R   | -      | Bit 15: 1 = deployment successful                               |  |  |  |  |  |  |  |  |

| \$16 DSR_3        | S, A     | R   | -      | Bit 15: 1 = deployment successful                               |  |  |  |  |  |  |  |  |

AN5739 - Rev 5 page 17/79

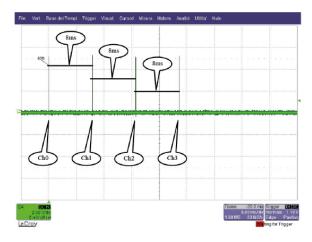

### 3.3.3 Deployment waveforms

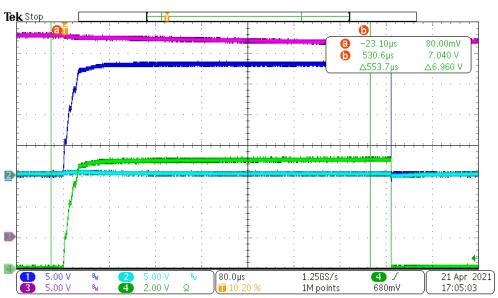

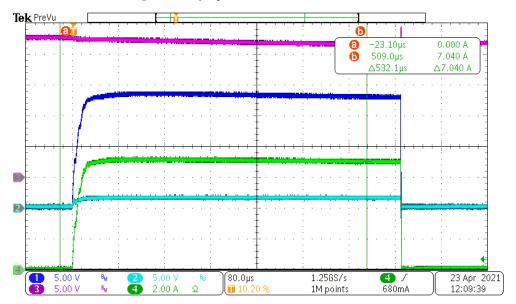

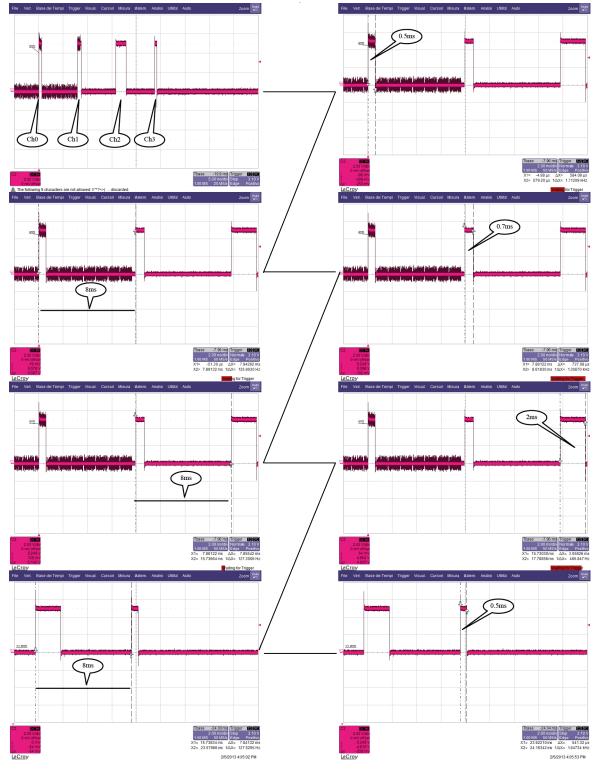

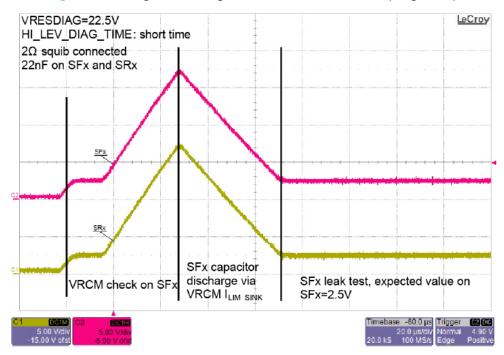

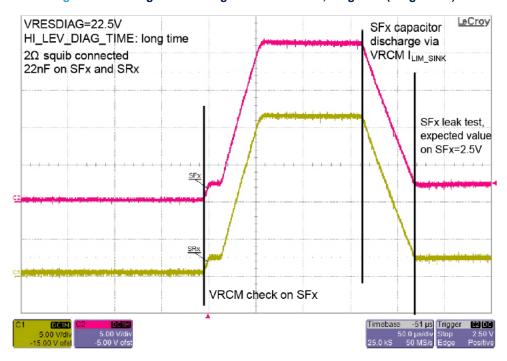

The Figure 7 and Figure 8 report some examples where a high current pyrofuse has been used and four channels have been put in parallel in order to achieve target current values for deployment to occur.

Referring to the Figure 1, the system has been setup with two different scenarios:

- With Safing FET, VER set to 33 V and VSF set to 25 V.

- Without Safing FET and VER set to 24 V.

The signals are the following:

- Blue = SRx

- Light blue = SFx

- Magenta = VER

- Green = Load current

Figure 8. Deployment waveforms, VER = 24 V

AN5739 - Rev 5 page 18/79

# 3.4 Arming command after deployment command

It is also possible to have a deployment event in a way different from the usual, i.e., first sending the SPI deploy command, then asserting the arming signal.

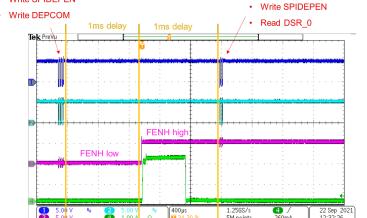

An example (watchdog disabled, deployment on Channel 0) is shown in the Table 14 and the Figure 9.

Table 14. Deploy event with Arming command after SPI deployment command

| Register read    | Register written                  | SPI frame (hex) |  |  |  |

|------------------|-----------------------------------|-----------------|--|--|--|

|                  | Configuration                     |                 |  |  |  |

| SYS_STATE        | SYS_CFG                           | 0x04030009      |  |  |  |

| SYS_CFG          | 1                                 | 0x01000000      |  |  |  |

| SYS_STATE        | 1                                 | 0x04000000      |  |  |  |

| SYS_STATE        | WD1_TEST                          | 0x046A3C00      |  |  |  |

| SYS_STATE        | 1                                 | 0x0400000       |  |  |  |

| POWER_STATE      | SYS_CTL                           | 0x050402E0      |  |  |  |

| FLTSR            | 1                                 | 0x00010000      |  |  |  |

| LOOP_MATRIX_ARM1 | LOOP_MATRIX_ARM1                  | 0x6EDC0001      |  |  |  |

| DCR_0            | DCR_0                             | 0x060D0050      |  |  |  |

| SYS_STATE        | SAFING_STATE                      | 0x0463ACAC      |  |  |  |

| SYS_STATE        | 1                                 | 0x04000000      |  |  |  |

|                  | Deployment commands               |                 |  |  |  |

| SPIDEPEN         | SPIDEPEN                          | 0x254B0FF0      |  |  |  |

| SPIDEPEN         | SPIDEPEN                          | 0x254BF00F      |  |  |  |

| DEPCOM           | DEPCOM                            | 0x12240001      |  |  |  |

| 1                | ms delay - FENH high - 1 ms delay |                 |  |  |  |

| SPIDEPEN         | SPIDEPEN                          | 0x254B0FF0      |  |  |  |

| DSR_0            | 1                                 | 0x13000000      |  |  |  |

Figure 9. Deploy event with Arming command after SPI deployment command

Write SPIDEPEN

Write SPIDEPEN

Blue = SPI\_CLK Light blue = SPI\_MOSI Magenta = FENH Green = Load current

AN5739 - Rev 5 page 19/79

# 4 Diagnostic

For all the channels the following diagnostics are implemented (elaborated by a 10 bits ADC converter):

- High voltage leak test, for SFx and SRx oxide isolation

- VRCM test

- Leakage to battery/ground for SFx and SRx with/ without squib

- Loop to loop short diagnostic

- Squib resistance measurement leakage cancellation

- High squib resistance, 500 Ω ÷ 2000 Ω

- SSxy, SFx,and VER voltage monitor

- Low side FET diagnostic

- High Side FET diagnostic

- · Loss of ground

- High Side Safing FET diagnostic

- · Deployment timer diagnostic

Diagnostic can be done in two ways, set in the LPDIAGREQ register via SPI:

- High level (DIAG\_LEVEL = 1): the set-up for each requested measurement is managed by the device itself.

- Low level (DIAG\_LEVEL = 0): the set-up for each requested measurement is managed by an external logic, step by step.

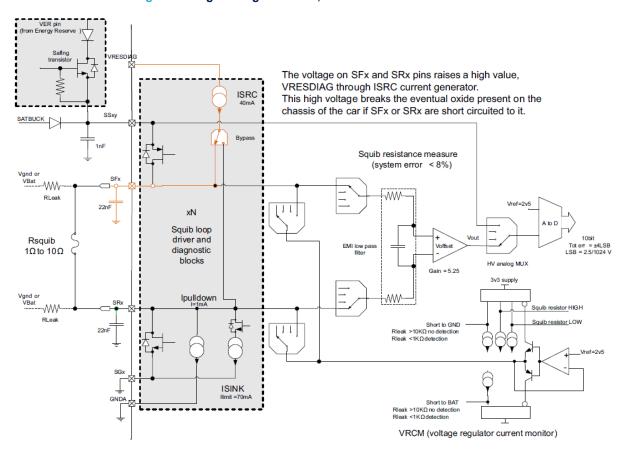

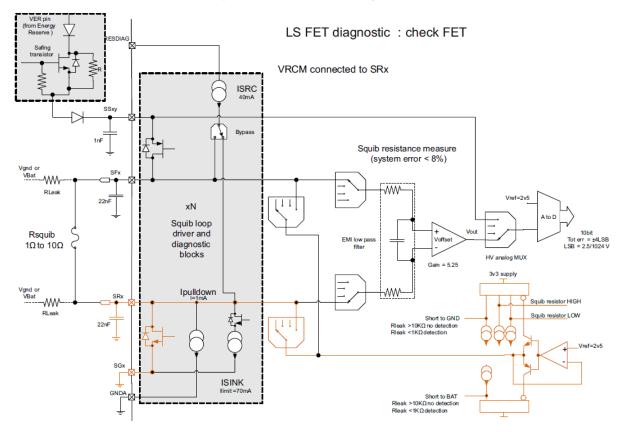

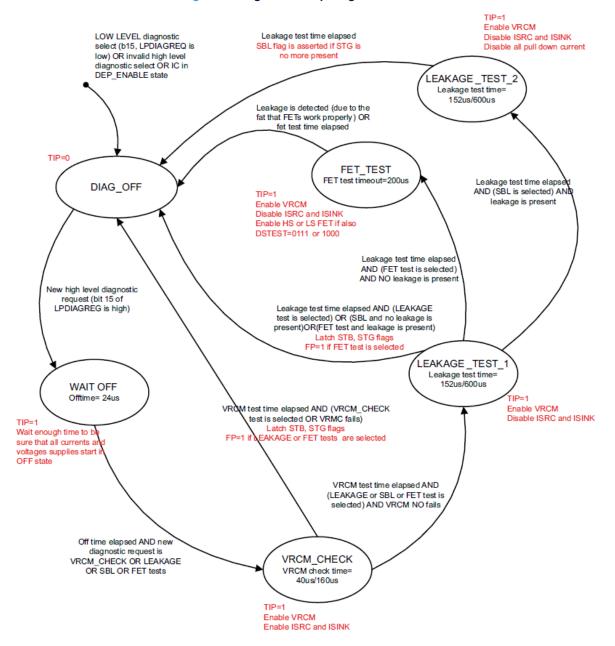

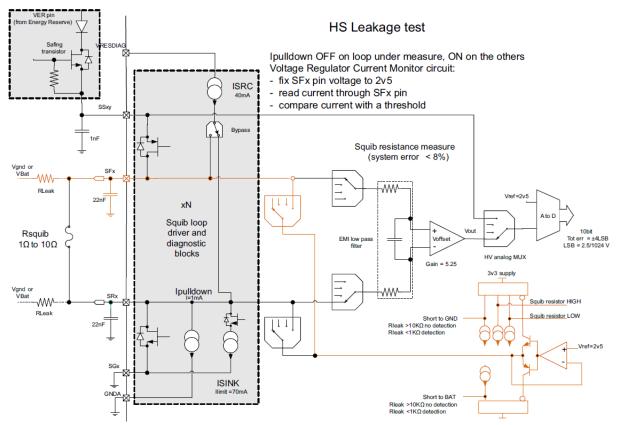

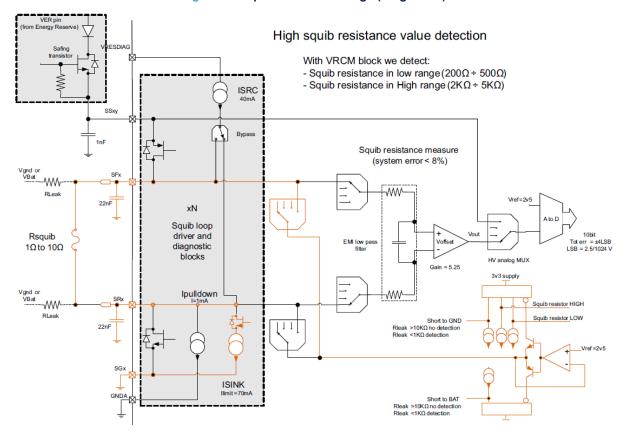

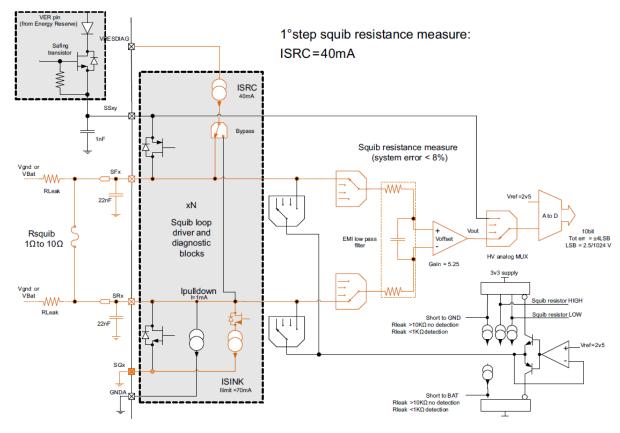

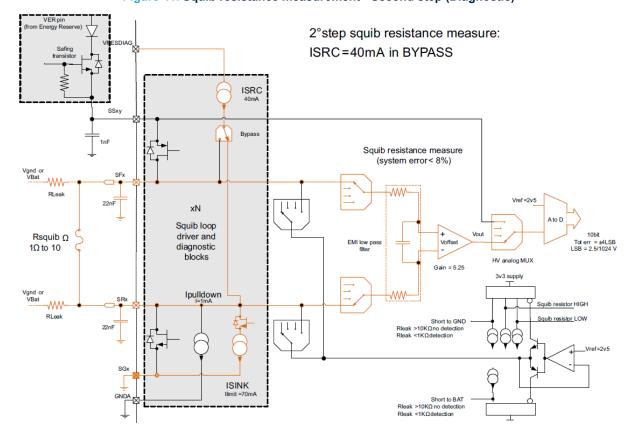

The relevant blocks used for the diagnostic are reported in the Figure 10.

In particular there are a Voltage Regulator Current Monitor (VRCM) and three current generators that withstand diagnostic operations, ISRC (40 mA), ISINK (limit 70 mA) and Ipulldown (1 mA).

VER pi ISRC SATBUCK Squib resistance measure (system error < 8%) χN A to D Squib loop Rsquib driver and diagnostic 1Ω to 10Ω blocks HV analog MUX Gain = 5.25 Ipulldown Squib resistor HIGH Squib resistor LOW 22nF ISINK GNDA

VRCM (voltage regulator current monitor)

Figure 10. Squib diagnostic blocks

AN5739 - Rev 5 page 20/79

# 4.1 Low level diagnostic

For a low level diagnostic, these steps shall be followed (see the Table 15):

- 1. ER charge has to be previously turned ON before running the diagnostic.

- 2. Verify that the IC is in DIAG state reading register \$04.

- 3. Decide, writing the appropriate bit in reg. \$38, which diagnostic mode is used.

Table 15. Low level diagnostic

|                                       | (1) | (2) | 15 | 14  | 13   | 12   | 11   | 10                    | 9                  | 8    | 7   | 6    | 5   | 4 | 3   | 2                           | 1    | 0  |                                                                         |

|---------------------------------------|-----|-----|----|-----|------|------|------|-----------------------|--------------------|------|-----|------|-----|---|-----|-----------------------------|------|----|-------------------------------------------------------------------------|

|                                       |     |     |    |     |      |      |      |                       |                    |      |     |      |     |   |     |                             |      |    | 12: VIN_TH_SEL (0 = 5.5 V as VIN threshold, 1 = 7.5 V as VIN threshold) |

|                                       |     |     |    |     |      |      | C    | 00                    |                    |      |     |      |     |   |     |                             |      |    | 11, 10: VBATMON_TH_SEL (00 = 6V, 01 = 6.8 V, 10 = 8 V, 11 = 8.8 V)      |

| \$02 SYS_CTL                          | (I) | W   | Х  | Х   | Х    | 0/1  | C    | )1                    | 0/1                | X    | 1   | 1    | 0   | 0 | x   | х                           | X    | X  | 9: ER_BST_V (0 = 23 V, 1 = 33 V)                                        |

| , , , , , , , , , , , , , , , , , , , | (-) |     |    |     |      |      | 1    | 0                     |                    |      |     |      |     |   |     |                             |      |    | 7: ER_CUR_EN (0 = OFF, 1 = ON)                                          |

|                                       |     |     |    |     |      |      | 1    | 11                    |                    |      |     |      |     |   |     |                             |      |    | 6: ER_BST_EN (0 = OFF, 1 = ON)                                          |

|                                       |     |     |    |     |      |      |      |                       |                    |      |     |      |     |   |     |                             |      |    | 5: VSUP_EN (0 = OFF, 1 = ON)                                            |

|                                       |     |     |    |     |      |      |      |                       |                    |      |     |      |     |   |     |                             |      |    | 4: SPI_OFF (0 = no effect, 1 = power off required)                      |

| ¢04 CVC CTATE                         |     | R   |    |     |      |      |      | 0                     | 0                  | 1    |     |      |     |   |     | 0                           | 4    | 0  | 10, 9, 8: 001 = DIAG                                                    |

| \$04 SYS_STATE                        |     | K   |    |     |      |      |      | U                     | 0                  | ļ '  |     |      |     |   |     | U                           | '    | U  | 2, 1, 0: 010 = RUN                                                      |

| \$38 LPDIAGREQ                        | (l) | W   | 0  |     |      |      |      | 14÷0                  | ): De              | fine | the | e te | est |   |     |                             |      |    | 15: 0 = low level diag setup                                            |

| \$37 LPDIAGSTAT                       |     | R   | 0  |     |      |      |      | 14÷0: Define the test |                    |      |     |      |     |   |     |                             |      |    | 15: 0 = low level diag                                                  |

| \$3X DIAGCTRL_X                       |     | W   |    | х   | Х    | Х    | Х    | х                     | X 6÷0: ADC address |      |     |      |     |   | oc. | ado                         | dres | ss |                                                                         |

| X = A, B, C, D                        |     |     |    |     |      |      |      |                       |                    |      |     |      |     |   |     |                             |      |    |                                                                         |

| (3) 19 18 17 16                       |     |     | 1  | 6÷0 | : AD | C ad | dres | ss                    | 9÷0: ADC result 1  |      |     |      | lt  |   |     | 19: 1 = conversion finished |      |    |                                                                         |

<sup>1.</sup> I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, - = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

- 2. R = READ, W = WRITE

- 3. Further bit over the 16 standard.

In low level mode, the IC performs the measurement following external requests. Each test set-up is driven, step by step, by the microcontroller, as the timing for the measurement.

AN5739 - Rev 5 page 21/79

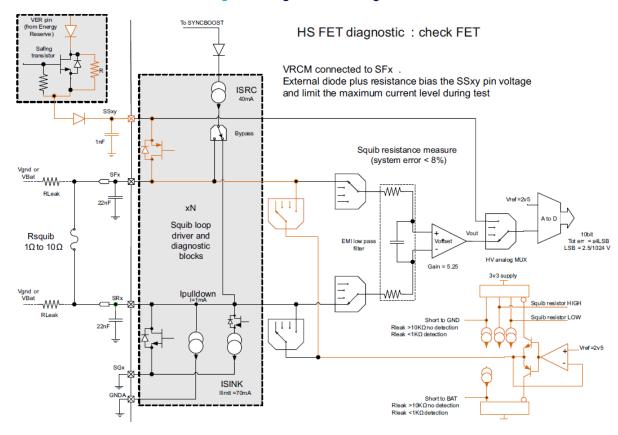

#### 4.1.1 High voltage leak test, oxide isolation IC-car chassis

Figure 11. High voltage leak test, oxide isolation IC-car chassis

This test is mandatory and verifies that no leakages are present on the SFx or SRx pins when high voltage is applied. ISRC current generator is ON and addressed on SFx (see the Table 16).

If there is no leakage, SFx raises up to VRESDIAG and, being the impedance between SFx and SRx very low (squib connected), SRx follows SFx (see Figure 11).

Confirmation of this is done through an ADC measurement request of the SFx voltage value.

Table 16. High voltage leak test, oxide isolation IC-car chassis - LPDIAGREQ register

|                | (1) | (2) | 15 | 14 | 13 | 12:11 | 10 | 9:8 | 7:4            | 3:0        |                                                |

|----------------|-----|-----|----|----|----|-------|----|-----|----------------|------------|------------------------------------------------|

|                |     |     |    |    |    |       |    |     |                |            | 15: 0 = low level diagnostic                   |

|                |     |     |    |    |    |       |    |     | RES_MEAS_CHSEL | LEAK_CHSEL | 14: 0 = ISRC = 40 mA                           |

|                |     |     |    |    |    |       |    |     | 0000 = ch0     | 0000 = ch0 | 13: 1 = pull-down current off for all channels |

| \$38 LPDIAGREQ | (1) | W   | 0  | 0  | 1  | 01    | 0  | 00  | 0001 = ch1     | 0001 = ch1 | 12, 11: 01 = ISRC for RES_MEAS_CHSEL, off      |

|                |     |     |    |    |    |       |    |     | 0010 = ch2     | 0010 = ch2 | for the other channels                         |

|                |     |     |    |    |    |       |    |     | 0011 = ch3     | 0011 = ch3 | 10: 0 = ISINK off for all channels             |

|                |     |     |    |    |    |       |    |     |                |            | 9, 8: 00 = VRCM not connected                  |

<sup>1.</sup> I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, - = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

SFx voltages and VRESGIAG are readable by the microcontroller through the ADC converter in the registers \$3X DIAGCTRL\_X, with X = A, B, C, D (see the Table 17. High voltage leak test, oxide isolation IC-car chassis - DIAGCTRL\_X registers).

AN5739 - Rev 5 page 22/79

<sup>2.</sup> R = READ, W = WRITE

|     |    |      |              |        | (1) | (2) | 15 | 14 | 13     | 12    | 11 | 10 | 9 | 8 | 7 | 6:0             |                             |

|-----|----|------|--------------|--------|-----|-----|----|----|--------|-------|----|----|---|---|---|-----------------|-----------------------------|

|     |    |      |              |        |     |     |    |    |        |       |    |    |   |   |   | ADCREQ_X        |                             |

|     |    |      |              |        |     |     |    |    |        |       |    |    |   |   |   | \$46 = SF0      |                             |

|     | \$ | 3X E | OIAG         | CTRL_X |     | W   | X  | Х  | X      | ×     | Х  | Х  | X | X | X | \$47 = SF1      |                             |

|     |    | X =  | = A, B, C, D |        | -   | VV  | ^  | ^  | ^      | ^     | ^  | ^  | ^ | ^ | ^ | \$48 = SF2      |                             |

|     |    |      |              |        |     |     |    |    |        |       |    |    |   |   |   | \$49 = SF3      |                             |

|     |    |      |              |        |     |     |    |    |        |       |    |    |   |   |   | \$42 = VRESDIAG |                             |

| (3) | 19 | 18   | 17           | 16     |     |     |    |    |        |       |    |    |   |   |   |                 | 19: 1 = conversion finished |

|     |    |      |              |        |     |     |    | Α  | DCR    | EQ_   | X  |    |   |   |   |                 | -                           |

|     |    |      |              |        |     |     |    |    | \$46 = | = SFC | )  |    |   |   |   |                 |                             |

Table 17. High voltage leak test, oxide isolation IC-car chassis - DIAGCTRL X registers

- 1. I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

- 2. R = READ, W = WRITE

- 3. Further bit over the 16 standard.

Once read the ADC measurement, to obtain the voltage value it is necessary to consider the divider ratio of the ADC. In case of SFx and VRESDIAG, it is 15:1.

As an example, consider the case where the VRESDIAG conversion has been requested and the readout of the ADC register is done. The voltage measured on VRESDIAG pin is 22.6 V.

ADC = 0b1001101000 = 616

ADCREQ X

In order to obtain the result in Volt, being the ADC characteristic linear:

\$47 = SF1

\$48 = SF2 \$49 = SF3 \$42 = VRESDIAG

$$2.5 V: 1024 = x: ADC \rightarrow x = \frac{616 * 2.5 V}{1024} = 1.5 V$$

(1)

ADCREQ\_X 10 bit ADC result

Considering the divider ratio (DR), the result is:

$$VRESDIAG = x * DR = 1.5 V * 15 = 22.6 V$$

(2)

#### **Test result**

In case of leakage on High Side (SFx) or Low Side (SRx), SFx voltage is not able to reach VRESDIAG and the microcontroller can detect the leakage problem, both on the High Side or on the Low Side, with no possibility, at this stage, to distinguish which of them is involved in the problem.

#### 4.1.2 VRCM test validation

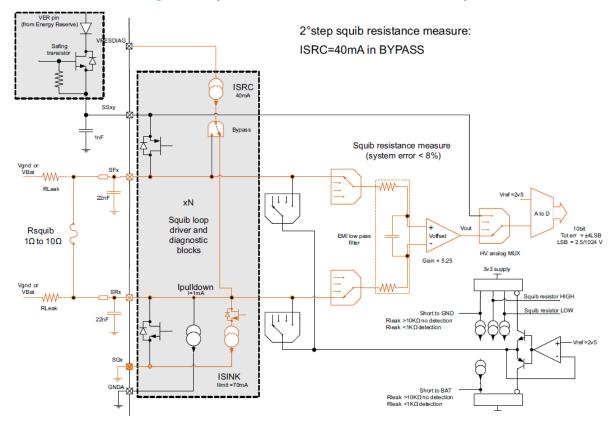

Before using VRCM block, used in many IC diagnostics, it is necessary a test for its validation. The test is done through short to battery and short to ground flag verification. Measurement set-up is composed by 2 steps, with VRESDIAG supplied.

AN5739 - Rev 5 page 23/79

#### 4.1.2.1 VRCM test - First step

HS FET diagnostic: check VRCM functionality First we use ISRC current generator to check VRCM block ISRC Squib resistance measure (system error < 8%) w Squib loop Rsquib driver and diagnostic  $1\Omega$  to  $10\Omega$ blocks 3v3 supply Vgnd or VBat lpulldown Squib resistor LOW Short to GND Rleak >10KΩ no detection 111 ISINK Short to BAT

Figure 12. VRCM test validation - First step

The first step (see the Figure 12) is verified through the LPDIAGREQ register (see the Table 18).

(1) 15 | 14 | 13 | 12:11 | 10 | 9:8 7:4 3:0 15: 0 = low level diagnostic 14: 0 = ISRC = 40 mA RES\_MEAS\_CHSEL LEAK\_CHSEL 13: 1 = pull-down current off for all channels 0000 = ch00000 = ch012. 11: 01 = ISRC for RES\_MEAS\_CHSEL, off 0001 = ch10001 = ch1\$38 LPDIAGREQ (I) W 0 0 01 0 01 for the other channels 0010 = ch20010 = ch210: 0 = ISINK off for all channels 0011 = ch30011 = ch39, 8: 01 = VRCM connected to SFx (LEAK\_CHSEL channel)

Table 18. VRCM test validation (first step) - LPDIAGREQ register

- 1. I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

- 2. R = READ, W = WRITE

RES\_MEAS\_CHSEL, bit[7:4] and LEAK\_CHSEL, bit[3:0] must refer to the same channel.

#### Test 1 result

Being ISRC and VRCM connected to SFx, if VRCM works correctly, short to battery, readable in the LPDIAGSTAT register, is asserted for the channel selected (see the Table 19).

AN5739 - Rev 5 page 24/79

|     |         |      |      |    | (1) | (2) | 15:12 | 11:8           | 7 | 6 | 5 | 4 | 3:0        |                               |

|-----|---------|------|------|----|-----|-----|-------|----------------|---|---|---|---|------------|-------------------------------|

| 5   | \$37 LI | PDIA | GSTA | T  |     | R   |       | RES_MEAS_CHSEL |   |   |   |   | LEAK_CHSEL | 19: 0 = low level diagnostic  |

| (3) | 19      | 18   | 17   | 16 |     | R   |       | 0000 = ch0     |   |   |   |   | 0000 = ch0 | 7: 0 = no short between loops |

|     |         |      |      |    |     |     |       | 0001 = ch1     | 0 | 0 | 1 | 1 | 0001 = ch1 | 6: 0 = STG not detected       |

|     | 0       | 0    | 0    | 0  |     |     |       | 0010 = ch2     |   |   |   |   | 0010 = ch2 | 5: 1 = STB detected           |

|     |         |      |      |    |     |     |       | 0011 = ch3     |   |   |   |   | 0011 = ch3 | 4: 1 = test on SFx            |

Table 19. VRCM test validation (first step) - LPDIAGSTAT register

- 1. I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

- 2. R = READ, W = WRITE

- 3. Further bit over the 16 standard.

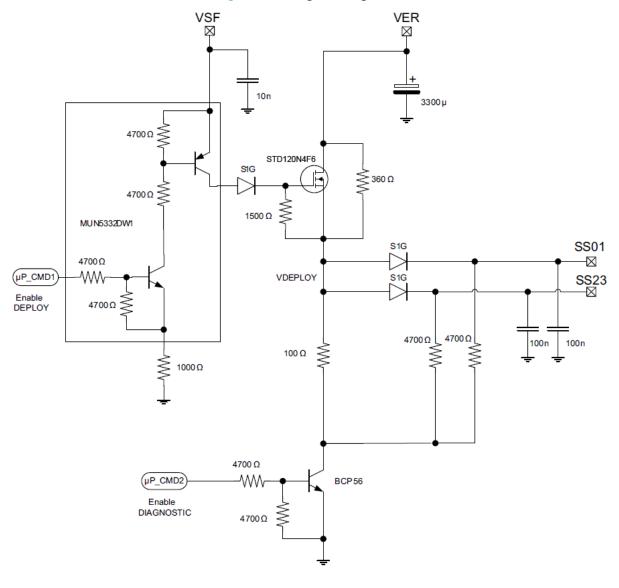

#### 4.1.2.2 VRCM test - Second step

LS FET diagnostic: check VRCM functionality Second we use ISINK current generator to check VRCM block ISRC Squib resistance measure (system error < 8%) -WW ₩ χN Squib loop Rsquib driver and 1Ω to 10 Ω diagnostic blocks HV analog MUX Gain = 5.25 3v3 supply Vgnd or VBat Ipulldown Squib resistor HIGH Squib resistor LOW

Figure 13. VRCM test validation - Second step

Once the first step of VRCM test is passed, it is possible to proceed with the second step (see the Figure 13), always through the LPDIAGREQ register (see the Table 20).

ISINK

AN5739 - Rev 5 page 25/79

|    | Table 20. VRCM test validation (second step) - LPDIAGREQ register |    |       |    |     |     |     |                              |  |  |  |  |  |  |  |

|----|-------------------------------------------------------------------|----|-------|----|-----|-----|-----|------------------------------|--|--|--|--|--|--|--|

| 15 | 14                                                                | 13 | 12:11 | 10 | 9:8 | 7:4 | 3:0 |                              |  |  |  |  |  |  |  |

|    |                                                                   |    |       |    |     |     |     | 15: 0 = low level diagnostic |  |  |  |  |  |  |  |

|                | (1) | (2) | 15 | 14 | 13 | 12:11 | 10 | 9:8 | 7:4            | 3:0        |                                                               |

|----------------|-----|-----|----|----|----|-------|----|-----|----------------|------------|---------------------------------------------------------------|

|                |     |     |    |    |    |       |    |     |                |            | 15: 0 = low level diagnostic                                  |

|                |     |     |    |    |    |       |    |     | RES_MEAS_CHSEL | LEAK_CHSEL | 14: 0 = ISRC = 40 mA                                          |

|                |     |     |    |    |    |       |    |     | 0000 = ch0     | 0000 = ch0 | 13: 1 = pull-down current off for all channels                |

| \$38 LPDIAGREQ | (I) | W   | 0  | 0  | 1  | 00/11 | 1  | 10  | 0001 = ch1     | 0001 = ch1 | 12, 11: 00/11 = ISRC off for all channels                     |

|                |     |     |    |    |    |       |    |     | 0010 = ch2     | 0010 = ch2 | 10: 1 = ISINK on for RES_MEAS_CHSEL                           |

|                |     |     |    |    |    |       |    |     | 0011 = ch3     | 0011 = ch3 | channel, off for the others  9, 8: 10 = VRCM connected to SRx |

|                |     |     |    |    |    |       |    |     |                |            | (LEAK_CHSEL channel)                                          |

<sup>1.</sup> I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, - = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

RES\_MEAS\_CHSEL, bit[7:4] and LEAK\_CHSEL, bit[3:0] must refer to the same channel.

#### **Test 2 result**

Being ISNK and VRCM connected to SRx, if VRCM works correctly, short to ground, readable in the LPDIAGSTAT register, is asserted for the channel selected (see the Table 21).

Table 21. VRCM test validation (second step) - LPDIAGSTAT register

|     |       |      |      |    | (1) | (2) | 15:12 | 11:8           | 7 | 6 | 5 | 4 | 3:0        |                               |

|-----|-------|------|------|----|-----|-----|-------|----------------|---|---|---|---|------------|-------------------------------|

| 5   | 37 LI | PDIA | GSTA | T  |     | R   |       |                |   |   |   |   |            | 19: 0 = low level diagnostic  |

| (3) | 19    | 18   | 17   | 16 |     | R   |       |                |   |   |   |   |            | 7: 0 = no short between loops |

|     |       |      |      |    |     |     |       | RES_MEAS_CHSEL | 0 | 1 | 0 | 0 | LEAK_CHSEL | 6: 1 = STG detected           |

|     | 0     | 0    | 0    | 0  |     |     |       |                |   |   |   |   |            | 5: 0 = STB not detected       |

|     |       |      |      |    |     |     |       |                |   |   |   |   |            | 4: 0 = test on SRx            |

<sup>1.</sup> I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, - = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

- 2. R = READ, W = WRITE

- 3. Further bit over the 16 standard.

#### **Final result**

If the second step of the VRCM test is passed too, the VRCM test is validated.

AN5739 - Rev 5 page 26/79

<sup>2.</sup> R = READ, W = WRITE

\_Vref =2v5

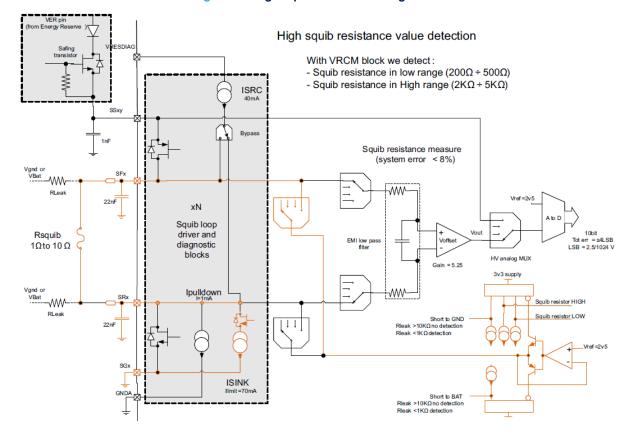

#### 4.1.3 Leakage test - High Side

HS Leakage test Ipulldown OFF on loop under measure , ON on the others Voltage Regulator Current Monitor circuit fix SFx pin voltage to 2v5 ISRC - read current through SFx pin compare current with a threshold SSxy Bypass Squib resistance measure (system error < 8%) Vgnd or VBat W RLeak Vref =2v5 χN A to D Squib loop 10bit driver and Rsquib Voffse Tot err = ±4LSB LSB = 2.5/1024 V 1Ω to 10 Ω diagnostic blocks HV analog MUX Gain = 5.25 3v3 supply lpulldown Squib resistor HIGH Squib resistor LOW Short to GNE Rleak >10KΩno detection [ ] ]

Rleak <1KΩ detection

Rleak >10KΩno detection

Figure 14. Leakage test - High Side

ISRC and ISINK are kept off and VRCM is connected to SFx (see the Figure 14), chosen through the LEAK\_CHSEL bits in the LPDIAGREQ register (see the Table 22).

ISINK

(1) (2) 15 14 13 12:11 10 9:8 3:0 7:4 15: 0 = low level diagnostic 14: 0 = ISRC = 40 mA RES\_MEAS\_CHSEL LEAK\_CHSEL 13: 0 = pull-down current off for VRCM 0000 = ch00000 = ch0channel, on for the others \$38 LPDIAGREQ | (I) | W 0001 = ch100/11 0 01 0001 = ch10 0 0 12, 11: 00/11 = ISRC off for all channels 0010 = ch20010 = ch210: 0 = ISINK off for all channels 0011 = ch30011 = ch39, 8: 01 = VRCM connected to SFx (LEAK\_CHSEL channel)

Table 22. Leakage test, High Side - LPDIAGREQ register

- 1. I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

- 2. R = READ, W = WRITE

#### Test result

If there is no leakage on the High Side, SFx voltage is equal to VREF = 2.5 V and no current is detected by VRCM itself. SFx voltage is readable addressing the ADC read out on it. The registers involved in this operation are the four DIAGCTRL\_X (see the Table 23).

AN5739 - Rev 5 page 27/79

|     |    |    |    |                  |     | иыс | 20. | _ou. | ugu              | ,                               | .,     | 9 0 | , i d |     |     |     |      |                   |                                 | 9.0      | ,,,         | •   |   |                             |

|-----|----|----|----|------------------|-----|-----|-----|------|------------------|---------------------------------|--------|-----|-------|-----|-----|-----|------|-------------------|---------------------------------|----------|-------------|-----|---|-----------------------------|

|     |    |    |    |                  | (1) | (2) | 15  | 14   | 13               | 12                              | 11     | 10  | 9     | 8   | 7   | 6   | 5    | 4                 | 3                               | 2        |             | 1   | 0 |                             |

|     | \$ |    |    | CTRL_X<br>, C, D | -   | W   | x   | X    | x                | X                               | X      | x   | X     | x   | X   |     |      | \$4<br>\$4<br>\$4 | CRE<br>6 =<br>7 =<br>8 =<br>9 = | SF<br>SF | 0<br>1<br>2 | •   |   |                             |

| (3) | 19 | 18 | 17 | 16               |     |     |     |      |                  |                                 |        |     |       |     |     |     |      |                   |                                 |          |             |     |   | 19: 1 = conversion finished |

|     | 1  | 0  | 0  | ADCREQ_X         | _   | R   |     | :    | \$46 =<br>\$47 = | REQ_<br>= SF0<br>= SF1<br>= SF2 | )<br>I |     |       | ADC | CRE | Q_> | ( 10 | ) bit             | ΑΣ                              | )C r     | es          | ult |   |                             |

Table 23. Leakage test, High Side - DIAGCTRL\_X register

1. I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, - = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

\$49 = SF3

- 2. R = READ, W = WRITE

- 3. Further bit over the 16 standard.

Once read the ADC measurement, to obtain the voltage value it is necessary to consider the divider ratio of the ADC, that is 15:1 in case of SFx and VRESDIAG.

In case of a leakage (to ground or to battery), VRCM will sink or source a current to maintain SFx at VREF. As a consequence, STG or STB is set in the LPDIAGSTAT register (see the Table 24).

|     |       |      |      |           | (1) | (2) | 15:12 | 11:8           | 7 | 6   | 5   | 4 | 3:0        |                               |

|-----|-------|------|------|-----------|-----|-----|-------|----------------|---|-----|-----|---|------------|-------------------------------|

| \$  | 37 LF | PDIA | GSTA | <b>ΑΤ</b> |     | R   |       | RES_MEAS_CHSEL |   |     |     |   | LEAK_CHSEL | 19: 0 = low level diagnostic  |

| (3) | 19    | 18   | 17   | 16        |     | R   |       | 0000 = ch0     |   |     |     |   | 0000 = ch0 | 7: 0 = no short between loops |

|     |       |      |      |           |     |     |       | 0001 = ch1     | 0 | 0/1 | 0/1 | 1 | 0001 = ch1 | 6: 1 = STG if leak vs GND     |

|     | 0     | 0    | 0    | 0         |     |     |       | 0010 = ch2     |   |     |     |   | 0010 = ch2 | 5: 1 = STB if leak vs BATT    |

|     |       |      |      |           |     |     |       | 0011 = ch3     |   |     |     |   | 0011 = ch3 | 4: 1 = test on SFx            |

Table 24. Leakage test, High Side - LPDIAGSTAT register

- 1. I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

- 2. R = READ, W = WRITE

- 3. Further bit over the 16 standard.

Pull-down current (1 mA) is active on all channels except the one under analysis. So, the STG requires further investigation to understand if it comes from a real short to ground of the channel itself or it comes from a short between the channel itself and another one.

Note: In Pyro Fuse Application with channels shorted together, a leakage on a channel causes a fault on all channels.

AN5739 - Rev 5 page 28/79

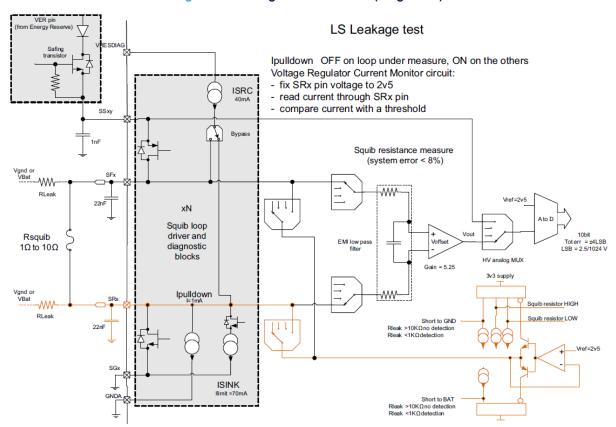

#### 4.1.4 Leakage test - Low Side

LS Leakage test Ipulldown OFF on loop under measure , ON on the others Voltage Regulator Current Monitor circuit fix SRx pin voltage to 2v5 ISRC - read current through SRx pin - compare current with a threshold SSx Bypass Squib resistance measure (system error < 8%) Vgnd or VBat w RLeak χN A to D Squib loop 10bit driver and Rsquib Voffse Tot err = ±4LSB LSB = 2.5/1024 V diagnostic 1Ω to 10Ω blocks HV analog MUX Gain = 5.25 Ipulldown -WW Squib resistor HIGH Short to GND Rleak >10KΩno detection Rleak <1KΩ detection Squib resistor LOW Vref=2v5 ISINK

Figure 15. Leakage test - Low Side

ISRC and ISINK are kept off and VRCM is connected to SRx (see the Figure 15), through the LEAK\_CHSEL bits in the LPDIAGREQ register (see the Table 25).

(1) (2) 15 14 13 12:11 10 9:8 3:0 7:4 15: 0 = low level diagnostic 14: 0 = ISRC = 40 mA RES\_MEAS\_CHSEL LEAK\_CHSEL 13: 0 = pull-down current off for VRCM 0000 = ch00000 = ch0channel, on for the others \$38 LPDIAGREQ (I) W 00/11 0 10 0001 = ch10001 = ch10 0 0 12, 11: 00/11 = ISRC off for all channels 0010 = ch20010 = ch210: 0 = ISINK off for all channels 0011 = ch30011 = ch39, 8: 10 = VRCM connected to SRx (LEAK\_CHSEL channel)

Table 25. Leakage test, Low Side - LPDIAGREQ register

- 1. I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

- 2. R = READ, W = WRITE

#### **Test result**

If there is no leakage on the High Side, SRx voltage is equal to VREF = 2.5 V and no current is detected by VRCM itself.

Only if the squib is connected, SFx and SRx pins are at the same voltage, so SRx voltage is readable indirectly through SFx voltage, as done in case of High Side leakage test.

AN5739 - Rev 5 page 29/79

SFx voltage is readable addressing the ADC read out on it. The registers involved in this operation are the four DIAGCTRL X (see the Table 26).

(1) (2) 15 14 13 12 11 10 8 7 6 5 4 3 2 1 0 ADCREQ X \$46 = SF0 \$3X DIAGCTRL\_X W Χ Х Χ Χ Χ Χ Х Χ Х \$47 = SF1 X = A, B, C, D\$48 = SF2 \$49 = SF3 19 18 17 16 19: 1 = conversion finished ADCREQ X \$46 = SF0 R ADCREQ\_X \$47 = SF1 ADCREQ\_X 10 bit ADC result 0 0 1 \$48 = SF2 \$49 = SF3

Table 26. Leakage test, Low Side - DIAGCTRL\_X register

- 1. I = INIT, D = DIAG, S = SAFING, C = SCRAP, A = ARMING, = ALL STATES, (I) = no in INIT, (D) = no in DIAG, (S) = no in SAFING, (C) = no in SCRAP, (A) = no in ARMING

- 2. R = READ, W = WRITE

- 3. Further bit over the 16 standard.

Once read the ADC measurement, to obtain the voltage value it is necessary to consider the divider ratio of the ADC, that is 15:1 in case of SFx and VRESDIAG.

If the squib between SFx and SRx pins is not connected, SRx voltage read out is not possible, as it is not mapped into the ADC request command.

In case of a leakage (to ground or to battery), VRCM will sink or source a current to maintain SFx at VREF. Therefore, STG or STB is set in the LPDIAGSTAT register (see the Table 27).