## Migrating within STM32U5 series microcontrollers

#### Introduction

The ability to replace easily one microcontroller type with another from the same product series is an important asset for designers of STM32 microcontroller applications.

Migrating an application to a different microcontroller is often needed when product requirements grow. This places extra demands on new features, memory size, or increases the number of I/Os. Cost reduction objectives may be also a reason to switch to smaller components, and shrink the PCB area.

This application note analyzes the steps required to migrate an existing design between STM32U5 series microcontrollers.

The hardware and peripherals are the main aspects to be considered for the migration.

This document lists the full set of features available for STM32U5 series devices.

To benefit from this application note, the user should be familiar with the STM32 microcontroller documentation available on www.st.com.

## 1 General information

This application note applies to the STM32U5 series microcontrollers that are Arm®Cortex® core-based devices.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

#### **Reference documents**

- [1] Reference manual STM32U5 series Arm®-based 32-bit MCUs (RM0456)

- [2] STM32U5 series datasheets and errata sheets

- [3] Application note Getting started with STM32U5 series MCU hardware development (AN5373)

AN5766 - Rev 1 page 2/27

## 2 Hardware migration guide

To understand the migration within the STM32U5 series on the hardware part, refer to document [3]. Document [3] is intended for system designers who require a hardware implementation overview of the development board features, such as: power supply, package differences, clock management, reset control, boot mode settings, and debug management.

Document [3] details how to migrate within the STM32U5 series microcontrollers and describes the minimum hardware resources required to develop an application using these microcontrollers. Detailed reference design schematics are also contained in this document with descriptions of main components, interfaces, and modes.

AN5766 - Rev 1 page 3/27

## 3 Peripheral migration guide

### 3.1 STM32 product cross-compatibility

STM32 microcontrollers embed a set of peripherals, which can be classified in three groups:

- Peripherals that are common and identical to all products. Those peripherals have the same structure, registers, and controls bits. There is no need to perform any firmware change to keep the same functionality at the application level after migration. All the features and behavior remain the same.

- Peripherals that are shared by all products but have only minor differences (in general to support new features). Therefore, migrating from one product to another is easy and does not need any significant new development effort.

- Peripherals that have considerable changes from one product to another (new architecture or new features). The migration for this group of peripherals requires a new development at application level.

The table below summarizes the available peripherals in STM32U5 series microcontrollers as well as their compatibility.

Table 1. Peripheral compatibility analysis within STM32U5 series microcontrollers

|                                 |                     | ıo         | ω.            | STM32U59x/5Ax | ×             |                                                                                             | Compatibility                                                         |  |  |

|---------------------------------|---------------------|------------|---------------|---------------|---------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|

| Peripl                          | Peripherals         |            | STM32U535/545 |               | STM32U5Fx/5Gx | Software                                                                                    | Comments                                                              |  |  |

| Flash memory <sup>(1)</sup>     | Size (bytes)        | Up to 512K | Up to 2M      | Up to         | o 4M          | Yes                                                                                         | -                                                                     |  |  |

| riasii illemory.                | Bank                |            | Dua           | I             |               | Yes                                                                                         | -                                                                     |  |  |

|                                 | SRAM1               | 192        | 2             | 76            | 68            | Yes                                                                                         | The SRAM2 and SRAM3 are                                               |  |  |

|                                 | SRAM2               |            | 64            |               |               | Yes                                                                                         | contiguous to the SRAM1 and the physical address remains 0x2000000 in |  |  |

|                                 | SRAM3               | N/A        | 512           | 832           |               | Yes                                                                                         | STM32U5 series.                                                       |  |  |

| SRAM<br>(Kbytes) <sup>(2)</sup> | SRAM4               |            | 16            |               |               | Yes                                                                                         | Used for low-power background-<br>autonomous mode in Stop 2 mode.     |  |  |

| , , ,                           | SRAM5               | N/A        | <b>\</b>      | 832           |               | Yes                                                                                         | New on STM32U59x/5Ax/5Fx/5Gx.                                         |  |  |

|                                 | SRAM6               |            | N/A           |               | 512           | Yes                                                                                         | Only on STM32U5Fx/5Gx.                                                |  |  |

|                                 | BKPSRAM             | 2          |               |               |               | Yes                                                                                         | -                                                                     |  |  |

|                                 | Number of instances | 2          |               |               |               | Yes                                                                                         | -                                                                     |  |  |

| GTZC                            | MPCWM resources     | 2          | 5             | (             | 6             | Mostly                                                                                      | New feature for HSPI on STM32U59x/5Ax/5Fx/5Gx.                        |  |  |

|                                 | MPCBB resources     | 3          | 4             | 5             | 6             | Mostly                                                                                      | New feature for SRAM5 and SRAM6 on STM32U59x/5Ax/5Fx/5Gx.             |  |  |

| ICACHE                          | Size (Kbytes)       | 8          |               | 3             | 2             | Yes                                                                                         | Same features                                                         |  |  |

| DCACHE                          | DCACHE1             | 4          |               | 1             | 6             | Yes                                                                                         | Same features                                                         |  |  |

| (Kbytes) <sup>(3)</sup> DCACHE2 |                     | N/A        | <b>\</b>      | 1             | 6             | No                                                                                          | New only on STM32U599/5A9/5Fx/5Gx for GPU2D.                          |  |  |

| PWR <sup>(4)</sup>              |                     | Yes        |               |               | Yes           | Additional supplies (V <sub>DDDSI</sub> , V <sub>DD11DSI</sub> , V <sub>DD11USB</sub> ) for |                                                                       |  |  |

|                                 |                     |            |               |               |               |                                                                                             | STM32U59x/5Ax/5Fx/5Gx.                                                |  |  |

AN5766 - Rev 1 page 4/27

|                                                                       |                                              |                                      |                                      |                                               |          | Compatibility                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|-----------------------------------------------------------------------|----------------------------------------------|--------------------------------------|--------------------------------------|-----------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Peripherals                                                           | STM32U535/545                                | STM32U575/585                        | STM32U59x/5Ax                        | STM32U5Fx/5Gx                                 | Software | Comments                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| RCC <sup>(5)</sup>                                                    |                                              | Yes                                  | 3                                    |                                               | Yes      | New features on STM32U59x/5Ax/5Fx/5Gx: new HSPI1 kernel clock to manage the HSPI peripheral, new OTG_HS kernel clock to manage the USB High Speed.  New features only on STM32U599/5A9/5Fx/5Gx: new clock for DSI and LTDC interfaces.  Bits only on STM32U59x/5Ax/5Fx/5Gx: for the GPU2D, GFXMMU, GPIOJ, HSPI, USART6, I2C6, I2C5, DSI, LTDC, DCACHE2, and SRAM5.  Bits only on STM32U5Fx/5Gx: for the JPEG, GFXTIM, and SRAM6. |  |  |

| CRS                                                                   |                                              | Yes                                  | 3                                    |                                               | Yes      | Only an external HSE is used as input for the USB peripheral on STM32U59x/5Ax/5Fx/5Gx.                                                                                                                                                                                                                                                                                                                                           |  |  |

| GPIOs number<br>LPGPIOs number<br>Wake-up pins<br>I/Os down to 1.08 V | Up to 82<br>Up to 16<br>Up to 23<br>Up to 14 | Up to 136 Up to 16 Up to 24 Up to 14 | Up to 151 Up to 16 Up to 24 Up to 14 | Up to 151<br>Up to 16<br>Up to 24<br>Up to 14 | Yes      | Additional I/Os port J on STM32U59x/5Ax/5Fx/5Gx.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| SYSCFG <sup>(6)</sup>                                                 |                                              | Yes                                  | 3                                    |                                               | Yes      | New features for USB HS PHY and HSPI on STM32U59x/5Ax/5Fx/5Gx.                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| GPDMA <sup>(7)</sup>                                                  |                                              | Yes                                  |                                      |                                               | Yes      | New triggers and requests on STM32U59x/5Ax/5Fx/5Gx.                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| LPDMA                                                                 |                                              | Yes                                  | 3                                    |                                               | Yes      | Same features                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| DMA2D                                                                 |                                              | Yes                                  | 3                                    |                                               | Yes      | New triggers interconnection on STM32U59x/5Ax/5Fx/5Gx.                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| GFXMMU <sup>(8)</sup>                                                 | N/A                                          |                                      | Up                                   | to 1                                          | No       | New peripheral on STM32U599/5A9/5Fx/5Gx.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| GFXTIM <sup>(9)</sup>                                                 |                                              | N/A                                  |                                      | Yes                                           | No       | New peripheral onSTM32U5Fx/5Gx.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| NVIC (number) <sup>(10)</sup>                                         | Up to 130 interrupts                         | Up to 141 interrupts                 | Up to 154                            | interrupts                                    | Yes      | New features on STM32U59x/5Ax/5Fx/5Gx.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| EXTI                                                                  |                                              | Yes                                  | 3                                    |                                               | Yes      | -                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| CRC                                                                   |                                              | Yes                                  | 3                                    |                                               | Yes      | -                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| CORDIC                                                                |                                              | Yes                                  | 3                                    |                                               | Yes      | -                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| FMAC                                                                  |                                              | Yes                                  | 3                                    |                                               | Yes      | -                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| FSMC                                                                  | N/A                                          |                                      | Yes                                  |                                               | Yes      | Same features <sup>(11)</sup>                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| OCTOSPI                                                               | 1                                            |                                      | 2                                    |                                               | Yes      | Same features                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| OCTOSPIM                                                              | N/A                                          |                                      | Yes                                  |                                               | Yes      | Same features                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| HSPI <sup>(12)</sup>                                                  | N/A                                          |                                      | Up                                   | to 1                                          | No       | New peripheral on STM32U599/5A9/5Fx/5Gx <sup>(11)</sup> .                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Communication interfaces SAI                                          | 1                                            |                                      | 2                                    |                                               | Yes      | _(11)                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

AN5766 - Rev 1 page 5/27

|                          |                     |                               |                                  |                                |               |               | Compatibility                                                                                            |  |

|--------------------------|---------------------|-------------------------------|----------------------------------|--------------------------------|---------------|---------------|----------------------------------------------------------------------------------------------------------|--|

| Perip                    | herals              | STM32U535/545                 | STM32U575/585                    | STM32U59x/5Ax                  | STM32U5Fx/5Gx | Software      | Comments                                                                                                 |  |

|                          | I2C                 | 4                             |                                  | (                              | 5             | Yes           | New I2C5 and I2C6 on STM32U59x/5Ax/5Fx/5Gx <sup>(11)</sup> .                                             |  |

|                          | USART/UART          | 4                             | 5                                | 6                              |               | Yes           | New USART6 on<br>STM32U59x/5Ax/5Fx/5Gx.                                                                  |  |

|                          | LPUART              |                               | 1                                |                                |               | Yes           | -                                                                                                        |  |

|                          | SPI                 |                               | 3                                |                                |               | Yes           | -                                                                                                        |  |

|                          | FDCAN               |                               | 1                                |                                |               | Yes           | -                                                                                                        |  |

|                          | SDMMC               | 1                             |                                  | 2                              |               | Yes           | -                                                                                                        |  |

| Communication interfaces | MDF                 |                               | 1                                |                                |               | Yes           | Additional features for ADC2 on STM32U59x/5Ax/5Fx/5Gx.                                                   |  |

|                          | ADF                 |                               | 1                                |                                |               | Yes           | Additional features for ADC2 on STM32U59x/5Ax/5Fx/5Gx.                                                   |  |

|                          | DCMI                |                               | Yes                              | i                              |               | Yes           | _(11)                                                                                                    |  |

|                          | PSSI                |                               | Yes                              | i                              |               | Yes           | _(11)                                                                                                    |  |

|                          | USB <sup>(13)</sup> | FS with clock recovery system | OTG FS<br>with clock<br>recovery | OTG HS with embedded PHY clock |               | No            | -                                                                                                        |  |

|                          | USB Type-C®         | N/A                           | Yes                              |                                | Yes           | -             |                                                                                                          |  |

| DL                       | YB                  | Yes                           |                                  |                                | Yes           | Same features |                                                                                                          |  |

|                          | Instance            | 4                             |                                  | ,                              |               | Vaa           | New ADC2 on                                                                                              |  |

| 14-bit ADC               | Instance            | 1                             |                                  | 4                              | 2             | Yes           | STM32U59x/5Ax/5Fx/5Gx.                                                                                   |  |

|                          | Number of channels  | Up to 20                      |                                  |                                | Yes           | -             |                                                                                                          |  |

|                          | Instance            |                               | 1                                |                                |               | Yes           | -                                                                                                        |  |

| 12-bit ADC               | Number of channels  | Up to 21                      | Up to 21                         |                                |               | Yes           | -                                                                                                        |  |

| 12-bit                   | DAC                 |                               | 2                                |                                |               | Yes           | -                                                                                                        |  |

| Internal voltage         | reference buffer    |                               | 1                                |                                |               | Yes           | -                                                                                                        |  |

| VREI                     | FBUF                |                               | 1                                |                                |               | Yes           | -                                                                                                        |  |

| Ultra-low-power co       | omparator (COMP)    | 1                             |                                  | 2                              |               | Yes           | -                                                                                                        |  |

| Operational am           | plifier (OPAMP)     | 1                             |                                  | 2                              |               | Yes           | -                                                                                                        |  |

| LTDC <sup>(14)</sup>     |                     | N/A                           |                                  | Ye                             | es            | No            | New peripheral only for STM32U599/5A9/5Fx/5Gx <sup>(11)</sup> .                                          |  |

| DSI <sup>(15)</sup>      |                     | N/A                           |                                  | Ye                             | es            | No            | New peripheral only for STM32U599/5A9/5F9/5G9 <sup>(11)</sup> .                                          |  |

| GPU2D <sup>(16)</sup>    |                     | N/A                           |                                  | Yes                            |               | No            | New peripheral only for STM32U599/5A9/5Fx/5Gx.  Vector graphics feature only available on STM32U5Fx/5Gx. |  |

| JPE                      | G <sup>(17)</sup>   |                               | N/A                              |                                | Yes           | No            | New peripheral onSTM32U5Fx/5Gx.                                                                          |  |

| TS                       | SC                  |                               | Yes                              | i                              |               | Yes           | -                                                                                                        |  |

AN5766 - Rev 1 page 6/27

|                |                                   | ις.           | 2                                                       | ×        | ×        |                                                                | Compatibility                          |                                        |                                        |

|----------------|-----------------------------------|---------------|---------------------------------------------------------|----------|----------|----------------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|

| Perip          | pherals                           | STM32U535/545 | STM32U535/545 STM32U575/585 STM32U59x/5Ax STM32U5Fx/5Gx |          | Software | Comments                                                       |                                        |                                        |                                        |

| Number of capa | citive sensing pins               | Up to 20      |                                                         | Up to 24 |          | Yes                                                            | -                                      |                                        |                                        |

| Random ger     | nerator (RNG)                     |               | Yes                                                     | 3        |          | Yes                                                            | -                                      |                                        |                                        |

| А              | ES                                |               | Yes                                                     | 6        |          | Yes                                                            | Feature only on STM32U545/585/5Ax/5Gx. |                                        |                                        |

| SA             | AES                               |               | Yes                                                     | 6        |          | Yes                                                            | Feature only on STM32U545/585/5Ax/5Gx. |                                        |                                        |

| HA             | ASH                               |               | Yes                                                     | 3        |          | Yes                                                            | -                                      |                                        |                                        |

| OTF            | OTFDEC Yes                        |               | OTFDEC                                                  |          | Yes      |                                                                | Yes                                    | Feature only on STM32U545/585/5Ax/5Gx. |                                        |

| Р              | PKA Yes                           |               | Yes                                                     |          |          | Yes                                                            |                                        | Yes                                    | Feature only on STM32U545/585/5Ax/5Gx. |

|                | Advanced control                  |               | 2 (16 b                                                 | oits)    |          | Mostly                                                         | New external trigger signals for ADC2. |                                        |                                        |

|                | General purpose                   |               | 3 (16bits)<br>4 (32 bits)                               |          | Mostly   | New external trigger signals for DCMI and LTDC. Same features. |                                        |                                        |                                        |

|                | Basic                             |               | 2 (16 b                                                 | oits)    |          | Yes                                                            | -                                      |                                        |                                        |

| _              | Low power<br>(LPTIM)              |               | 4 (16 t                                                 | oits)    |          | Yes                                                            | -                                      |                                        |                                        |

| Timers         | SysTick                           |               | 2                                                       |          |          | Yes                                                            | -                                      |                                        |                                        |

|                | Infrared (IRTIM)                  |               | 2                                                       |          |          | Yes                                                            | -                                      |                                        |                                        |

|                | Independent<br>watchdog<br>(IWDG) |               | 1                                                       |          |          | Yes                                                            | -                                      |                                        |                                        |

|                | System window watchdog (WWDG)     |               | 1                                                       |          |          | Yes                                                            | -                                      |                                        |                                        |

| R              | TC                                | Yes           |                                                         |          |          | Yes                                                            | -                                      |                                        |                                        |

| Tamper         | External pins                     |               | Up to                                                   | 8        |          | Yes                                                            | -                                      |                                        |                                        |

| ramper         | Internal events                   |               | 11                                                      |          |          | Yes                                                            | -                                      |                                        |                                        |

- 1. Refer to Section 3.3 for more details.

- 2. Refer to Section 3.4 for more details.

- 3. Refer to Section 3.5 for more details.

- 4. Refer to Section 3.6 for more details.

- 5. Refer to Section 3.7 for more details.

- 6. Refer to Section 3.8 for more details.

- 7. Refer to Section 3.9 for more details.

- 8. Refer to Section 3.10 for more details.9. Refer to Section 3.17 for more details.

- 3. Refer to economic at the more detailed

- 10. Refer to Section 3.11 for more details.

- 11. Refer to datasheet for availability on specific packages.

- 12. Refer to Section 3.12 for more details.

- 13. Refer to Section 3.18 for more details.

- 14. Refer to Section 3.13 for more details.

AN5766 - Rev 1 page 7/27

- 15. Refer to Section 3.14 for more details.

- 16. Refer to Section 3.15 for more details.

- 17. Refer to Section 3.16 for more details.

## 3.2 Memory mapping

The table below compares register boundary addresses of the peripherals for STM32U5 series microcontrollers.

Table 2. Peripheral register boundary addresses comparison

'-' means absent; 'X' means present

| Bus      | s absent; 'X' means p | Nonsecure address         | Secure address            | STM32U535/545 | STM32U575/585 | STM32U59x/5Ax | STM32U5Fx/5Gx |

|----------|-----------------------|---------------------------|---------------------------|---------------|---------------|---------------|---------------|

|          | HSPI1                 | 0x420D 3400 – 0x420D 37FF | 0x520D 3400 – 0x520D 37FF | -             | -             | Х             | X             |

|          | OCTOSPI2              | 0x420D 2400 – 0x420D 27FF | 0x520D 2400 – 0x520D 27FF | -             | Х             | Х             | Х             |

|          | FMC                   | 0x420D 0400 - 0x420D 07FF | 0x520D 0400 – 0x520D 07FF | -             | Х             | Х             | Х             |

|          | DLYBOS2               | 0x420C F400 – 0x420C F7FF | 0x520C F400 – 0x520C F7FF | -             | Х             | Х             | Х             |

|          | SDMMC2                | 0x420C 8C00 - 0x420C 8FFF | 0x520C 8C00 – 0x520C 8FFF | -             | Х             | Х             | Х             |

| 01       | DLYBSD2               | 0x420C 8800 - 0x420C 8BFF | 0x520C 8800 – 0x520C 8BFF | -             | Х             | Х             | Х             |

| AHB2     | OTFDEC2               | 0x420C 5400 - 0x420C 57FF | 0x520C 5400 – 0x520C 57FF | -             | Х             | Х             | Х             |

|          | OCTOSPIM              | 0x420C 4000 – 0x420C 43FF | 0x520C 4000 – 0x520C 43FF | -             | Х             | Х             | Х             |

|          | OTG_HS                | 0x4204 0000 – 0x4205 FFFF | 0x5204 0000 – 0x5205 FFFF | -             | -             | Х             | Х             |

|          | OTG_FS                | 0x4204 0000 – 0x420B FFFF | 0x5204 0000 – 0x520B FFFF | -             | Х             | -             | -             |

|          | GPIOJ                 | 0x4202 2400 – 0x4202 27FF | 0x5202 2400 – 0x5202 27FF | -             | -             | Х             | Х             |

|          | GPIOI                 | 0x4202 2000 – 0x4202 23FF | 0x5202 2000 – 0x5202 23FF | -             | Х             | Х             | Х             |

|          | GPIOF                 | 0x4202 1400 – 0x4202 17FF | 0x5202 1400 – 0x5202 17FF | -             | Х             | Х             | Х             |

|          | GTZC1_MPCBB6          | 0x4003 3800 - 0x4003 3BFF | 0x5003 3800 – 0x5003 3BFF | -             | -             | -             | Х             |

|          | GTZC1_MPCBB5          | 0x4003 3C00 - 0x4003 3FFF | 0x5003 3C00 - 0x5003 3FFF | -             | -             | Х             | Х             |

|          | GTZC1_MPCBB3          | 0x4003 3400 - 0x4003 37FF | 0x5003 3400 – 0x5003 37FF | -             | Х             | Х             | Х             |

| <u>1</u> | DCACHE2               | 0x4003 1800 – 0x4003 1BFF | 0x5003 1800 – 0x5003 1BFF | -             | -             | Х             | Х             |

| AHB1     | GPU2D                 | 0x4002 F000 – 0x4002 FFFF | 0x5002 F000 – 0x5002 FFFF | -             | -             | Х             | Х             |

|          | GFXMMU                | 0x4002 C000 – 0x4002 EFFF | 0x5002 C000 – 0x5002 EFFF | -             | -             | Х             | Х             |

|          | DMA2D                 | 0x4002 B000 – 0x4002 BBFF | 0x5002 B000 – 0x5002 BBFF | -             | Х             | Х             | Х             |

|          | JPEG                  | 0x4002 A000 – 0x4002 AFFF | 0x5002 A000 – 0x5002 AFFF | -             | -             | -             | Х             |

|          | DSI                   | 0x4001 6C00 - 0x4001 7BFF | 0x5001 6C00 – 0x5001 7BFF | -             | -             | Х             | Х             |

|          | LTDC                  | 0x4001 6800 – 0x4001 6BFF | 0x5001 6800 – 0x5001 6BFF | -             | -             | Х             | Х             |

| B2       | GFXTIM                | 0x4001 6400 – 0x4001 67FF | 0x5001 6400 – 0x5001 67FF | -             | -             | -             | Х             |

| APB2     | USB RAM               | 0x4001 6400 – 0x4001 6BFF | 0x5001 6400 – 0x5001 6BFF | Х             | -             | -             | -             |

|          | USB                   | 0x4001 6000 – 0x4001 63FF | 0x5001 6000 – 0x5001 63FF | Х             | -             | -             | -             |

|          | SAI2                  | 0x4001 5800 – 0x4001 5BFF | 0x5001 5800 – 0x5001 5BFF | -             | Х             | Х             | Х             |

| 31       | UCPD1                 | 0x4000 DC00 – 0x4000 DFFF | 0x5000 DC00 – 0x5000 DFFF | -             | Х             | Х             | Х             |

| APB1     | I2C6                  | 0x4000 9C00 – 0x4000 9FFF | 0x5000 9C00 – 0x5000 9FFF | -             | -             | Х             | Х             |

AN5766 - Rev 1 page 8/27

| Bus | Peripherals | Nonsecure address         | Secure address            | STM32U535/545 | STM32U575/585 | STM32U59x/5Ax | STM32U5Fx/5Gx |

|-----|-------------|---------------------------|---------------------------|---------------|---------------|---------------|---------------|

| _   | I2C5        | 0x4000 9800 – 0x4000 9BFF | 0x5000 9800 – 0x5000 9BFF | -             | -             | Х             | Х             |

| APB | USART6      | 0x4000 6400 – 0x4000 67FF | 0x5000 6400 – 0x5000 67FF | -             | -             | Х             | Х             |

|     | USART2      | 0x4000 4400 – 0x4000 47FF | 0x5000 4400 – 0x5000 47FF | -             | Х             | Х             | Х             |

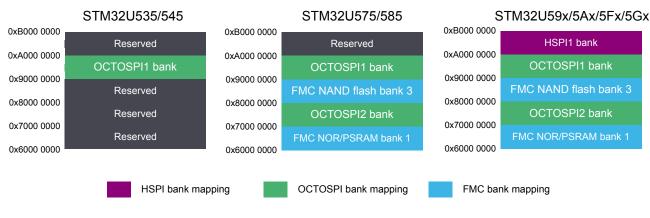

The figure below presents the external memory-mapping differences for STM32U5 series microcontrollers.

Figure 1. External memory-mapping differences for STM32U5 series microcontrollers

## 3.3 Flash memory

The table below details the flash memory differences for STM32U5 series microcontrollers.

Table 3. Flash memory differences for STM32U5 series microcontrollers

| Flash n             | nemory       | STM32U535/545                                                                                                                                                  | STM32U575/585                                                                                        | STM32U59x/5Ax/5Fx/5Gx                                                                                |

|---------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Main/program        | flash memory | Up to 512 Kbytes Split in two banks Pages of 8 Kbytes per bank                                                                                                 | Up to 2 Mbytes Split in two banks Pages of 8 Kbytes per bank                                         | Up to 4 Mbytes Split in two banks Pages of 8 Kbytes per bank                                         |

| Management          | Bank 1       | 0x800 0000 – 0x803 FFFF<br>(for 512-Kbyte devices)<br>0x800 0000 – 0x801 FFFF<br>(for 256-Kbyte devices)<br>0x800 0000 – 0x800 FFFF<br>(for 128-Kbyte devices) | 0x800 0000 – 0x80F FFFF<br>(for 2-Mbyte devices)<br>0x800 0000 – 0x807 FFFF<br>(for 1-Mbyte devices) | 0x800 0000 – 0x81F FFFF<br>(for 4-Mbyte devices)<br>0x800 0000 – 0x80F FFFF<br>(for 2-Mbyte devices) |

| Memory organization | Bank 2       | 0x804 0000 – 0x807 FFFF<br>(for 512-Kbyte devices)<br>0x802 0000 – 0x803 FFFF<br>(for 256-Kbyte devices)<br>0x801 0000 – 0x801 FFFF<br>(for 128-Kbyte devices) | 0x810 0000 – 0x81F FFFF<br>(for 2-Mbyte devices)<br>0x808 0000 – 0x80F FFFF<br>(for 1-Mbyte devices) | 0x820 0000 – 0x83F FFFF<br>(for 4-Mbyte devices)<br>0x810 0000 – 0x81F FFFF<br>(for 2-Mbyte devices) |

| Feat                | tures        | Dual bank                                                                                                                                                      |                                                                                                      |                                                                                                      |

AN5766 - Rev 1 page 9/27

0540V1

| Flash memory                       | STM32U535/545                                                               | STM32U575/585                                       | STM32U59x/5Ax/5Fx/5Gx |  |  |  |

|------------------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------|-----------------------|--|--|--|

| Features                           | Read while write (RWW)                                                      |                                                     |                       |  |  |  |

| Read access                        | Read access of 128 bits (+ 9-                                               | bit ECC)                                            |                       |  |  |  |

| Wait states                        | Up to four (depending on the                                                | supply voltage and the frequen                      | cy)                   |  |  |  |

|                                    | Write protection: two areas pe                                              | r bank                                              |                       |  |  |  |

|                                    | Four levels of readout protection (RDP)                                     |                                                     |                       |  |  |  |

|                                    | Privileged block-based volatile areas with page granularity                 |                                                     |                       |  |  |  |

| Protections                        | Secure protections when TrustZone <sup>®</sup> is activated:                |                                                     |                       |  |  |  |

|                                    | up to two secure watermark-based nonvolatile areas                          |                                                     |                       |  |  |  |

|                                    | <ul> <li>up to two secure hide p</li> <li>secure block-based vol</li> </ul> | rotection areas<br>atile areas with page granularit | V                     |  |  |  |

| One time programmable (OTP) memory | 512 bytes                                                                   | Paga grantania.                                     | ,                     |  |  |  |

|                                    | 0x4002 2000 – 0x4002 23FF                                                   | (nonsecure)                                         |                       |  |  |  |

| Register interface                 | 0x5002 2000 - 0x5002 23FF (secure)                                          |                                                     |                       |  |  |  |

|                                    | 000002 2000 - 000002 251 1                                                  | (Secure)                                            |                       |  |  |  |

## 3.4 RAM memory

The table below details the RAM memory differences for STM32U5 series microcontrollers.

Table 4. RAM memory differences for STM32U5 series microcontrollers

| R       | AM       | STM32U535/545      | STM32U575/585                                                       | STM32U59x/5Ax                         | STM32U5Fx/5Gx       |  |  |

|---------|----------|--------------------|---------------------------------------------------------------------|---------------------------------------|---------------------|--|--|

|         | SRAM1    | 192                | Kbytes                                                              | 768 k                                 | Cbytes              |  |  |

|         | SRAM2    |                    | 64 KI                                                               | bytes                                 |                     |  |  |

| Size    | SRAM3    | N/A                | 512 Kbytes                                                          | 832 k                                 | Cbytes              |  |  |

| Size    | SRAM4    |                    | 16 KI                                                               | bytes                                 |                     |  |  |

|         | SRAM5    | N                  | J/A                                                                 | 832 k                                 | Cbytes              |  |  |

|         | BKPSRAM  |                    | 2 Kb                                                                | ytes                                  |                     |  |  |

|         | SRAM1    | 0x2000 0000 – 0x20 | 0000 – 0x2002 FFFF (nonsecure) 0x2000 0000 – 0x200B FFFF (nonsecure |                                       |                     |  |  |

|         | SIVAIVIT | 0x3000 0000 – 0x   | 3002 FFFF (secure)                                                  | 0x3000 0000 – 0x3                     | 300B FFFF (secure)  |  |  |

|         | SRAM2    | 0x2003 0000 - 0x20 | 003 FFFF (nonsecure)                                                | 0x200C 0000 - 0x20                    | OC FFFF (nonsecure) |  |  |

|         | OTVAIVIZ | 0x3003 0000 – 0x   | 3003 FFFF (secure)                                                  | 0x300C 0000 - 0x300C FFFF (secure)    |                     |  |  |

| Address | SRAM3    | N/A                | 0x2004 0000 – 0x200B<br>FFFF (nonsecure)                            | 0x200D 0000 – 0x2019 FFFF (nonsecure) |                     |  |  |

| Address | SIVAIVIS | IV/A               | 0x3004 0000 - 0x300B<br>FFFF (secure)                               | 0x300D 0000 – 0x3019 FFFF (secure)    |                     |  |  |

|         | SRAM4    |                    | 0x2800 0000 - 0x280                                                 | 00 3FFF (nonsecure)                   |                     |  |  |

|         | SKAIVI4  |                    | 0x3800 0000 – 0x3                                                   | x3800 3FFF (secure)                   |                     |  |  |

|         | SRAM5    |                    | I/A                                                                 | 0x201A 0000 – 0x20                    | 26 FFFF (nonsecure) |  |  |

|         | OTVAIVIO | '                  | W/A                                                                 | 0x301A 0000 – 0x3                     | 3026 FFFF (secure)  |  |  |

|         |          |                    | ECC on SRAM2, SRA                                                   | M3 <sup>(1)</sup> , and BKPSRAM       |                     |  |  |

|         |          |                    | Readout <sub>I</sub>                                                | protection                            |                     |  |  |

| Г       | tures    |                    | Write protection 1-Kbyte                                            | e granularity for SRAM2               |                     |  |  |

| rea     | luies    |                    | Wait states of                                                      | configuration                         |                     |  |  |

|         |          |                    | Hardware erase wi                                                   | ith RDP regression                    |                     |  |  |

|         |          |                    | System re                                                           | eset erase                            |                     |  |  |

AN5766 - Rev 1 page 10/27

| RAM      | STM32U535/545 | STM32U575/585                | STM32U59x/5Ax             | STM32U5Fx/5Gx |

|----------|---------------|------------------------------|---------------------------|---------------|

| Features | H             | ardware erase in tamper dete | ection (SRAM2 and BKPSRAI | M)            |

<sup>1.</sup> SRAM3 is not available on STM32U535/545 devices.

## 3.5 Data cache (DCACHE)

The table below details the data cache (DCACHE) differences for STM32U5 series microcontrollers.

Table 5. DCACHE differences for STM32U5 series microcontrollers

| DCA               | CHE                               | STM32U535/545/575/585 | STM32U59x/5Ax/5Fx/5Gx   |  |

|-------------------|-----------------------------------|-----------------------|-------------------------|--|

| Nur               | nber                              | 1                     | <b>2</b> <sup>(1)</sup> |  |

|                   | Number of ways                    | 2                     | 4                       |  |

|                   | Cache size                        | 4 Kbytes              | 16 Kbytes               |  |

| Features          | Cache line width                  | 16 bytes              | 32 bytes                |  |

|                   | Data size of AHB master interface | 32                    | bits                    |  |

| DCACHE registers  | DCACHE_CMDRSADDRR                 | CMDSTARTADDR [31:4]   | CMDSTARTADDR [31:5]     |  |

| DONOTIL TEGISTETS | DCACHE_CMDREADDRR                 | CMDENDADDR [31:4]     | CMDENDADDR [31:5]       |  |

<sup>1.</sup> DCACHE2 only available on STM32U599/5A9/5Fx/5Gx devices.

Note:

In STM32U599/5A9/5Fx/5Gx, the data cache 2 (DCACHE2) is placed on the AHB bus driven by the GPU2D M0 port.

## 3.6 Power control (PWR)

The table below details the power control (PWR) differences for STM32U5 series microcontrollers.

Table 6. PWR differences for STM32U5 series microcontrollers

'-' means absent; 'X' means present

|            | Power control registers | STM32U535/545 | STM32U575/585 | STM32U59x/5Ax | STM32U5Fx/5Gx |

|------------|-------------------------|---------------|---------------|---------------|---------------|

|            | Bit15: FORCE_USBPWR     | -             | -             | X             | X             |

| PWR_CR1    | Bit13: SRAM6PD          | -             | -             | -             | X             |

| T WIC_OICT | Bit12: SRAM5PD          | -             | -             | X             | X             |

|            | Bit 10: SRAM3PD         | -             | X             | Х             | X             |

|            | Bit 26: JPEGRAMPDS      | -             | -             | -             | Х             |

|            | Bit 25: DSIRAMPDS       | -             | -             | Х             | Х             |

| DWD CD2    | Bit 24: GPRAMPDS        | -             | -             | Х             | Х             |

| PWR_CR2    | Bits[23:16]: SRAM3PDSx  | -             | X             | Х             | Х             |

|            | Bit 10: DMA2DRAMPDS     | -             | X             | Х             | Х             |

|            | Bit 7: DC2RAMPDS        | -             | -             | Х             | Х             |

| DWD VOOD   | Bit 21: VDD11USBDIS     | -             | -             | Х             | Х             |

| PWR_VOSR   | Bit 20: USBBOOSTEN      | -             | -             | Х             | Х             |

AN5766 - Rev 1 page 11/27

|            | Power control registers | STM32U535/545 | STM32U575/585   | STM32U59x/5Ax    | STM32U5Fx/5Gx    |

|------------|-------------------------|---------------|-----------------|------------------|------------------|

| PWR_VOSR   | Bit 19: USBPWREN        | -             | -               | X                | X                |

| T WK_VOOK  | Bit 13: USBBOOSTRDY     | -             | -               | X                | Х                |

| DWB LICDDB | Bit 1: UCPD_STBY        | -             | X               | Х                | Х                |

| PWR_UCPDR  | Bit 0: UCPD_DBDIS       | -             | Х               | X                | Х                |

|            | PWR_PUCRF               |               |                 | Х                | Х                |

|            | PWR_PUCRI               |               | Bits [7:0]: PUy | Bits [15:0]: PUy | Bits [15:0]: PUy |

|            | PWR_PUCRJ               |               | -               | X                | X                |

|            | Bits [28:16]: SRAM5PDSx | -             | -               | Х                | Х                |

| PWR_CR4    | Bits [14:10]: SRAM3PDSx | -             | X               | X                | Х                |

|            | Bits [7:0]: SRAM6PDSx   | -             | -               | -                | Х                |

After reset, the regulator is the LDO, in range 4. Switching to SMPS provides lower consumption at high voltage. It is possible to switch from LDO to SMPS, or from SMPS to LDO in any range, by configuring the REGSEL bit in PWR\_CR3.

On STM32U59x/5Ax/5Fx/5Gx devices only, when using the device at extended temperature ranges (from 85 °C to 125 °C), it is necessary to reduce the system frequency below 100 MHz before switching from LDO to SMPS. When exiting the Stop or Standby mode, the regulator is the same than when entering low-power modes. The voltage range is the range 4.

### Dynamic voltage-scaling management

On STM32U59x/5Ax/5Fx/5Gx devices only, the maximum frequency increase or decrease in range 1 (1.2 V) is 80 MHz.

To increase the frequency in range 1 above 80 MHz, follow the steps below:

- 1. Divide the system clock by two, using the AHB prescaler (HPRE = 0b1000 in RCC\_CFGR2).

- 2. Configure and enable the PLL1 if needed.

- 3. Select PLL1 as system clock source (SW = 0b11 in RCC\_CFGR1).

- Wait for 3 μs.

- 5. Set the AHB prescaler to 1 (HPRE = 0b0000 in RCC\_CFGR2).

When running at frequencies higher than 80 MHz in range 1, follow the steps below to decrease the frequency:

- 1. Divide the system clock by two, using the AHB prescaler (HPRE = 0b1000 in RCC CFGR2).

- 2. Wait for 3 μs.

- 3. Define the lower speed clock as system clock source.

- 4. Set the AHB prescaler back to 1 (HPRE = 0b0000 in RCC CFGR2).

In the other ranges, there is no limitation during system frequency increase or decrease.

AN5766 - Rev 1 page 12/27

### Peripheral voltage monitoring (PVM)

Due to the difference on the USB peripheral between the STM32U535/545/575/585 with a USB Full Speed (FS) and the STM32U59x/5Ax/5Fx/5Gx with a USB High Speed (HS), the following sequence must be done before using the USB OTG\_HS peripheral on STM32U59x/5Ax/5Fx/5Gx devices:

- If V<sub>DDUSB</sub> is independent from V<sub>DD</sub>:

- a. Enable the UVM by setting UVMEN bit in PWR SVMCR.

- b. Wait for the UVM wake-up time.

- c. Wait until VDDUSBRDY bit is set in PWR SVMSR.

- d. Disable the UVM for consumption saving (optional).

- 2. Set the USV bit in PWR\_SVMCR to remove the  $V_{DDUSB}$  power isolation.

- Make sure that the voltage scaling is in range 1 or range 2 (using VOS [1:0] bits in PWR\_VOSR).

- 4. Make sure that the EPOD booster is in range 1 or range 2 (using PLL1MBOOST [3:0] in RCC\_PLL1CFGR).

- 5. Enable the USB internal power by setting the USBPWREN and USBBOOSTEN bits in the PWR\_VOSR.

- 6. Wait for USBBOOSTRDY in PWR VOSR to be set.

#### **USB** power management in low-power modes

On STM32U59x/5Ax/5Fx/5Gx devices only, in Stop 0 and Stop 1 modes, it is possible to keep the OTG\_HS configuration by leaving the USBPWREN bit set. This allows the OTG\_HS to wake up the MCU from Stop mode. However, to decrease the power consumption, it is recommended to shut off the OTG\_HS before entering Stop 0 or Stop 1 mode.

In Stop 2 and Stop 3 modes, it is not possible to keep the OTG\_HS configuration. The OTG\_HS must be shut off before entering Stop 2 or Stop 3 mode.

To shut off the OTG\_HS before entering Stop mode, follow the steps below:

- 1. Clear the USNPWREN and USBBOOSTEN bits in PWR VOSR.

- Request entry in Stop mode.

Upon wake-up from Stop mode, and before configuring the OTG\_HS:

- 1. Make sure that the voltage scaling is in range 1 or range 2 (using VOS [1:0] in PWR\_VOSR).

- 2. Make sure that the EPOD booster clock is enabled using PLL1MBOOST [3:0] in RCC PLL1CFGR.

- 3. Enable the USB internal power by setting the USBPWREN and USBBOOSTEN bits in PWR\_VOSR.

- 4. Wait for USBBOOSTRDY in PWR\_VOSR to be set.

AN5766 - Rev 1 page 13/27

## 3.7 Reset and clock control (RCC)

The table below details the RCC (reset and clock controller) differences for STM32U5 series microcontrollers.

Table 7. RCC differences for STM32U5 series microcontrollers

| RCC                        | STM32U535/545                                 | STM32U575/585                                           | STM32U59x/5Ax    | STM32U5Fx/5Gx                |  |  |

|----------------------------|-----------------------------------------------|---------------------------------------------------------|------------------|------------------------------|--|--|

| UCPD1                      | N/A                                           |                                                         | HSI16            |                              |  |  |

| USARTx <sup>(1)</sup>      |                                               | PCL<br>LS<br>HSI<br>SYS                                 | E<br>16          |                              |  |  |

| 12Cx <sup>(2)</sup>        |                                               | PCLK1<br>HSI16<br>SYSCLK<br>MSI kernel clock            |                  |                              |  |  |

| OCTOSPIx <sup>(3)</sup>    |                                               | SYSCLK<br>MSI kernel clock<br>PLL1/Q<br>PLL2/Q          |                  |                              |  |  |

| SAIx <sup>(3)</sup>        |                                               | AUDIOCLK PLL1/P PLL2/P PLL3/P HSI16                     |                  |                              |  |  |

| SDMMCx <sup>(3)</sup>      |                                               | PLL1/P<br>PLL1/Q<br>PLL2/Q<br>MSI kernel clock<br>HSI48 |                  |                              |  |  |

| USB                        | MSI kernel clock<br>HSI48<br>PLL1/Q<br>PLL2/Q | N/A                                                     |                  |                              |  |  |

| OTG_FS                     | N/A                                           | MSI kernel clock<br>HSI48<br>PLL1/Q<br>PLL2/Q           | N                | I/A                          |  |  |

| OTG_HS                     | N.                                            | /A                                                      | PLI<br>PLL       | SE<br>L1/P<br>1/2P<br>SE/2   |  |  |

| ADCx <sup>(4)</sup>        |                                               | HC                                                      |                  |                              |  |  |

| DAC1                       |                                               | SYSCLK<br>PLL2/R<br>HSE<br>HSI16<br>MSI kernel clock    |                  |                              |  |  |

| DAC1 sample and hold clock |                                               | LS<br>LS                                                | SI<br>E          |                              |  |  |

| HSPI                       | N.                                            | /A                                                      | PLI<br>PLI       | SCLK<br>_1/Q<br>_2/Q<br>_3/R |  |  |

| LTDC                       | N                                             | /A                                                      | PLL2/R<br>PLL3/R |                              |  |  |

| DSI                        | N                                             | /A                                                      | PLL3/P<br>HSE    |                              |  |  |

| PLL                        |                                               | 3 PLLs (PLL1,                                           | PLL2, PLL3)      |                              |  |  |

AN5766 - Rev 1 page 14/27

- 1. x = 1, 3, 4, 5 for STM32U535/545 x = 1 to 5 for STM32U575/585 x = 1 to 6 for STM32U59x/5Ax/5Fx/5Gx

- 2. x = 1, 2, 4, 5 for STM32U535/545/575/585 x = 1, 2, 4, 5, 6 for STM32U59x/5Ax/5Fx/5Gx

- 3. Refer to datasheet for availability.

- 4. x = 1, 4 for STM32U535/545/575/585 x = 1, 2, 4 for STM32U59x/5Ax/5Fx/5Gx

The table below highlights the RCC (reset and clock controller) registers differences for STM32U5 series microcontrollers.

Table 8. RCC registers differences for STM32U5 series microcontrollers

'-' means absent; 'X' means present

| RCC registers |                             |   |   | STM32U59x/5Ax | STM32U5Fx/5Gx |

|---------------|-----------------------------|---|---|---------------|---------------|

| RCC_CFGR2     | Bits [14:12]: DPRE          | - | - | Χ             | X             |

|               | Bit 20: GPU2DRST            | - | - | Х             | Х             |

| RCC_AHB1RSTR  | Bit 19: GFXMMURST           | - | - | Х             | Х             |

| NOO_ARBINOTIC | Bit 18: DMA2DRST            | - | X | Χ             | X             |

|               | Bit 15: JPEGRST             | - | - | -             | X             |

|               | Bit 28: SDMMC2RST           | - | X | Х             | X             |

|               | Bit 24: OTFDEC2RST          | - | X | Χ             | X             |

| RCC_AHB2RSTR1 | Bit 21: OCTOSPIMRST         | - | X | Χ             | X             |

|               | Bit 14: OTGRST (for OTG_FS) | - | X | Χ             | X             |

|               | Bit 9: GPIOJRST             | - | - | Χ             | X             |

|               | Bit 8:GPIOIRST              | - | Х | Х             | Х             |

|               | Bit 5:GPIOFRST              | - | Х | Х             | Х             |

|               | Bit 12: HSPI1RST            | - | - | Χ             | Х             |

| RCC_AHB2RSTR2 | Bit 8: OCTOSPI2RST          | - | Х | Х             | Х             |

|               | Bit 0: FSMCRST              | - | X | Χ             | X             |

| RCC_APB1RSTR1 | Bit 25: USART6RST           | - | - | Х             | Х             |

| RCC_AFBIRSTR1 | Bit 17: USART2RST           | - | Х | Х             | Х             |

|               | Bit 23: UCPD1RST            | - | Х | Х             | Х             |

| RCC_APB1RSTR2 | Bit 7: I2C6RST              | - | - | Х             | Х             |

|               | Bit 6: I2C5RST              | - | - | Х             | Х             |

|               | Bit 27: DSIRST              | - | - | Х             | Х             |

|               | Bit 26: LTDCRST             | - | - | Х             | Х             |

| RCC_APB2RSTR  | Bit 25:GFXTIMRST            | - | - | -             | Х             |

|               | Bit 24: USBRST              | X | - | -             | -             |

|               | Bit 22: SAI2RST             | - | Х | Х             | Х             |

|               | Bit 21: DCACHE2EN           | - | - | Х             | Х             |

| RCC_AHB1ENR   | Bit 20: GPU2DEN             | - | - | Х             | Х             |

AN5766 - Rev 1 page 15/27

| RCC registers      |                      |   | STM32U575/585 | STM32U59x/5Ax | STM32U5Fx/5Gx |

|--------------------|----------------------|---|---------------|---------------|---------------|

|                    | Bit 19: GFXMMUEN     | - | -             | Х             | Х             |

| RCC_AHB1ENR        | Bit 18: DMA2DEN      | - | Х             | Х             | Х             |

|                    | Bit 15: JPEGEN       | - | -             | -             | Х             |

|                    | Bit 31: SRAM3EN      | - | Х             | Х             | Х             |

|                    | Bit 28: SDMMC2EN     | - | Х             | Х             | Х             |

|                    | Bit 24: OTFDEC2EN    | - | Х             | Х             | Х             |

| RCC_AHB2ENR1       | Bit 21: OCTOSPIMEN   | - | Х             | Х             | Х             |

|                    | Bit 15: OTGHSPHYEN   | - | -             | Х             | Х             |

|                    | Bit 14: OTGEN        | - | Х             | Х             | Х             |

|                    | Bit 9: GPIOJEN       | - | -             | Х             | Х             |

|                    | Bit 8: GPIOIEN       | - | X             | X             | X             |

|                    | Bit 5: GPIOFEN       | - | X             | X             | X             |

| RCC_AHB2ENR2       | Bit 31: SRAM5EN      | - | -             | Х             | Х             |

|                    | Bit 30: SRAM6EN      | - | -             | -             | X             |

|                    | Bit 12: HSPIEN       | - | -             | Х             | Х             |

|                    | Bit 8: OCTOSPI2EN    | - | Х             | Х             | Х             |

|                    | Bit 0: FSMCEN        | - | Х             | Х             | Х             |

| RCC APRIENRI       | Bit 25: USART6EN     | - | -             | Х             | Х             |

| RCC_APB1ENR1       | Bit 17: USART2EN     | - | Х             | Х             | Х             |

|                    | Bit 23: UCPD1EN      | - | Х             | Х             | Х             |

| RCC_APB1ENR2       | Bit 7: I2C6EN        | - | -             | Х             | Х             |

|                    | Bit 6: I2C5EN        | - | -             | Х             | Х             |

|                    | Bit 27: DSIEN        | - | -             | Х             | Х             |

|                    | Bit 26: LTDCEN       | - | -             | Х             | Х             |

| RCC_APB2ENR        | Bit 25: GFXTIMEN     | - | -             | -             | Х             |

|                    | Bit 24: USBEN        | X | -             | -             | -             |

|                    | Bit 22: SAI2EN       | - | Х             | Х             | Х             |

|                    | Bit 21: DCACHE2SMEN  | - | -             | Х             | Х             |

|                    | Bit 20: GPU2DSMEN    | - | _             | Х             | Х             |

| RCC_AHB1SMENR      | Bit 19: GFXMMUSMEN   | - | _             | Х             | Х             |

| _                  | Bit 18: DMA2DSMEN    | - | Х             | Х             | Х             |

|                    | Bit 15: JPEGSMEN     | _ | -             | -             | Х             |

|                    | Bit 31: SRAM3SMEN    | - | Х             | Х             | Х             |

|                    | Bit 28: SDMMC2SMEN   | _ | Х             | Х             | Х             |

| RCC_AHB2SMENR1     | Bit 24: OTFDEC2SMEN  | _ | Х             | Х             | Х             |

| .100_1102001211111 | Bit 21: OCTOSPIMSMEN | - | X             | X             | X             |

|                    | Bit 15: OTGHSPHYSMEN | _ | _             | X             | X             |

AN5766 - Rev 1 page 16/27

| RCC re          | STM32U535/545           | STM32U575/585 | STM32U59x/5Ax | STM32U5Fx/5Gx |   |

|-----------------|-------------------------|---------------|---------------|---------------|---|

|                 | Bit 14: OTGSMEN         | -             | Х             | Х             | Х |

| RCC_AHB2SMENR1  | Bit 9: GPIOJSMEN        | -             | -             | Х             | Х |

| TOO_NIBZOMETAT  | Bit 8: GPIOISMEN        | -             | Х             | Х             | Х |

|                 | Bit 5: GPIOFSMEN        | -             | Х             | Х             | Х |

| RCC_AHB2SMENR2  | Bit 31: SRAM5SMEN       | -             | -             | Х             | Х |