## Boost voltage mode on B-G474E-DPOW1 Discovery kit

#### Introduction

This document describes the contents of the Boost\_VoltageMode\_HW project, a software example running on the B-G474E-DPOW1 hardware. This low-cost and easy-to-use kit is convenient for quick evaluation and application development with STM32G4 Series microcontrollers, a family of devices designed for digital power conversion applications, combining high integration with performance.

The document illustrates how to drive PSU DC-DC Boost converter, with voltage closed-loop control, by describing the steps required to execute the code and to check output signals, using the IAR Embedded Workbench® and STMicroelectronics STM32CubeIDE toolchains. The document describes the boost voltage mode usage with the X-CUBE-DPOWER STM32Cube Expansion Package. Finally, it lists the STM32G474xx capabilities exploited by this application, and how they can be used in larger scale systems.

## 1 General information

This document applies to the STM32G4 Series microcontrollers, based on Arm® cores.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

Caution: At full load, the converter may become hot, so please take care. After measuring the converter's performance, it

is recommended to set the converter to 0% load.

AN5785 - Rev 4 page 2/43

### 2 Hardware board overview

The B-G474E-DPOW1 is a complete digital power starter kit controlled by the STM32G474RET6 microcontroller. The kit helps the user discover the features of digital power including LED dimming, buck or boost with variable load, power delivery (USB type- $C^{TM}$ ), and audio Class-D amplification.

Figure 1. Discovery kit: top (left) and bottom (right) sides

### 2.1 Buck-boost converter

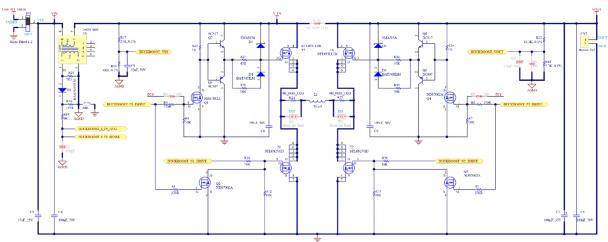

This kit embeds a buck and a boost converter. There are either a boost or either a buck switching FETs at each side of the converter's inductor. The extract from the schematic shown in Figure 2 identifies the relevant switches. The full schematic is available on www.st.com.

Figure 2. Buck-boost power stage schematic

AN5785 - Rev 4 page 3/43

### 2.2 Onboard load

This board includes two parallel load banks at the output of the converter, as shown in Figure 3.

Figure 3. Onboard load banks controlled via MOSFETs

The load banks are controlled by the MCU by toggling the PC14 and PC15 outputs, which drive, respectively, the BUCKBOOST\_LOAD\_50% and BUCKBOOST\_LOAD\_100% signals. The MOSFET switches the resistive load bank in and out of the circuit.

Therefore, when PC14 is high, load bank 1 is ON. When PC15 is high, load bank 2 is ON. The test pins TP1 and TP2 are also used to check the load activation status, although these are not populated. The load banks have the total resistance shown in Table 1.

|            | 0%         | 50%        | 100%           |

|------------|------------|------------|----------------|

| Load (%)   | Load 1 OFF | Load 1 ON  | Load 1 ON      |

|            | Load 2 OFF | Load 2 OFF | Load 2 ON      |

| Load       | ∞          | 33 Ω       | 16.5 Ω         |

| LED status | All OFF    | Green      | Green + Orange |

Table 1. Onboard load steps

The load status can also be observed via the green and orange LED toggling. Moreover, it can be modified with the use of the joystick on the board.

AN5785 - Rev 4 page 4/43

### 3 Application contents

This application implements a voltage mode closed-loop control on the boost converter, using the USB power delivery as power supply.

The USB-PD provides a 5 V supply as the input voltage for a boost converter. The board loads can handle a maximum voltage of 7.5 V, which is achieved by regulating the output voltage of the boost converter to 7.5 V.

### 3.1 Boost converter closed-loop operation

#### **Operating principle**

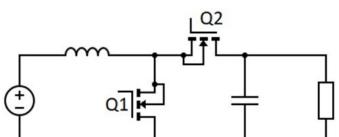

The kit contains a synchronous boost converter power stage (see Figure 4).

Figure 4. Simplified boost power stage schematic

At the beginning of the switching period, the PWM of the bottom switch is set high and the top switch is set low. This turns MOSFET Q1 on, and MOSFET Q2 off.

The current through the inductor increases linearly. The output capacitor is already charged in steady-state and holds the output voltage on the load. At the end of the duty cycle, the switch Q1 is turned off.

A dead time is inserted between low side and high side PWM for switches Q1 and Q2 to prevent shoot-through. When this dead time has elapsed, the high side PWM for the switch Q2 goes high turning on the switch Q2.

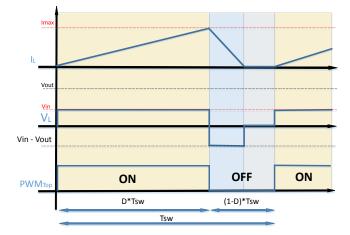

The inductor current decreases linearly when it charges the output capacitor again (output voltage is higher than input), and current flows through switch Q2. This switching action is described in Figure 5.

Figure 5. Boost converter operation waveforms

The output filter capacitor filters the AC component, while the DC component is the output load current. The output voltage is always greater than or equal to the input voltage.

AN5785 - Rev 4 page 5/43

The steady-state output voltage is dependent upon the input voltage and the duty cycle:

$$K = \sqrt{\frac{I_{mo}}{I_{mode}}} = \sqrt{\frac{62.7MHz}{13.56MHz}} = 2.15$$

(1)

The voltage mode control loop is implemented to ensure reference tracking in the event of disturbances (such as load-stepping or supply variation). A changing voltage provided by the boost converter is associated to a line variation.

#### 3.1.1 Voltage mode control loop

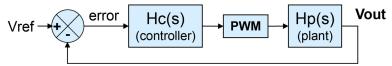

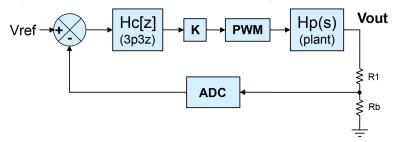

A typical power supply control loop is schematized in Figure 6.

Figure 6. Generic schematic of a PSU control loop

The classic procedure for designing the controller is to model the system in the frequency domain, then select the best controller type to compensate for the system behavior, obtaining adequate transient and stationary regulation.

When a mathematical model is known for the system, the compensator is calculated from that model.

The compensator can also be calculated empirically by measuring the system response, and designing a controller that compensates for the measured behavior.

Note: The control mode (for example, current or voltage mode) affects the system behavior.

Implementing voltage mode on a boost topology is not very common (regulation is poor compared to current mode, as shown in Section 6: Results of measurements). The boost plant is running at the same time, making it suitable for the plant response measurement method for identifying the compensator, as the mathematical models are not common for this operation.

The process of measuring the plant frequency response and placing the compensator poles and zeroes is not discussed here. Several workshops are provided by Biricha Digital to fine-tune controllers with this method.

The resulting compensator is a type 3 filter (three poles, three zeroes IIR filter).

Figure 7. Schematic of the implemented voltage mode control loop

Figure 7 shows the power stage containing the switching MOSFETs, output filter inductor, and output filter capacitor within the block Hp(s). The controller, designed as a 3p3z filter, is the block Hc(z). This controller transfer function is expressed in the Z domain as it is implemented by digital means.

Digital voltage mode PSU control implies:

- the presence of the ADC sampling

- a scaling factor K

- the PWM generator

In Figure 7 the output voltage of the power stage is returned and compared with a reference, V<sub>REF</sub>. The controller output is the duty cycle, which is used as an input to the power stage and modulates the MOSFET switches.

#### 3.2 Load regulation

The user controls the load switching using the joystick supplied with the kit as follows:

AN5785 - Rev 4 page 6/43

- Left: decrease load by 50% (from 100 to 0%)

- Right: increase load by 50% (from 0 to 100%)

- Up: enable automatic load toggling (50 to 100%), useful for transient measurements

- Down: manual load selection

The status of the load bank during the transient is indicated by the LEDs:

- green LED: bank 1 is enabled

- orange LED: bank 2 is enabled

AN5785 - Rev 4 page 7/43

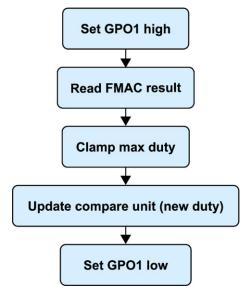

### 4 Software implementation

### 4.1 Targeted application

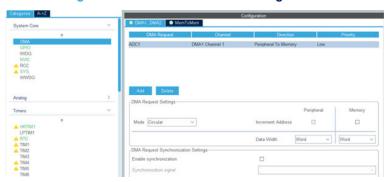

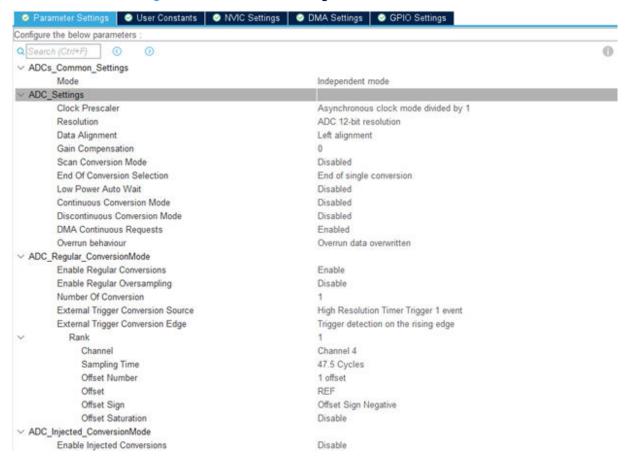

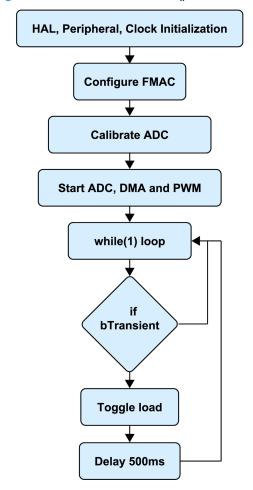

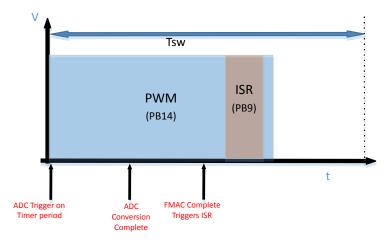

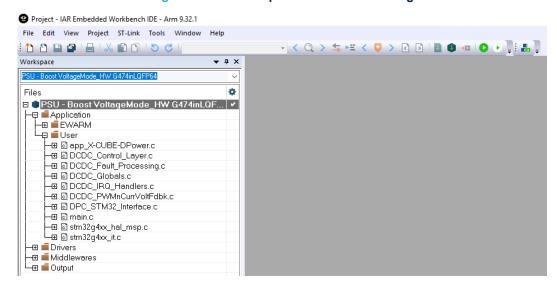

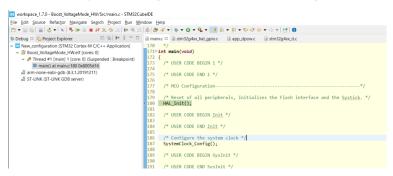

The following configuration sets up the STM32 MCU to operate a closed-loop voltage mode step-up converter using the onboard peripherals including the ADC, DMA, and HRTIM. The FMAC is used to implement the 3p3z controller. This implementation means that the main core usage is reduced to an absolute minimum and is the preferred option allowing the MCU to be used for other tasks or running more power supplies. The example software project to accompany this application note is called <code>Boost\_VoltageMode\_HW</code> as it uses as many hardware peripherals as possible.

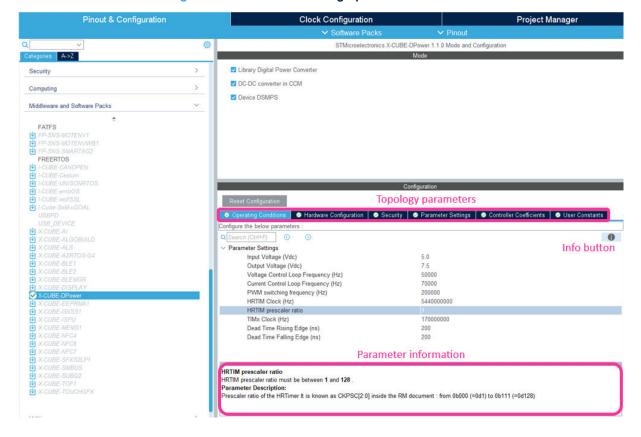

### 4.2 Configuration using STM32CubeMX

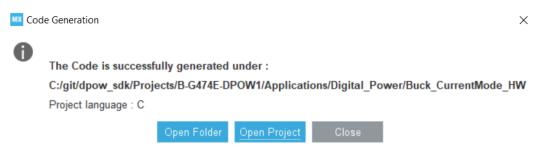

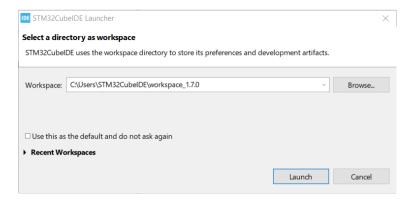

This section contains step-by-step instructions for recreating the STM32CubeMX project for the Boost converter under voltage mode control on the Discovery kit. This complete project can be downloaded by following the links provided within this application note appendix. However, the full configuration is included here for completeness. Open STM32CubeMX by clicking on the icon shown in Figure 10 (note that the icon may differ slightly).

Figure 8. STM32CubeMX icon

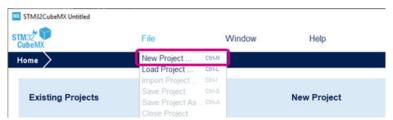

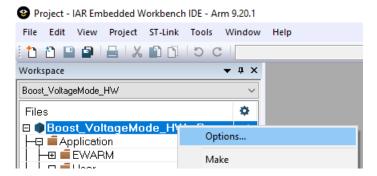

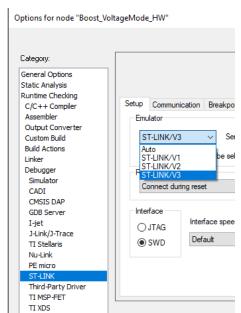

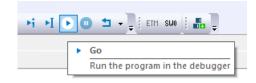

Now, create a new STM32CubeMX project. This project configures the MCU peripherals and generates an IAR Embedded Workbench® project. IAR Systems® is used to compile and link the code as well as for programming and debugging the MCU.

Within the STM32CubeMX window click on File, New Project

Figure 9. New project selection

AN5785 - Rev 4 page 8/43

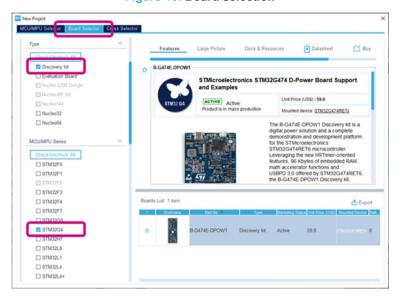

The new project device selector window now opens. Within this window click on the *Board selector* tab and filter down the boards by selecting the *Discovery kit* for the Type and *STM32G4* for the *MCU/MPU Series*

Figure 10. Board selection

This may filter down the available boards on the right-hand side of this window to include the *B-G474E-DPOW1* Discovery kit, which this application note is using. Double-click on this board within the table.

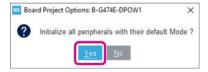

A prompt is displayed asking if the user likes to initialize all peripherals with their default mode. Click Yes. This sets up the pins and peripherals with their default setting for this particular evaluation board.

Figure 11. Peripherals default mode initialization

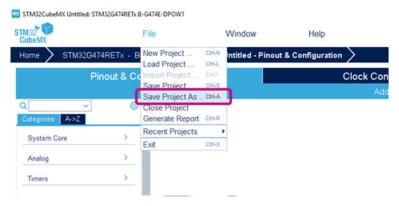

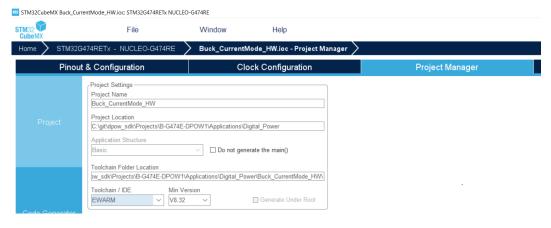

Before making any changes to the project, save the project by going to File, Save Project As.

Figure 12. Project naming

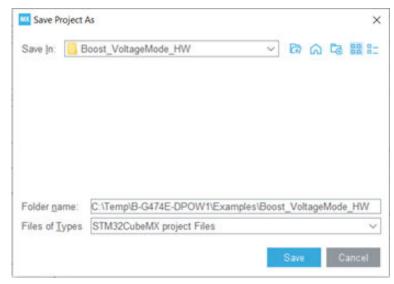

The name given to the folder, *Folder Name*, is also the name of the project. If this folder does not exist it is created. Click *Save* when done.

AN5785 - Rev 4 page 9/43

Figure 13. Project saving

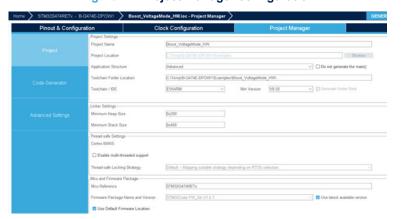

On the right-hand side of the main window, click *Project Manager* and select the preferred toolchain and version from the dropdown list as shown in Figure 14.

Figure 14. Project manager configuration

AN5785 - Rev 4 page 10/43

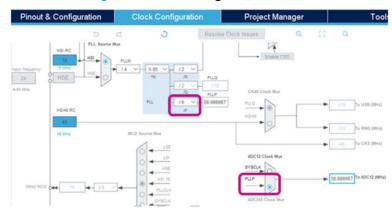

### 4.2.1 Clock configuration

Select the *Clock Configuration* tab which is along the top of the main STM32CubeMX window. Locate the PLL section and change the peripheral clock divider to /6. Then select the clock source for the ADC12 Clock Mux to *PLLP*. These settings are highlighted in Figure 15.

Figure 15. Clock configuration window

The ADC12 clock may now be 56.66 MHz.

### 4.3 Peripheral configuration: voltage mode closed loop boost

The MCU resources needed to run a voltage mode control loop on the boost converter are:

- Two complementary high-resolution PWM outputs with programmable duty cycle and deadtime insertion using one of the channels of the IP HRTIM1, available on STM32G474.

- An ADC channel to sample the output voltage, triggered synchronously with the PWMs. This is performed via the ADC1 and the IP interconnect in STM32G474.

- A digital filter processing engine, which allows the CPU to be unloaded when calculating the compensator. This is provided by the FMAC IP in STM32G474.

- A DMA channel to transfer the measured output voltage from the ADC to the FMAC at the end of each conversion.

AN5785 - Rev 4 page 11/43

### 4.3.1 GPIO peripheral configuration

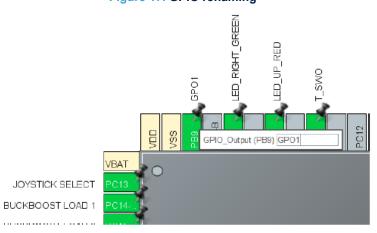

For this application note, a digital pin is configured to allow timing measurements to be performed. On the *Pinout & Configuration* tab, locate the pin PB9 towards the top left of the microcontroller. Left-click on the pin PB9 and select *GPIO\_Output* as in Figure 16. GPIO peripheral configuration.

TIM4\_CH4

TIM8\_CH3

USART3\_TX

GPIO\_Input

GPIO\_Output

GPIO\_EXTI9

VBAT

\*\*K SELECT PC13

ST LOAD 1 PC14...

ST LOAD 2 PC15-...

Figure 16. GPIO peripheral configuration

Then, right-click on PB9 and select *Enter User Label*. This allows us to change the name of the pin so that it can be easily referenced within the code. This pin is called *GPO1*.

Enter this into the pop-up box as in Figure 17.

Figure 17. GPIO renaming

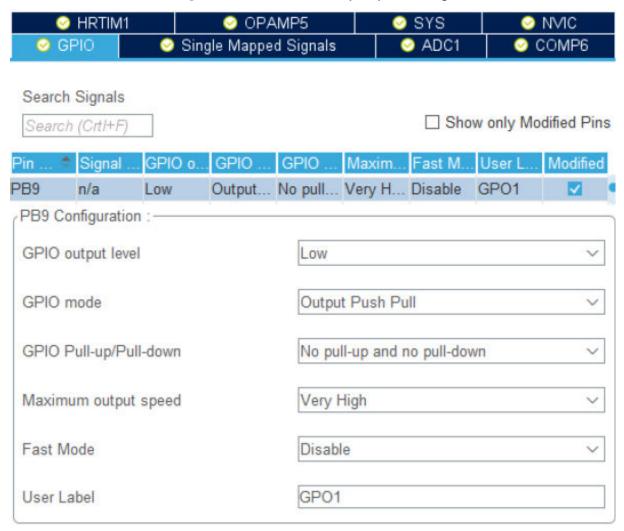

Now expand the *System Core* category on the left-hand side of the window. Click on *GPIO*. Under the GPIO tab, click on the row for PB9. Change the *Maximum output* speed setting to Very high as per the Figure 18.

AN5785 - Rev 4 page 12/43

Figure 18. GPIO maximum output speed setting

The configuration for GPO1 is now complete.

AN5785 - Rev 4 page 13/43

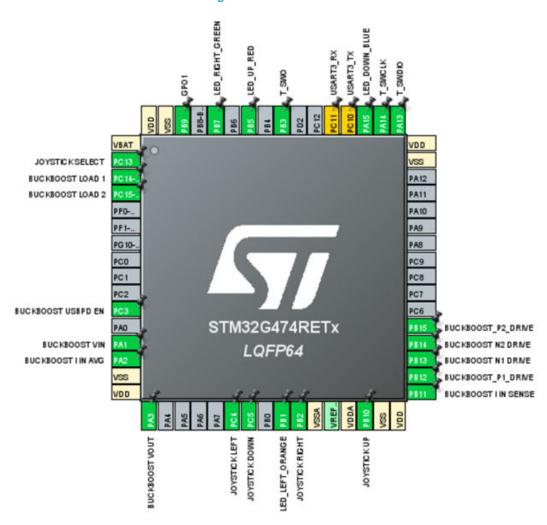

Now, some of the default pin labels must be changed to work with the example code provided. Within the pinout view of the MCU, locate the following pins, right-click on them and select *Enter User Label* and change the label to the new label listed in Table 2.

Pin

Existing label

New label

PB7

LD4 [green LED]

LED\_RIGHT\_GREEN

PB5

LD5 [red LED]

LED\_UP\_RED

PA15

LD2 [blue LED]

LED\_DOWN\_BLUE

PB1

LD3 [orange LED]

LED\_LEFT\_ORANGE

Table 2. User label setting

The pin locations are highlighted in Figure 19.

Figure 19. Pins location

The GPIO configuration is now complete.

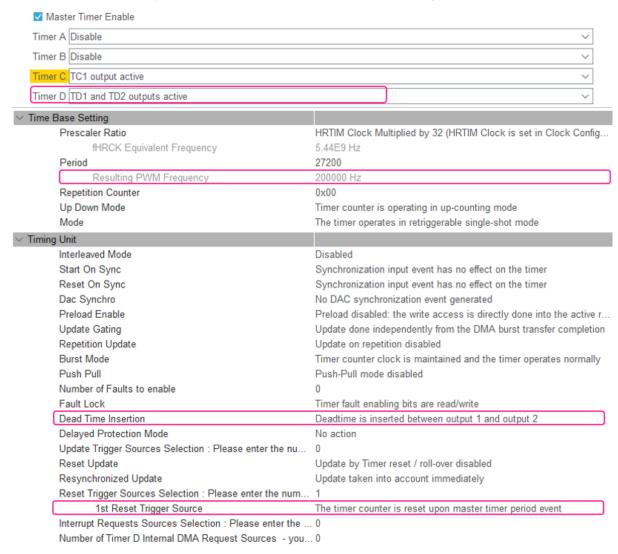

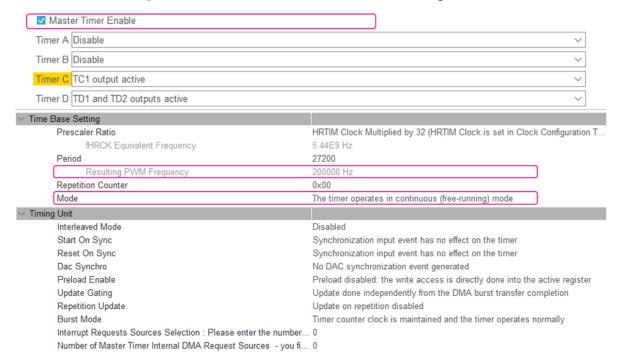

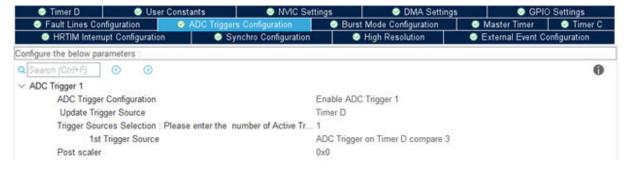

### 4.3.2 HRTIM1 STM32CubeMX configuration

The boost switches are driven by Channel D of the HRTIM1, which outputs two opposite signals at 200 kHz, with a 147 ns deadtime insertion on both edges.

AN5785 - Rev 4 page 14/43

Two comparators must be programmed, one modifying every period with the value calculated by the Compensator (DUTY\_TICKS\_MIN), and another representing the maximum duty cycle value, to limit the maximum output current (DUTY\_TICKS\_MAX).

DUTY\_TICKS\_MIN and DUTY\_TICKS\_MAX terms that are defined on the code.

An additional comparator is programmed to initiate the ADC conversion later in the period, which improves system stability and reduces potential noise caused by switching currents. For more information see AN5496, available on www.st.com.

STM32CubeMX configuration within the HRTIM1 section is available in the Boost\_VoltageMode\_HW.ioc file.

Figure 20. STM32CubeMX HRTIM1 channel D configuration

AN5785 - Rev 4 page 15/43

Figure 21. STM32CubeMX HRTIM1 channel D configuration (continued)

| Compare Unit 2 Configuration  Triggered-Half Mode  Timer Compare 2 register is behaving in standard mode  Compare Value  DUTY_TICKS_MAX  Auto Delayed Mode  Standard compare mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Compare Unit 1                                        |                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------|

| Greater-than comparison Compare Unit 2 Compare Unit 2 Compare Unit 2 Configuration Triggered-Half Mode Compare Value DUTY_TICKS_MAX Auto Delayed Mode Compare Unit 3 Compare Value 3000 Greater-than comparison Timer Compare 3 event is generated when counter is equal  Dead Time  Dead Time Dead Time Dead Time Configuration Prescaler (PSC - 16 bits value) Rising Value 200 Rising Sign Positive deadtime on rising edge Rising Lock Deadtime rising value and sign is writable Falling Value 200 Falling Value 200 Falling Sign Positive deadtime on falling edge Falling Lock Deadtime falling value and sign is writable Toutput 1 Configuration Output 1 Configuration Output 1 Configuration Tid Set Source Selection : Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its inactive state Reset Source Selection : Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state The output is not affected by the burst mode operation Output at inactive level when in IDLE state The output is not affected by the fault input Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                             | Compare Unit 1 Configuration                          | Enable                                                              |

| Compare Unit 2 Configuration Enable Triggered-Half Mode DUTY_TICKS_MAX Auto Delayed Mode standard compare mode Compare Unit 3 Configuration Enable Compare Unit 3 Configuration Enable Compare Value 3000 Greater-than comparison Timer Compare 3 event is generated when counter is equal  Dead Time Dead Time Configuration Enable Prescaler (PSC - 16 bits value) fiDTG = ftHRTIM * 8  Rising Value 200 Rising Sign Positive deadtime on rising edge Rising Lock Deadtime rising value and sign is writable Falling Value 200 Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime on falling edge Falling Sign Lock Deadtime fising sign is writable Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime on falling edge Falling Sign Deadtime fising value and sign is writable Falling Sign Positive deadtime on falling edge Falling Lock Deadtime falling sign is writable Deadtime falling sign is writable  Tot Dutput 1 Configuration Output 1 Configuration Output 1 Configuration Polarity Output is active HIGH  Set Source Selection : Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its active state Reset Source Selection : Please enter the number of A 2  1st Reset Source Inner compare 1 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state The output is not affected by the burst mode operation Output at inactive level when in IDLE state The output is not affected by the fault input                                                                                                                                                                                                                                  | Compare Value                                         | DUTY_TICKS_MIN                                                      |

| Compare Unit 2 Configuration Triggered-Half Mode Compare Value Auto Delayed Mode Compare Unit 3 Compare Unit 3 Configuration Greater-than comparison  Dead Time Dead Time Dead Time Dead Time Configuration Prescaler (PSC - 16 bits value) Rising Sign Roadtime rising sign is writable Falling Sign Positive deadtime on falling edge Falling Sign Roadtime falling sign is writable Falling Sign Coth Rising Sign Roadtime rising value and sign is writable Falling Sign Roadtime rising value and sign is writable Falling Sign Roadtime rising value and sign is writable Falling Sign Roadtime falling value and sign is writable Falling Sign Roadtime falling value and sign is writable Deadtime falling sign is writable Deadtime falling value and sign is writable Trigger of the write deadtime on falling edge Deadtime falling sign is writable Deadtime falling value and sign is writable Deadtime falling value and sign is writable Deadtime falling sign is writable Trigger of the write deadtime on falling edge Deadtime falling value and sign is writable Deadtime falling value and sign is writable Trigger of the write deadtime on falling edge Deadtime falling value and sign is writable Deadtime falling value and sign is writable Trigger of the write deadtime on falling edge Trigger of the value  | Greater-than comparison                               | Timer Compare 1 event is generated when counter is equal            |

| Triggered-Half Mode Timer Compare 2 register is behaving in standard mode  Compare Value DUTY_TICKS_MAX  Auto Delayed Mode standard compare mode  Compare Unit 3  Compare Unit 3 Configuration Enable  Compare Value 3000  Greater-than comparison Timer Compare 3 event is generated when counter is equal  Dead Time  Dead Time Configuration Enable  Prescaler (PSC - 16 bits value) fDTG = fHRTIM * 8  Rising Value 200  Rising Sign Positive deadtime on rising edge Rising Lock Deadtime rising value and sign is writable  Falling Value 200  Falling Sign Positive deadtime on falling edge Falling Value 200  Falling Sign Positive deadtime on falling edge Falling Value 200  Falling Sign Positive deadtime on falling edge Falling Value 200  Falling Sign Positive deadtime on falling edge Falling Sign Lock Deadtime falling value and sign is writable  Falling Sign Lock Deadtime falling value and sign is writable  Total Configuration TD1  Output 1 Configuration TD1  Polarity Output 1 Configuration TD1  Set Source Selection : Please enter the number of Activ 1  1st Set Source Selection : Please enter the number of Activ 1  1st Reset Source Selection : Please enter the number of Activ 1  1st Reset Source Timer compare 1 event forces the output to its active state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Idle Mode  Idle Level The output is not affected by the burst mode operation Output at inactive level when in IDLE state Fault Level The output is not affected by the fault input Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                        | Compare Unit 2                                        |                                                                     |

| Compare Value DUTY_TICKS_MAX Auto Delayed Mode standard compare mode  Compare Unit 3 Compare Unit 3 Configuration Enable Compare Value 3000 Greater-than comparison Timer Compare 3 event is generated when counter is equal  Dead Time Dead Time Enable Prescaler (PSC - 16 bits value) fDTG = fHRTIM * 8  Rising Value 200 Rising Sign Positive deadtime on rising edge Rising Lock Deadtime rising value and sign is writable Falling Value 200 Falling Sign Positive deadtime on falling edge Falling Value 200 Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime on falling sign is writable  Deadtime falling value and sign is writable  Tothut 1 Configuration Output 1 Configuration Output 1 Configuration Output 1 Configuration TD1 Polarity Output is active HIGH  Set Source Selection : Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its active state Reset Source Selection : Please enter the number of Activ 1  1st Reset Source Timer compare 1 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 3 event is generated when in IDLD event forces the output state The output is not affected by the fault input             | Compare Unit 2 Configuration                          | Enable                                                              |

| Auto Delayed Mode  Compare Unit 3 Compare Unit 3 Configuration Compare Value Compare Value Source Than comparison Timer Compare 3 event is generated when counter is equal  Dead Time  Dead Time Dead Time Configuration Prescaler (PSC - 16 bits value) Rising Value 200 Rising Sign Positive deadtime on rising edge Rising Lock Deadtime rising value and sign is writable Falling Value 200 Falling Sign Lock Deadtime rising sign is writable Falling Value 200 Falling Sign Positive deadtime on falling edge Positive deadtime on falling edge Falling Value Deadtime falling value and sign is writable Falling Value Deadtime falling value and sign is writable Deadtime falling value and sign is writable  Falling Sign Lock Deadtime falling sign is writable  Output 1 Configuration Output 1 Configuration Output 1 Configuration TD1 Output 1 Configuration Output 1 Configuration TD1 Set Source Selection : Please enter the number of Activ 1  1st Set Source Timer compare 1 event forces the output to its inactive state Reset Source Selection : Please enter the number of Activ 2  1st Reset Source Timer compare 1 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state The output is not affected by the burst mode operation Output signal is not affected by the fault input Chopper Mode Enable Output signal is not affected by the fault input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Triggered-Half Mode                                   | Timer Compare 2 register is behaving in standard mode               |

| Compare Unit 3 Compare Unit 3 Configuration Compare Value 3000 Greater-than comparison Timer Compare 3 event is generated when counter is equal  Dead Time  Dead Time Configuration Prescaler (PSC - 16 bits value) Fishing Sign Rising Value 200 Rising Sign Rising Lock Deadtime rising value and sign is writable Falling Value Positive deadtime on rising edge Rising Lock Deadtime rising sign is writable Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime on fising edge Falling Value  Deadtime falling value and sign is writable  Deadtime falling value and sign is writable  Deadtime falling value and sign is writable  The master timer period event forces the output to its active state The master timer period event forces the output to its inactive state Timer compare 1 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state The output is not affected by the burst mode operation Output at inactive level when in IDLE state The output is not affected by the fault input Chopper Mode Enable Output signal is not affected by the fault input                                                                                                                                                                 | Compare Value                                         | DUTY_TICKS_MAX                                                      |

| Compare Unit 3 Configuration  Compare Value  Compare Value  Greater-than comparison  Timer Compare 3 event is generated when counter is equal  Dead Time  Dead Time Configuration  Prescaler (PSC - 16 bits value)  Rising Value  Rising Sign  Rising Lock  Rising Lock  Rising Sign Lock  Peadtime rising value and sign is writable  Falling Value  200  Falling Sign  Positive deadtime on rising edge  Palting Value  200  Falling Sign  Positive deadtime on falling edge  Falling Sign  Positive deadtime on falling edge  Palling Sign Lock  Deadtime falling value and sign is writable  Deadtime falling value and sign is writable  Deadtime falling sign is writable  Deadtime falling sign is writable  Deadtime falling sign is writable  TD1  Output 1 Configuration  Output 1 Configuration  Output 1 Configuration  TD1  Set Source Selection : Please enter the number of Activ 1  1st Set Source  The master timer period event forces the output to its inactive state  Reset Source Selection : Please enter the number of A 2  1st Reset Source  Timer compare 1 event forces the output to its inactive state  Timer compare 2 event forces the output to its inactive state  If woutput is not affected by the burst mode operation  Output at inactive level when in IDLE state  The output is not affected by the fault input  Chopper Mode Enable  Output signal is not affected by the fault input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Auto Delayed Mode                                     | standard compare mode                                               |

| Greater-than comparison Timer Compare 3 event is generated when counter is equal  Dead Time Dead Time Configuration Prescaler (PSC - 16 bits value) Finable Prescaler (PSC - 16 bits value) Fissing Value Positive deadtime on rising edge Rising Sign Rising Lock Deadtime rising value and sign is writable Rising Sign Lock Deadtime rising sign is writable Falling Value Positive deadtime on falling edge Rising Sign Lock Deadtime falling value and sign is writable Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime on falling edge Falling Lock Deadtime falling value and sign is writable Deadtime falling sign is writable  Output 1 Configuration  Output 1 Configuration  Output 1 Configuration  TD1 Polarity Output is active HIGH  Set Source Selection : Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its active state Reset Source Selection : Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state In me output is not affected by the burst mode operation Idle Level Output at inactive level when in IDLE state Fault Level The output is not affected by the fault input Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Compare Unit 3                                        |                                                                     |

| Compare Value Greater-than comparison Timer Compare 3 event is generated when counter is equal  Dead Time  Dead Time Configuration Prescaler (PSC - 16 bits value) Fightharpoorus Rising Value 200 Rising Sign Rising Lock Deadtime rising value and sign is writable Rising Sign Lock Deadtime rising sign is writable Falling Value 200 Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime on falling sign is writable  Falling Sign Positive deadtime on falling edge Falling Sign Positive deadtime falling value and sign is writable Deadtime falling sign is writable  Totaling Sign Lock Deadtime falling sign is writable  Output 1 Configuration  Output 1 Configuration  TD1 Polarity Output is active HIGH  Set Source Selection : Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its active state Reset Source Selection : Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state In mer compare 2 event forces the output to its inactive state In mer compare 2 event forces the output to its inactive state In mer compare 2 event forces the output to its inactive state In mer compare 2 event forces the output to its inactive state In mer compare 2 event forces the output to its inactive state The output is not affected by the burst mode operation Utput at inactive level when in IDLE state Fault Level Chopper Mode Enable Output signal is not affected by the fault input                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Compare Unit 3 Configuration                          | Enable                                                              |

| Dead Time  Dead Time Configuration Prescaler (PSC - 16 bits value)  Rising Value  200  Rising Sign Positive deadtime on rising edge Rising Lock Deadtime rising value and sign is writable Palling Value  200  Falling Sign Positive deadtime on falling edge Falling Value  200  Falling Sign Positive deadtime on falling edge Falling Lock Deadtime falling value and sign is writable  Enable Positive deadtime on falling edge Falling Sign Positive deadtime on falling edge Falling Sign Lock Deadtime falling sign is writable  Output 1 Configuration Output 1 Configuration Output 1 Configuration Polarity Output is active HIGH  Set Source Selection : Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its active state Reset Source Selection : Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state 2nd Reset Source Timer compare 2 event forces the output to its inactive state Inde Mode Idle Level Output at inactive level when in IDLE state Fault Level The output is not affected by the fault input Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Compare Value                                         | 3000                                                                |

| Dead Time Configuration Prescaler (PSC - 16 bits value)  Rising Value 200  Rising Sign Positive deadtime on rising edge Rising Lock Deadtime rising value and sign is writable Rising Sign Lock Deadtime rising sign is writable Falling Value 200  Falling Sign Positive deadtime on falling edge Falling Sign Deadtime rising sign is writable Falling Sign Positive deadtime on falling edge Falling Lock Deadtime falling value and sign is writable Deadtime falling sign is writable  Output 1 Configuration Output 1 Configuration Output 1 Configuration TD1 Polarity Output is active HIGH Set Source Selection: Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its active state Reset Source Selection: Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state If me output is not affected by the burst mode operation Idle Level Output at inactive level when in IDLE state Fault Level The output is not affected by the fault input Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Greater-than comparison                               | Timer Compare 3 event is generated when counter is equal            |

| Prescaler (PSC - 16 bits value)  Rising Value  200  Rising Sign  Positive deadtime on rising edge Rising Lock  Rising Sign Lock  Rising Sign Lock  Peadtime rising sign is writable  Falling Value  200  Falling Sign  Positive deadtime on falling edge Falling Value  200  Falling Sign  Positive deadtime on falling edge Falling Lock  Deadtime falling value and sign is writable  Falling Sign Lock  Deadtime falling value and sign is writable  Output 1 Configuration  Output 1 Configuration  Output 1 Configuration  Polarity  Output is active HIGH  Set Source Selection: Please enter the number of Activ 1  1st Set Source  Reset Source Selection: Please enter the number of A 2  1st Reset Source  Timer compare 1 event forces the output to its inactive state  2nd Reset Source  Timer compare 2 event forces the output to its inactive state  Idle Mode  In output is not affected by the burst mode operation  Output at inactive level when in IDLE state  Fault Level  The output is not affected by the fault input  Chopper Mode Enable  Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Dead Time                                             |                                                                     |

| Rising Value 200 Rising Sign Positive deadtime on rising edge Rising Lock Deadtime rising value and sign is writable Rising Sign Lock Deadtime rising sign is writable Falling Value 200 Falling Sign Positive deadtime on falling edge Falling Lock Deadtime falling value and sign is writable Falling Sign Lock Deadtime falling value and sign is writable Falling Sign Lock Deadtime falling sign is writable  Output 1 Configuration Output 1 Configuration Polarity Output is active HIGH  Set Source Selection : Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its active state Reset Source Selection : Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state In Its Plance Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Idle Mode The output is not affected by the burst mode operation Idle Level Output at inactive level when in IDLE state Fault Level The output is not affected by the fault input Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Dead Time Configuration                               | Enable                                                              |

| Rising Value 200 Rising Sign Positive deadtime on rising edge Rising Lock Deadtime rising value and sign is writable Rising Sign Lock Deadtime rising sign is writable Falling Value 200 Falling Sign Positive deadtime on falling edge Falling Lock Deadtime falling value and sign is writable Falling Sign Lock Deadtime falling value and sign is writable Falling Sign Lock Deadtime falling sign is writable  Output 1 Configuration Output 1 Configuration Polarity Output is active HIGH  Set Source Selection : Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its active state Reset Source Selection : Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Timer compare 2 event forces the output to its inactive state Idle Mode The output is not affected by the burst mode operation Idle Level Output at inactive level when in IDLE state Fault Level The output is not affected by the fault input Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Prescaler (PSC - 16 bits value)                       | fDTG = fHRTIM * 8                                                   |

| Rising Lock  Rising Sign Lock  Deadtime rising value and sign is writable  Palling Value  200  Falling Sign  Positive deadtime on falling edge Falling Lock  Falling Sign Lock  Deadtime falling value and sign is writable  Deadtime falling value and sign is writable  Deadtime falling sign is writable  Deadtime falling sign is writable  Output 1 Configuration  Output 1 Configuration  Polarity  Output is active HIGH  Set Source Selection: Please enter the number of Activ 1  1st Set Source  The master timer period event forces the output to its active state  Reset Source Selection: Please enter the number of A 2  1st Reset Source  Timer compare 1 event forces the output to its inactive state  2nd Reset Source  Timer compare 2 event forces the output to its inactive state  Timer compare 2 event forces the output to its inactive state  Output is not affected by the burst mode operation  Idle Level  Output at inactive level when in IDLE state  Fault Level  Chopper Mode Enable  Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                       | 200                                                                 |

| Rising Sign Lock  Falling Value  200  Falling Sign  Falling Lock  Falling Sign Deadtime falling value and sign is writable  Falling Sign Deadtime falling value and sign is writable  Deadtime falling value and sign is writable  Deadtime falling value and sign is writable  Deadtime falling value and sign is writable  The Deadtime falling value and sign is writable  Deadtime f | Rising Sign                                           | Positive deadtime on rising edge                                    |

| Falling Value  Falling Sign  Falling Lock  Falling Sign Lock  Deadtime falling value and sign is writable  Deadtime falling sign is writable  Deadtime falling sign is writable  Output 1 Configuration  Output 1 Configuration  Output 1 Configuration  Polarity  Output is active HIGH  Set Source Selection: Please enter the number of Activ 1  1st Set Source  The master timer period event forces the output to its active state  Reset Source Selection: Please enter the number of A 2  1st Reset Source  Timer compare 1 event forces the output to its inactive state  2nd Reset Source  Timer compare 2 event forces the output to its inactive state  Inter compare 2 event forces the output to its inactive state  Output at inactive level when in IDLE state  Fault Level  The output is not affected by the fault input  Chopper Mode Enable  Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Rising Lock                                           | Deadtime rising value and sign is writable                          |

| Falling Sign Positive deadtime on falling edge Falling Lock Deadtime falling value and sign is writable Falling Sign Lock Deadtime falling sign is writable  Output 1 Configuration  Output 1 Configuration TD1 Polarity Output is active HIGH  Set Source Selection: Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its active state Reset Source Selection: Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state 2nd Reset Source Timer compare 2 event forces the output to its inactive state Idle Mode The output is not affected by the burst mode operation Idle Level Output at inactive level when in IDLE state Fault Level The output is not affected by the fault input Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Rising Sign Lock                                      | Deadtime rising sign is writable                                    |

| Falling Lock Falling Sign Lock  Deadtime falling value and sign is writable  Deadtime falling value and sign is writable  The output is not affected by the fault input  Deadtime falling value and sign is writable  Deadtime falling  | Falling Value                                         | 200                                                                 |

| Falling Sign Lock  Deadtime falling sign is writable  Output 1 Configuration  Output 1 Configuration  Polarity  Output is active HIGH  Set Source Selection: Please enter the number of Activ 1  1st Set Source  The master timer period event forces the output to its active state  Reset Source Selection: Please enter the number of A 2  1st Reset Source  Timer compare 1 event forces the output to its inactive state  2nd Reset Source  Timer compare 2 event forces the output to its inactive state  Idle Mode  Idle Level  Output is not affected by the burst mode operation  Output at inactive level when in IDLE state  Fault Level  Chopper Mode Enable  Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Falling Sign                                          | Positive deadtime on falling edge                                   |

| Output 1 Configuration Output 1 Configuration Polarity Output is active HIGH  Set Source Selection: Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its active state Reset Source Selection: Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state 2nd Reset Source Timer compare 2 event forces the output to its inactive state Idle Mode The output is not affected by the burst mode operation Idle Level Output at inactive level when in IDLE state Fault Level The output is not affected by the fault input Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Falling Lock                                          | Deadtime falling value and sign is writable                         |

| Output1 Configuration Polarity Output is active HIGH  Set Source Selection: Please enter the number of Activ 1  1st Set Source Selection: Please enter the number of Activ 2  Reset Source Selection: Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state 2nd Reset Source Timer compare 2 event forces the output to its inactive state Idle Mode The output is not affected by the burst mode operation Idle Level Output at inactive level when in IDLE state Fault Level The output is not affected by the fault input Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Falling Sign Lock                                     | Deadtime falling sign is writable                                   |

| Output1 Configuration Polarity Output is active HIGH  Set Source Selection: Please enter the number of Activ 1  1st Set Source Reset Source Selection: Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state 2nd Reset Source Timer compare 2 event forces the output to its inactive state Idle Mode Idle Level Output at inactive level when in IDLE state Fault Level Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Output 1 Configuration                                |                                                                     |

| Polarity Output is active HIGH  Set Source Selection: Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its active state.  Reset Source Selection: Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state.  2nd Reset Source Timer compare 2 event forces the output to its inactive state.  Idle Mode The output is not affected by the burst mode operation.  Idle Level Output at inactive level when in IDLE state.  Fault Level The output is not affected by the fault input.  Chopper Mode Enable Output signal is not altered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                       | TD1                                                                 |

| Set Source Selection: Please enter the number of Activ 1  1st Set Source The master timer period event forces the output to its active state.  Reset Source Selection: Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state.  2nd Reset Source Timer compare 2 event forces the output to its inactive state.  Idle Mode The output is not affected by the burst mode operation.  Idle Level Output at inactive level when in IDLE state.  Fault Level The output is not affected by the fault input.  Chopper Mode Enable Output signal is not altered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                       | Output is active HIGH                                               |

| Reset Source Selection: Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state 2nd Reset Source Timer compare 2 event forces the output to its inactive state Idle Mode The output is not affected by the burst mode operation Idle Level Output at inactive level when in IDLE state Fault Level The output is not affected by the fault input Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                       |                                                                     |

| Reset Source Selection: Please enter the number of A 2  1st Reset Source Timer compare 1 event forces the output to its inactive state 2nd Reset Source Timer compare 2 event forces the output to its inactive state Idle Mode The output is not affected by the burst mode operation Idle Level Output at inactive level when in IDLE state Fault Level The output is not affected by the fault input Chopper Mode Enable Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1st Set Source                                        | The master timer period event forces the output to its active state |

| 2nd Reset Source  Idle Mode  Idle Level  Fault Level  Chopper Mode Enable  Timer compare 2 event forces the output to its inactive state  The output is not affected by the burst mode operation  Output at inactive level when in IDLE state  The output is not affected by the fault input  Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Reset Source Selection : Please enter the number of A |                                                                     |

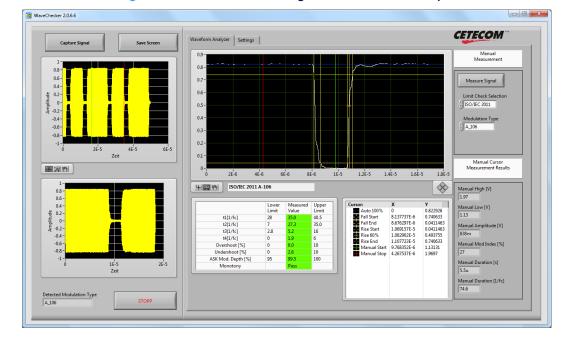

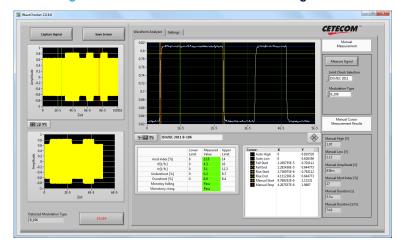

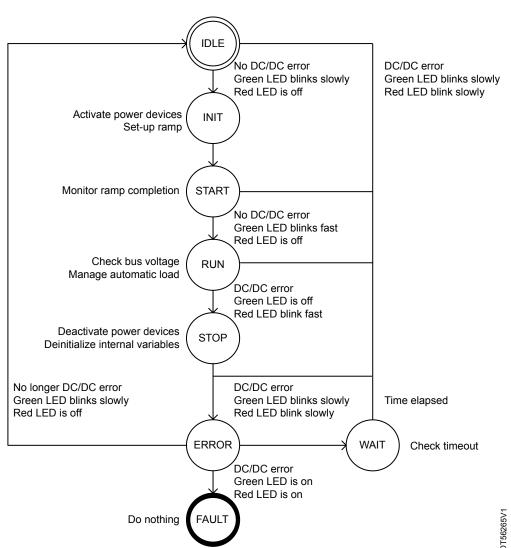

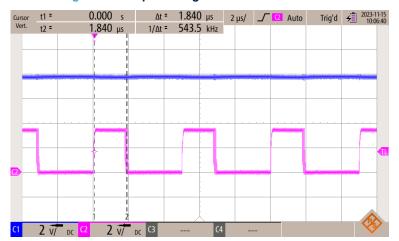

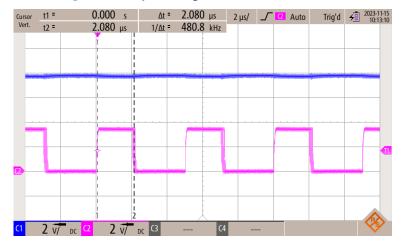

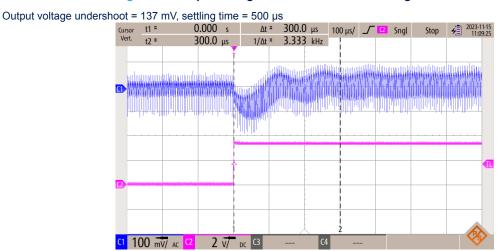

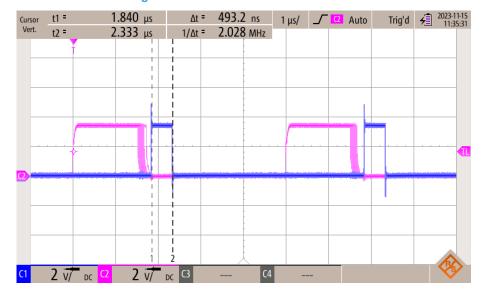

| 2nd Reset Source  Idle Mode  Idle Level  Fault Level  Chopper Mode Enable  Timer compare 2 event forces the output to its inactive state  The output is not affected by the burst mode operation  Output at inactive level when in IDLE state  The output is not affected by the fault input  Output signal is not altered                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1st Reset Source                                      | Timer compare 1 event forces the output to its inactive state       |