### L99LDLH32 – PWM synchronization among several devices

#### Introduction

When operating multiple devices on the same PCB, it is useful to synchronize these devices so that they have the same PWM frequency. In addition, the start of the PWM cycle of each device can be shifted from each other.

This feature, together with the gradual delay function (delay between individual channels of the device), allows the inrush current from the preregulator to be "smoothed" when multiple channels are activated at the same time or when operating continuously in PWM mode. This helps to minimize the voltage drops/peaks on the preregulator output, caused by its limited transient response capability.

This is particularly important when you use the SEPIC topology, where the bandwidth of the control loop is limited by the presence of a right half zero in its transfer function. Smoothing the inrush current then allows the use of a smaller output capacitor without the risk of excessive voltage drops/false open load detections.

### PWM synchronization between devices

#### 1.1 Device connection and configuration

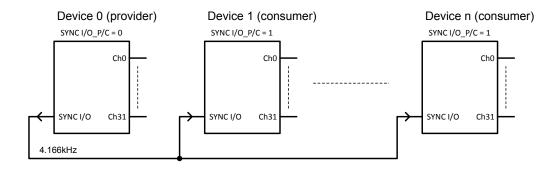

The PWM frequency and phase relation of several devices can be synchronized versus each other through the SYNC\_I/O pin. There is one dedicated bit (SYNC I/O\_P/C – see FTP/RAM memory map in Reference documents) to configure the device in clock provider [1] or clock consumer [0] mode. In provider mode, the device clock frequency (divided to 4.166 kHz) is sent on the SYNC\_I/O pin. In consumer mode, the clock frequency on the SYNC I/O line is used to synchronize its own clock.

Figure 1. PWM synchronization between devices via SYNC\_I/O pin

The phase relation among several devices can be configured by PHASE\_DEV bits (3-bits - see FTP/RAM memory map – see Reference documents).

Note:

The PHASE\_DEV value can be changed only via FTP programming (row 12). In the RAM (Configuration register #1, address 15h) it is read only:

| PHASE_DEV [2÷0] |       |       | PWM_PHASE_SHIFT [µs] |

|-----------------|-------|-------|----------------------|

| Bit 2           | Bit 1 | Bit 0 | FWM_FHA3E_SHIFT [µs] |

| 0               | 0     | 0     | 0                    |

| 0               | 0     | 1     | 15                   |

| 0               | 1     | 0     | 30                   |

| 0               | 1     | 1     | 45                   |

| 1               | 0     | 0     | 60                   |

| 1               | 0     | 1     | 75                   |

| 1               | 1     | 0     | 90                   |

| 1               | 1     | 1     | 105                  |

Table 1. PHASE\_DEV values

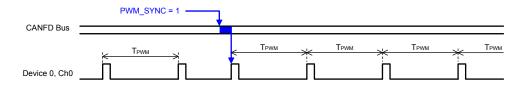

The PHASE\_DEV value determines the initial offset of the internal PWM counter. This offset (time delay) is applied after a power on reset or after the user sends the PWM\_SYNC=1 reset command. The PWM\_SYNC is a bit n.18 in the configuration register #1 (address 15h). When this bit is set to "1", the PWM counter is reset after the time offset defined by PHASE\_DEV and the bit is automatically cleared. The effect of this reset command and the specific PHASE\_DEV value can be seen in the following figures. The following figure shows the effect of the reset command with PHASE\_DEV value set to 0. In this case the PWM counter is reset immediately after receiving the command, so the new PWM cycle is immediately started.

AN5803 - Rev 1 page 2/15

Figure 2. Effect of the PWM\_SYNC=1 command with PHASE\_DEV = 0

The previously explained case is demonstrated on a real device in the following figure that shows the CAN bus communication (yellow plot) and the Output 0 configured to 3% duty cycle (blue plot). The PWM counter is reset just after receiving PWM\_SYNC=1 reset command (see rising edge of the PWM cycle at the end of the CAN command on detailed screenshot):

EYSIGHT

| MSO-X 4154A, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| South | MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| South | MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| South | MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| South | MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:3515 202

| MS0-X 4054, M52400376, 07.20.2017100515; Fr.1 Feb 25 11:351

Figure 3. Demonstration of the PWM\_SYNC=1 @ PHASE\_DEV = "000"

When sending the PWM\_SYNC=1 command using register 15h, take care also about other values configured by this register (like SYNC\_I/O\_M/S, PWM frequency, OUT\_DELAY etc.). In case the application SW wants to reset the PWM counter but do not know these other settings (for example when default values, configured through FTP, are used), it is possible to first execute a read command and after sending a write command with the same content with the PWM\_SYNC bit changed to "1".

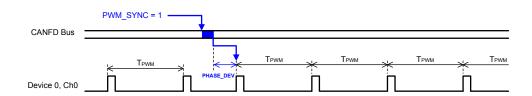

The following figure shows the effect of PWM\_SYNC=1 when PHASE\_DEV is set to a non-zero value. As shown in the figure, the PWM counter is reset after the configured PHASE\_DEV delay time, so the start of the new PWM cycle is delayed from this reset command.

Figure 4. Effect of the PWM\_SYNC=1 command with non-zero PHASE\_DEV value

AN5803 - Rev 1 page 3/15

The previously explained case is demonstrated on a real device in the following figure. The PHASE\_DEV is set to maximum value of 105  $\mu$ s in this example, so the PWM counter is reset with delay of 105  $\mu$ s after receiving PWM\_SYNC=1 reset command (see detailed screenshot in the following figure):

Figure 5. Demonstration of the PWM\_SYNC=1 @ PHASE\_DEV = "111" (105 μs)

#### 1.2 Synchronization sequence

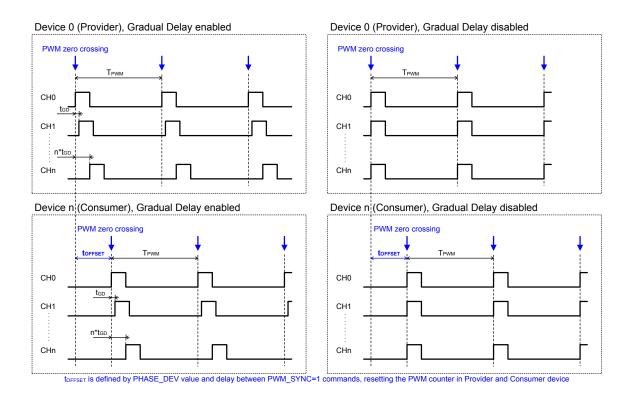

As explained in the previous chapter, the devices synchronized via the SYNC\_I/O pins operate at exactly the same PWM frequency. However, even if the devices are synchronized, the phase relation between them is not accurately defined after system startup (Power- on Reset).

The reason for this initial phase inaccuracy is the fact that the device logic is supplied from its own V3V3 voltage with an external decoupling capacitor, so the time to reach the reset threshold (= starting the PWM counter and applying configured PHASE\_DEV) may vary from device to device due to the tolerance of the capacitor value and the tolerance of POR threshold. Also, blocking consumer devices at the provider's frequency is not instantaneous, so all devices run on their own frequency, with some tolerance, for some time.

It causes sometimes delay between devices, shown as "t<sub>OFFSET</sub>" in the following figure. In case the configured PHASE\_DEV value is 0 on all devices, the t<sub>OFFSET</sub> represents only the above-mentioned tolerances. If a non-zero PHASE\_DEV is configured, the t<sub>OFFSET</sub> is a sum of configured PHASE\_DEV and offset due to tolerances.

AN5803 - Rev 1 page 4/15

Figure 6. PWM synchronization between devices via SYNC\_I/O pin

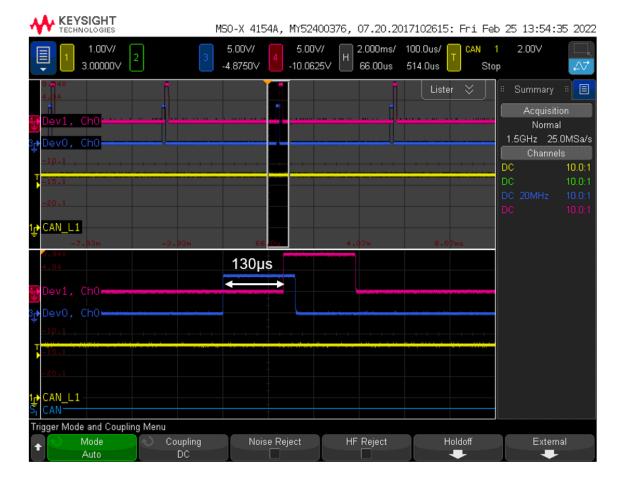

This initial time offset between devices is also demonstrated in the following figure. In this case, the two L99LDLH32 devices are synchronized via the SYNC\_I/O pins and PHASE\_DEV is set to 0 on both devices. The blue plot shows PWM signal on CH.0 of device 0 (3.3% duty cycle) and the red plot shows PWM signal on CH.0 of device 1. The measured time offset is 130  $\mu$ s:

AN5803 - Rev 1 page 5/15

Figure 7. Initial phase shift between 2 devices after POR

#### 1.2.1 Synchronization sequence–example 1

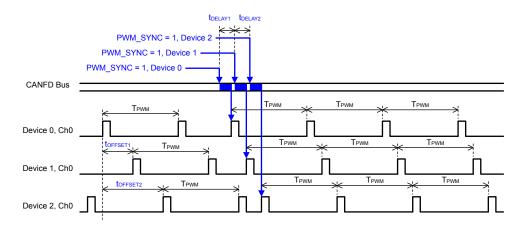

In order to eliminate this not very well-defined time offset, a synchronization sequence, writing PWM\_SYNC bit of each device to "1", can be applied. An example of such synchronization sequence is depicted in the following figure. This example shows three synchronized devices whose initial (not well defined) time offset is  $t_{OFFSET1}$  and  $t_{OFFSET2}$ . Then the PWM\_SYNC=1 command is sequentially applied to device 0, device 1, and device 2. Since the PHASE\_DEV value is set to 0 for all devices, the PWM counter of a particular device is reset just after the command is received. This means that the phase shift between devices after the synchronization sequence is defined by the time delay of the sent commands,  $t_{DELAY2}$ , and  $t_{DELAY2}$ .

AN5803 - Rev 1 page 6/15

Figure 8. Synchronization sequence example 1)

Note: The outputs on the previous figure are active for illustration purposes only, but it is not necessary. Normally, the synchronization sequence should be sent once during application initialization before the outputs are activated.

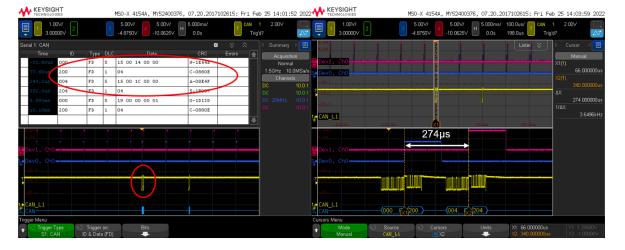

The synchronization sequence in example 1 is also demonstrated on real devices in the following figure (in this

The synchronization sequence in example 1 is also demonstrated on real devices in the following figure (in this case there are only two devices). The phase shift between devices is defined by sending 2 PWM\_SYNC=1 commands with delay of  $274\mu s$ :

Figure 9. Demonstration of example 1)

#### 1.2.2 Synchronization sequence – example 2

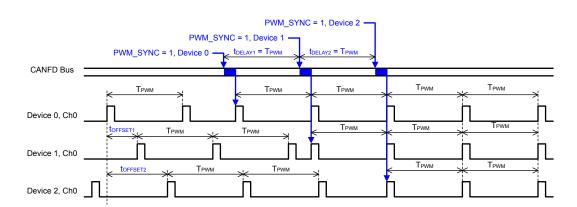

As explained in the previous example, the PWM\_SYNC=1 command can only be sent to one device at a time, so a sequence of several commands is required to reset all devices. Hence, it is not possible to reset all devices at once. But then, how to achieve such synchronization when the PWM zero crossings of all devices are aligned (without any phase shift) or defined only by the PHASE\_DEV value programmed in FTP?

AN5803 - Rev 1 page 7/15

The answer to this question is shown in the following figure. The principle is to send a sequence of individual PWM\_SYNC=1 commands with a delay of exactly 1 PWM period. In this way, a zero phase shift between devices or a phase shifts defined only by PHASE\_DEV can be achieved.

Figure 10. Synchronization sequence example 2)

The accuracy of this adjustment depends on the accuracy of the delay between PWM\_SYNC=1 commands (the error is defined by the difference between the applied  $t_{DELAY}$  and the actual TPWM). If the error needs to be minimized, the SYNC\_I/O line frequency can be measured by the microcontroller to determine the actual PWM period.

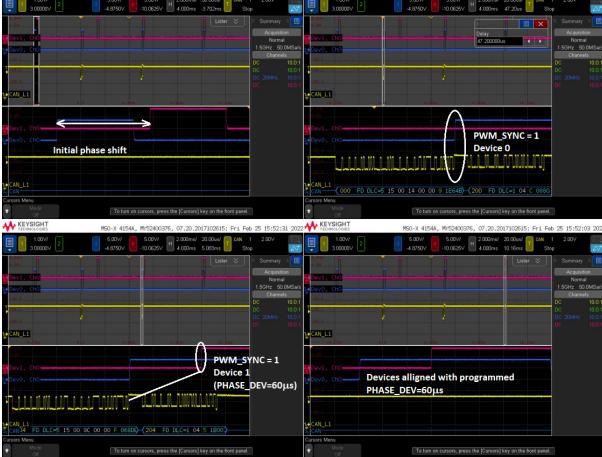

The example 2 is also demonstrated on real devices in the following figure with PHASE\_DEV=0 on both devices, respectively in the following figure, with PHASE\_DEV=0 on Device 0 and PHASE\_DEV=60µs on Device 1.

AN5803 - Rev 1 page 8/15

**KEYSIGHT**

AN\_L1

KEYSIGHT MSO-X 4154A, MY52400376, 07.20.2017102615: Fri Feb 25 14:09:53 2022 5.000ms/ 3.000000∨ -4.8750V Trig'd? Serial 1: CAN \* Type DLC 000 FD 15 00 14 00 00 9-1E64B 200 C-0880E A-08E4F 004 FD 15 00 1C 00 00 204 FD 5-1B007 AN L1 Initial phase shift PWM\_SYNC = 1 Device 0 PWM\_SYNC = 1 Devices alligned Device 1

To turn on cursors, press the [Cursors] key on the front panel.

Figure 11. Demonstration of example 2) - PHASE\_DEV=0

AN5803 - Rev 1 page 9/15

To turn on cursors, press the [Cursors] key on the front panel.

KEYSIGHT

KEYSIGHT MSO-X 4154A, MY52400376, 07.20.2017102615: Fri Feb 25 15:51:25 2022 2.000ms/ 4.000ms 3.000000∨ -4.8750∨ Serial 1: CAN ₩ 000 FD 15 00 14 00 00 9-1E64B Normal 1.5GHz 50.0MSa/s 200 FD 04 C-0880E 004 15 00 9C 00 00 F-068DE FD 204 04 5-1B007 FD T<sub>PWM</sub> = 5ms To turn on cursors, press the [Cursors] key on the front panel. Fri Feb 25 15:53:10 2022 \*\* KEYSIGHT AN L1 PWM\_SYNC = 1 Device 0

Figure 12. Demonstration of example 2) – PHASE\_DEV @ device1 = 60 μs

AN5803 - Rev 1 page 10/15

# **Appendix A Reference documents**

**Table 2. Reference documents**

| Document name | Title                                                                      |

|---------------|----------------------------------------------------------------------------|

| DS12879       | 32-channel LED driver with automotive CAN FD Light interface-<br>Datasheet |

AN5803 - Rev 1 page 11/15

## **Revision history**

Table 3. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 10-Jun-2022 | 1       | Initial release. |

AN5803 - Rev 1 page 12/15

## **Contents**

| 1  | PWI    | <b>I</b> l synch | ronization between devices           | .2  |

|----|--------|------------------|--------------------------------------|-----|

|    | 1.1    | Device           | e connection and configuration       | . 2 |

|    | 1.2    | Synch            | ronization sequence                  | . 4 |

|    |        | 1.2.1            | Synchronization sequence–example 1   | . 6 |

|    |        | 1.2.2            | Synchronization sequence – example 2 | . 7 |

| Αp | pendix | A Re             | ference documents                    | 11  |

| Re | vision | history          |                                      | 12  |

## **List of figures**

| Figure 1.  | PWM synchronization between devices via SYNC_I/O pin           | . 2 |

|------------|----------------------------------------------------------------|-----|

| Figure 2.  | Effect of the PWM_SYNC=1 command with PHASE_DEV = 0            |     |

| Figure 3.  | Demonstration of the PWM_SYNC=1 @ PHASE_DEV = "000"            | . 3 |

| Figure 4.  | Effect of the PWM_SYNC=1 command with non-zero PHASE_DEV value | . 3 |

| Figure 5.  | Demonstration of the PWM_SYNC=1 @ PHASE_DEV = "111" (105 µs)   | . 4 |

| Figure 6.  | PWM synchronization between devices via SYNC_I/O pin           | . 5 |

| Figure 7.  | Initial phase shift between 2 devices after POR                | . 6 |

| Figure 8.  | Synchronization sequence example 1)                            | . 7 |

| Figure 9.  | Demonstration of example 1)                                    | . 7 |

| Figure 10. | Synchronization sequence example 2)                            | . 8 |

| Figure 11. | Demonstration of example 2) – PHASE_DEV=0                      | . 9 |

| Figure 12. | Demonstration of example 2) – PHASE_DEV @ device1 = 60 µs      | 10  |

AN5803 - Rev 1 page 14/15

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics - All rights reserved

AN5803 - Rev 1 page 15/15