# 12 V – 150 W power supply based on the STNRG011A digital combo and SRK2001 adaptive synchronous rectifier controller

## Introduction

This application note describes the EVL011A150ADP, a 12 V, 150 W power supply demo board for 90 Vac to 264 Vac mains, which is representative of an AC-DC converter for an all in one (AiO) computer or a general purpose high power adapter.

The design is based on the STNRG011A IC, a digital combo that controls a two stage AC-DC SMPS. The front-end is a transition mode PFC pre-regulator and the second stage is an LLC HB resonant converter. The SRK2001 implements the synchronous rectification in order to obtain a higher efficiency.

No auxiliary supply is needed due to the very low consumption at no load.

A full set of auxiliary functions and protections is also provided; this allows to reduce the overall BOM while maintaining a rugged design.

Figure 1. EVL011A150ADP demo board

# 1 STNRG011A, the digital controller approach

The STNRG011A digital combo is a PFC+LLC digital controller that allows to design high efficiency SMPS with the minimum component count.

Even though the architecture of this demo board is somehow conventional and already seen with analog controllers, the full advantage of a digital implementation using the STNRG011A IC can be obtained without writing a single line of code. In fact, all the firmware and software are embedded in the controller, while the required flexibility can be achieved through a complete set of parameters, stored in its non-volatile memory (NVM), which allows to configure and fine-tune the application.

Moreover, if special, custom, functions are required, they can be coded and written in an external EEPROM. At startup the controller reads this code and integrates it in the original SW.

The same memory is also used by the STNRG011A to store all the housekeeping data.

A two-wire serial bus is used for all the communications between STNRG011A, EEPROM, and an (optional) external device. A programmable asynchronous serial protocol is used for data exchange between the controller and the external unit, while I<sup>2</sup>C allows to access the EEPROM.

A PC, with a dedicated hardware interface that guarantees the galvanic isolation, can be connected to the serial bus of the board, and a windows based application with a graphical user interface (GUI) is available for complete configuration and monitoring of the application.

#### **Related documents**

Additional information and details about parameter settings and the GUI and related hardware can be found in the following documents:

- UM3002 STNRG011A NVM parameters description (see www.st.com)

- UM2945 Getting started with the STEVAL-PCC020V2: USB to I<sup>2</sup>C UART interface board for STNRG01x products (see www.st.com)

This evaluation board has been developed starting from the existing STEVAL-ISA170V1 demo board, based on full analog control. Its application note (AN4677 on www.st.com) can be used to obtain a comparison between a fully analog design and the digital one.

The NVM parameters stored in the STNRG011A are in Section Appendix A.

# 1.1 Target specifications

Table 1 summarizes the main specifications that were considered for the board design.

**Table 1. Target specifications**

| Parameter                                          | Value                                        | Note |

|----------------------------------------------------|----------------------------------------------|------|

| Input mains range                                  | 90 ÷ 264 Vac - frequency 45 ÷ 65 Hz          |      |

| Output power                                       | 0 W - 150 W continuous operation, 200 W peak | 1    |

| Nominal output voltage                             | 12 V                                         |      |

| Output voltage regulation                          | +/- 5%                                       | 2    |

| Ripple / Noise                                     | < 120 mV <sub>p-p</sub>                      | 3    |

| Full load efficiency                               | > 90% at 115/230 Vac                         |      |

| Avg. efficiency (at 25, 50, 75, 100% of full load) | > 90% at 115/230 Vac                         |      |

| Efficiency (at 250 mW)                             | > 60% at 115/230 Vac                         |      |

| No load mains consumption                          | < 75 mW                                      |      |

| Hold-up time                                       | > 10 ms                                      |      |

| Mains harmonics according to                       | EN-61000-3-2 Class-D and JEITA-MITI, Class-D |      |

| EMI                                                | According to EN55022 Class-B                 |      |

| Safety                                             | According to EN60950                         |      |

AN5839 - Rev 2 page 2/60

| Parameter  | Value                                    | Note |

|------------|------------------------------------------|------|

| Dimensions | 175 x 65 x 35 mm                         |      |

| PCB        | Double side, 70 µm, CEM-1, mixed PTH/SMT |      |

- 1. Peak power loading for 100 ms minimum.

- 2. Steady-state and dynamic load (0.5 A/µs), no load to full load.

- 3. Measured over a bandwidth of 20 MHz with a 10  $\mu$ F electrolytic capacitor in parallel with a 100 nF ceramic capacitor placed at the point of measurement.

# 1.2 Electrical diagrams

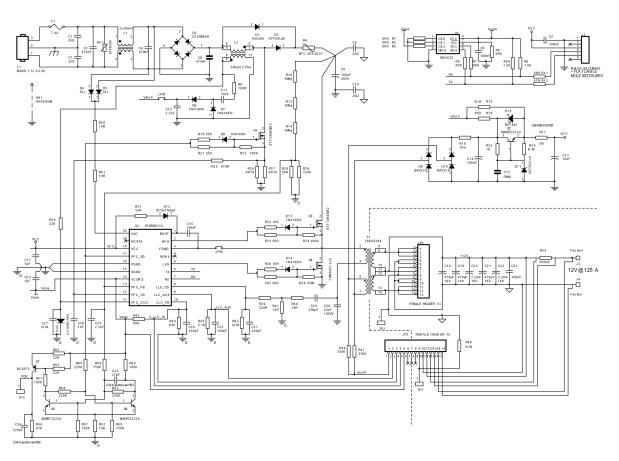

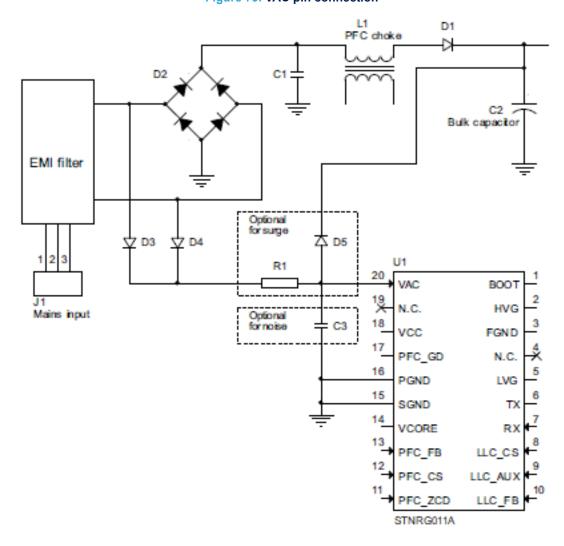

Figure 2. Motherboard electrical diagram

AM040230

AN5839 - Rev 2 page 3/60

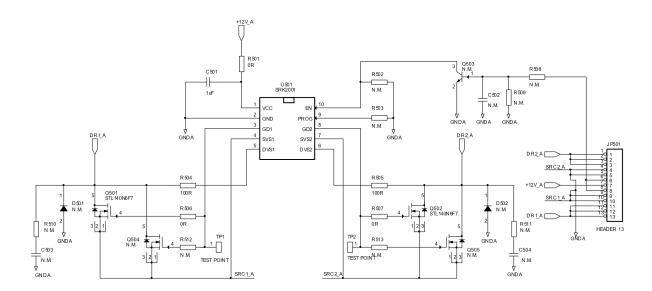

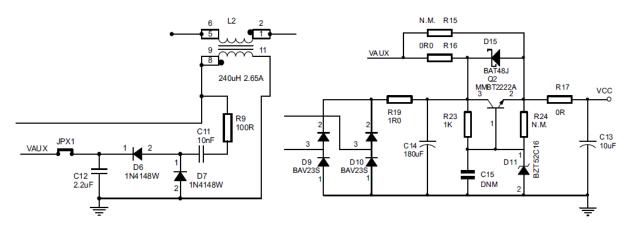

Figure 3. Synchronous rectification (SRK) board electrical diagram

AM040231

AN5839 - Rev 2 page 4/60

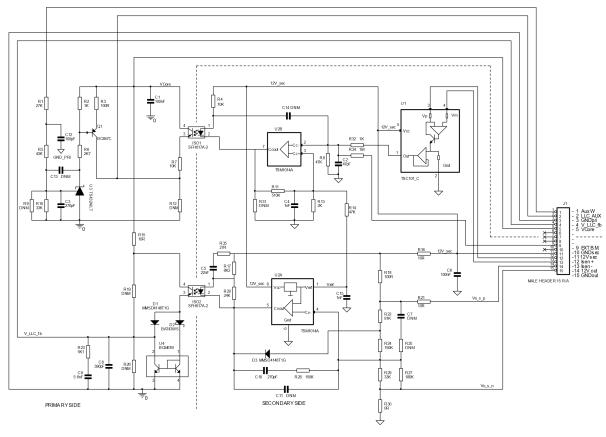

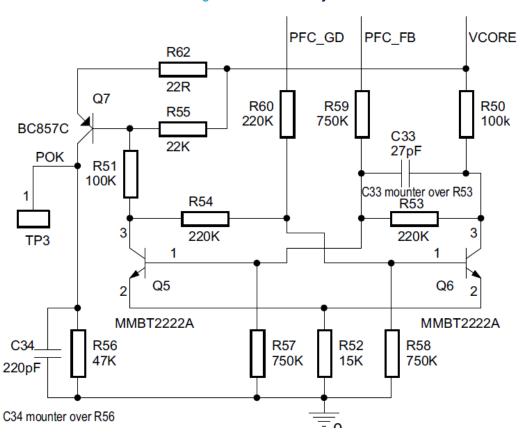

Figure 4. Feedback (control) board electrical diagram

AM040232

## 1.3 Board architecture

The block diagram of the demo board is shown in Figure 5: the architecture is a standard Transition Mode PFC pre-regulator that generates the 400 V bulk voltage and an LLC half-bridge resonant downstream converter that generates the isolated 12 V output. The feedback signal comes from the secondary side with an optocoupler that guarantees galvanic isolation from primary to secondary side. All the compensation related network for the LLC converter is analog and located on the secondary side of the converter. The SRK2001 synchronous rectification is used on the secondary side to increase the overall efficiency of the board.

AN5839 - Rev 2 page 5/60

PFC

B+

LLC

RESONANT

HB

Compensation

& isolation

STNRG011A

Feedback

Figure 5. Block diagram of the demo board

The design of the demo board reflects the analog implementation described in AN4677 (see www.st.com). For this reason, only the major differences are analyzed.

## 1.3.1 PFC power boost

The PFC power section is a standard PFC TM design. The ST proprietary Ramp-enhanced Constant On Time (ReCOT) algorithm of the STNRG011A allows to reach high PF and low THD also with high input capacitance at the mains input. The digital PI filter and a complete set of protections, allow to design the PFC with very low component count.

#### 1.3.2 LLC half-bridge DC-DC converter

The LLC half-bridge resonant converter is designed to have a resonance frequency of about 100 kHz. The ST proprietary Time Shift Control algorithm of the STNRG011A allows high input voltage ripple rejection, even with a single pole compensation. Anyway, due to the tight requirements imposed, the LLC control loop has a more complex configuration than usual. The IC's protections for the LLC stage, always ensure the correct mode of operation, also avoiding entering into the capacitive region, and the new burst mode functionality guarantees the minimum power consumption at low loads.

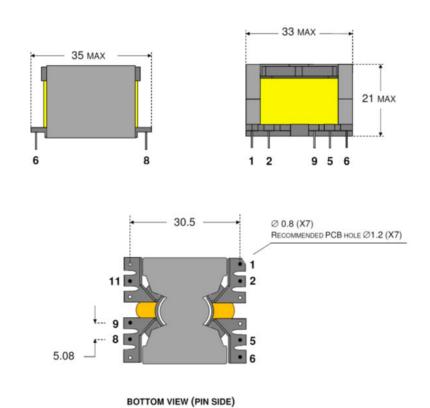

# 1.3.3 Synchronous rectification

The synchronous rectification is the standard SRK2001 demo board with a PowerFLAT 5x6 package STEVAL-ISA168V. The SR-MOSFETs have been changed with the new STripFET F7 Power MOSFET STL140N6F7, which guarantees higher performance and lower switching losses compared with the STL140N4LLF5 mounted on the standard demo board. Also, the disabled circuit has been removed, being the feature not used in this application.

#### 1.3.4 LLC control loop

It is worth noting that the tight requirements imposed, lead to a more complex configuration than usual, while for relaxed specs, conventional solutions can be used.

AN5839 - Rev 2 page 6/60

Table 2 indicates each requirement of the consequent main constraint and its implication.

Table 2. Constraints / implications vs. requirements

| Constraints / implications   | Requirements                                                             |

|------------------------------|--------------------------------------------------------------------------|

| DC accuracy                  | High DC loop gain, remote sense                                          |

| Load transient response      | Controlled large signal behavior, avoid saturation                       |

| Stability                    | Small signal transfer function with adequate phase margin                |

| Output ripple                | High bulk voltage rejection ratio: high gain at twice the line frequency |

| Power consumption at no load | Reduced currents, also for the optocoupler                               |

An analog solution has been chosen to control the output voltage of the SMPS, in order to minimize the delay between an output voltage change and the correction of the time shift value that compensates it; assuring in this way a fast response to load transients and a good dynamic behavior.

The output voltage of the resonant converter is set by means of an analog feedback loop: a TSM1014A, at secondary side, provides a voltage reference and an error amplifier that compares the resistor divided output voltage to its internal reference. The optocoupler's diode cathode is driven by the error amplifier output, while its anode is connected to the output capacitor's array through an R-C parallel network. On the primary side, the optocoupler's phototransistor is configured as an emitter follower and drives the "diode section" of an integrated current mirror (BCM61B). Two diodes, D1 and D2, have been introduced to clamp the current mirror's output in case of overdrive, also avoiding the saturation. The current mirror feeds a complex load and the central node of a voltage divider; this node is also connected to the LLC\_FB pin of the STNRG011A IC, of which the voltage is sampled and converted into a digital number that is used by the SMEDs as the time-shift value for LLC power stage control.

AN5839 - Rev 2 page 7/60

Figure 6 shows the reference circuit diagram of the LLC control loop, used hereafter to describe its behavior.

Mother\_Board Output\_Current V+ R\_sense R\_load Output\_Current Output\_Capacitors\_Array RI V\_core CI D3 *≥* ∑ Rvsh Rldh Rf D1 LLC\_FB D2 Ro TSM1014A\_CV Rvsl Rld Vref Daughter\_Board AM040233

Figure 6. Control loop reference circuit diagram

#### 1.3.4.1 Vout remote sense

Due to the high load current (12.5 A and more during peak power) and being the TSM1014A controller mounted on a daughterboard, it has been chosen to connect the output voltage sense resistors (Rvsh, Rvsl) to the output faston connectors through dedicated PCB traces, as indicated in the circuit diagram in Figure 6.

In this way, the sense circuit is separated from the output current path and a more accurate measure of the voltage at the output terminals can be obtained.

## 1.3.4.2 Secondary side error amplifier

The CV section of the TSM1014A compares the output voltage divided by Rvsh and Rvsl, to its internal reference voltage and drives the cathode of an SFH617A photodiode, while its anode is connected to the output capacitors through RI and CI.

With this configuration the current through the photodiode is controlled by two paths:

- a "slow" one implemented by the TSM1014A and its compensation network.

- a "fast" one composed by the parallel RI and CI.

In static conditions the TSM1014A fixes the operating point and then the output voltage with good accuracy, while in case of fast load transients the photodiode current is modulated also by the output voltage variations through RI and CI, speeding up the response.

AN5839 - Rev 2 page 8/60

#### 1.3.4.3 Primary side optocoupler load

The standard primary side optocoupler's transistor configuration is the common emitter with a resistor of several kilo ohms placed between its collector and the supply. The main drawback of this solution is that the high output capacitance of the phototransistor (approximately 3 nF to 8 nF) with the relatively high resistive load introduces a pole at low frequency in the response of the circuit, with consequent slow transient response.

To avoid this, the load resistor could be reduced, but this would increase the power consumption.

A better solution is instead implemented, connecting the phototransistor as emitter follower that drives a current mirror. In this way the phototransistor sees a low impedance, and the pole is pushed at higher frequencies, while maintaining the required resistive load.

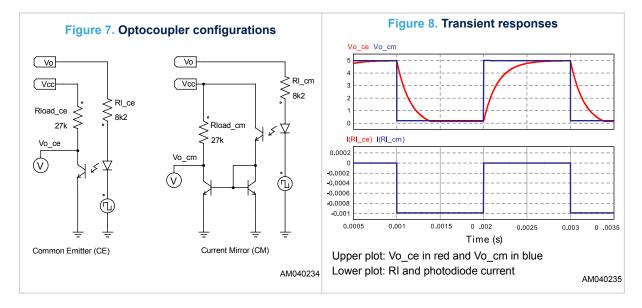

Figure 7 shows the basic circuit diagram used for a simple simulation of the two configurations, while Figure 8 shows the resulting waveforms.

As can be seen, the current mirror configuration is much faster, and in the case of overdrive (due to heavy load transients), it avoids the phototransistor saturation and the consequent delay in response.

In order to analyze this point also in the frequency domain (small signal), a simple circuit that is representative of the actual configuration has been implemented with an SFH617A optocoupler:

- The photodiode was polarized with a DC source with a series resistor, in order to fix the static current at 400 uA.

- The phototransistor was configured either as common emitter or with the current mirror circuit.

In both cases, the same resistive load has been used and it has been connected to a fixed voltage source to set up the bias voltage at 1.5 V.

A network analyzer has been connected to measure the transfer function (output voltage on the resistive load with respect to the photodiode current, in gain and phase) of the two configurations.

Figure 9 below compares the two structures: the current mirror configuration has a bandwidth about an order of magnitude wider than the common emitter.

AN5839 - Rev 2 page 9/60

10.0 270  $\Omega$ 0 225 180 10.0 20.0 135 30.0 90 45 40.0 50.0 100,000 10 100 1,000 10,000 Frequency (Hz) Mag\_[BA] Mag\_B-A] -Phase\_[B/A]-Phase\_[B/A] (cm) (ce) (m) (ce)

Figure 9. CE and CM optocouplers configurations frequency response

SFH617A\_2 FdT common emitter (ce) vs. current mirror (cm)

AM040236

#### 1.3.4.4 Voltage clamps

During heavy load transients, the nodes of the feedback path can be driven well out of the linear region and then the recovery time to the steady-state may be long. For this reason, a clamp mechanism has been introduced, both on the primary and on the secondary side.

On the primary side two diodes, D1 and D2, are placed between the emitter of the phototransistor and the collectors of the two transistors of the current mirror. In this way, in case of an overdrive, when an excess current flows in the optocoupler, D1 conducts and avoids the transistor saturation.

The second diode D2 has been introduced to raise the clamp level of the LLC\_FB voltage to about 360 mV, thus accelerating the response when exiting burst mode.

Moreover, the current mirror load is composed of two resistors, one towards Vcore (equal to 56 k $\Omega$ ) and the other towards ground (equal to 62 k $\Omega$ ), such that when no current flows through the optocoupler, the LLC\_FB voltage is limited to 2.627 V, about 100 mV over the A/D converter full scale of 2.5 V.

The clamp circuit on the secondary side has been introduced to avoid the TSM1014A saturation and to limit the maximum current in the photodiode. This has been done splitting the resistor between Vout and the inverting input of the error amplifier and placing a diode between these two resistors and the TSM1014A output. In steady-state condition the CV- input equals the CV+ (1.25 V of the reference voltage), and then the converter output voltage is at the nominal value of 12 V while the node between the two resistors is at 7.97 V. If the output voltage goes above the regulation point, the TSM1014A output is forced low, but it is clamped to 7.97 V - 0.7 V = 7.27 V because the diode starts conducting.

Taking into account a voltage drop on the phototransistor of 1.1 V, the maximum voltage excursion on the photodiode series resistor (equal to  $8.2~k\Omega$ ) is 12~V-7.27~V-1.1~V=3.63~V, that leads to a maximum current in the photodiode equal to  $3.63~V/8.2~k\Omega=443~\mu A$ . With this current the circuit must guarantee that the LLC\_FB pin voltage goes towards zero (actually below the clamp voltage on the primary side), so the phototransistor has to sink the entire current that is equal to Vcore /  $56~k\Omega=89~\mu A$ .

In other words, when in the photodiode flows the maximum current of 443  $\mu$ A, in the phototransistor 89  $\mu$ A must flow, and then the minimum CTR required for the optocoupler is 89  $\mu$ A / 443  $\mu$ A = 0.2 at a bias current of about 400  $\mu$ A.

AN5839 - Rev 2 page 10/60

#### 1.3.4.5 Control loop stability

A good starting point for the definition of the compensator is the evaluation of the transfer function of the power section (plant). In order to do this, the TSM1014A CV operational amplifier can be overcompensated increasing the Cf value to  $0.1~\mu F$  to  $1~\mu f$  and reducing RF to few hundreds ohms: in this way, the system would behave as having a single pole at low frequency. The plant transfer function can be measured with the network analyzer with this configuration, starting from low output current, and then increasing the output power while observing the output and feedback voltages, immediately stopping in case of signs of instability.

With this approach the result achieved was that the most critical condition from the stability point of view was at full load, when the plant first pole was at the highest frequency and the gain loop has the highest bandwidth, and for this reason the analysis and fine-tune was performed at this condition.

The final plots of the transfer functions of the power section, the compensation network, and the complete gain loop can be found in the performance verification section.

AN5839 - Rev 2 page 11/60

# 2 Functional verification

## 2.1 Startup

As soon as the mains is applied, the STNRG011A starts sinking current from the VAC pin, charging the VCC capacitor. The total VCC capacitor charging time is strictly related to the total capacitance connected to the VCC pin. When the VCC voltage reaches the 17 V threshold (Vcc<sub>On</sub> threshold) the device turns on. It requires at least 1 complete mains cycle to perform the MCC synchronization. After that, the device turns on at the estimated peak of the mains voltage and at the falling edge of the internal MCC line comparator (that is, at about 135° of the sinusoidal voltage), in order to estimate the resonance period of the PFC boost section for TM and valley skipping operation. The PFC soft-start begins at the next mains estimated zero crossing, with a fixed power set by the "PFC pss" parameter.

The PFC soft-start ends when the PFC reaches the value set by NVM with the parameter "PFC Vout SS end (delta)". The NVM of the device installed into the demo board is set in order to end the PFC soft-start when the bulk voltage reaches approximately 396 V. The LLC soft-start begins only at the next mains estimated zero crossing, until the output voltage reaches the regulation. The LLC soft-start ends when the LLC feedback reaches the steady-state condition.

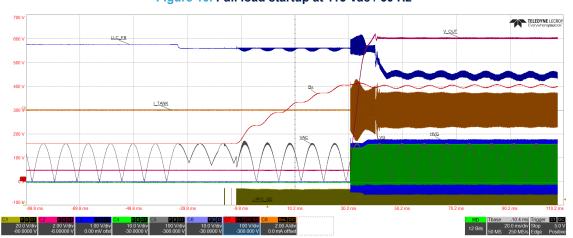

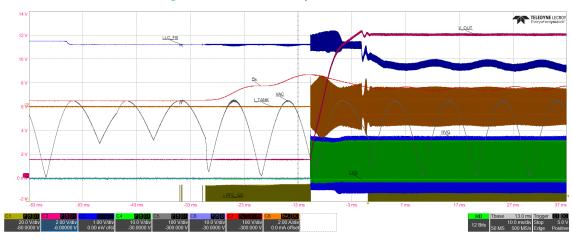

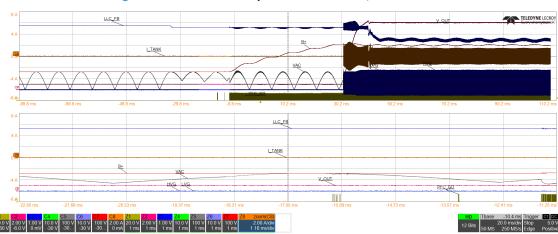

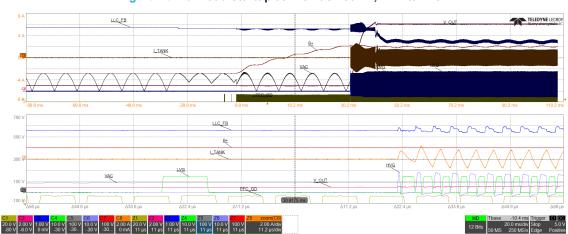

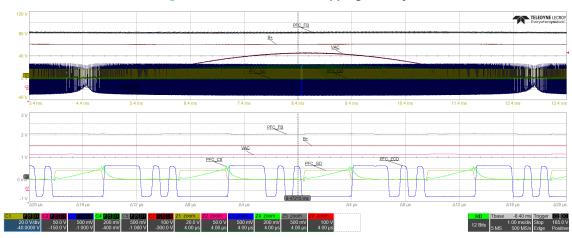

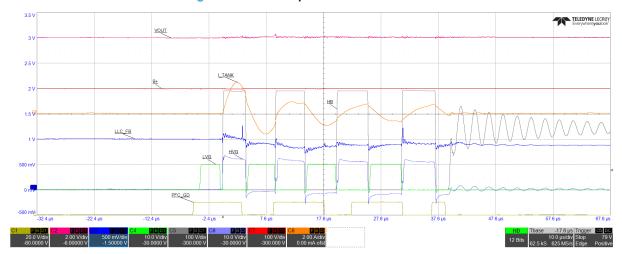

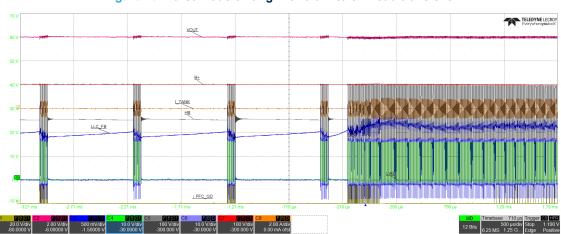

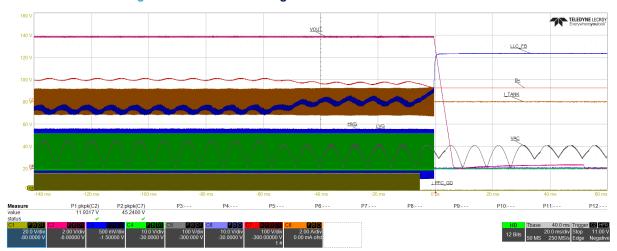

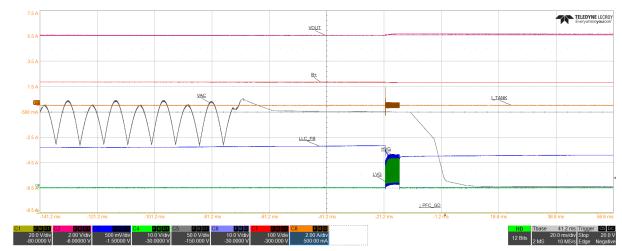

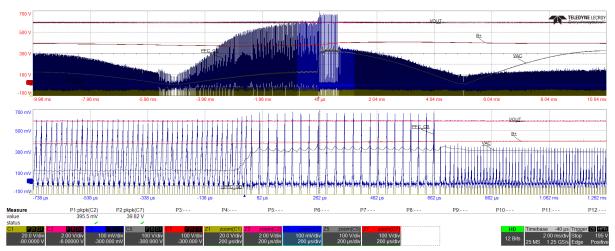

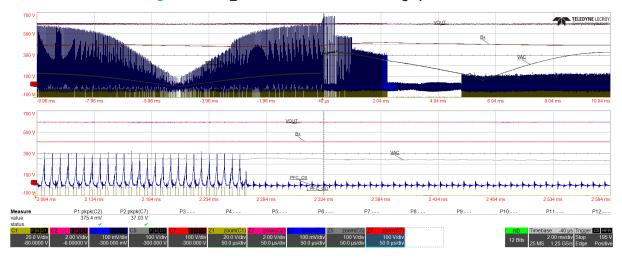

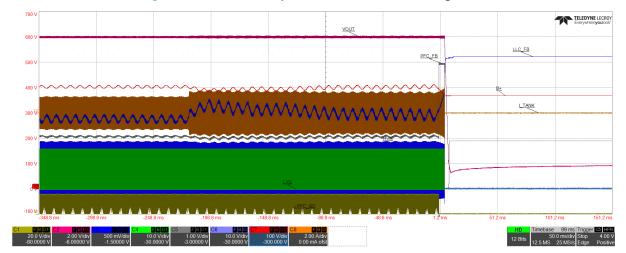

Figure 10 and Figure 11 show the full load startup from the PFC soft-start to the end of the LLC soft-start, when the mains voltage is 115 Vac / 60 Hz and 230 Vac / 50 Hz respectively. Figure 12 shows the PFC synchronization and startup, while Figure 13 shows the LLC startup with the safe start procedure that avoids hard switching during first turn-on.

Figure 10. Full load startup at 115 Vac / 60 Hz

$CH1 = PFC\_GD; CH2 = VOUT; CH3 = LLC\_FB; CH4 = LVG; CH5 = VAC; CH6 = HVG; CH7 = B+; CH8 = I\_TANK$

AN5839 - Rev 2 page 12/60

Figure 11. Full load startup at 230 Vac / 50 Hz

Figure 12. Full load startup at 115 Vac / 60 Hz, PFC turn-on

CH1 = PFC\_GD; CH2 = VOUT; CH3 = LLC\_FB; CH4 = LVG; CH5 = VAC; CH6 = HVG; CH7 = B+; CH8 = I\_TANK

Figure 13. Full load startup at 115 Vac / 60 Hz, LLC turn-on

CH1 = PFC\_GD; CH2 = VOUT; CH3 = LLC\_FB; CH4 = LVG; CH5 = VAC; CH6 = HVG; CH7 = B+; CH8 = I\_TANK

AN5839 - Rev 2 page 13/60

# 2.2 Early warning feature

The STNRG011A has integrated the early warning feature to generate an early warning signal in case the system is shutting down. This feature is important in PC power applications where all the supplied devices must be informed that the power supply is shutting down. The early warning signal is generated on the PFC\_FB pin, putting it up to 5 V and the information is latched with the Q5 and Q6 latch circuitry. The latch is reset as soon as the PFC gate drive restarts switching. Even though the demo board application is an adapter power supply, and the early warning feature is not necessary, it is anyway enabled in order to clarify how a practical application could be. For more information regarding the Power OK circuitry, please refer to the Section Appendix D.3.

## 2.3 PFC operation

## 2.3.1 ReCOT functionality

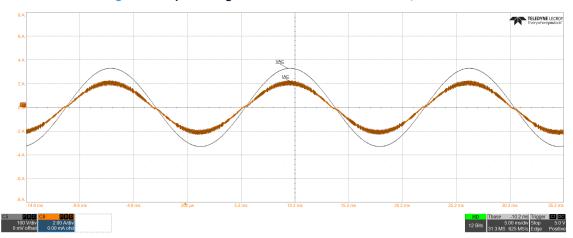

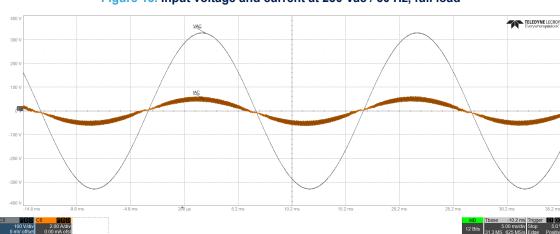

The STNRG011A controls the PFC MOSFET turn-on time with the proprietary Ramp Enhanced Constant On-Time algorithm. It allows to compensate the input EMI filter capacity, to increase the PF and consequently to reduce the THD, keeping it low not only at full load. Figure 14 and Figure 15 show the input voltage and current at 115 Vac / 60 Hz and 230 Vac / 50 Hz respectively.

Figure 14. Input voltage and current at 115 Vac / 60 Hz, full load

CH5 = VAC; CH8 = IAC

Figure 15. Input voltage and current at 230 Vac / 50 Hz, full load

CH5 = VAC; CH8 = IAC

AN5839 - Rev 2 page 14/60

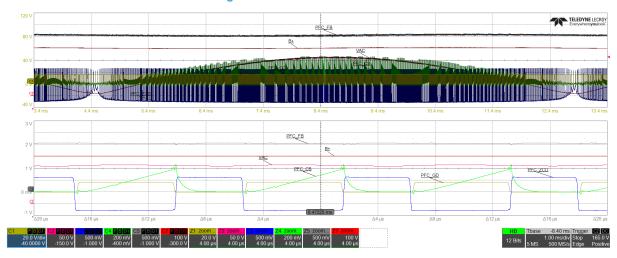

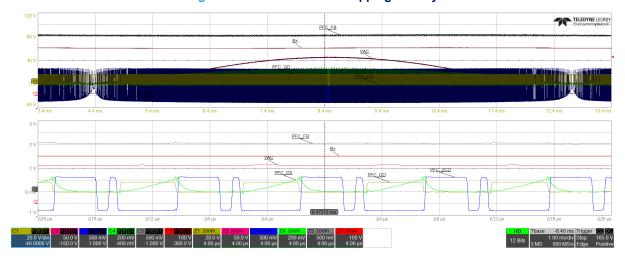

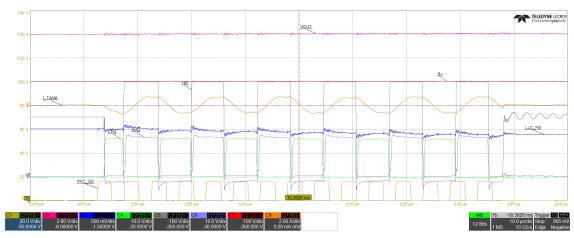

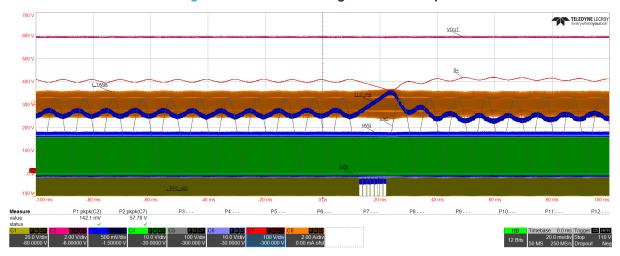

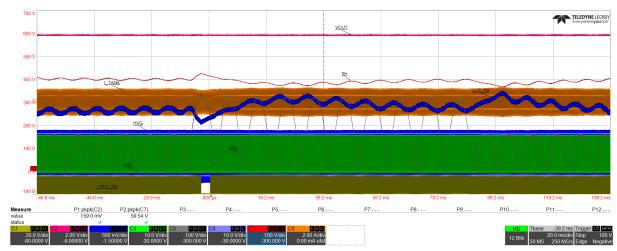

## 2.3.2 Operating modes: transition mode, valley skipping and DCM

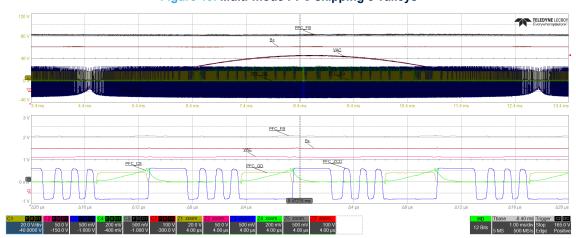

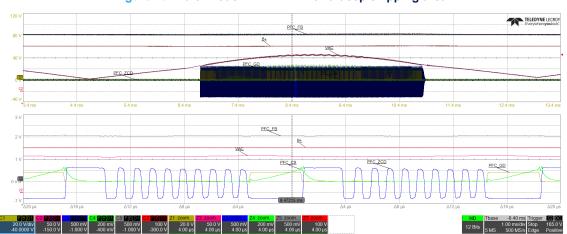

The PFC manager changes the operating mode dynamically, obtaining optimal performance in terms of both efficiency and THD, from transition mode to DCM, passing through one, two or three valley skippings. This is possible thanks to the NVM configurability that allows to fit the IC to the application. Figure 16 to Figure 20 show the different operating modes of the PFC.

Figure 16. Multi-mode PFC in TM

CH1 = PFC\_GD; CH2 = VAC; CH3 = PFC\_ZCD; CH4 = PFC\_CS; CH5 = PFC\_FB; CH7 = B+

Figure 17. Multi-mode PFC skipping 1 valley

CH1 = PFC\_GD; CH2 = VAC; CH3 = PFC\_ZCD; CH4 = PFC\_CS; CH5 = PFC\_FB; CH7 = B+

AN5839 - Rev 2 page 15/60

Figure 18. Multi-mode PFC skipping 2 valleys

CH1 = PFC\_GD; CH2 = VAC; CH3 = PFC\_ZCD; CH4 = PFC\_CS; CH5 = PFC\_FB; CH7 = B+

Figure 19. Multi-mode PFC skipping 3 valleys

CH1 = PFC\_GD; CH2 = VAC; CH3 = PFC\_ZCD; CH4 = PFC\_CS; CH5 = PFC\_FB; CH7 = B+

Figure 20. Multi-mode PFC in DCM and deep skipping area

CH1 = PFC\_GD; CH2 = VAC; CH3 = PFC\_ZCD; CH4 = PFC\_CS; CH5 = PFC\_FB; CH7 = B+

AN5839 - Rev 2 page 16/60

## 2.3.3 Skipping area functionality (below 75 W)

The skipping area feature allows to reduce the PFC dissipated power, turning on the PFC MOSFET only during the peak of the line voltage, either reducing the lost power having reduced the number of switching cycles and increasing the performance of the PFC where the transferred power is more efficient. The skipped area increases when the load decreases and the entering threshold has been set in order to be out of the skipping area feature when the input power is 75 W and above, in order to be compliant with the mains harmonic reduction standards at that power threshold. When the system is working in the skipping area power region, the operating mode and the MOSFET on-time are not fixed but modulated depending on the requested power, as can be seen previously in Figure 20.

# 2.4 LLC operation

## 2.4.1 Symmetric time shift control

The symmetric time shift control is the evolution of the time shift control that always guarantees 50% of duty cycle for the half-bridge resonant converter. The algorithm changes the time between the zero current detection and the MOSFET turn-off of the low-side MOSFET and cycle-by-cycle copies the total on-time to the high-side MOSFET. The time shift applied is directly converted from the LLC\_FB pin, while the deadtime between half-bridge gate drivers is set by the "LLC deadtime" NVM parameter. Figure 21 shows the resonant stage key waveforms at full load.

Figure 21. LLC resonant converter key waveforms

CH1 = PFC\_GD; CH2 = VOUT; CH3 = LLC\_FB; CH4 = LVG; CH5 = HB; CH6 = HVG; CH7 = B+; CH8 = I\_TANK

## 2.5 Burst mode

The STNRG011A has three kinds of burst mode: the LLC\_FB controlled burst mode, the pure external burst mode and the hybrid external burst mode.

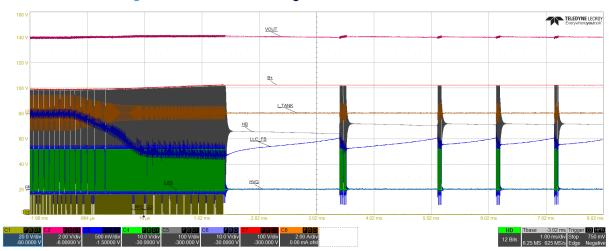

The EVL011A150ADP, and the NVM of the installed STNRG011A, is configured to use the LLC\_FB controlled burst mode, but the demo board is ready for the pure external burst mode, changing two NVM parameters. During burst mode, the PFC is always synchronized with the LLC and the PFC MOSFET on-time is modulated in order to reduce acoustic noise. Figure 22 shows a burst mode sequence at no load.

AN5839 - Rev 2 page 17/60

Figure 22. Burst sequence details at no load

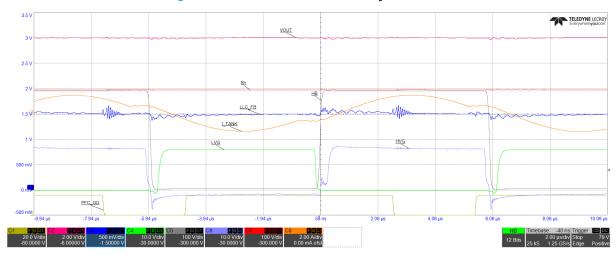

#### 2.5.1 Feedback controlled

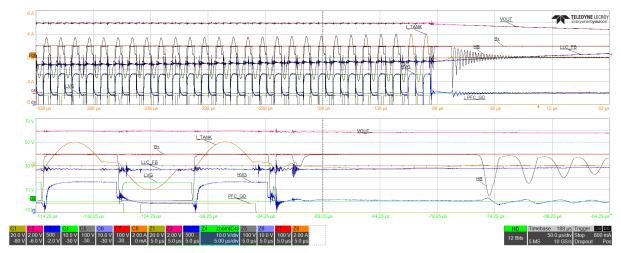

Figure 23 shows the behavior of the demo board when the LLC\_FB voltage goes below the threshold set by the "LLC\_FB burst entering threshold" parameter. After the digital filtering set by the "Burst entering digital filtering" parameter, the system enters burst mode.

Each burst sequence is performed when the LLC\_FB value triggers the wake-up comparator, whose threshold is set by the "LLC\_FB burst wake-up thr" parameter. The number of burst pulses is modulated depending on the load. Figure 22 shows a burst sequence at no load, where the number of burst pulses is the minimum and set by the "Min number of burst pulses" parameter. Figure 24 shows a burst sequence before exiting burst mode, where the number of burst pulses is the maximum and set by the "Max number of burst pulses (delta)" parameter.

If the load increases, as soon as the period of consecutive burst sequences is lower than "Minimum period to exit burst" parameter, the system exits burst. This is shown in Figure 25.

In order to respond on a heavy load transient, the system exits burst mode also in case the LLC\_FB voltage after the burst sequence is sensed higher than the "LLC\_FB burst wake-up thr" parameter minus the hysteresis set by the "LLC\_FB burst wake-up hyst" parameter. This is shown in Figure 26.

Figure 23. Burst mode entering with a full load to 0.3 A transient

CH1 = PFC\_GD; CH2 = VOUT; CH3 = LLC\_FB; CH4 = LVG; CH5 = HB; CH6 = HVG; CH7 = B+; CH8 = I\_TANK

AN5839 - Rev 2 page 18/60

Figure 24. Burst sequence detail with the maximum number of burst pulses set

Figure 25. Burst mode exiting with 0.3 A to 1 A load transient

CH1 = PFC\_GD; CH2 = VOUT; CH3 = LLC\_FB; CH4 = LVG; CH5 = HB; CH6 = HVG; CH7 = B+; CH8 = I\_TANK

Figure 26. Burst mode exiting with 0.3 A to 5 A load transient

CH1 = PFC\_GD; CH2 = VOUT; CH3 = LLC\_FB; CH4 = LVG; CH5 = HB; CH6 = HVG; CH7 = B+; CH8 = I\_TANK

AN5839 - Rev 2 page 19/60

#### 2.5.2 Load current controlled

In order to enable the load current controlled burst mode, it is necessary to change two NVM parameters. In particular, the "External burst mode" parameter must be set to "enabled" and the "LLC\_FB burst entering threshold" parameter must be set to the minimum, otherwise the hybrid external burst mode is enabled, but it is not effective for this demo board.

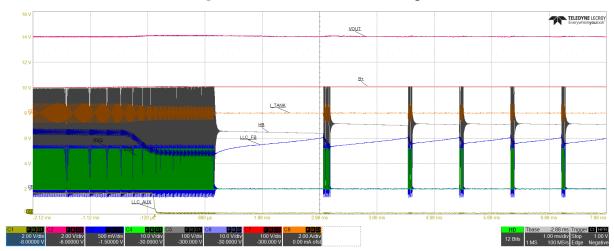

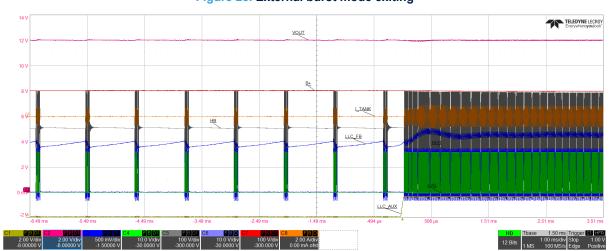

When the secondary side burst mode comparator senses the output current below its threshold, the LLC\_AUX pin is put below 0.8 V and, after the digital filtering set by the "Burst entering digital filtering" parameter, the system enters burst mode, as shown in Figure 27. The burst mode function is still managed by the LLC\_FB voltage and a burst sequence is started when it triggers the wake-up comparator, whose threshold is set by the "LLC\_FB burst wake-up thr" parameter.

The system exits burst mode when the secondary side current level exceeds the comparator threshold and the LLC\_AUX pin is put above 0.9 V. This is shown in Figure 28.

Figure 27. External burst mode entering

CH1 = LLC AUX; CH2 = VOUT; CH3 = LLC FB; CH4 = LVG; CH5 = HB; CH6 = HVG; CH7 = B+; CH8 = I TANK

Figure 28. External burst mode exiting

CH1 = LLC\_AUX; CH2 = VOUT; CH3 = LLC\_FB; CH4 = LVG; CH5 = HB; CH6 = HVG; CH7 = B+; CH8 = I\_TANK

## 2.6 Brown-in / brown-out

The STNRG011A has integrated the mains brown-in / brown-out function. Figure 29 and Figure 30 show both functions when mains voltage changes from 70 Vac to 85 Vac and vice versa.

AN5839 - Rev 2 page 20/60

Figure 29. Brown-in during line transient from 70 Vac to 85 Vac

Figure 30. Brown-out during line transient from 85 Vac to 70 Vac

CH1 = PFC\_GD; CH2 = VOUT; CH3 = LLC\_FB; CH4 = LVG; CH5 = VAC; CH6 = HVG; CH7 = B+; CH8 = I\_TANK

# 2.7 X-Cap discharge

The integrated X-Cap discharge function compliant with IEC 62368-1 is activated anytime there is no activity sensed on the line, for about 50 ms. Figure 31 shows the activation of the XCD function at no load, simulating the cable unplugging on the mains connector. As soon as the STNRG011A detects the inactivity, it restarts LLC switching for 5 ms in order to generate the early warning signal and to keep the output regulated. This feature could be disabled in case the application is not designed to keep the output voltage regulated also at no load, changing the "EW signal in burst mode" NVM parameter from "normal" to "quick". This applies for any early warning managed fault in burst mode.

AN5839 - Rev 2 page 21/60

Figure 31. X-Cap discharge function activation and normal early warning pulse at no load

# 2.8 Mains dip

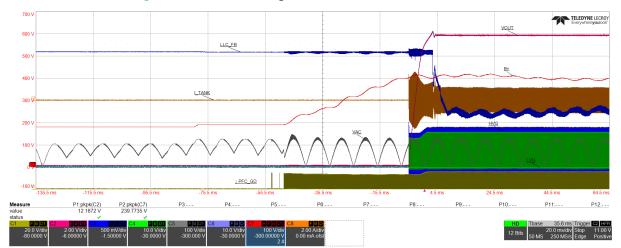

The system was designed to keep the output voltage regulated if a half-cycle mains dip occurs. Figure 32 shows the behavior of the demo board at 230 Vac / 50 Hz: the output voltage stays within the regulation bandwidth during the mains dip.

Figure 32. Waveforms during 10 ms mains dip

CH1 = PFC\_GD; CH2 = VOUT; CH3 = LLC\_FB; CH4 = LVG; CH5 = VAC; CH6 = HVG; CH7 = B+; CH8 = I\_TANK

## 2.9 Line transient

In case a line voltage transient is detected, the STNRG011A immediately adapts the PFC MOSFET turn-on time. Figure 33 shows a line voltage transient from 115 Vac to 230 Vac and vice versa.

AN5839 - Rev 2 page 22/60

Figure 33. Line transient from 115 Vac to 230 Vac and vice versa

## 2.10 Faults managing

## 2.10.1 PFC OCP1

The PFC OCP1 sets the limit for the maximum allowed peak current into the PFC MOSFET. The protection works cycle-by-cycle. If the PFC OC1 comparator threshold is hit, the PFC state machine turns off the PFC gate drive for this cycle and the entire system continues to run. Figure 34 shows the behavior of the PFC during full load line transient from 90 Vac to 265 Vac at the peak of the line.

Figure 34. PFC\_CS hit PFC OC1 comparator

$\mathsf{CH1} = \mathsf{PFC\_GD}; \, \mathsf{CH2} = \mathsf{VOUT}; \, \mathsf{CH3} = \mathsf{PFC\_CS}; \, \mathsf{CH5} = \mathsf{VAC}; \, \mathsf{CH7} = \mathsf{B+}$

## 2.10.2 PFC OCP2

The PFC OCP2 fault is generated when the PFC OC2 comparator is triggered. The protection turns off the PFC MOSFET until the next mains half cycle for a maximum number of times defined by the "Max number of PFC OC2" parameter, beyond which the system shuts down. The counter is decreased every new line half cycle when the PFC OC2 comparator does not trigger any overcurrent for at least one line half cycle. The protection is usually triggered if the PFC coil saturates, and the current is no longer controlled.

AN5839 - Rev 2 page 23/60

#### 2.10.3 PFC SW OVP

The PFC SW OVP fault turns off the PFC MOSFET until the next mains half cycle if the bulk voltage exceeds the value defined by the "PFC SW OVP threshold (delta)" parameter. The fault never shuts down the system. Figure 35 shows the behavior of the converter when the PFC SW OVP is triggered during a line transient.

Figure 35. PFC\_FB hit the software overvoltage protection

CH1 = PFC\_GD; CH2 = VOUT; CH3 = PFC\_CS; CH5 = VAC; CH7 = B+

## 2.10.4 PFC HW OVP

The PFC HW OVP fault immediately shuts down the system as soon as the HW OVP threshold is reached. The PFC SW OVP is usually able to avoid that the PFC HW OVP comparator shuts down the system.

#### 2.10.5 LLC SS timeout

The LLC SS timeout fault is declared if the LLC is stuck in the soft-start state for at least 100 ms. This usually happens when the system starts with the output short circuited and cannot reach the regulation, as shown in Figure 36.

Figure 36. LLC SS timeout protection

CH1 = PFC\_GD; CH2 = VOUT; CH3 = LLC\_FB; CH4 = LVG; CH5 = HB; CH6 = HVG; CH7 = B+; CH8 = I\_TANK

AN5839 - Rev 2 page 24/60

#### 2.10.6 LLC OLP frequency-based management

The LLC OLP frequency-based management allows the system to source an output current higher than the nominal one, for a maximum number of occurrences defined by the "Maximum OLP occurrences" parameter. Figure 37 shows the behavior of the converter in case of a load transition from 12.5 A to 16 A.

Figure 37. LLC overload protection, frequency-based management.

$\label{eq:ch1} \text{CH1} = \text{PFC\_GD}; \text{ CH2} = \text{VOUT}; \text{ CH3} = \text{LLC\_FB}; \text{ CH4} = \text{LVG}; \text{ CH5} = \text{PFC\_FB}; \text{ CH6} = \text{HVG}; \text{ CH7} = \text{B+}; \text{ CH8} = \text{I\_TANK}$

## 2.10.7 LLC OLP time-based management

The LLC OLP time-based management allows the system to source an output current higher than the nominal one, for a maximum allowed time defined by the "LLC OLP timeout" parameter. Figure 38 shows the behavior of the converter in case of a load transition from 12.5 A to 16 A.

Figure 38. LLC overload protection, time-based management

CH1 = PFC\_GD; CH2 = VOUT; CH3 = LLC\_FB; CH4 = LVG; CH5 = PFC\_FB; CH6 = HVG; CH7 = B+; CH8 =  $I\_TANK$

## 2.10.8 LLC OCP2

The LLC OCP2 fault is generated when the LLC OC2 comparator is triggered for a maximum number of times defined by the "Max number of LLC OC2" parameter. This could happen in case of a sudden output short-circuit, as shown in Figure 39. The soft ACP functionality avoids also reaching capacitive region.

AN5839 - Rev 2 page 25/60

Figure 39. LLC\_CS hit the LLC OC2 comparator during output short at full load

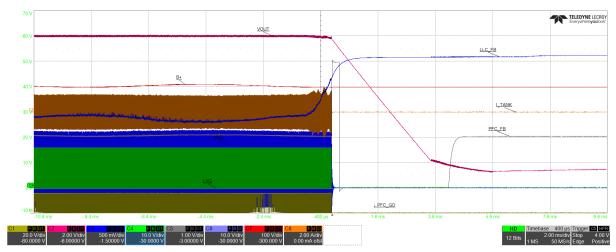

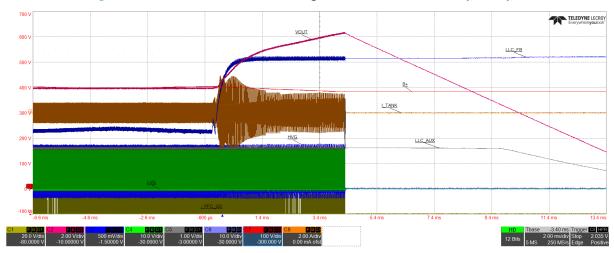

#### 2.10.9 LLC ACP

The LLC ACP feature avoids that the resonant converter works in the capacitive region, losing the soft switching capability. The soft ACP feature intervenes in case the resonant tank is approaching the capacitive region, as shown in Figure 40 in case of a heavy load transient from 12.5 A to 22 A for 1 ms. The feature immediately decreases the time shift value, in order to move aside the capacitive region.

The hard ACP feature intervenes in case the system reaches the capacitive mode, where the resonant tank current changes its sign during deadtime or during the half-bridge MOSFET turn-on instant. Usually, the soft ACP feature avoids entering the capacitive region and loosing ZVS operation, triggering the hard ACP.

Figure 40. LLC soft ACP intervention during heavy load transient

$\mathsf{CH1} = \mathsf{PFC\_GD}; \ \mathsf{CH2} = \mathsf{VOUT}; \ \mathsf{CH3} = \mathsf{LLC\_FB}; \ \mathsf{CH4} = \mathsf{LVG}; \ \mathsf{CH6} = \mathsf{HVG}; \ \mathsf{CH7} = \mathsf{B+}; \ \mathsf{CH8} = \mathsf{I\_TANK}$

## 2.10.10 LLC OVP

The LLC OVP function is active on the LLC\_AUX pin: if the voltage on the auxiliary winding of the LLC resonant transformer is sensed higher than the OVP threshold, the LLC\_AUX pin is brought up to Vcore voltage and the LLC OVP fault is declared, as shown in Figure 41.

AN5839 - Rev 2 page 26/60

Figure 41. LLC OVP simulation, shorting the diode section of the optocoupler

$\label{eq:ch1} \text{CH1} = \text{PFC\_GD}; \text{ CH2} = \text{VOUT}; \text{ CH3} = \text{LLC\_FB}; \text{ CH4} = \text{LVG}; \text{ CH5} = \text{LLC\_AUX}; \text{ CH6} = \text{HVG}; \text{ CH7} = \text{B+}; \text{ CH8} = \text{I\_TANK}$

AN5839 - Rev 2 page 27/60

# 3 Performance verification

The test setup was done with a Chroma AC source and a Chroma DC Electronic Load connected to the board. The tests input voltage was set to 115 Vac / 60 Hz and to 230 Vac / 50 Hz, while the output current was set to the nominal point of measurement.

# 3.1 Efficiency

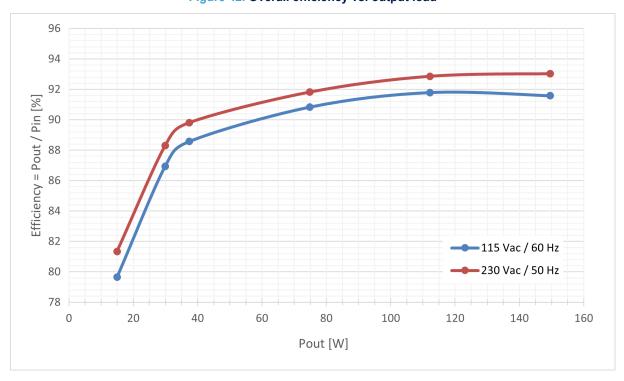

#### 3.1.1 Overall

Table 3 and Figure 42 show the overall efficiency of the EVL011A150ADP demo board, measured at the nominal mains voltages, after a warm-up time of about ½ h at full load after which each measurement point has been kept for about ¼ h, starting from heavy loads down to light loads. Active load has been set in CC mode with output voltage sensing. The output voltage and current have been read on the active load display, while the output power has been computed as Vout \* lout. The input power has been measured through a power meter with voltage probe at the AC inlet of the converter.

| Output Load |                               |          |          | 230 Vac / 50 Hz |       |             |              |          |         |       |

|-------------|-------------------------------|----------|----------|-----------------|-------|-------------|--------------|----------|---------|-------|

| Output Load | Vout [V]                      | lout [A] | Pout [W] | Pin [W]         | η [%] | Vout [V]    | lout [A]     | Pout [W] | Pin [W] | η [%] |

| 10%         | 11.997                        | 1.246    | 14.95    | 18.77           | 79.65 | 11.992      | 1.246        | 14.94    | 18.37   | 81.34 |

| 20%         | 11.985                        | 2.496    | 29.91    | 34.41           | 86.94 | 11.985      | 2.496        | 29.91    | 33.88   | 88.30 |

| 25%         | 11.982                        | 3.121    | 37.40    | 42.22           | 88.57 | 11.983      | 3.121        | 37.40    | 41.64   | 89.81 |

| 50%         | 11.976                        | 6.246    | 74.80    | 82.35           | 90.83 | 11.978      | 6.246        | 74.81    | 81.48   | 91.82 |

| 75%         | 11.970                        | 9.371    | 112.17   | 122.21          | 91.79 | 11.973      | 9.371        | 112.20   | 120.82  | 92.86 |

| 100%        | 11.967                        | 12.495   | 149.53   | 163.27          | 91.58 | 11.966      | 12.495       | 149.52   | 160.71  | 93.03 |

|             | Average (100, 75, 50, 25 %) = |          |          | 90.69           | Ave   | erage (100, | 75, 50, 25 % | ) =      | 91.88   |       |

Table 3. Overall efficiency

AN5839 - Rev 2 page 28/60

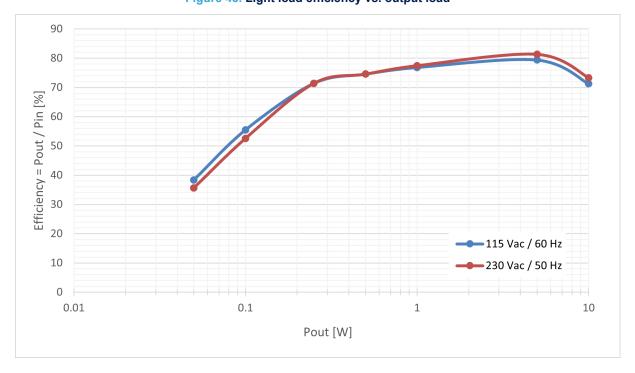

## 3.1.2 Light Load

The light load measurement procedure is described hereafter, while results are shown in Table 4 and Figure 43.

- 1. The board under test is supplied by the AC source and it is loaded by the active load set in CC mode with output voltage sensing. Input power and voltage are measured by a power meter while the output current and voltage are read through multimeters. Output power has been computed as Vout \* lout. At light loads, the current drawn by the board under test from the AC source is irregular and its measurement is typically unstable. To overcome this issue, the active energy consumption is measured by integration in mWh, and the corresponding input power is computed as energy divided by time. For the very light loads, that is, from open load to 500 mW, integration time has been 6 minutes, while for loads between 1 W and 10 W, the integration time has been 36 s.

- 2. Each measurement point is kept for about 5 minutes, hence the values are taken. Loads have been applied increasing the output power from minimum to maximum. For the no load input power measurements, the only connection to the board was the input AC source.

| Output | 115 Vac / 60 Hz |              |          |         |       | 230      | Vac / 50 H   | łz          |         |       |

|--------|-----------------|--------------|----------|---------|-------|----------|--------------|-------------|---------|-------|

| Load   | Vout [V]        | lout<br>[mA] | Pout [W] | Pin [W] | η [%] | Vout [V] | lout<br>[mA] | Pout<br>[W] | Pin [W] | η [%] |

| 0 mW   | 11.992          | -            | -        | 0.051   | -     | 11.993   | -            | -           | 0.063   | -     |

| 50 mW  | 11.995          | 4.16         | 0.05     | 0.13    | 38.38 | 11.997   | 4.16         | 0.05        | 0.14    | 35.65 |

| 100 mW | 11.995          | 8.33         | 0.10     | 0.18    | 55.51 | 11.996   | 8.33         | 0.10        | 0.19    | 52.59 |

| 250 mW | 11.999          | 20.83        | 0.25     | 0.35    | 71.41 | 12.001   | 20.83        | 0.25        | 0.35    | 71.42 |

| 500 mW | 11.995          | 41.66        | 0.50     | 0.67    | 74.58 | 11.995   | 41.66        | 0.50        | 0.67    | 74.58 |

| 1 W    | 11.989          | 83.33        | 1.00     | 1.30    | 76.85 | 11.991   | 83.33        | 1.00        | 1.29    | 77.46 |

| 5 W    | 11.987          | 416.66       | 4.99     | 6.29    | 79.40 | 11.989   | 416.66       | 5.00        | 6.14    | 81.36 |

| 10 W   | 11.993          | 833.33       | 9.99     | 14.03   | 71.23 | 11.994   | 833.33       | 9.99        | 13.63   | 73.33 |

Table 4. Light load efficiency

Figure 43. Light load efficiency vs. output load

AN5839 - Rev 2 page 29/60

# 3.2 Eco design requirement

The most important eco design requirements are summarized in Table 5, Table 6 and Table 7.

Table 5. ENERGY STAR® requirements for computers ver. 6.1

| ENERGY STAR® for computers ver. 6.1 | Test re       | sults         | Limits | Ctatus |  |

|-------------------------------------|---------------|---------------|--------|--------|--|

|                                     | 115Vac / 60Hz | 230Vac / 50Hz | Limits | Status |  |

| Efficiency at 20% load              | 86.72%        | 88.07%        | > 82%  |        |  |

| Efficiency at 50% load              | 91.03%        | 92.12%        | > 85%  | PASS   |  |

| Efficiency at 100% load             | 91.54%        | 93.12%        | > 82%  | PASS   |  |

| Power factor at 100% load           | 0.995         | 0.982         | > 0.9  |        |  |

Table 6. EuP Lot 6 Tier 2 requirements for household and office equipment

| EuP Lot 6 Tier 2                             | Test re       | Limits        | Status  |        |

|----------------------------------------------|---------------|---------------|---------|--------|

| Eur Lot o Hei 2                              | 115Vac / 60Hz | 230Vac / 50Hz | Lillits | Glatus |

| Avg. Efficiency measured at 25, 50, 75, 100% | 90.66%        | 91.94%        | > 87%   |        |

| Efficiency at 250mW load                     | 66.45%        | 66.45%        | > 50%   | PASS   |

| Efficiency at 100mW load                     | 57.03%        | 54.18%        | > 33%   |        |

Table 7. European CoC ver. 5 Tier 2 requirements for external power supplies

| European CoC ver. 5 Tier-2 for Ext. Pow. Sup. | Test          | Limits        | Status   |        |

|-----------------------------------------------|---------------|---------------|----------|--------|

| European Coc ver. 5 Her-2 for Ext. Pow. Sup.  | 115Vac / 60Hz | 230Vac / 50Hz | Lillins  | Status |

| Avg. Efficiency measured at 25, 50, 75, 100%  | 90.66%        | 91.94%        | > 89%    |        |

| Efficiency at 10% load                        | 79.77%        | 81.06%        | > 79%    | PASS   |

| No Load Input Power [W]                       | 0.051 W       | 0.063 W       | < 0.15 W |        |

# 3.3 PFC

## 3.3.1 Harmonics contents measurements

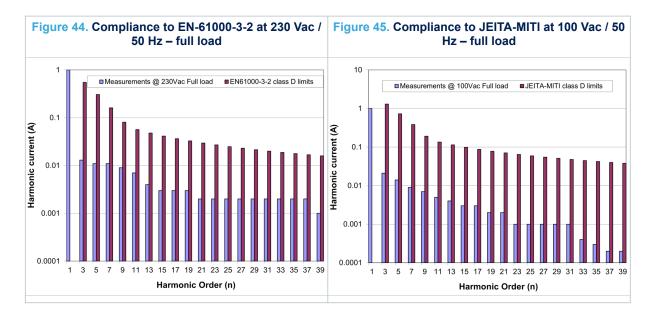

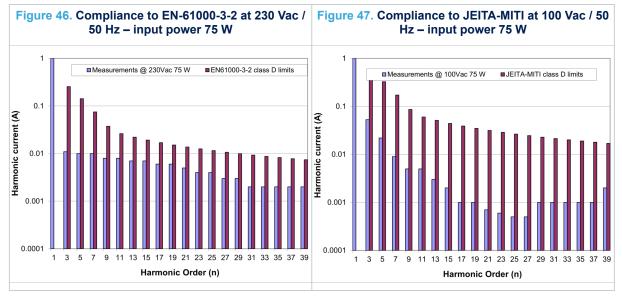

The board has been tested according to the European standard EN-61000-3-2 Class-D and Japanese standard JEITA-MITI Class-D, at 230 Vac and 100 Vac / 50 Hz, both at full load and at 75 W of input power. As reported from Figure 44 to Figure 47, the circuit is able to reduce the harmonics well below the limits of both regulations. The total harmonic distortion and power factor measurements are included in the charts below. The values clearly indicate the correct functionality of the PFC in all conditions.

AN5839 - Rev 2 page 30/60

## 3.3.2 Total Harmonic Distortion and Power Factor

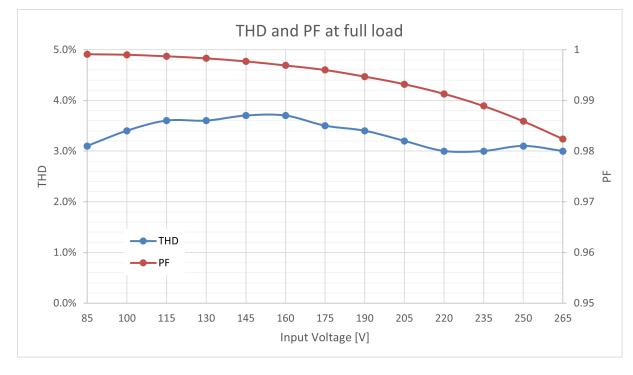

The THD and the PF have been measured at full load varying the input voltage from 85 Vac to 265 Vac. The line frequency has been set to 50 Hz. Figure 48 shows the performance of the converter.

AN5839 - Rev 2 page 31/60

Figure 48. THD and PF at full load, varying input voltage

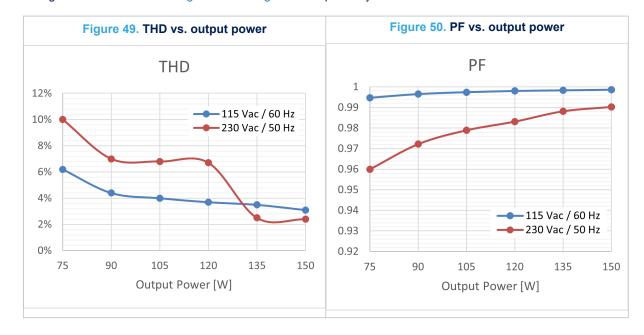

The THD and the PF have been measured also varying the output power from half to full load, with a fixed input voltage. These are shown in Figure 49 and Figure 50 respectively.

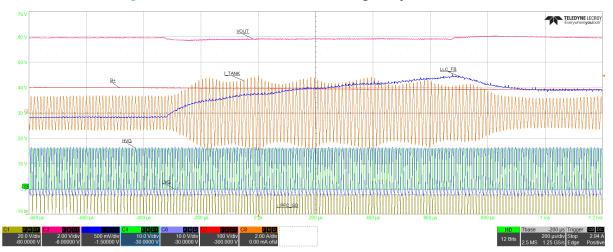

## 3.4 LLC

## 3.4.1 Output voltage regulation

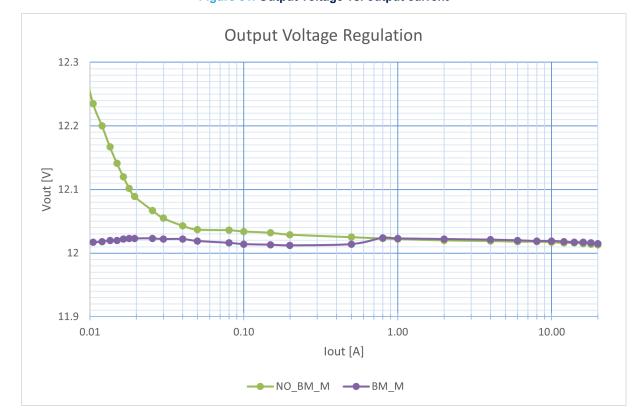

Figure 51 shows the output voltage as a function of the output current in case the burst mode is enabled (standard configuration) or in case it is disabled up to no load.

When burst mode is disabled, at very low output current (less than 30 mA), the output voltage is slightly above the set point (12 V nominal), and it increases up to 13.6 V when the load is disconnected.

On the other hand, when the burst mode is enabled, the regulation is maintained down to no load.

AN5839 - Rev 2 page 32/60

This behavior is due to the fact that the LLC resonant tank is not designed to work at no load, and thus, even with the minimum time shift, there is still enough energy-transfer to drive the output voltage above 12 V. Enabling the burst mode, instead, forces the system to stop and wait before restarting, until the output voltage goes below the regulation point. In this way the output voltage is always in range and the efficiency is increased. The only drawback is a higher output ripple. This strictly depends on two NVM parameters "LLC\_FB burst entering thr" and "Minimum period to exit burst", that allow to set the output-current thresholds to enter / exit the burst mode, and thus also the output voltage ripple.

Figure 51. Output voltage vs. output current

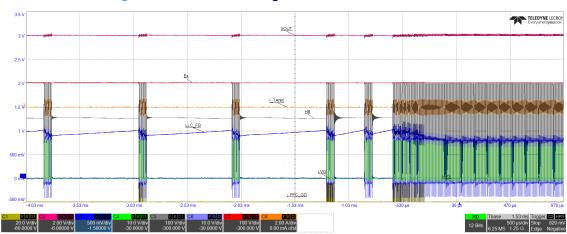

## 3.4.2 Transient response

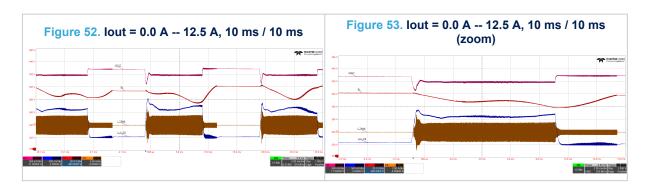

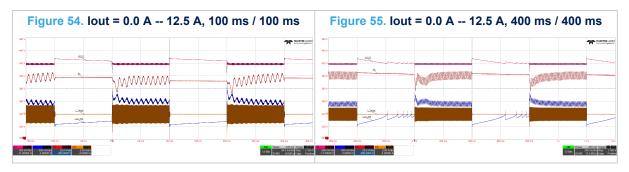

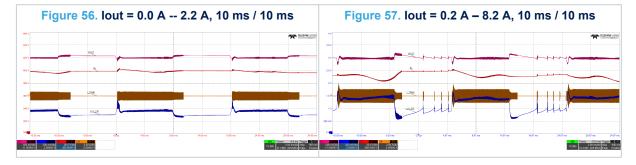

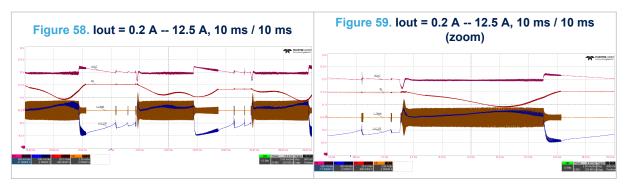

The transient response is shown in the following figures. Test results are not affected by the input voltage and then, in the figures below, the AC input voltage information is not present. Also, the output current variation (dl/dt slope) is always in the order of 2.5 A/us as indicated on the Chroma menu.

Figure 52 and Figure 53 represent the most demanding situation of a load variation with 20 ms period (10 ms / 10 ms), and no load to full load swing.

Figure 54 and Figure 55 show the same load variation, but with longer periods, 200 ms and 800 ms.

Figure 56 is representative of a standby condition, where the load transition is between 0 A and 2.2 A.

Figure 57 shows a transition 0.2 A - 8.2 A with 20 ms period (10 ms / 10 ms).

Figure 58 and Figure 59 are representative of the active mode (0.2 A - 12.5 A).

AN5839 - Rev 2 page 33/60

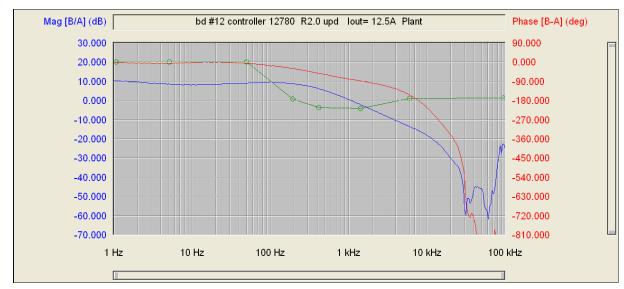

#### 3.4.3 Transfer functions

A network analyzer has been used to evaluate the stability of the SMPS and its design margins.

To simplify the measurement, the resistor R18 (100  $\Omega$ ) on the daughter control board has been shorted, and the injected signal was applied between this point and the output connector.

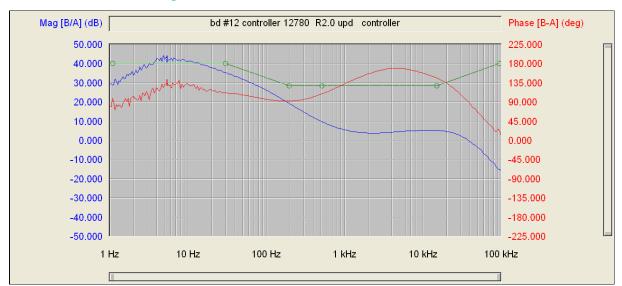

The plant transfer function was measured with a probe connected to the LLC\_FB pin (J1 pin 4) and the other to the output connector J3. It is shown in Figure 60.

The controller transfer function was measured with a probe connected to R18 (shorted) and the other at the LLC\_FB pin. It is shown in Figure 61.

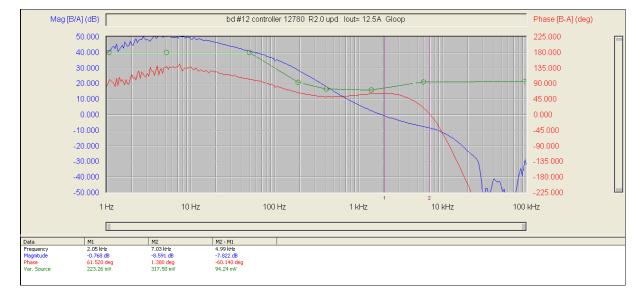

The overall gain loop (Gloop) transfer function was measured with the probes connected at the injection points. The result is shown in Figure 62.

AN5839 - Rev 2 page 34/60

As can be seen, the phase margin is more than 60 degrees, and the loop gain at 100 Hz is about 36 dB, assuring a good stability as well as enough loop gain to reject the bulk voltage ripple.

Figure 60. Plant transfer function at lout = 12.5 A

AN5839 - Rev 2 page 35/60

Figure 62. Gloop transfer function at lout = 12.5 A

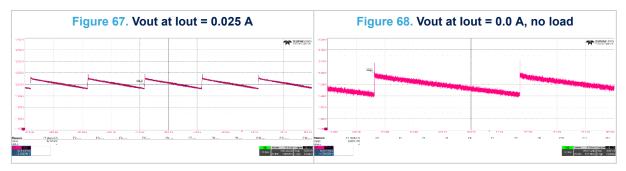

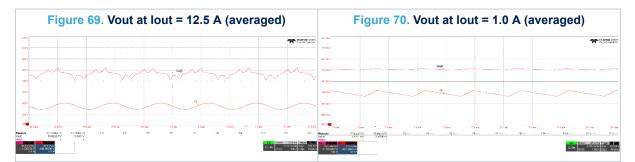

## 3.4.4 Output voltage ripple and noise

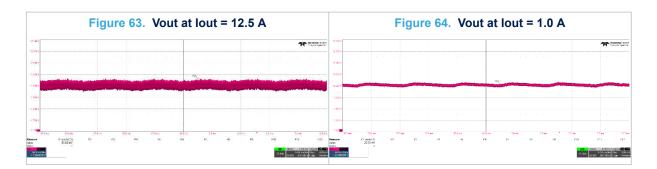

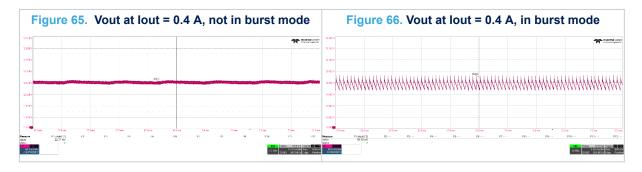

In order to measure the output ripple and noise, an oscilloscope has been used with the vertical channel set-up with a DC offset of about 12 V and a bandwidth of 20 MHz. A 10X probe was connected directly to the output connector of the board, with two capacitors of 10  $\mu$ F and 0.1  $\mu$ F in parallel, placed just at the probe tip.

The line voltage was set to 115 Vac / 60 Hz, then the tests were repeated at 230 Vac / 50 Hz. As no relevant differences appeared during the tests, only the first measurements are reported hereafter.

The table below summarizes the result of the measures of the output voltage corresponding to a load current of 12.5 A, 1.0 A, 0.4 A (out of burst mode), 0.4 A (in burst mode), 25 mA, and no-load.

The corresponding figures from Figure 63 to Figure 68 are also annexed. As can be seen, the ripple and noise values are well below the 120 mV peak-to-peak of the requirement.

Moreover, two averaged acquisitions have been taken to evaluate only the output ripple at 2\*(F-line), while measuring the corresponding bulk voltage variations. These are shown in Figure 69 and Figure 70. In this way, the CMRR of the resonant converter at 2\*(F-line) at a rated output current can be evaluated.

$$CMRR|_{Iout} = 20*Log \left(\frac{\Delta Vout}{\Delta Vbulk}\right)|_{Iout}$$

$$CMRR|_{12.5 A} = 20*Log \left(\frac{10.926 \cdot 10^{-3}}{11.840}\right)|_{12.5 A} = -60.70 \ dB$$

$$CMRR|_{1 A} = 20*Log \left(\frac{1.424 \cdot 10^{-3}}{2.528}\right)|_{1 A} = -64.99 \ dB$$

**Table 8. Vout Ripple and Noise**

| lout              | Vout (peak-to-peak) |

|-------------------|---------------------|

| 12.5 A            | 60.62 mV            |

| 1.0 A             | 25.65 mV            |

| 0.4 A (not in BM) | 22.37 mV            |

| 0.4 A (in BM)     | 68.59 mV            |

| 0.025 A           | 67.04 mV            |

| 0.0 A             | 33.01 mV            |

AN5839 - Rev 2 page 36/60

AN5839 - Rev 2 page 37/60

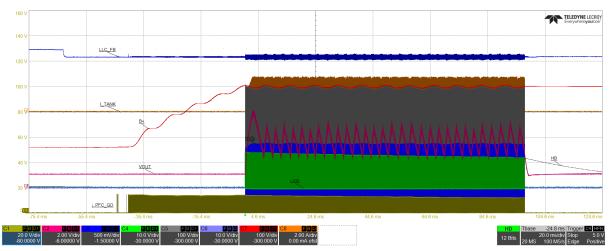

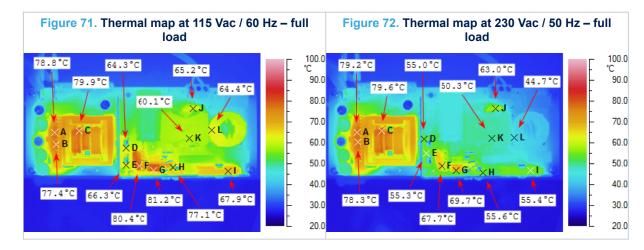

# 4 Thermal map

Thermal mapping with an IR image sensor was performed to verify the design reliability. Figure 71 and Figure 72 below show the thermal measurements of the component side of the board at nominal input voltages. Key components or components showing higher temperatures are highlighted. The ambient temperature during measurement is 26 °C. Table 9 summarizes all the values.

Table 9. Thermal maps reference points

| Point | Reference | Description                   | Temp at 115 Vac / 60 Hz | Temp at 230 Vac / 50 Hz |

|-------|-----------|-------------------------------|-------------------------|-------------------------|

| Α     | Q502      | SR MOSFET                     | 78.8 °C                 | 79.2 °C                 |

| В     | Q501      | SR MOSFET                     | 77.4 °C                 | 78.3 °C                 |

| С     | T1        | Resonant power transformer    | 79.9 °C                 | 79.6 °C                 |

| D     | Q4        | Resonant low-side MOSFET      | 64.3 °C                 | 55 °C                   |

| Е     | Q3        | Resonant high-side MOSFET     | 66.3 °C                 | 55.3 °C                 |

| F     | R4        | Inrush limiting NTC resistor  | 80.4 °C                 | 67.7 °C                 |

| G     | D3        | PFC output diode              | 81.2 °C                 | 69.7 °C                 |

| Н     | Q1        | PFC MOSFET                    | 77.1 °C                 | 55.6 °C                 |

| I     | D2        | Bridge rectifier              | 67.9 °C                 | 55.4 °C                 |

| J     | R9        | Charge pump limiting resistor | 65.2 °C                 | 63 °C                   |

| K     | L2        | PFC inductor                  | 60.1 °C                 | 50.3 °C                 |

| L     | L1        | EMI filtering inductor        | 64.4 °C                 | 44.7 °C                 |

AN5839 - Rev 2 page 38/60

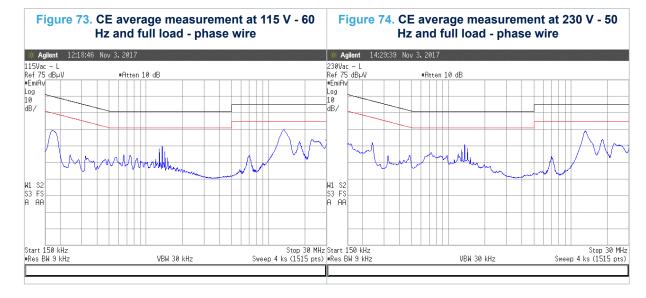

# 5 Conducted emission pre-compliance test

Figure 73 and Figure 74 are the average measurements of the conducted emission noise at full load and nominal mains voltages. The limits shown in the diagrams are EN55022 Class-B, which is the most popular standard for domestic equipment and has more severe limits compared to Class-A, dedicated to IT technology equipment. The EN55022 Class-B limit relevant to average measurements is indicated in red on the diagrams. In all test conditions the measurements are significantly below the limits.

AN5839 - Rev 2 page 39/60

# **Appendix A NVM parameters configuration**

**Table 10. NVM parameters**

| Item | Name                           | Raw  | Value             |

|------|--------------------------------|------|-------------------|

| 0    | Shutdown feature               | 0x00 | 0 = Disabled      |

| 1    | Patch upload from EEPROM       | 0x01 | 1 = Enabled       |

| 2    | ATE mode                       | 0x00 | 0 = Enabled       |

| 3    | System monitoring              | 0x00 | 0 = Enabled       |

| 4    | VAC reading improvement        | 0x01 | 1 = Enabled       |

| 5    | Early warning feature          | 0x00 | 0 = Enabled       |

| 6    | EW signal in burst mode        | 0x01 | 1 = Quick         |

| 7    | Non latched faults timer       | 0x03 | 3 = 4.37s         |

| 8    | Surge detection                | 0x01 | 1 = Enabled       |

| 9    | PFC OC2 detection              | 0x01 | 1 = Enabled       |

| 10   | Max. number of PFC OC2         | 0x02 | 2 = 4             |

| 11   | PFC HW OVP detection           | 0x01 | 1 = Enabled       |

| 12   | LLC OC2 detection              | 0x01 | 1 = Enabled       |

| 13   | Max. number of LLC OC2         | 0x02 | 2 = 4             |

| 14   | LLC OVP detection              | 0x01 | 1 = Enabled       |

| 15   | Disconnection faults detection | 0x01 | 1 = Enabled       |

| 16   | PFC OC2 behavior               | 0x01 | 1 = Latched       |

| 17   | PFC HW OVP behavior            | 0x01 | 1 = Latched       |

| 18   | PFC UVP behavior               | 0x01 | 1 = Adaptive      |

| 19   | LLC SS timeout behavior        | 0x01 | 1 = Latched       |

| 20   | LLC ACP behavior               | 0x00 | 0 = Not Latched   |

| 21   | LLC OC2 behavior               | 0x01 | 1 = Latched       |

| 22   | LLC OLP behavior               | 0x00 | 0 = Not Latched   |

| 23   | LLC OVP behavior               | 0x01 | 1 = Latched       |

| 24   | PFC Ki                         | 0x02 | 8                 |

| 25   | PFC Kp                         | 0x04 | 32                |

| 26   | PFC MOSFET LEB                 | 0x04 | 16 = 267ns        |

| 27   | PFC THD improver base          | 0x05 | 5 = 10mV          |

| 28   | PFC THD improver gain          | 0x00 | 0 = gain disabled |

| 29   | PFC maximum power              | 0x09 | 9216              |

| 30   | PFC pss                        | 0x03 | 2560              |

| 31   | PFC pcc                        | 0x03 | 10238             |

| 32   | PFC min. pin Vskip             | 0x0E | 2176              |

| 33   | PFC max. pin Vskip (delta)     | 0x0A | 2560              |

| 34   | PFC delta pin Vskip            | 0x0C | 352               |

| 35   | PFC maximum DCM power          | 0x0C | 3072              |

| 36   | PFC min. Tsw Vskip             | 0x0C | 448 = 134kHz      |

| 37   | PFC max. Tsw Vskip             | 0x03 | 688 = 87kHz       |

AN5839 - Rev 2 page 40/60

| Item | Name                                   | Raw  | Value                                |

|------|----------------------------------------|------|--------------------------------------|

| 38   | Skipping area threshold                | 0x0A | 1536                                 |

| 39   | PFC Vout target                        | 0x05 | 80 = 2.063V - 400V                   |

| 40   | PFC Vout SS end (delta)                | 0x00 | 8 = 19.5mV - 3.8V                    |

| 41   | PFC UVP threshold (delta)              | 0x01 | 32 = 0.234V - 45V                    |

| 42   | PFC SW OVP threshold (delta)           | 0x02 | 2 = 105mV - 20V                      |

| 43   | Soft ACP feature                       | 0x00 | 0 = Enabled                          |

| 44   | LLC HVG first Ton                      | 0x04 | 24 = 400ns                           |

| 45   | LLC LVG first TS                       | 0x07 | 30 = 400ns                           |

| 46   | LLC deadtime                           | 0x02 | 24 = 400ns                           |

| 47   | LLC soft-start speed                   | 0x01 | 2 = 16.7n                            |

| 48   | Minimum time shift                     | 0x0F | 60 = 625ns                           |

| 49   | Maximum time shift                     | 0x0F | 480 = 7.96us                         |

| 50   | LLC OLP threshold                      | 0x09 | 19 = 309.55mV                        |

| 51   | LLC OLP timeout                        | 0x01 | 1 = 200ms                            |

| 52   | Maximum OLP occurrences                | 0x00 | 0 = 8                                |

| 53   | LLC OLP management                     | 0x00 | 0 = OLP time based management        |

| 54   | ACP sensitivity                        | 0x01 | 1 = High (= 150ns delay)             |

| 55   | Hard ACP detection                     | 0x01 | 1 = Enabled                          |

| 56   | Soft ACP entering threshold            | 0x02 | 14 = 233ns                           |

| 57   | Soft ACP TS decrement                  | 0x05 | 5 = 400ns                            |

| 58   | Maximum soft ACP occurrences           | 0x00 | 0 = 33                               |

| 59   | External burst mode                    | 0x00 | 0 = Disabled                         |

| 60   | BM enter for minimum TS                | 0x01 | 1 = Enabled                          |

| 61   | Burst entering digital filtering       | 0x03 | 18 = 990 us                          |

| 62   | LLC_FB burst entering thr              | 0x2E | 294 = 717.8mV - 1883ns               |

| 63   | LLC_FB burst wake-up thr               | 0x01 | 1 = 1.0V - 2.85us                    |

| 64   | LLC_FB burst wake-up hyst              | 0x01 | 1 = 10mV                             |

| 65   | Min. TS in burst mode                  | 0x13 | 19 = 3.53us                          |

| 66   | Min. number of burst pulses            | 0x02 | 4                                    |

| 67   | Max. number of burst pulses (delta)    | 0x02 | 2                                    |

| 68   | Min. time between burst seq            | 0x01 | 128 = 10.2ms                         |

| 69   | Max. time between burst seq (delta)    | 0x01 | 64 = 4.97ms                          |

| 70   | Minimum period to exit burst           | 0x09 | 9 = 367us                            |

| 71   | No-burst window width                  | 0x01 | 1 = 7.5ms                            |

| 72   | Surge comp digital filtering           | 0x01 | 30 = 500ns                           |

| 73   | PFC CS comp digital filtering          | 0x03 | 3 = 50ns                             |

| 74   | PFC OC2 comp digital filtering         | 0x03 | 24 = 400ns                           |

| 75   | PFC OC1 comp digital filtering (delta) | 0x00 | 2 = +33.3ns                          |

| 76   | PFC ZCD comp digital filtering         | 0x00 | 2 = 33.3ns                           |

| 77   | PFC ZCD comp falling thr               | 0x00 | 0 = 0mV                              |

| 78   | PFC ZCD comp rising thr                | 0x01 | 1 = 110mV (N/A with TH_F[3] = 200mV) |

AN5839 - Rev 2 page 41/60

| Item | Name                              | Raw  | Value          |

|------|-----------------------------------|------|----------------|

| 79   | PFC HW OVP comp digital filtering | 0x00 | 255 = 4.25us   |

| 80   | LLC OLP comp digital filtering    | 0x01 | 1 = 16.7ns     |

| 81   | LLC OC2 comp digital filtering    | 0x03 | 14 = 233.3nsec |

| 82   | LLC ZCD comp digital filtering    | 0x03 | 15 = 250ns     |

| 83   | LLC OVP comp digital filtering    | 0x00 | 255 = 4.25us   |

AN5839 - Rev 2 page 42/60

# Appendix B Bill of materials

Table 11. EVL011A150ADP motherboard bill of materials

| Reference               | Part number / part value | Description                         | Supplier           | Case                    |

|-------------------------|--------------------------|-------------------------------------|--------------------|-------------------------|

| C1, C5, C7, C10         | 2N2                      | Ceramic Y1 capacitor - 250Vac       | Murata             | p10mm                   |

| C2, C6, C23             | 100nF                    | SMD ceramic capacitor X7R           | AVX                | 0805                    |

| C3, C4                  | 470nF                    | Polypropylene X2 capacitor - 275Vac | EPCOS              | 9.0 × 18.0 p15mm        |

| C8                      | 470nF                    | Polypropylene Film Cap 630Vdc       | EPCOS              | Plastic radial          |

| C9                      | 100uF                    | Electrolytic capacitor TXW - 450V   | Rubycon            | DIA 18 x 32 mm          |

| C11                     | 10nF                     | SMD ceramic capacitor X7R - 100V    | AVX                | 1206                    |

| C12                     | 2.2uF                    | SMD ceramic capacitor X7R           | AVX                | 1206                    |

| C13                     | 10uF                     | Electrolytic capacitor YXF          | Rubycon            | DIA 5.0 x 11 mm<br>p2mm |

| C14                     | 180uF                    | Electrolytic capacitor ZLH - 63V    | Rubycon            | DIA10 x 20 mm<br>p5mm   |

| C15                     | N.M.                     | SMD ceramic capacitor               |                    | 1206                    |

| C16                     | 100nF                    | SMD ceramic capacitor X7R           | AVX                | 1206                    |

| C17                     | 1uF                      | SMD ceramic capacitor X7R           | AVX                | 1206                    |

| C18, C19, C21           | 470uF                    | Aluminum polymer capacitor          | Panasonic          | DIA 10 x 13 mm<br>p5mm  |

| C20, C22                | 2.2mF                    | Elect Cap.                          | RUBYCON            | Radial                  |

| C24                     | 1uF                      | SMD ceramic capacitor X7R           | AVX                | 0805                    |

| C25                     | 330pF                    | Ceramic capacitor - 1kV             | MURATA             | 1206                    |

| C26                     | 22nF                     | Film capacitor - 1kV                | EPCOS / TDK        | CKR05                   |

| C27                     | N.M.                     | SMD ceramic capacitor X7R           | AVX                | 0805                    |

| C28                     | 1nF                      | SMD ceramic capacitor X7R           | AVX                | 0805                    |

| C29                     | 2.2nF                    | SMD ceramic capacitor X7R           | AVX                | 0805                    |

| C30                     | 150pF                    | SMD ceramic capacitor X7R           | AVX                | 0805                    |

| C31                     | 220pF                    | SMD ceramic capacitor X7R           | AVX                | 0805                    |

| C32                     | 100pF                    | SMD ceramic capacitor X7R           | AVX                | 0805                    |

| C33 on R53              | 27pF                     | SMD ceramic capacitor X7R           | AVX                | 0805                    |

| C34 on R56              | 220pF                    | SMD ceramic capacitor X7R           | AVX                | 0805                    |

| D1                      | 1N5406                   | General purpose rectifier           | Vishay             | DO-201                  |

| D2                      | D15XB60H                 | Bridge rectifier                    | Shindengen         | 5S                      |

| D3                      | STTH5L06                 | Ultrafast diode                     | STMicroelectronics | DO-201                  |

| D4, D5                  | S1J                      | Diode                               | Vishay             | DO214AC-SMA             |

| D6, D7, D8, D13,<br>D14 | 1N4148W                  | SMD diode                           | Vishay             | SOD123                  |

| D9, D10                 | BAV23S                   | Switching rectifier                 | Diodes Inc.        | SOT23                   |

| D11                     | BZT52C16                 | SMD Zener diode                     | Diodes Inc.        | SOD123                  |

| D12                     | STTH1R06A                | Ultrafast rectifier                 | STMicroelectronics | DO214AC-SMA             |

| D15                     | BAT48J                   | SMD Schottky diode SOD-323          | STMicroelectronics | SOD323                  |

AN5839 - Rev 2 page 43/60

| Reference                           | Part number / part value | Description                                            | Supplier           | Case                  |

|-------------------------------------|--------------------------|--------------------------------------------------------|--------------------|-----------------------|

| D16                                 | 1N4148W-7-F              | Fast switching rectifier                               | Diodes Inc.        | SOD123                |

| F1                                  | T 4A                     | PCB fuse 4A time lag                                   | Littelfuse         | TE5                   |

| HS1                                 | HEAT-SINK                | HEAT SINK FOR D2, Q1, Q3, Q4                           |                    | DWG                   |

| JPX1, JPX2                          | SHORTED                  | WIRE JUMPER                                            |                    | DWG                   |

| JP1                                 | STRIP1X36PF              | FEMALE HEADER 13 pin                                   |                    | p2.54mm               |

| JP2                                 | STRIP1X36PF              | FEMALE HEADER 15 pin – pin 6,7,8 removed               |                    | p2.54mm               |

| J1                                  | MKDS 1,5/ 3-5,08         | AC socket                                              | Phoenix Contact    | 3P - p5mm             |

| J2                                  | MOLEX 90325-0006         | Molex PicoFlex connector 6P 1,27mm pitch               | MOLEX              | 1.27mm pitch          |

| J3                                  | FASTBFH/A1/6,3           | Faston .250 TAB PCB                                    | KEYSTONE           | DWG                   |

| J4                                  | FASTBFH/A1/6,3           | Faston .250 TAB PCB                                    | KEYSTONE           | DWG                   |

| L1                                  | 2x28mH                   | Input EMI filter                                       | Magnetica          | DWG                   |

| L2                                  | 240uH 2.65A              | PFC INDUCTOR - add Kapton to isolate inductor from PCB | Magnetica          | DWG                   |

| Q1                                  | STF24N60M2               | Power MOSFET                                           | STMicroelectronics | TO220-FP              |

| Q2, Q5, Q6                          | MMBT2222A                | SMD NPN transistor                                     |                    | SOT23                 |

| Q3, Q4                              | STF13N60M2               | Power MOSFET                                           | STMicroelectronics | TO220-FP              |

| Q7                                  | BC857C                   | Trans. PNP General Purpose                             | NXP                | SOT23                 |

| RV1                                 | S14K300                  | Metal oxide varistor                                   | EPCOS              | DIA.15x5 mm<br>p7.5mm |

| R1, R2, R3, R5, R6,<br>R7, R11, R16 | 0R0                      | SMD resistor                                           | Vishay             | 0805                  |

| R4                                  | NTC 2R5-S237             | NTC resistor S237                                      | EPCOS              | DWG                   |

| R8, R49                             | 1.5K                     | SMD resistor                                           | Vishay             | 0805                  |

| R9                                  | 100R                     | SMD resistor 1/2W                                      | Vishay             | 1206                  |

| R10, R13, R14                       | 3M                       | SMD resistor                                           | Vishay             | 1206                  |

| R12                                 | 47R                      | SMD resistor                                           | Vishay             | 0805                  |

| R15, R24                            | N.M.                     | SMD resistor                                           | Vishay             | 0805                  |

| R17                                 | 0R                       | SMD resistor                                           | TTI                | 0805                  |

| R18, R32, R36                       | 10R                      | SMD resistor                                           | Vishay             | 0805                  |

| R19                                 | 1R0                      | SMD resistor                                           | Vishay             | 1206                  |

| R20, R31, R61                       | 10R                      | SMD resistor                                           | Vishay             | 1206                  |

| R21, R62                            | 22R                      | SMD resistor                                           | Vishay             | 0805                  |

| R22, R34, R38, R50,<br>R51          | 100K                     | SMD resistor                                           | Multi-Comp         | 0805                  |

| R23                                 | 1K                       | SMD resistor                                           | Vishay             | 0805                  |

| R25                                 | 470R                     | SMD resistor                                           | Vishay             | 0805                  |

| R26, R27                            | 0R18                     | SMD resistor                                           | YAGEO (PHYCOMP)    | 2512                  |

| R28, R42                            | 56K                      | SMD resistor                                           | Multi-Comp         | 0805                  |

| R29                                 | 330K                     | SMD resistor                                           | Multi-Comp         | 0805                  |

| R30, R55                            | 22K                      | SMD resistor                                           | Vishay             | 0805                  |

| R33, R37                            | 56R                      | SMD resistor                                           | Vishay             | 0805                  |

AN5839 - Rev 2 page 44/60

| Reference     | Part number / part value | Description                          | Supplier           | Case  |

|---------------|--------------------------|--------------------------------------|--------------------|-------|

| R35           | 0R002                    | SMD resistor                         | YAGEO              | 2512  |

| R39           | 220R                     | SMD resistor                         | Vishay             | 1206  |

| R40           | 15R                      | SMD resistor                         | Vishay             | 0805  |

| R41           | 12R                      | SMD resistor                         | Multi-Comp         | 0805  |

| R44           | 62K                      | SMD resistor                         | Multi-Comp         | 0805  |

| R45           | 5K1                      | SMD resistor                         | Multi-Comp         | 0805  |

| R46, R47      | 330K                     | SMD resistor                         |                    | 1206  |

| R48           | N.M.                     | SMD resistor                         | Vishay             | 0805  |

| R52           | 15K                      | SMD resistor                         | Multi-Comp         | 0805  |

| R53, R54, R60 | 220K                     | SMD resistor                         | Multicomp          | 0805  |

| R56           | 47K                      | SMD resistor                         | Multi-Comp         | 0805  |

| R57, R58, R59 | 750K                     | SMD resistor                         | Multi-Comp         | 0805  |

| TP1, TP2, TP3 | TEST POINT               | Testpoint                            |                    |       |

| T1            | 1860.0164                | LLC transformer                      | Magnetica          | ETD34 |

| U1            | M24C32                   | 32-Kbit I <sup>2</sup> C 1MHz EEPROM | STMicroelectronics | SO-8  |

| U2            | STNRG011A                | Digital combo controller             | STMicroelectronics | SO-20 |

Table 12. EVL011A150ADP daughter (control) board bill of materials

| Reference    | Part number / part value | Description                                     | Supplier | Case    |

|--------------|--------------------------|-------------------------------------------------|----------|---------|

| C1, C6       | 100nF                    | SMD ceramic capacitor X7R                       | SCI      | 0603    |

| C2           | 47pF                     | SMD ceramic capacitor C0G/NP0                   | SCI      | 0603    |

| C3, C10      | 270pF                    | SMD ceramic capacitor X7R                       | SCI      | 0603    |

| C4, C15      | 1nF                      | SMD ceramic capacitor X7R                       | SCI      | 0603    |

| C5           | 22nF                     | SMD ceramic capacitor X7R                       | SCI      | 0603    |

| C7, C11, C13 | N.M.                     | SMD ceramic capacitor                           |          | 0805    |

| C8           | 390pF                    | SMD ceramic capacitor C0G/NP0                   | SCI      | 0603    |

| C9           | 5.6nF                    | SMD ceramic capacitor C0G/NP0                   | SCI      | 0805    |

| C12          | 100pF                    | SMD ceramic capacitor C0G/NP0                   | SCI      | 0603    |

| C14          | N.M.                     | SMD ceramic capacitor                           | SCI      | 0603    |

| D1, D3       | MMSD4148T1G              | Switching rectifier                             | SCI      | SOD123  |

| D2           | BAT43WS                  | Schottky rectifier                              | SCI      | SOD323  |

| ISO1, ISO2   | SFH617A-2                | Optocoupler                                     | Vishay   | DIP4    |

| J1           | MALE HEADER 15 R/A       | Strip Male 15 Pin, 90° - pin 6,7,8,9,10 removed | SCI      | p2.54mm |

| Q1           | BC857C                   | Trans. PNP General Purpose                      | SCI      | SOT23   |

| R1           | 27K                      | SMD resistor                                    | SCI      | 0805    |

| R2           | 1K                       | SMD resistor                                    | SCI      | 0805    |

| R3, R18      | 100R                     | SMD resistor                                    | SCI      | 0603    |

| R4, R7       | 10K                      | SMD resistor                                    | SCI      | 0603    |