Application note

## STPMIC1 auto turn-on

#### Introduction

The STPMIC1 is provided with an auto turn-on feature that allows the device to be turned ON automatically as soon as VIN rises above a valid threshold voltage.

See section "VIN conditions and monitoring" in STPMIC1 datasheet for more details.

# 1 Auto turn-on VIN sequence

An auto turn-on event is normally triggered only after the device exits from the NO\_SUPPLY state (VIN<V $_{IN\_POR\_Fall}$ ) and VIN continues increasing, crossing also the "V $_{INOK\_Rise}$  threshold".

In more detail, as soon as the VIN rises above the  $V_{INOK\_Rise}$  threshold, the STPMIC1 goes to PRELOAD\_NVM state and loads the AUTO\_TURN\_ON bit from NVM.

If the AUTO\_TURN\_ON bit is set, the STPMIC1 goes directly into CHECK&LOAD then goes to POWER\_UP followed by the POWER\_ON sequence. Otherwise, the device remains in PRELOAD\_NVM state and all the regulators output stays disabled.

AN5861 - Rev 1 page 2/11

### 1.1 INTLDO internal voltage and auto turn-on sequence

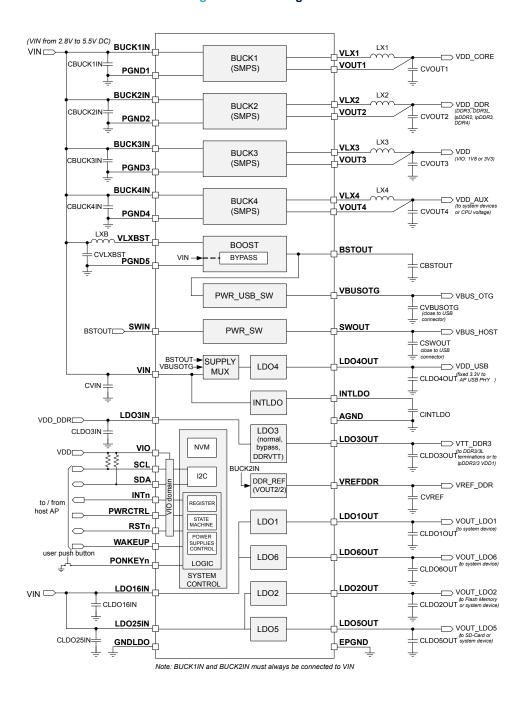

The STPMIC1 internal circuitries are supplied by the INTLDO voltage generated by an internal LDO (supplied from the VIN voltage pin) and compensated by the external CINTLDO output capacitor (see Figure 1).

The INTLDO regulator takes part in the regular auto turn-on sequence occurring when the VIN voltage is applied at startup. The CINTLDO capacitor needs to be discharged at every VIN startup cycle.

Figure 1. Block diagram

#### 1.2 CINTLDO charge status and VIN bounces

The CINTLDO charge status is important also in case of unwanted VIN voltage bounces, which may occur after a correct auto turn-on sequence is completed.

AN5861 - Rev 1 page 3/11

In fact, if a voltage bounce event occurs, causing the VIN to go below the "V<sub>INOK\_Fall</sub> threshold" for a short time but fast enough to keep the CINTLDO capacitor still charged, when the VIN rises again above the VINOK threshold, the auto turn-on sequence timing is violated, and the device disables all the outputs rails and does not respond to any command until the CINTLDO is discharged and the turn-on sequence is restarted.

#### 1.2.1 Auto turn-on suggestion against VIN bounces

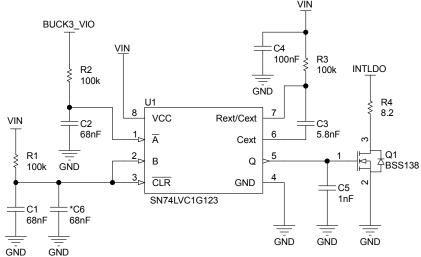

VIN BUCK3\_VIO

Figure 2. INTLDO additional circuit example

Passive components example:

- $R1 = R2 = R3 = 100 \text{ k}\Omega$

- $R4 = 8.2 \Omega$

- C1 = C2 = 68 nF

- C3 = 5.8 nF

- C4 = 100 nF

- C5 = 1 nF

- \*C6 = to insert for additional power ON delay

The proposed above additional circuit allows the PMIC to perform the auto turn-on sequence in case of possible VIN brownout reaching the following thresholds in a short time (< 2 ms):

VIN < V<sub>INPOR Fall</sub> threshold

Note:  $(V_{INPOR Fall} = 2.1 V typ.)$

VINPOR Fall < VIN < VINOK Fall.

Note:  $(V_{INOK\_Fall} = V_{INOK\_Rise} - V_{INOK\_HYST}$  where  $V_{INOK\_Rise}$  and  $V_{INOK\_HYST}$  are NVM programmable)

Following the truth table valid for the SN74LVC1G123:

AN5861 - Rev 1 page 4/11

| Inputs   |          |   | Outputs |

|----------|----------|---|---------|

| CLR      | Ā        | В | Q       |

| L        | X        | X | L       |

| X        | Н        | X | L       |

| X        | X        | L | L       |

| Н        | L        | 1 | л       |

| Н        | <b>↓</b> | Н | л       |

| <b>↑</b> | L        | Н | Л       |

Table 1, SN74LVC1G123 truth table

On the A pin of the SN74LVC1G123, one 3.3 V output channel of the PMIC1 (that is, Buck 3 output of figure 2 example) is applied, which is monitored to trigger the PMIC power OFF caused by the VIN brownout.

The values of R2 and C2 determine the delay between the negative slope of  $\overline{A}$  and the pulse generated on Q (when  $\overline{CLR}$  and B are high).

VIN of PMIC1 is applied to the pins B =  $\overline{\text{CLR}}$  and VCC.

The values of R1 and C1 determine the delay between the positive slope of B =  $\overline{\text{CLR}}$  and the pulse generated on Q (when  $\overline{\text{A}}$  is low).

The duration of the pulse generated on Q output depends on the values of R3 and C3 used on pins Rext/Cext and Cext. The pin Rext/Cext is connected to VIN, and the C4 is an additional cap used as VIN filter.

The output Q of SN74LVC1G123 drives Q1 NMOS.

In order to perform the auto turn-on sequence in case of possible VIN brownout, the INTLDO capacitor needs to be discharged below its internal POR threshold allowing the NVM content to be reloaded and restarting the turn-on sequence.

This is achieved by connecting the INTLDO pin to the NMOS drain, close to GND for a pulse period defined by R3/C3

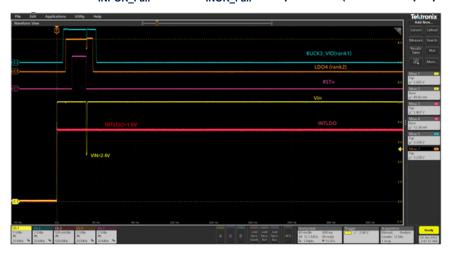

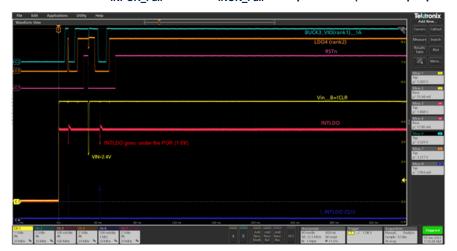

The following scope plots show the behavior of the PMIC1 when a VIN bounce occurs:

Figure 3. VIN brownout under the V<sub>INPOR Fall</sub> after power-on (without the proposed circuit)

AN5861 - Rev 1 page 5/11

Figure 4. VIN brownout under the V<sub>INPOR\_Fall</sub> after power-on (with the proposed circuit).

Figure 5. VIN brownout to  $V_{INPOR\_Fall} < VIN < V_{INOK\_Fall}$  after power-on (without the proposed circuit)

Figure 6. VIN brownout to  $V_{INPOR\_Fall} < VIN < V_{INOK\_Fall}$  after power-on (with the proposed circuit)

AN5861 - Rev 1 page 6/11

## **Revision history**

Table 2. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 29-Nov-2022 | 1       | Initial release. |

AN5861 - Rev 1 page 7/11

## **Contents**

| 1   | Auto  | turn-o  | n VIN sequence                               | 2 |

|-----|-------|---------|----------------------------------------------|---|

|     | 1.1   | INTLD   | O internal voltage and auto turn-on sequence | 3 |

|     |       |         | DO charge status and VIN bounces             |   |

|     |       | 1.2.1   | Auto turn-on suggestion against VIN bounces  | 4 |

| Rev | ision | history |                                              | 7 |

AN5861 - Rev 1

## **List of tables**

| Table 1. | SN74LVC1G123 truth table  | 5 |

|----------|---------------------------|---|

| Table 2. | Document revision history | 7 |

AN5861 - Rev 1 page 9/11

# **List of figures**

| Figure 1. | Block diagram                                                                                                     | 3 |

|-----------|-------------------------------------------------------------------------------------------------------------------|---|

| Figure 2. | INTLDO additional circuit example                                                                                 | 4 |

| Figure 3. | VIN brownout under the $V_{\mbox{\footnotesize INPOR\_Fall}}$ after power-on (without the proposed circuit)       | 5 |

| Figure 4. | VIN brownout under the V <sub>INPOR_Fall</sub> after power-on (with the proposed circuit)                         | 6 |

| Figure 5. | VIN brownout to $V_{INPOR\_Fall} < VIN < V_{INOK\_Fall}$ after power-on (without the proposed circuit)            | 6 |

| Figure 6. | VIN brownout to V <sub>INPOR_Fall</sub> < VIN < V <sub>INOK_Fall</sub> after power-on (with the proposed circuit) | 6 |

AN5861 - Rev 1 page 10/11

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics - All rights reserved

AN5861 - Rev 1 page 11/11