## Guidelines for design and board assembly of land grid array packages

#### Introduction

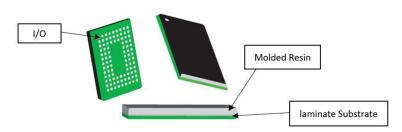

This application note provides guidelines for the handling and assembly of LGA packages on a printed circuit board. Land grid array(LGA) are molded array packages based on laminate interposer, which have an external pin or I/O on the bottom of the package arranged in columns and rows as shown in Figure 1.

This document presents the general guidelines and suggestions for robust and reliable board assembly of the LGA packages, especially proper board and stencil design, assembly and rework. To develop a specific solution, actual experience and development efforts are required to optimize the assembly process and match the individual device requirements.

Figure 1. LGA package type

### 1 Packages

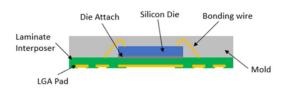

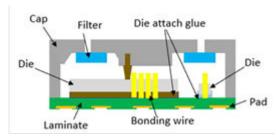

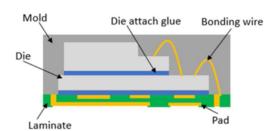

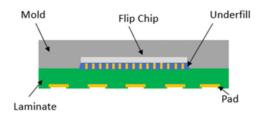

LGA is like a BGA but without the solder sphere or like a QFN package but with a laminate interposer. It is a resin molding package with a laminate substrate with Nickel Gold (NiAu) plated terminations and some LGAs have capping layers. Some typical LGA cross-section views are as shown below in Figure 2, Figure 3, Figure 4 and Figure 5.

The external pins or terminations have a land structure and are arranged on the bottom surface and edges of the package. The land pattern could be either in the shape of a circle, square or rectangular. Some packages have large plane or exposure pads for thermal dissipation. It can be mounted on boards just like any other SMD package.

The interconnection is formed only by the solder paste, which results in a lower stand-off suitable for a product that requires a more compact design.

Figure 2. LGA with over mold

Figure 3. Time-of-Flight LGA

Figure 4. MEMS LGA

Figure 5. FCCSP LGA

### 1.1 Package configuration and dimensions

Some typical LGA sizes, example from 2x2 to 3.5x3 mm, with a pitch of 0.35 mm and 0.65 mm, as shown in the table below.

| Table 1. LGA page | kages typical | dimensions |

|-------------------|---------------|------------|

|-------------------|---------------|------------|

| LGABody size<br>(mm) | Package<br>family | IO's | Pitch<br>(mm) | Max<br>thickness<br>(mm) | Substrate land<br>pad size (mm x<br>mm) | Land pad<br>design<br>(SMD,<br>NSMD,<br>SSMD) | E-pad<br>size<br>(mm) | Substrate<br>finishing |

|----------------------|-------------------|------|---------------|--------------------------|-----------------------------------------|-----------------------------------------------|-----------------------|------------------------|

| 2 x 2                | WF                | 14   | 0.35          | 0.70                     | 0.275 x0.200                            | SSMD                                          | None                  | NiAu                   |

| 2 x 2                | WF                | 12   | 0.50          | 0.70                     | 0.275 x0.250                            | SSMD                                          | None                  | NiAu                   |

| 2.3 x 2.3            | WF                | 16   | 0.40          | 0.70                     | 0.300 x0.200                            | SSMD                                          | None                  | NiAu                   |

| 2 x 2                | VF                | 14   | 0.35          | 0.96                     | 0.275 x0.200                            | SSMD                                          | None                  | NiAu                   |

| 2 x 2                | VF                | 10   | 0.40          | 1.00                     | 0.300 x0.200                            | SSMD                                          | None                  | NiAu                   |

| 2 x 2                | VF                | 12   | 0.50          | 1.00                     | 0.275 x0.250                            | SSMD                                          | None                  | NiAu                   |

| 2.5 x 2.5            | VF                | 14   | 0.50          | 0.86                     | 0.300 x0.250                            | SSMD                                          | None                  | NiAu                   |

| 3 x 2.5              | VF                | 14   | 0.50          | 0.86                     | 0.450 x0.250                            | SSMD                                          | None                  | NiAu                   |

AN5886 - Rev 2 page 2/23

| LGABody size<br>(mm) | Package<br>family | lO's | Pitch<br>(mm) | Max<br>thickness<br>(mm) | Substrate land<br>pad size (mm x<br>mm)     | Land pad<br>design<br>(SMD,<br>NSMD,<br>SSMD) | E-pad<br>size<br>(mm) | Substrate<br>finishing |

|----------------------|-------------------|------|---------------|--------------------------|---------------------------------------------|-----------------------------------------------|-----------------------|------------------------|

| 3 x 3                | VF                | 16   | 0.50          | 1.00                     | 0.350 x0.250                                | SSMD                                          | None                  | NiAu                   |

| 3.5 x 3              | TF                | 24   | 0.43          | 1.03                     | 0.350 x0.230                                | SSMD                                          | None                  | NiAu                   |

| 4 x 4                | L                 | 16   | 0.65          | 1.10                     | 0.400 x0.300                                | SSMD                                          | None                  | NiAu                   |

| 5 x 5                | VF                | 45   | 0.50          | 0.70                     | 0.350 X0.350                                | SMD                                           | None                  | NiAu                   |

| 8 x 8                | VF                | 56   | 0.45          | 0.94                     | 0.400 x0.200                                | SSMD                                          | 4x 4                  | NiAu                   |

| 7.3 x 11             | F                 | 86   | 0.90          | 1.43                     | 0.35 x 0.30,<br>0.35 x 0.35,<br>0.90 x 0.90 | SMD                                           | 24 small pads         | NiAu                   |

### 1.2 Benefit of LGA

- 1. LGA devices can be used for either leaded or lead-free assemblies depending on the SMT assembly solder paste used.

- 2. Eliminates the risk of missing or damaged spheres due to shipping or handling.

- 3. LGA devices have a lower mounted height than BGA. This can permit small form-factor applications.

- 4. LGA is more robust than BGA in case of mechanical drop.

- 5. LGA can use the same recommended board assembly process as a BGA.

### 1.3 LGA packages pads design types

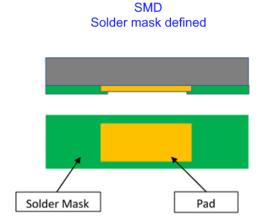

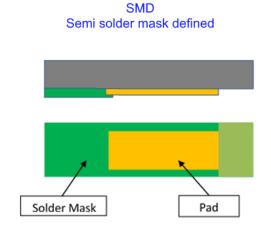

There are typically two types of pad designs for the LGA package as shown below in Figure 6 and Figure 7. The SMD pads have a solder mask opening smaller than the Cu pad while a SSMD has a solder mask covering only the three sides of the Cu pad. The SSMD pad mostly is on the perimeter of the package and this design helps to avoid solder voids during reflow.

Figure 6. Example of package with SMD pad

Figure 7. Example of package with SSMD pad

AN5886 - Rev 2 page 3/23

## 2 Board design

PCB footprint sizes and shapes and stencil designs are critical to surface mount assembly yields and subsequent electrical and mechanical performance of the mounted package. The package design can be obtained from the STMicroelectronics package outline assembly drawing as illustrated in Figure 8.

TOP VIEW SIDE VIEW BOTTOM VIEW PIN A1 CORNER \/ bbb C 5.550 PIN A1 CORNER 0.525 Μ 2.300 47 48 + + 68 + 46 H 0.600 67 2 6.018 ref 45 50 66 3 0.525 65 4 44 51 Top surface sputter: 3~6 μm 43 + 52 64 5 . + 63 54 55 56 57 58 50 61 62 63 6 78 1⊞ 40 39 Ω 5 38 - #38 - #37 - 36 - 35 75 74 +s9 6.983 ref (x54) 0.35x0.30 11 +<sub>76</sub> 73 70 12 (x9) 0.60x0.60 13 Ġ 34 33 <del>7</del><sup>7</sup> <del>7</del><sup>3</sup> 71 15 16 0.525 31 (x4) 0.35x0.35 Side wall sputter: 1~3 µm -BеĒ 0.525 E1 -A-△ aaa (4x) 0.150 um ref. DETAIL A'

Figure 8. Example of LGA 77-lead, 10 x 6.5 mm package drawing

Note: For LGA packages in SMT the stencil opening is 1:1

AN5886 - Rev 2 page 4/23

The package outline assembly drawing can include a small triangle that may or may not be visible on the chip. This is used for manufacturing and is not relevant for assembly of the device.

Figure 9. Example of triangle in POA drawing

AN5886 - Rev 2 page 5/23

### 2.1 Land pattern design

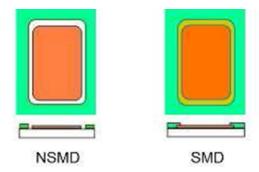

It is recommended to use a non solder mask defined (NSMD) pads, see Figure 10, with opening slightly larger than the land geometry, as copper etching has better dimensional control than solder masking process, because it allow solder to adhere to the sides of the Cu land for better reliability.

Figure 10. Comparison of NSMD and SMD leads

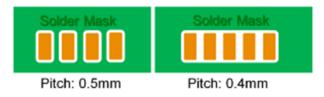

The solder mask opening should be minimum 0.050 mm, for the registration tolerance of the solder mask. For very fine pitch of 0.4 mm and below, solder mask defined is recommended and openings as "trench" should be considered asthere is not enough space for solder mask web in between pads, see Figure 11, Figure 12 and Figure 13.

Figure 11. Solder mask opening for perimeter lands with pitch 0.5 mm and 0.4 mm

In general, 1 to 1 ratio between the package pad and the PCB signal pad is used.

AN5886 - Rev 2 page 6/23

Figure 13. Example of joint with SMD pad

Top View of PCB

X-sect View

LGA

LGA

LGA

LGA

LGA

LGA

PCB

Solder mask

View of PCB

X-sect View

A-sect View

PCB

### 2.2 PCB pads design: NSMD vs SMD

Figure 12. Example of joint with NSMD pad

|   | -    | Pros                                                                                                                                                                   | Cons                                                                                                   |

|---|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| ı | NSMD | Solder "wets" to the side of the copper pad and gives a better solder joint reliability.                                                                               | Smaller pads have poorer adhesion strength, pads tend to peel off during multiple reworks and reflows. |

|   | SMD  | Copper pads are stronger as the mask is covering the pads and only the soldering pad is exposed. This improves the adhesion strength between the pad and the laminate. | Less space is required between pads for routing.                                                       |

### 2.3 Board finishing

Common board finishing is organic solderability preservative (OSP), electroless nickel immersion gold (ENIG) with good flatness and acceptable land pad surface. HASL is not preferred as the poor flatness gives rise to solder paste printing issue. Immersion Ag is another lead free alternative in terms of flatness but requires special handling

AN5886 - Rev 2 page 7/23

### 3 Board assembly

Precise process development and experimentation are needed to optimize specific applications or performance.

### 3.1 Assembly process flow

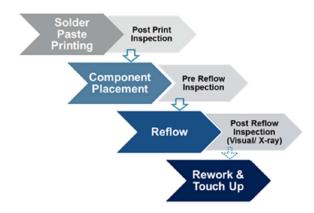

Figure 14. Typical assembly process flow

### 3.2 Stencil design for perimeter pads

It is crucial to use a good quality stencil to achieve a robust solder paste printing process.

Nickel electroform or laser cut electro-polished stainless steel (or nickel) is recommended.

Taper aperture walls 5° tapering are recommended to facilitate paste release. Suggested stencil thickness (T) is 100 µm for 0.4 mm pitch and stencil aperture should follow the rules for aspect and area ratio.

For the best solder paste transfer, an area ratio of

> 0.66 (laser cut) and > 0.55 for electro form or an aspect ratio > 1.5 is required

Aspect Ratio =

$$D_{NA}/T$$

or  $(D/T, 2R/T) \ge 1.5$

{NARROWEST APERTURE DIMENSION / STENCIL THICKNESS}

Area Ratio =  $A_P/A_{VV}$  or  $(D/4T, R/2T) \ge 0.66$

{PAD AREA / WALL AREA}

One of the most important parts of SMT is to have a robust and consistent solder paste printing process. To achieve this requires process monitoring of paste volume and stencil condition.

Overprinting may cause solder bridging and inconsistent solder paste volume results in opens after reflowing due to poor coplanarity. Marginal pass solder paste volume causes reliability issue in the field as the solder paste is the only connection between LGA pad and PCB pad.

The stencil aperture is typically designed to match the PCB perimeter pad size (i.e., 1:1) depending on area ratio for proper disposition of solder paste. As for smaller pitch < 0.40 mm for a circle pad, A square aperture is recommended for round pads and a pitch smaller than 0.40 mm. This produces a slightly larger volume of solder paste for easy release

AN5886 - Rev 2 page 8/23

#### 3.3 Solder paste printing

Typical lead-free solder paste is SAC alloy. Solder paste type 4 (or type 3) is recommended to optimize the deposition efficiency as per below table.

Table 2. Solder paste powder size

| Pa                | Ту           | pe    |   |

|-------------------|--------------|-------|---|

| Solder paste type | 3            | 4     |   |

| Powder size (µm)  | 45-25        | 36-25 |   |

| Pitch (mm)        | 0.5 to 1.0   | √     | √ |

|                   | 0.35 and 0.4 | -     | √ |

There are two different types of soldering flux for solder paste. Water soluble and no clean flux. No clean solder paste with very little residue after soldering is recommended. The left-over residue is not corrosive and des not damages the PCB.

Precaution must be taken for water soluble flux as it tends to corrode after a prolonged time if it is not well cleaned (esp. very small stand-off).

### 3.4 Solder paste inspection

Inspection of the printed solder paste is recommended before placing parts. A 2D (X, Y) inspection or an automated 3D (X, Y, Z) volume inspection or a statistical measurement process control plan is part of the assembly process to assure a repeatable solder deposit and a high yield assembly quality.

### 3.5 Component placement

Precise and accurate component placement is required (tolerance of  $\pm 50~\mu m$  and below) to have uniform solder coverage, especially with the high density I/O configurations.

Misalignment can easily cause solder bridging and other problems like skewing especially for 0.40 mm pitch packages.

Pick and place equipment is recommended to have placement force control and force being minimized where possible:

The guideline of the mounting before pre-reflow:

Figure 15. Placement and self-alignment during reflow

#### 3.6 Convection reflow

There are no special requirements necessary when reflowing LGA components. As with all SMT components, it is important that profiles be checked on all new board designs. In addition, if there are multiple packages on the board, the profile must be checked at different locations on the board. The solder paste manufacturer's temperature profile is used to optimize flux activity and minimize voiding.

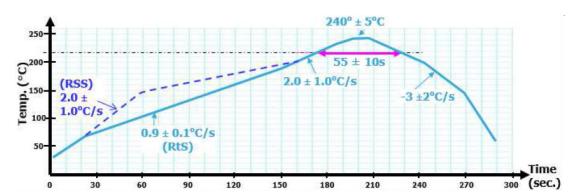

The recommended lead-free reflow profile as illustrated on Figure 16

AN5886 - Rev 2 page 9/23

Figure 16. Typical Lead-free reflow profile for LGA

- 1. Ramp-to-spike profile is recommended for Pb-free assembly with better wetting and less thermal exposure than traditional ram-soak-spite profile.

- 2. Thermocouple is attached through bottom side of board undermeath the center of LGA.

- 3. Perfom optimization for actual board/panel and refer to solder paste supplier's recommendation

Table 3. Typical Lead-free reflow profile for LGA

| Profile                            | Ramp-to-spike (straight line profile) | Ramp soak spike                 |  |

|------------------------------------|---------------------------------------|---------------------------------|--|

| Temperature gradient (in preheat)  | (T = 70-150 °C): 0.9 ± 0.1 °C/s       | (T = 70-150 °C): 2.0 ± 0.5 °C/s |  |

| Soak/Dwell <sup>(1)</sup>          | N/A                                   | Soak                            |  |

|                                    | or (T = 150-200 °C): 60 ± 20 s        | (T = 150-200 °C): 70 ± 30 s     |  |

| Temperature gradient (in pre-flow) | (T = 200-225 °C): 2.0 ± 1.0 °C/s      |                                 |  |

| Peak temperature (in reflow)       | 240 ± 5 °C                            |                                 |  |

| Time above 220 °C                  | 55 ± 10 s                             |                                 |  |

| Temparuture gradient (in cooling)  | -3 ± 2 °C/s                           |                                 |  |

| Time from 50 to 220 °C             | 150 to 230 s                          |                                 |  |

<sup>1.</sup> Refer to solder paste recommention

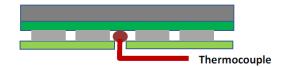

For an example of thermocouple insertion on profile board for larger LGA, see Figure 17. For a smaller package, like 2x2, the thermocouple can be attached to the side of the package.

Figure 17. Insertion of thermocouple for large LGA

### 3.7 Double-sided process

The double-sided process follows the same procedure as the single-sided process: mount and reflow the packages on one side and simply turnover the board and repeat the process.

AN5886 - Rev 2 page 10/23

# 4 Inspection, defects and analysis

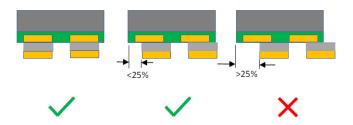

After surface mount assembly, X-ray should be used for sample monitoring of the solder attachment process; this identifies defects such as solder bridging, insufficient solder and voids.

Currently there is no specific standard for solder voids after reflow. As a general guideline for solder joints it is recommended to use a 25% maximum voids criteria.

Figure 18. X-Ray inspection, acceptable joints

Table 4. Typical defects with causes and remedy

| Type of defect | Causes                                                                                                       | Remedy                                                                                        |

|----------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

|                | <ul> <li>Too much solder paste volume.</li> <li>Stencil not properly clean after printing.</li> </ul>        | <ul> <li>Optimize the aperture opening.</li> <li>Optimize the cleaning parameters.</li> </ul> |

| Void >25%      | <ul> <li>Reflow profile not optimized.</li> <li>Too much solvent in flux content of solder paste.</li> </ul> | Increase the soaking time of reflow profile to reduce the solvent before reflow.              |

AN5886 - Rev 2 page 11/23

# 5 Cleaning after reflow

No-clean solder paste generally doesn't require cleaning. However, depending on the application, soldering flux activity, cleaning after solder reflow may be required, such as by ultrasonic agitation or spray cleaning, which is commonly used in PCB process.

Be cautious when using ultrasonic cleaning as it could weaken the soldering joint.

AN5886 - Rev 2 page 12/23

# 6 Board level reliability

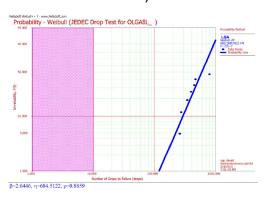

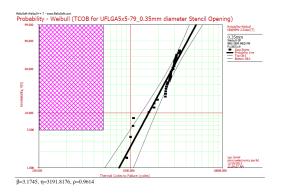

STMicroelectronics has evaluated several LGA for board mounting and solder joints reliability, especially versus thermal cycling with good performance.

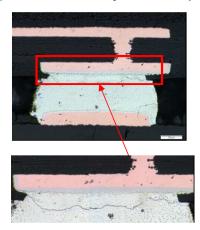

See examples in Figure 19 to Figure 22 for OLGA2.7x2.3-8L\_0.85 mm pitch and UFLGA 5x5-79 with 0.5 mm pitch:

Figure 19. Drop test for OLGA 2.7x2.3-8L (JESD22-B111)

Figure 21. Thermal cycling for UFLGA5x5-79 (JESD22-A104D)

Figure 20. Failure analysis after drop test

Figure 22. Failure analysis after thermal cycling

AN5886 - Rev 2 page 13/23

### 7 Rework guidelines

#### 7.1 Rework of LGA

Reworking of LGA is carried out due to:

- 1. Damage

- 2. Misalignment after reflowing

- 3. Solder bridging

- 4. Malfunction of the package

### 7.2 Package removal and site dressing

- 1. Bake the PCB (e.g., 125C for 4 hrs) to remove the moisture (if necessary)

- 2. Package can be removed manually or semi auto method.

- 3. For manual method, apply heat on the LG package with a hot air gun and cover neighborhood component with heat shielding material to prevent damage.

- 4. Use a vacuum pick up nozzle or a tweezer to remove the device from the board after the solder has melted.

- 5. For semi-automated method, PCB is clamped on a rework equipment conveyor. Heat is applied from the equipment rework nozzle to melt the package solder.

- 6. After the solder has melted, a vacuum pickup nozzle is lowered to remove the package automatically.

- 7. Remove solder residue from the PCB pad with solder wick and solder iron before replacing with a new LGA.

- 8. Clean the solder pad with IPA to remove flux residue after de-soldering process.

### 7.3 Manual method for placing new LGA

- 1. Use a mini stencil to apply solder paste onto the PCB LGA pad.

- 2. Mini stencil must have the same thickness, aperture opening and pattern as the normal stencil.

- 3. Inspect the printed pad to ensure even and sufficient solder paste before component placement.

- 4. If the neighboring parts is too close to the LGA components and mini stencil method is not applicable, then solder paste can be applied to the package LGA pad instead.

- 5. The solder paste is applied to the LGA pad using rework jig and mini stencil.

- 6. The LGA package is then subjected to reflow to form the solder joint.

- 7. Apply a thin layer of no clean flux on the PCB LGA pad.

- 8. Mount LGA package on PCB by "Pick & Place" machine.

- 9. Use hot air nozzle to melt the solder to form the joint between the package and PCB pad.

- 10. Proceed X-ray to inspect solder joint quality.

#### 7.4 Semi-automated method

- 1. This is a better method for reworking LGA.

- 2. There are many rework equipments in the markets which are capable to perform the rework. See example in Figure 19.

- 3. Execute Section 7.3: Manual method for placing new LGA step 1 to 3

- 4. Then the PCB is clamped on the rework equipment conveyor/table.

- 5. New LGA is picked up by a nozzle and the LGA soldering pad is aligned to the PCB pad.

- 6. Heat is applied to the PCB until the solder melting point is reached. The LGA is then slowly lowered to perform the soldering.

- If the neighboring parts is too close to the LGA components and mini stencil method is not applicable, solder

paste can be applied to the LGA pad instead. Repeat Section 7.3: Manual method for placing new LGA step 5

to 7.

- 8. LGA package with solder is then picked up by a nozzle and aligned to soldering pad on the PCB

AN5886 - Rev 2 page 14/23

- Use hot air nozzle with controlled temperature to melt the solder. Bottom board side heating (150 °C) is often

needed to avoid warpage and overheating of component.

Heat is applied to the PCB until the solder melting point is reached. LGA is then slowly lowered to perform the

soldering.

- 10. The quality of the solder joint is then inspected by X-ray machine.

AN5886 - Rev 2 page 15/23

### 8 LGA handling

### 8.1 Handling ESD package

Integrated circuits and components are ESD sensitive, so proper precautions are required for handling and mounting processes as electrostatic discharge could cause damage and failure to the devices. Ensure to have proper ESD control during the handling and mounting process using industry standard requirements such as JEDS625-B guideline, for proper handling and ESD controls.

#### 8.2 Handling moisture sensitive package

Most LGA packages are classified level 3 as per JEDEC J-STD 020E standard. The humidity is easily trapped by LGA packages in laminate (substrate) mold compound glue and underfill materials inducing vapor pressure during reflow. The moisture pressure inside non-hermetic packages may cause internal materials /delamination or crack or bond damage.

In the most severe case, the stress can extend to external package cracks, commonly known as "popcorn" that bulge and then crack. Humidity inside the package can induce some package deformations during the reflow which contribute to stress on the solder joints and could lead to quality and reliabilities risk.

#### Recommendation:

Implement tight control to minimize the moisture absorption level after opening the dry-pack, observe and follow the moisture sensitively guidelines on package dry-pack label and in JEDEC standard J-STD-033.

E.g., use nitrogen or dry/desiccator cabinets to store packages before boards soldering.

Parts can be re-baked after few days in open air in order not to exceed the moisture sensitivity guidelines.

Baking is required before assembly if the following condition occurs:-

- 1. Package is exposed to floor life more than specific requirements

- 2. Humidity indicator card show more than the specific percent level

- 3. Packages are not stored according to J-STD-033B standard

AN5886 - Rev 2 page 16/23

# 9 Reference

Table 5. Reference list

| Reference         | Description                                                                                       |

|-------------------|---------------------------------------------------------------------------------------------------|

| JEDEC J-STD 020E  | "Moisture/Reflow sensitivity classification for non-hermetic surface mount devices", Jan 2015     |

| JEDEC J-STD-033D  | "Handling, packing, shippingand use of moisture/reflow sensitive surface mount devices", Apr 2018 |

| JEDEC JESD 625-B  | "Requirementsf or handling electrostatic discharge sensitive (ESDS)- devices", Dec 2011           |

| IPC7093           | "Design and assembly process implementation for bottom termination components", March 2011        |

| IPC-A-610J        | "Requirements for soldered electrical and electronic assemblies", May2016                         |

| IPC7351B          | "Generic requirements for surface mount design and land pattern standard", June 2010              |

| JEDEC JESD22A104F | "JEDEC standard thermal cycling", Nov 2020                                                        |

| JEDEC JESD 22B111 | "JEDEC standard board level drop test", July 2003                                                 |

| IPC-7525          | "Stencil design guideline", February 2007                                                         |

AN5886 - Rev 2 page 17/23

# 10 Acronym

Table 6. Acronym list

| symbol | Description                          |

|--------|--------------------------------------|

| BGA    | Ball grid array                      |

| Cu     | Copper                               |

| ESD    | Electrostatic discharge              |

| I/O    | Input and Output                     |

| LGA    | Land grid array                      |

| MSL    | Moisture sensitive level             |

| NSMD   | Non solder mask define               |

| PCB    | Printed circuit board                |

| PCBA   | Printed circuit board assembly       |

| SMD    | Solder mask define                   |

| TFLGA  | Thin profile fine pitch LGA          |

| VFLGA  | Verythin profile fine pitch LGA      |

| WFLGA  | Veryvery thin profile fine pitch LGA |

AN5886 - Rev 2 page 18/23

# **Revision history**

Table 7. Document revision history

| Date        | Version | Changes                                                                    |

|-------------|---------|----------------------------------------------------------------------------|

| 01-Feb-2023 | 1       | Initial release.                                                           |

| 09-May-2024 | 2       | Updated:  Table 1. LGA packages typical dimensions Section 2: Board design |

AN5886 - Rev 2 page 19/23

# **Contents**

| 1   | Pac  | kages                                | 2  |

|-----|------|--------------------------------------|----|

|     | 1.1  | Package configuration and dimensions | 2  |

|     | 1.2  | Benefit of LGA                       | 3  |

|     | 1.3  | LGA packages pads design types       | 3  |

| 2   | Boa  | rd design                            | 4  |

|     | 2.1  | Land pattern design                  | 6  |

|     | 2.2  | PCB pads design: NSMD vs SMD         | 7  |

|     | 2.3  | Board finishing                      | 7  |

| 3   | Boa  | rd assembly                          | 8  |

|     | 3.1  | Assembly process flow                | 8  |

|     | 3.2  | Stencil design for perimeter pads    | 8  |

|     | 3.3  | Solder paste printing                | 9  |

|     | 3.4  | Solder paste inspection              | 9  |

|     | 3.5  | Component placement                  | 9  |

|     | 3.6  | Convection reflow                    | 9  |

|     | 3.7  | Double-sided process                 | 10 |

| 4   | Insp | ection, defects and analysis         | 11 |

| 5   | Clea | aning after reflow                   | 12 |

| 6   | Boa  | rd level reliability                 | 13 |

| 7   | Rew  | ork guidelines                       | 14 |

|     | 7.1  | Rework of LGA                        | 14 |

|     | 7.2  | Package removal and site dressing    | 14 |

|     | 7.3  | Manual method for placing new LGA    | 14 |

|     | 7.4  | Semi-automated method                | 14 |

| 8   | LGA  | handling                             | 16 |

|     | 8.1  | Handling ESD package                 | 16 |

|     | 8.2  | Handling moisture sensitive package  | 16 |

| 9   | Refe | erence                               |    |

| 10  |      | onym                                 |    |

| Rev |      | history                              |    |

# **List of tables**

| Table 1. | LGA packages typical dimensions          | 2  |

|----------|------------------------------------------|----|

| Table 2. | Solder paste powder size                 | 9  |

| Table 3. | Typical Lead-free reflow profile for LGA | 10 |

| Table 4. | Typical defects with causes and remedy   | 11 |

| Table 5. | Reference list                           | 17 |

| Table 6. | Acronym list                             | 18 |

| Table 7. | Document revision history                | 19 |

AN5886 - Rev 2

# **List of figures**

| Figure 1.  | LGA package type                                                     | . 1 |

|------------|----------------------------------------------------------------------|-----|

| Figure 2.  | LGA with over mold                                                   | . 2 |

| Figure 3.  | Time-of-Flight LGA                                                   | . 2 |

| Figure 4.  | MEMS LGA                                                             | . 2 |

| Figure 5.  | FCCSP LGA                                                            | . 2 |

| Figure 6.  | Example of package with SMD pad                                      | . 3 |

| Figure 7.  | Example of package with SSMD pad                                     | . 3 |

| Figure 8.  | Example of LGA 77-lead, 10 x 6.5 mm package drawing                  | . 4 |

| Figure 9.  | Example of triangle in POA drawing                                   | . 5 |

| Figure 10. | Comparison of NSMD and SMD leads                                     | . 6 |

| Figure 11. | Solder mask opening for perimeter lands with pitch 0.5 mm and 0.4 mm | . 6 |

| Figure 12. | Example of joint with NSMD pad                                       | . 7 |

| Figure 13. | Example of joint with SMD pad                                        | . 7 |

| Figure 14. | Typical assembly process flow                                        | . 8 |

| Figure 15. | Placement and self-alignment during reflow                           | . 9 |

| Figure 16. | Typical Lead-free reflow profile for LGA                             | 10  |

| Figure 17. | Insertion of thermocouple for large LGA                              | 10  |

| Figure 18. | X-Ray inspection, acceptable joints                                  | 11  |

| Figure 19. | Drop test for OLGA 2.7x2.3-8L (JESD22-B111)                          | 13  |

| Figure 20. | Failure analysis after drop test                                     | 13  |

| Figure 21. | Thermal cycling for UFLGA5x5-79 (JESD22-A104D)                       | 13  |

| Figure 22. | Failure analysis after thermal cycling                               | 13  |

| Figure 23. | Example of rework station                                            | 15  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

AN5886 - Rev 2 page 23/23