### TVS devices for power line communication applications

#### Introduction

All communication applications are bound to comply with electro-magnetic compatibility (EMC) standards, whose requirements depend on the application environment.

This application note aims at showing the good usage of the transient voltage suppressor (TVS) devices to protect power line communication (PLC) circuits against electrical over-stress (EOS) and specifically against surge events as defined by IEC 61000-4-5 and EN50065-2-3 international standards.

Even though 4 kV test level is required as maximum withstand level by the previously mentioned application standards, for this application note, a PLC circuit has been tested against 6 kV surges. Customers often require this higher level for higher confidence or specific applications. Tests performed and results are presented, focusing in the end on an optimized PLC protection solution.

### 1 Application description

Power line communication can be used in various applications such as smart metering, home automation, street lighting, solar inverters and so on.

In all cases, the PLC circuit is coupled to a power line (AC or DC) with high probability of high-energy transients, potentially causing EOS events that could damage the application.

The application conditions described above create the need for specific protection devices to be included in the power line coupling circuit.

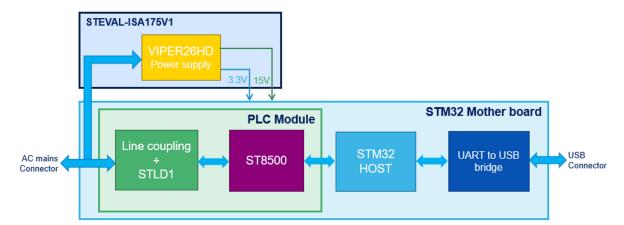

Tests on adequate protection devices have been performed using the ST demonstration kit EVALKITST8500-1. Built around the ST8500 power line networking system-on-chip, this demonstration kit embeds all the functions required for a "turn-key" power line communication network: the PLC node based on the ST8500, the AC power supply (based on the VIPER26HD chip), and the STM32 microcontroller, to either control the system as a standalone application or to connect the EVALKITST8500-1 to an external host.

For all EVALKITST8500-1 documentation, including application note, schematics, and PCB layout, please go to ST PLC products webpage or the EVALKITST8500-1 webpage.

Figure 1. EVALKITST8500-1 block diagram

AN5887 - Rev 2 page 2/23

## 2 Transient voltage suppressor devices

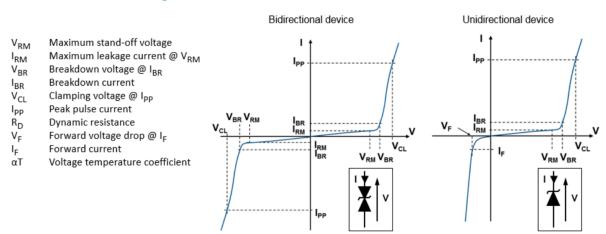

The working principle of a TVS is the following: once the voltage at the TVS node exceeds the breakdown voltage  $V_{BR}$ , the TVS clamps the voltage across it, reaching a clamping level  $V_{CL}$  that depends on the current flowing through the TVS.

Two kinds of TVS can be used: bidirectional or unidirectional.

#### **Bidirectional**

A bidirectional TVS clamps the voltage in the same way whatever the direction (V > 0 or V < 0).

The voltage is able to vary from  $-V_{BR}$  to  $+V_{BR}$  but will be clamped to  $-V_{CL}$  or  $V_{CL}$  if a surge tries to push the voltage out of boundaries.

#### Unidirectional

A unidirectional TVS clamps the voltage differently depending on the direction (V > 0 or V < 0).

For V < 0, it acts as a diode in forward conduction, with a clamping voltage below 1 V, generally around 0.7 V. For V > 0, the voltage is able to vary from 0 V to  $V_{BR}$  but will be clamped to  $V_{CL}$  if a surge tries to force it lower.

Figure 2. Bidirectional and unidirectional TVS behavior

AN5887 - Rev 2 page 3/23

### 3 Description of the EMC standards for surge tests

Surge waveforms and levels are defined in the IEC 61000-4-5 standard. The standard defines the surge waveforms and the test levels separately: the surge voltage and current waveforms have always the same shape and timings, while the voltage and current levels depend on the test and the application specifications.

### 3.1 Voltage and current waveforms

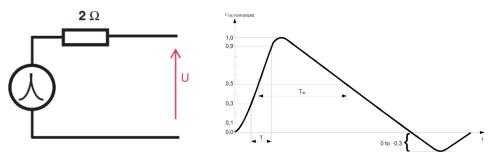

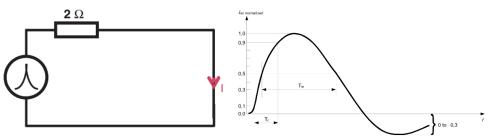

The surge generator is specified in terms of open circuit voltage and short circuit current to have the correct waveform. The voltage waveform has 1.2  $\mu$ s front time and 50  $\mu$ s duration and the current waveform has 8  $\mu$ s front time and 20  $\mu$ s duration.

#### The front time and duration for open-circuit voltage are defined to be:

- Front time: 1.67 times the 30%-90% rise time

- Duration: time interval between the 50% point of its rising edge and the 50% point of its falling edge

#### The front time and duration for short-circuit current are defined to be:

- Front time: 1.25 times the 10%-90% rise time

- Duration: 1.18 times the interval between the 50% point of its rising edge and the 50% point of its falling edge

Figure 3. IEC61000-4-5 voltage setup circuit and waveform (1.2/50 μs)

Figure 4. IEC61000-4-5 current setup circuit and waveform (8/20µs)

AN5887 - Rev 2 page 4/23

### 3.2 Power line communication EMC standards

In Europe, the requirements to be satisfied by PLC applications are stated in the EN50065 2-x documents, all referring to the IEC61000-4-5 standard for surge definition:

- EN50065-2-1: for the residential, commercial, and light industrial environment (that is, home automation and similar)

- EN50065-2-2: for industrial environments (that is, industrial command and control)

- EN50065-2-3: for use by electricity suppliers and distributors (that is, AMR/AMI)

The most stringent requirements are set by the EN50065-2-3 part and ask for  $\pm 4$  kV 1.2/50  $\mu$ s (8/20  $\mu$ s) withstanding in both differential and common-mode surge coupling.

However, to match the higher requirements set by some applications and customers, a ±6 kV level has been applied.

AN5887 - Rev 2 page 5/23

### 3.3 Surge test levels

Surge levels should be selected according to application environment.

Table 1 below provides the different voltage levels and environment description according to IEC61000-4-5:

Table 1. Voltage levels and environment description according to IEC61000-4-5

| Class | Environment                                                                                                                                                         | Voltage level   |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0     | Well protected environment, often in a special room                                                                                                                 | 25 V            |

| 1     | Partially, protected environment                                                                                                                                    | 500 V           |

| 2     | Electrical environment where the cables are well separated, even at short runs                                                                                      | 1 kV            |

| 3     | Electrical environment where power and signal cables run in parallel                                                                                                | 2 kV            |

| 4     | Electrical environment where the interconnections include outdoor cables along with the power cable, and cables are used for both electronics and electric circuits | 4 kV            |

| 5     | Electrical environment for electronic equipment connected to telecommunication cables and overhead power lines in a non-densely populated area                      | Same as class 4 |

Series resistance of the surge generator depends on the surge application mode:

- When the surge is applied in differential mode (that is, surge applied between lines), the series resistance is 2  $\Omega$

- When the surge is applied in common mode (that is, between a line and the ground), the series resistance is  $12 \Omega (2 \Omega + 10 \Omega)$ .

As the surge current impacts on the power rating of the protection devices, the Table 2 shows the maximum peak current values depending on voltage level and series resistance.

Table 2. Surge current versus source impedance and surge level

|          | Class<br>25 V | Class 1<br>500 V | Class 2<br>1 kV | Class 3<br>2 kV | Class 4<br>4 kV |

|----------|---------------|------------------|-----------------|-----------------|-----------------|

| R = 12 Ω | 2.1 A         | 42 A             | 84 A            | 167 A           | 334 A           |

| R = 2 Ω  | 12.5 A        | 250 A            | 500 A           | 1000 A          | 2000 A          |

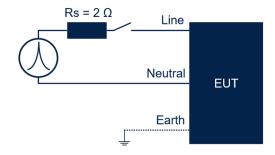

Figure 5 shows how the surge is applied to the EUT in differential configuration.

Figure 5. IEC61000-4-5 surge application to EUT

AN5887 - Rev 2 page 6/23

### 4 Surge tests

### 4.1 Test setup

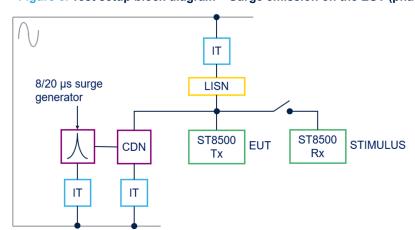

The setup described below and used for the tests reported in this document is in accordance with EN50065-2-3.

The first phase is the surge emission. There is the equipment under test (one EVALKITST8500-1 as EUT, transmitting PLC frames) connected to the 8/20 µs surge generator. The EUT is transmitting during the test because this is the most sensitive mode of operation for the EVALKITST8500-1 against surge.

The second phase is to test. The surge generator is cut off from EUT. Then a corresponding device is connected to the EUT (another EVALKITST8500-1 as stimulus, receiving PLC frames) to establish that after applying the surge test, communication between the two devices is still possible.

The boards are supplied via an isolation transformer (IT) plus two-line impedance stabilization networks (LISN). LISN reference is R and S ENV216 according to EN50065-1 specifications. Measurement ports of the LISNs are terminated in 50 to maintain the network characteristics.

The surge generator is connected in parallel with the EUT through the appropriate coupling / decoupling network (CDN).

Figure 6. Test setup block diagram - Surge emission on the EUT (phase 1)

Figure 7. Test setup block diagram - EUT test after a surge (phase 2)

AN5887 - Rev 2 page 7/23

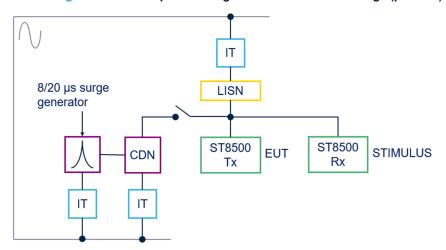

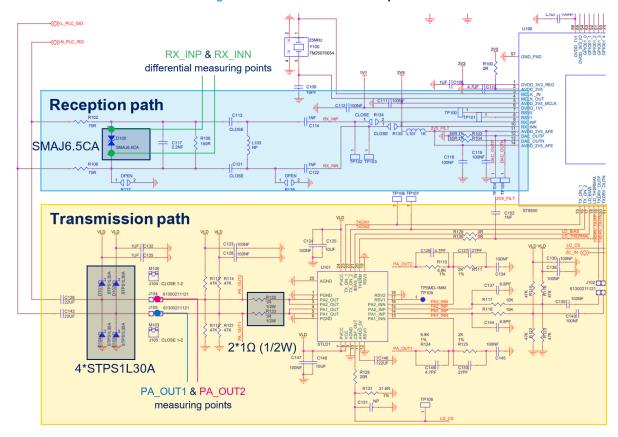

### 4.2 PLC circuit description

The PLC coupling circuit comprises three levels of protection, exploiting different protection devices:

#### Direct power line protection:

- Metal oxide varistor (MOV) is used as a first-line protection to clamp most of the surge energy. The part number for the EVALKITST8500-1 is B72214S0461K101 with the main characteristics listed below:

- Maximum clamping voltage V<sub>C,max</sub> = 1240 V

- Maximum working voltage V<sub>DC</sub> = 615 V

- Maximum surge current 1 time (8/20 μs) i<sub>max</sub> = 4500 A and 15 times (8/20 μs) i<sub>max</sub> = 3000 A

A single MOV is not sufficient to protect the entire circuit against the high power coming from a surge that is why we also need to add TVS diodes.

#### Power line coupling primary side protection:

• It is implemented through a bidirectional TVS diode put within the L-C series resonance. This position gives best protection while limiting the current flowing through the TVS.

#### Transformer secondary side protection:

Transformer secondary side: Two bidirectional TVS diodes are used against surges. They act specially against common mode surges

#### Secondary side protection at pin level:

Two pins of the PLC device and two pins of the STLD1 are directly connected to line coupling:

- PA\_OUT1 and PA\_OUT2: it is the line driver output of the PLC device forcing the transmission signal to the power line. This is the most sensitive point to be protected.

- Two 1 Ω resistors (half watt) are used to absorb the residual power coming from a surge at the input of the STLD1.

- Four Schottky diodes are used to clamp any residual disturbance to VLD or ground. The part number for the EVALKITST8500-1 is STPS1L30A.

- RX\_INN and RX\_INP: They are the differential high impedance receiving input of the PLC device. It is

protected by a bidirectional TVS diode put just before the dc-decoupling capacitors connected in series

with the pins.

The following tests and analysis focus on the TVS and Schottky diodes included in the PLC circuit.

Figure 8. PLC circuit schematic part 1

AN5887 - Rev 2 page 8/23

Figure 9. PLC circuit schematic part 2

Figure 8 and Figure 9 show the PLC circuit used for the tests, based on the EVALKITST8500-1 with all the protection components highlighted.

The measuring points are also shown related to the captures introduced Section 4.3 Test results.

AN5887 - Rev 2 page 9/23

#### 4.3 Test results

Tests results given in this chapter should be understood as follows:

Table 3. Surge test results definition

| Results | Details                                                                                             |

|---------|-----------------------------------------------------------------------------------------------------|

| OK      | The EUT is still operating and able to communicate after the surge test, as required by EN50065-2-x |

| КО      | The EUT is NOT operating and/or able to communicate after the surge test.                           |

The following table shows the TVS references mounted on the EVALKITST8500-1 according to their placement and the surge level applied with the results.

Table 4. Surge test report

| TVS          |                |               | Test r      | esults      |

|--------------|----------------|---------------|-------------|-------------|

| Primary side | Secondary side | Receiver side | ±4 kV level | ±6 kV level |

| SM6T15CA     | SM6T10CA       | SMAJ6.5CA     | OK          | OK          |

Based on the EN50065-2-3 requirement, it appears that the tested products can protect the PLM circuitry.

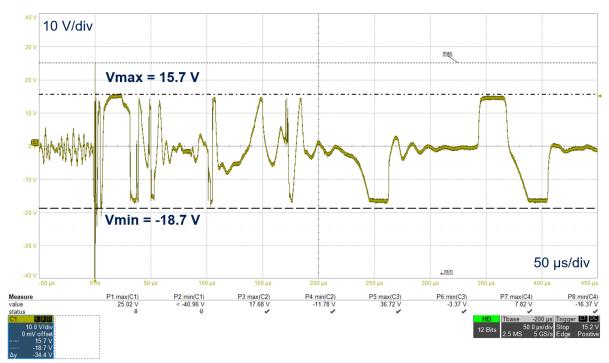

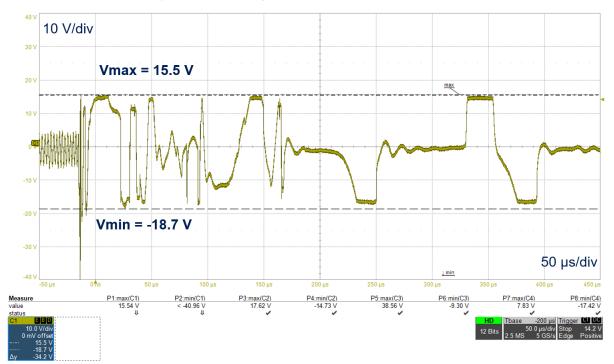

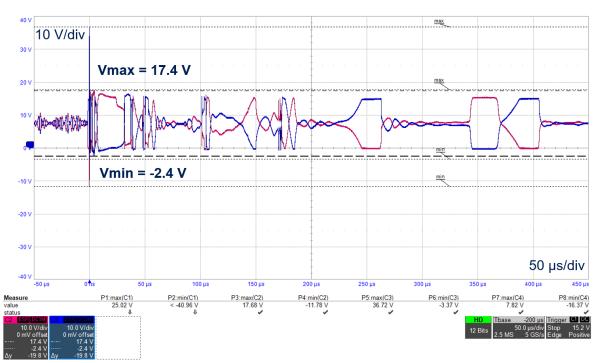

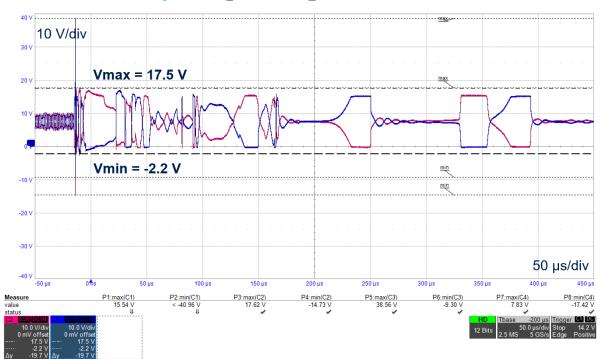

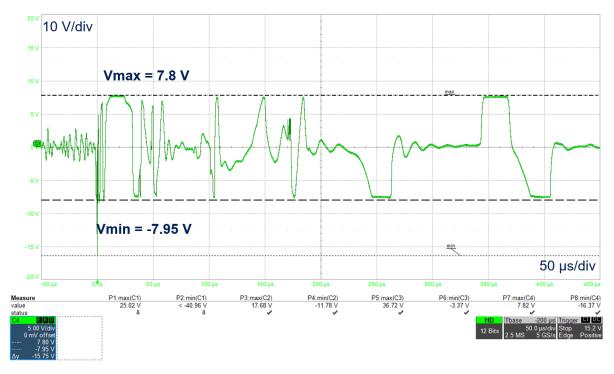

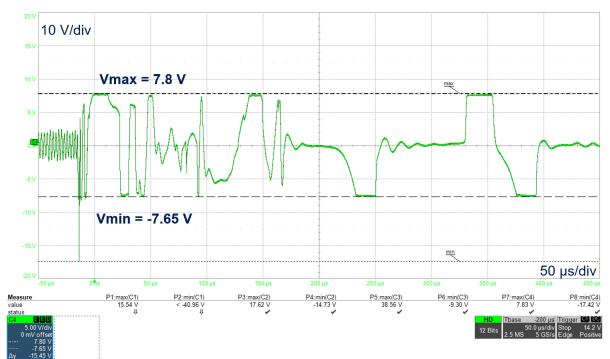

The following oscilloscope screenshots show a comparison of the residual disturbance level and duration of the two most sensitive points of the PLC coupling circuit, which are the transmitted signal output (PA\_OUT) and the received signal input (RX\_IN).

Regarding PA\_OUT, the most sensitive state is when the STLD1 is transmitting frames, its pins PA\_OUT1 and PA\_OUT2 are fully active through a low impedance output: if the surge occurs, the STLD1 tries to maintain its own output level, compensating the entering surge current.

The tests are done on an 230  $V_{AC}$  network at 50 Hz. Then the surge can be triggered at different phases of the AC signal. The most sensitive cases are at 90° and 270° because these are the higher levels of the AC signal. So, we should have 4 kV or 6 kV + 325  $V_{AC}$  on the surge coming to the DUT.

Therefore, for each measure, the STLD1 is transmitting, and the surge occurs at 90° of the AC mains.

The measurements prove that the TVS chosen gives a good protection to the PLC device.

AN5887 - Rev 2 page 10/23

Figure 10. Secondary side differential waveform at 4 kV

AN5887 - Rev 2 page 11/23

Figure 12. PA\_OUT1 and PA\_OUT2 waveform at 4 kV

AN5887 - Rev 2 page 12/23

Figure 14. RX\_INN and RX\_INP differential waveform at 4 kV

AN5887 - Rev 2 page 13/23

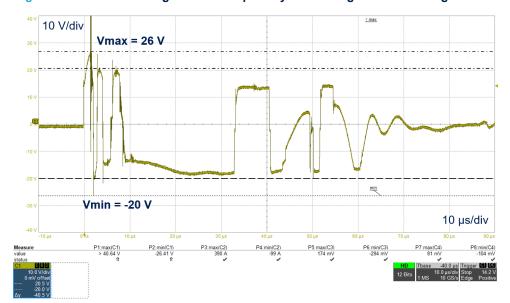

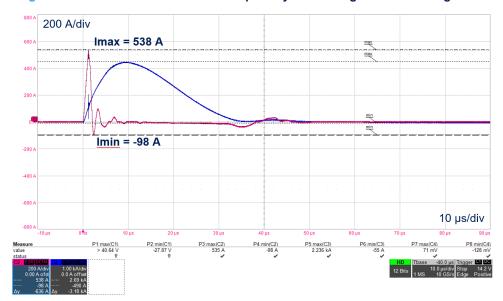

# 5 Primary side TVS validation through power rating

To guarantee reliability of the primary side protection TVS, an additional verification should be performed. Current, as well as voltage across the protection device during surge, should be measured and compared against the datasheet specifications.

In order to verify the exact TVS power management, measured voltage, and current across the TVS during differential surge is reported.

Figure 16. Measured current across the primary TVS during differential surge at 4 kV

AN5887 - Rev 2 page 14/23

Figure 18. Measured current across the primary TVS during differential surge 6 kV

Figure 16 and Figure 18 illustrates the current (pink) and the voltage (blue) at the input of the EVALKITST8500-1 inducted by the surge generator. Figure 17 and Figure 19 show the differential voltage measured at primary TVS terminals (SM6T15CA).

Indeed, most of the power is already absorbed by the MOV as first-stage protection.

The residual surge left after the MOV has a peak current  $I_{PEAK}$  around 390 A at 4 kV and 538 A at 6 kV and lasts about 2 µs. The measured peak voltage VPEAK is above 26 V at 4 kV and 28 V at 6 kV. Therefore, the peak power across the TVS during the surge can be estimated as PPEAK<sub>4kV</sub> = 26 V \* 390 A = 10.14 kW and PPEAK<sub>6kV</sub> = 28 V \* 538 A = 15 kW.

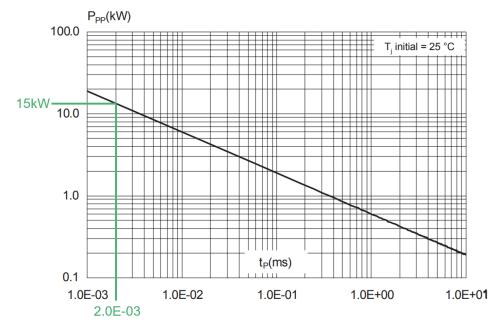

In the STM6T15CA, the peak pulse power versus exponential pulse duration is provided Figure 20. According to this parameter, a pulse lasting 2  $\mu$ s can be withstood up to 15 kW.

This power capability does not exceed the requirement. At the end, thanks to the results, we showed that it is safe to use SM6T15CA TVS at the primary side up to 6 kV surge level.

AN5887 - Rev 2 page 15/23

Figure 20. Maximum peak pulse power versus exponential pulse duration

AN5887 - Rev 2 page 16/23

## 6 Conclusion

A detailed description of surge test setup, measurements, and results has been provided to verify compliance with international EMC standards.

The analyzed coupling circuit topology proved to be well devised to protect the PLC device. The TVS part numbers were accurately tested.

Following these criteria to develop a PLC application ensures reliability of the solution at the 4 kV and 6 kV surge level

AN5887 - Rev 2 page 17/23

# **Appendix A References**

- 1. ST8500 datasheet on www.st.com

- 2. ST8500 application note AN5120 on www.st.com

- 3. ETSI TS 103 909

AN5887 - Rev 2 page 18/23

# **Revision history**

Table 5. Document revision history

| Date        | Revision | Changes           |

|-------------|----------|-------------------|

| 25-Nov-2022 | 1        | Initial release.  |

| 13-Dec-2022 | 2        | Updated Figure 8. |

AN5887 - Rev 2 page 19/23

# **Contents**

| 1   | App    | olication description                         | 2  |

|-----|--------|-----------------------------------------------|----|

| 2   | Trar   | nsient voltage suppressor devices             |    |

| 3   | Des    | cription of the EMC standards for surge tests | 4  |

|     | 3.1    | Voltage and current waveforms                 | 4  |

|     | 3.2    | Power line communication EMC standards        |    |

|     | 3.3    | Surge test levels                             | 6  |

| 4   | Sur    | ge tests                                      | 7  |

|     | 4.1    | Test setup                                    |    |

|     | 4.2    | PLC circuit description                       | 8  |

|     | 4.3    | Test results                                  |    |

| 5   | Prin   | nary side TVS validation through power rating | 14 |

| 6   | Con    | nclusion                                      | 17 |

| Ap  | pendi  | x A References                                | 18 |

| Rev | /ision | history                                       |    |

# **List of tables**

| Table 1. | Voltage levels and environment description according to IEC61000-4-5 | 6  |

|----------|----------------------------------------------------------------------|----|

| Table 2. | Surge current versus source impedance and surge level                | 6  |

| Table 3. | Surge test results definition                                        | 10 |

| Table 4. | Surge test report                                                    | 10 |

| Table 5. | Document revision history                                            | 19 |

AN5887 - Rev 2 page 21/23

# **List of figures**

| Figure 1.  | EVALKITS 18500-1 block diagram                                            | . 2 |

|------------|---------------------------------------------------------------------------|-----|

| Figure 2.  | Bidirectional and unidirectional TVS behavior                             |     |

| Figure 3.  | IEC61000-4-5 voltage setup circuit and waveform (1.2/50 μs)               | . 4 |

| Figure 4.  | IEC61000-4-5 current setup circuit and waveform (8/20μs)                  | . 4 |

| Figure 5.  | IEC61000-4-5 surge application to EUT                                     | . 6 |

| Figure 6.  | Test setup block diagram – Surge emission on the EUT (phase 1)            | . 7 |

| Figure 7.  | Test setup block diagram - EUT test after a surge (phase 2)               | . 7 |

| Figure 8.  | PLC circuit schematic part 1                                              | . 8 |

| Figure 9.  | PLC circuit schematic part 2                                              | . 9 |

| Figure 10. | Secondary side differential waveform at 4 kV                              | 11  |

| Figure 11. | Secondary side differential waveform at 6 kV                              |     |

| Figure 12. | PA_OUT1 and PA_OUT2 waveform at 4 kV                                      | 12  |

| Figure 13. | PA_OUT1 and PA_OUT2 waveform at 6 kV                                      | 12  |

| Figure 14. | RX_INN and RX_INP differential waveform at 4 kV                           | 13  |

| Figure 15. | RX_INN and RX_INP differential waveform at 6 kV                           | 13  |

| Figure 16. | Measured current across the primary TVS during differential surge at 4 kV | 14  |

| Figure 17. | Measured voltage across the primary TVS during differential surge at 4 kV | 14  |

| Figure 18. | Measured current across the primary TVS during differential surge 6 kV    | 15  |

| Figure 19. | Measured voltage across the primary TVS during differential surge at 6 kV |     |

| Figure 20. | Maximum peak pulse power versus exponential pulse duration                | 16  |

AN5887 - Rev 2 page 22/23

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics - All rights reserved

AN5887 - Rev 2 page 23/23