## Migrating between STM32U5 and STM32U3 MCUs

#### Introduction

The ability to easily replace one microcontroller type with another from the same product family is an important asset for designers of STM32 microcontroller applications.

Migrating an application to a different microcontroller is often needed when product requirements grow. This places extra demands on new features, memory size, or increases the number of I/Os. Cost reduction objectives may also be a reason to switch to smaller components, and shrink the PCB area.

This application note analyzes the steps required to migrate an existing application design from STM32U5 series microcontroller to STM32U3 series microcontroller, or the other way around.

The peripherals, performance, and power consumption are the main aspects to be considered for the migration.

Both STM32U3 and STM32U5 series belong to ultra-low-power family of microcontrollers based on the high-performance Arm<sup>®</sup> Cortex<sup>®</sup>- M33 32-bit RISC core, with Cortex<sup>®</sup> for Arm v8-M. The level of security is very high, as devices of both series embed advanced accelerators for cryptography and advanced features thanks to the Arm<sup>®</sup> TrustZone<sup>®</sup>.

While STM32U5 series offer more peripherals and features, better performance and bigger packages, STM32U3 series excel in power consumption thanks to the near-threshold voltage technology. With near-threshold technology, STM32U3 series reduce the active consumption down to 10 uA/MHz, resulting in far longer battery life for any application.

To benefit most from this application note, it is recommended that the reader is familiar with the STM32 microcontroller documentation available on www.st.com.

# 1 General information

This application note applies to STM32U3 series and STM32U5 series microcontrollers that are Arm<sup>®</sup> Cortex<sup>®</sup>-M33 core-based devices.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

#### **Reference documents**

- [1] Reference manual STM32U5 series Arm®-based 32-bit MCUs (RM0456)

- [2] Reference manual STM32U3 series Arm®-based 32-bit MCUs (RM0487)

- [3] STM32U5 series datasheets and errata sheets

- [4] STM32U3 series datasheets and errata sheets

- [5] Application note Getting started with STM32U5 series MCU hardware development (AN5373)

- [6] Application note Getting started with STM32U3 series MCU hardware development (AN6011)

- [7] Application note STM32 microcontroller system memory boot mode (AN2606)

AN6012 - Rev 2 page 2/33

## 2 Hardware migration guide

The STM32U3 and STM32U5 devices are pin-to-pin compatible and replaceable for the same package sizes. Three variants of packages are available:

- Legacy with LDO regulator only.

- SMPS with additional power pins for internal SMPS regulator.

- SMPS DSI with additional power pins for internal SMPS regulator and internal DSI transceiver.

Note that legacy SMPS and SMPS DSI packages are not pin-to-pin compatible. For example, a legacy package cannot be replaced by any SMPS package, or an SMPS package cannot be replaced with SMPS DSI package without a change of the application design.

Some functions might not be available on all pins due to unavailability of some peripherals. Refer to Section 3.1 and/or product datasheets for more information.

See Table 1 for an overview of the available packages for both series. If not stated otherwise, checked cells represent the availability of both legacy and SMPS packages.

The WLCSPx packages are not mentioned there, because they are dedicated to individual product lines. Refer to product datasheets for more information.

| Package                         | Package STM32U5 |               |               |                           | STM32U3       |

|---------------------------------|-----------------|---------------|---------------|---------------------------|---------------|

| (size in mm)                    | STM32U535/545   | STM32U575/585 | STM32U59x/5Ax | STM32U5Fx/5Gx             | STM32U375/385 |

| UFQFPN32 (5 x 5)                | -               | -             | -             | -                         | Legacy only   |

| LQFP48 (7 x 7)                  | X               | X             | -             | -                         | X             |

| UFQFPN48 (7 x 7)                | X               | X             | -             | -                         | X             |

| LQFP64 (10 x 10)                | X               | X             | X             | -                         | X             |

| UFBGA64 (5 x 5)                 | X               | -             | -             | -                         | X             |

| LQFP100 (14 x 14)               | X               | X             | X             | Legacy, SMPS,<br>SMPS DSI | X             |

| UFBGA100 (7 x 7)                | X               | -             | -             | -                         | X             |

| UFBGA132 (7 x 7)                | -               | X             | X             | -                         | -             |

| LQFP144 (20 x 20)               | -               | X             | X             | SMPS DSI only             | -             |

| UFBGA144 (10 x 10)              | -               | -             | -             | SMPS DSI only             | -             |

| UFBGA169 (7 x 7)                | -               | X             | -             | -                         | -             |

| TFBGA169 (7 x 7) <sup>(1)</sup> | -               | -             | X             | -                         | -             |

| TFBGA216 (13 x 13)              | -               | -             | SMPS DSI only | SMPS DSI only             | -             |

Table 1. Available packages in STM32U3 and STM32U5

For more details about available packages, refer to product datasheets and/or documents [5] and [6].

AN6012 - Rev 2 page 3/33

<sup>1.</sup> The difference between UFBGA and TFBGA is in package height and ball diameter.

# 3 Peripheral migration guide

## 3.1 Peripheral compatibility

Refer to Table 2 for summary of peripheral availability and compatibility on both series.

Table 2. Comparison of peripheral availability and compatibility for STM32U3 and STM32U5

| Peripherals         |                     | STM32U535/<br>545 | STM32U575/<br>585 | STM32U59x/<br>5Ax | STM32U5Fx/<br>5Gx | STM32U375/<br>385 | Register compatibility |  |

|---------------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------------|--|

| Core                |                     |                   |                   | Cortex-M33        | ,                 |                   | -                      |  |

| Maximum cor         | e frequency         |                   | 160               | MHz               |                   | 96 MHz            | -                      |  |

|                     | SRAM1               | 1:                | 92                | 70                | 38                | 192               | Dti-l                  |  |

|                     | SRAM2               |                   | 6                 | 64                |                   | 64                | Partial                |  |

|                     | SRAM3               | N/A               | 512               | 83                | 32                | N/A               | -                      |  |

| SRAM size (Kbytes)  | SRAM4               |                   | 1                 | 6                 |                   | N/A               | -                      |  |

| (.15)100)           | SRAM5               | N                 | /A                | 832               | -                 | N/A               | -                      |  |

|                     | SRAM6               |                   | N/A               | ,                 | 512               | N/A               | -                      |  |

|                     | BKPSRAM             |                   |                   | 2                 |                   | N/A               | -                      |  |

| Flash               | Size (bytes)        | 128K-512K         | 1M-2M             | 2M-4M             | 4M                | 512K-1M           | Dartial                |  |

| memory              | Туре                |                   |                   | Dual bank         |                   |                   | Partial                |  |

|                     | ICACHE              |                   | 8                 | 3                 | 2                 | 8                 | Yes                    |  |

| Cache size (Kbytes) | DCACHE1             |                   | 4                 | 1                 | 6                 | N/A               | -                      |  |

| ()                  | DCACHE2             | N                 | /A                | 1                 | 6                 | N/A               | -                      |  |

|                     | Number of instances |                   | 2                 |                   |                   | 1                 |                        |  |

| GTZC                | MPCWM resources     | 2                 | 5                 | 6                 |                   | N/A               | No                     |  |

|                     | MPCBB resources     | 3                 | 4                 | 5                 | 6                 | 2                 |                        |  |

|                     | LDO + SMPS          |                   | Y                 | es                |                   | Yes               | No                     |  |

| PWR                 | DSI power pins      | N                 | /A                | Y                 | es                | N/A               | -                      |  |

|                     | LPBAM               |                   | Y                 | es                |                   | N/A               | -                      |  |

|                     |                     |                   |                   |                   |                   | HSI16             |                        |  |

|                     |                     |                   |                   | HSI48             |                   |                   |                        |  |

| RCC Clocks          |                     |                   |                   |                   |                   | HSE               |                        |  |

|                     | Clocks              | HSI16, HS         | 148, HSE, MSI (   | 16 ranges), LSI,  | LSE, SHSI         | MSI (8 ranges)    | No                     |  |

|                     |                     |                   |                   |                   | LSI               |                   |                        |  |

|                     |                     |                   |                   |                   |                   | LSE               | _                      |  |

|                     | PLL                 |                   | Y                 | es                |                   | N/A               |                        |  |

| GPIO                | GPIO                |                   | Y                 | es                |                   | Yes               | Yes                    |  |

| 51 10               | LPGPIO              |                   | Y                 | es                |                   | N/A               | -                      |  |

AN6012 - Rev 2 page 4/33

| Peripherals     |                 | STM32U535/<br>545 | STM32U575/<br>585 | STM32U59x/<br>5Ax | STM32U5Fx/<br>5Gx | STM32U375/<br>385         | Register compatibility |

|-----------------|-----------------|-------------------|-------------------|-------------------|-------------------|---------------------------|------------------------|

| SYSCFG          |                 |                   | Y                 | es                |                   | Yes                       | Mostly yes             |

|                 | GPDMA           |                   | Yes (16 o         | Yes (16 channels) |                   |                           | Mostly yes             |

| DMA             | LPDMA           |                   | Voc (1 c          | hannels)          |                   | (11 channels)             | _                      |

|                 | DMA2D           | N/A               | 165 (4 0          | Yes               |                   | N/A                       | _                      |

| GFXMMU          | DIVIAZO         | IV/A              | N/A               | 163               | Yes               | N/A                       |                        |

| NVIC            |                 |                   |                   | es                | 165               | Yes                       | Mostly yes             |

| EXTI            |                 |                   |                   | es                |                   | Yes                       | Mostly yes             |

| CRC             |                 |                   |                   | es                |                   | Yes                       | Mostly yes             |

| CORDIC          |                 |                   |                   | es<br><br>es      |                   | N/A                       | iviosity yes           |

| FMAC            |                 |                   |                   | es<br>es          |                   | N/A                       |                        |

| FSMC            |                 | N/A               |                   | Yes               |                   | N/A                       | -                      |

| OCTOSPI         |                 | 1                 |                   | 2                 |                   | 1                         | Mostly yes             |

| OCTOSPIM        |                 | N/A               |                   | Yes               |                   | N/A                       | - IVIOSITY YES         |

| HSPI            |                 | N.A.              | /^                |                   | <br>1             | N/A                       |                        |

| SDMMC           |                 | 1                 |                   | 2                 | ı                 | 1                         | Yes                    |

| SDIVING         | ADC 12-bit      | l                 |                   | <br>1             |                   | 2                         | 162                    |

|                 | ADC 12-bit      |                   | <br>1             | I                 | 2                 |                           | No                     |

|                 | DAC 12-bit      |                   |                   | 2                 |                   | 0 2                       | Yes                    |

| Analog          | VREFBUF         |                   |                   | es                |                   | Yes                       | Yes                    |

|                 | COMP            | 1                 |                   |                   |                   | 2                         | Yes                    |

|                 | OPAMP           |                   |                   | 2                 |                   |                           |                        |

|                 |                 | 1                 |                   |                   |                   | 2                         | Yes                    |

| Digital filters | MDF             |                   |                   | es                |                   | N/A                       | -                      |

| DOM             | ADF             |                   |                   | es                |                   | Yes                       | Mostly yes             |

| DCMI            |                 |                   |                   | es                |                   | N/A                       | -                      |

| PSSI            |                 |                   |                   | es                |                   | N/A                       | -                      |

| LTDC            |                 |                   | /A                |                   | es                | N/A                       | -                      |

| DSI             |                 |                   | /A                |                   | es                | N/A                       | -                      |

| GPU2D           |                 | N                 | /A                | Y                 | es                | N/A                       | -                      |

| JPEG            |                 |                   | N/A               |                   | Yes               | N/A                       | -                      |

| TSC (number     |                 | Up to 20          |                   | 0 22              | Up to 24          | Up to 21                  | Mostly yes             |

|                 | ССВ             |                   |                   | /A                |                   | Yes                       |                        |

|                 | RNG             |                   | Yes               |                   | Yes<br>Yes        | Partial                   |                        |

|                 | AES             |                   | Yes               |                   |                   |                           | Yes                    |

| Cryptography    | SAES            |                   |                   | es                |                   | Yes                       | Mostly yes             |

|                 | HASH            |                   |                   | es                |                   | Yes                       | Mostly yes             |

|                 | OTFDEC          |                   | Yes               |                   |                   | N/A                       | -                      |

|                 | PKA             |                   |                   | es                |                   | Yes                       | Mostly yes             |

| _               | Advanced        |                   | 2 (1              | 6-bit)            |                   | 1 (16-bit)                | Mostly yes             |

| Timers          | General purpose |                   | 4 (32-bit)        | + 3 (16-bit)      |                   | 3 (32-bit) +3<br>(16-bit) | Mostly yes             |

AN6012 - Rev 2 page 5/33

| Peripherals   |               | STM32U535/<br>545                 | STM32U575/<br>585     | STM32U59x/<br>5Ax | STM32U5Fx/<br>5Gx | STM32U375/<br>385      | Register compatibility    |

|---------------|---------------|-----------------------------------|-----------------------|-------------------|-------------------|------------------------|---------------------------|

|               | Basic         |                                   | 2 (1                  | 6-bit)            |                   | 2 (16-bit)             | Mostly yes                |

|               | Low-power     |                                   | 4 (1                  | 6-bit)            |                   | 4 (16-bit)             | Yes                       |

| Timers        | Graphic       |                                   | N/A                   |                   | Yes               | N/A                    | -                         |

|               | SysTick       |                                   |                       | 2                 |                   | 2                      | Yes                       |

|               | Watchdog      |                                   |                       | IWDG + WWDG       |                   |                        | Yes                       |

| RTC           |               |                                   | Y                     | es                |                   | Yes                    | Mostly yes                |

| TAMP (numbe   | r of tampers) | Up to 7 (active) Up to 6 (active) |                       | Up to 5 (passive) | Partial           |                        |                           |

|               | I2C           |                                   | 4 6                   |                   |                   | 3                      | Yes                       |

|               | I3C           | N/A                               |                       |                   |                   | 2                      | -                         |

|               | USART         | 2                                 | 3                     | 4                 | 1                 | 2                      | Yes                       |

|               | UART          |                                   |                       | 2                 |                   | 2                      | Yes                       |

| Communicati   | LPUART        |                                   | 1 1                   |                   | 1                 | Mostly yes             |                           |

| on interfaces | SPI           |                                   | ;                     | 3                 |                   | 3                      | Yes                       |

|               | SAI           | 1                                 |                       | 2                 |                   | 1                      | Yes                       |

|               | FDCAN         |                                   | 1                     |                   |                   |                        | Yes                       |

|               | USB           | USB FS host/<br>device            | USB OTG FS USB OTG HS |                   | TG HS             | USB FS host/<br>device | With<br>STM32U535/<br>545 |

| UCPD          |               | N/A                               |                       | Yes               |                   | N/A                    | -                         |

In the following chapters, the system architecture and memory mapping of both series are compared. Then, for individual peripherals that are embedded in devices of both STM32U3 and STM32U5 devices but are not the same, the differences are listed and/or explained.

For complete information about other peripherals (that is peripherals available either on STM32U3, or STM32U5 devices), see document [1], [2], [3], and [4].

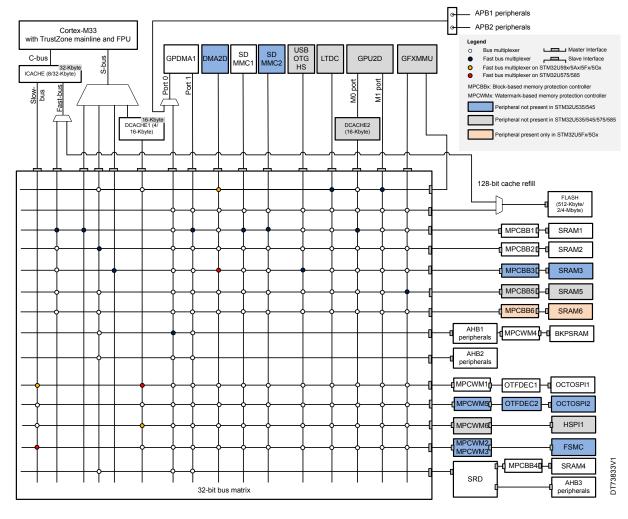

#### 3.2 System architecture

The system architectures of both series, STM32U3 and STM32U5, are very similar and differ mainly in the number of peripherals and memories available.

STM32U5 devices have (among other features) DCACHE on S-bus, OTFDEC protection for external OCTOSPI memories, SmartRun domain, or direct connection of flash memory and ICACHE for faster code execution. For more details, see Figure 1 and Figure 2.

AN6012 - Rev 2 page 6/33

- APB1 peripherals APB2 peripherals Cortex-M33 GPDMA1 SDMMC1 with TrustZone mainline and FPU Port 1 S-bus Legend Bus multiplexer ICACHE (8-Kbyte) Fast bus multiplexer Slave Interface MPCBBx: Block-based memory protection controller FLASH (2 × 512 Kbyte) MPCBB1 SRAM1 MPCBB2 SRAM2 AHB1 peripherals AHB2 peripherals

32-bit bus matrix

OCTOSPI1

Figure 1. System architecture of STM32U3

DT71401V1

AN6012 - Rev 2 page 7/33

Figure 2. System architecture of STM32U5

#### 3.3 Peripheral memory mapping

The main differences in memory mapping between STM32U3 and STM32U5 devices are caused by different sets of embedded peripherals, and additional SmartRun domain on STM32U5 devices (AHB3 and APB3 buses).

In Table 3 summarizes the memory mapping for all peripherals. Peripherals common for both series with different memory mappings are highlighted in bold.

Secure boundary addresses are not compared as the only difference from nonsecure addresses is their base address (0x4000 0000 for nonsecure and 0x5000 0000 for secure).

STM32U5 **STM32U3 Peripheral** Nonsecure boundary address Nonsecure boundary address Bus Bus LPDMA1 0x4602 5000 - 0x4602 5FFF AHB3 N/A N/A ADF1 AHB3 0x4602 4000 - 0x4602 4FFF AHB1 0x4003 4000 - 0x4003 4FFF GTZC2 AHB3 0x4602 3000 - 0x4602 3BFF N/A N/A **EXTI** AHB3 0x4602 2000 - 0x4602 23FF ΔHR1 0x4003 2000 - 0x4003 23FF DAC1 AHB3 0x4602 1800 - 0x4602 1BFF AHB2 0x4202 8400 - 0x4202 87FF ADC4 AHB3 0x4602 1000 - 0x4602 13FF N/A RCC AHB3 0x4602 0C00 - 0x4602 0FFF AHB1 0x4003 0C00 - 0x4003 0FFF

Table 3. Peripheral memory mapping

AN6012 - Rev 2 page 8/33

| Parinharal |      | STM32U5                    | STM32U3 |                            |  |

|------------|------|----------------------------|---------|----------------------------|--|

| Peripheral | Bus  | Nonsecure boundary address | Bus     | Nonsecure boundary address |  |

| PWR        | AHB3 | 0x4602 0800 - 0x4602 0BFF  | AHB1    | 0x4003 0800 - 0x4003 0BFF  |  |

| LPGPIO     | AHB3 | 0x4602 0000 - 0x4602 03FF  | N/A     | N/A                        |  |

| TAMP       | APB3 | 0x4600 7C00 - 0x4600 7FFF  | APB1    | 0x4000 7C00 - 0x4000 7FFF  |  |

| RTC        | APB3 | 0x4600 7800 - 0x4600 7BFF  | APB1    | 0x4000 7800 - 0x4000 7BFF  |  |

| VREFBUF    | APB3 | 0x4600 7400 - 0x4600 77FF  | APB1    | 0x4000 7400 - 0x4000 77FF  |  |

| COMP       | APB3 | 0x4600 5400 - 0x4600 57FF  | APB3    | 0x4004 5400 - 0x4004 57FF  |  |

| OPAMP      | APB3 | 0x4600 5000 - 0x4600 53FF  | APB1    | 0x4000 7000 - 0x4000 73FF  |  |

| LPTIM4     | APB3 | 0x4600 4C00 - 0x4600 4FFF  | APB3    | 0x4004 4C00 - 0x4004 4FFF  |  |

| LPTIM3     | APB3 | 0x4600 4800 - 0x4600 4BFF  | APB3    | 0x4004 4800 - 0x4004 4BFF  |  |

| LPTIM1     | APB3 | 0x4600 4400 - 0x4600 47FF  | APB3    | 0x4004 4400 - 0x4004 47FF  |  |

| 2C3        | APB3 | 0x4600 2800 - 0x4600 2BFF  | APB3    | 0x4004 2800 - 0x4004 2BFF  |  |

| LPUART1    | APB3 | 0x4600 2400 - 0x4600 27FF  | APB3    | 0x4004 2400 - 0x4004 27FF  |  |

| SPI3       | APB3 | 0x4600 2000 - 0x4600 23FF  | APB1    | 0x4000 2000 - 0x4000 23FF  |  |

| SYSCFG     | APB3 | 0x4600 0400 - 0x4600 07FF  | APB3    | 0x4004 0400 - 0x4004 07FF  |  |

| HSPI1      | AHB2 | 0x420D 3400 - 0x420D 37FF  | N/A     | N/A                        |  |

| OCTOSPI2   | AHB2 | 0x420D 2400 - 0x420D 27FF  | N/A     | N/A                        |  |

| OCTOSPI1   | AHB2 | 0x420D 1400 - 0x420D 17FF  | AHB2    | 0x420D 1400 - 0x420D 17FF  |  |

| FSMC       | AHB2 | 0x420D 0400 - 0x420D 07FF  | N/A     | N/A                        |  |

| DLYBOS2    | AHB2 | 0x420C F400 - 0x420C F7FF  | N/A     | N/A                        |  |

| DLYBOS1    | AHB2 | 0x420C F000 - 0x420C F3FF  | AHB2    | 0x420C F000 - 0x420C F3FF  |  |

| SDMMC2     | AHB2 | 0x420C 8C00 - 0x420C 8FFF  | N/A     | N/A                        |  |

| DLYBSD2    | AHB2 | 0x420C 8800 - 0x420C 8BFF  | N/A     | N/A                        |  |

| DLYBSD1    | AHB2 | 0x420C 8400 - 0x420C 87FF  | AHB2    | 0x420C 8400 - 0x420C 87FF  |  |

| SDMMC1     | AHB2 | 0x420C 8000 - 0x420C 83FF  | AHB2    | 0x420C 8000 - 0x420C 83FF  |  |

| ССВ        | N/A  | N/A                        | AHB2    | 0x420C 7C00 - 0x420C 7FFF  |  |

| OTFDEC2    | AHB2 | 0x420C 5400 - 0x420C 57FF  | N/A     | N/A                        |  |

| OTFDEC1    | AHB2 | 0x420C 5000 - 0x420C 53FF  | N/A     | N/A                        |  |

| OCTOSPIM   | AHB2 | 0x420C 4000 - 0x420C 43FF  | N/A     | N/A                        |  |

| PKA +RAM   | AHB2 | 0x420C 2000 - 0x420C 3FFF  | AHB2    | 0x420C 2000 - 0x420C 3FFF  |  |

| SAES       | AHB2 | 0x420C 0C00 - 0x420C 0FFF  | AHB2    | 0x420C 0C00 - 0x420C 0FFF  |  |

| RNG        | AHB2 | 0x420C 0800 - 0x420C 0BFF  | AHB2    | 0x420C 0800 - 0x420C 0BFF  |  |

| HASH       | AHB2 | 0x420C 0400 - 0x420C 07FF  | AHB2    | 0x420C 0400 - 0x420C 07FF  |  |

| AES        | AHB2 | 0x420C 0000 - 0x420C 03FF  | AHB2    | 0x420C 0000 - 0x420C 03FF  |  |

| OTG_HS     | AHB2 | 0x4204 0000 - 0x4205 FFFF  | N/A     | N/A                        |  |

| OTG_FS     | AHB2 | 0x4204 0000 - 0x420B FFFF  | N/A     | N/A                        |  |

| PSSI       | AHB2 | 0x4202 C400 - 0x4202 C7FF  | N/A     | N/A                        |  |

| DCMI       | AHB2 | 0x4202 C000 - 0x4202 C3FF  | N/A     | N/A                        |  |

| ADC1_2     | AHB2 | 0x4202 8000 - 0x4202 83FF  | AHB2    | 0x4202 8000 - 0x4202 83FF  |  |

| GPIOJ      | AHB2 | 0x4202 2400 - 0x4202 27FF  | N/A     | N/A                        |  |

| GPIOI      | AHB2 | 0x4202 2000 - 0x4202 23FF  | N/A     | N/A                        |  |

AN6012 - Rev 2 page 9/33

|            |      | STM32U5                    |      | STM32U3                    |

|------------|------|----------------------------|------|----------------------------|

| Peripheral | Bus  | Nonsecure boundary address | Bus  | Nonsecure boundary address |

| GPIOH      | AHB2 | 0x4202 1C00 - 0x4202 1FFF  | AHB2 | 0x4202 1C00 - 0x4202 1FFF  |

| GPIOG      | AHB2 | 0x4202 1800 - 0x4202 1BFF  | AHB2 | 0x4202 1800 - 0x4202 1BFF  |

| GPIOF      | AHB2 | 0x4202 1400 - 0x4202 17FF  | N/A  | N/A                        |

| GPIOE      | AHB2 | 0x4202 1000 - 0x4202 13FF  | AHB2 | 0x4202 1000 - 0x4202 13FF  |

| GPIOD      | AHB2 | 0x4202 0C00 - 0x4202 0FFF  | AHB2 | 0x4202 0C00 - 0x4202 0FFF  |

| GPIOC      | AHB2 | 0x4202 0800 - 0x4202 0BFF  | AHB2 | 0x4202 0800 - 0x4202 0BFF  |

| GPIOB      | AHB2 | 0x4202 0400 - 0x4202 07FF  | AHB2 | 0x4202 0400 - 0x4202 07FF  |

| GPIOA      | AHB2 | 0x4202 0000 - 0x4202 03FF  | AHB2 | 0x4202 0000 - 0x4202 03FF  |

| BKPSRAM    | AHB1 | 0x4003 6400 - 0x4003 6BFF  | N/A  | N/A                        |

| GTZC1      | AHB1 | 0x4003 2400 - 0x4003 3FFF  | AHB1 | 0x4003 2400 - 0x4003 33FF  |

| GCACHE     | AHB1 | 0x4003 1800 - 0x4003 1BFF  | N/A  | N/A                        |

| DCACHE     | AHB1 | 0x4003 1400 - 0x4003 17FF  | N/A  | N/A                        |

| ICACHE     | AHB1 | 0x4003 0400 - 0x4003 07FF  | AHB1 | 0x4003 0400 - 0x4003 07FF  |

| GPU2D      | AHB1 | 0x4002 F000 - 0x4002 FFFF  | N/A  | N/A                        |

| GFXMMU     | AHB1 | 0x4002 C000 - 0x4002 EFFF  | N/A  | N/A                        |

| DMA2D      | AHB1 | 0x4002 B000 - 0x4002 BBFF  | N/A  | N/A                        |

| JPEG       | AHB1 | 0x4002 A000 - 0x4002 AFFF  | N/A  | N/A                        |

| RAMCFG     | AHB1 | 0x4002 6000 - 0x4002 6FFF  | AHB1 | 0x4002 6000 - 0x4002 6FFF  |

| MDF1       | AHB1 | 0x4002 5000 - 0x4002 5FFF  | N/A  | N/A                        |

| TSC        | AHB1 | 0x4002 4000 - 0x4002 43FF  | AHB1 | 0x4002 4000 - 0x4002 43FF  |

| CRC        | AHB1 | 0x4002 3000 - 0x4002 33FF  | AHB1 | 0x4002 3000 - 0x4002 33FF  |

| FLASH      | AHB1 | 0x4002 2000 - 0x4002 23FF  | AHB1 | 0x4002 2000 - 0x4002 23FF  |

| FMAC       | AHB1 | 0x4002 1400 - 0x4002 17FF  | N/A  | N/A                        |

| CORDIC     | AHB1 | 0X4002 1000 - 0x4002 13FF  | N/A  | N/A                        |

| GPDMA1     | AHB1 | 0x4002 0000 - 0x4002 0FFF  | AHB1 | 0x4002 0000 - 0x4002 0FFF  |

| DSIHOST    | APB2 | 0x4001 6C00 - 0x4001 7BFF  | N/A  | N/A                        |

| LCD-TFT    | APB2 | 0x4001 6800 - 0x4001 6BFF  | N/A  | N/A                        |

| I3C2       | N/A  | N/A                        | APB2 | 0x4001 6C00 - 0x4001 6FFF  |

| GFXTIM     | APB2 | 0x4001 6400 - 0x4001 67FF  | N/A  | N/A                        |

| USB RAM    | APB2 | 0x4001 6400 - 0x4001 6BFF  | APB2 | 0x4001 6400 - 0x4001 6BFF  |

| USB        | APB2 | 0x4001 6000 - 0x4001 63FF  | APB2 | 0x4001 6000 - 0x4001 63FF  |

| SAI2       | APB2 | 0x4001 5800 - 0x4001 5BFF  | N/A  | N/A                        |

| SAI1       | APB2 | 0x4001 5400 - 0x4001 57FF  | APB2 | 0x4001 5400 - 0x4001 57FF  |

| TIM17      | APB2 | 0x4001 4800 - 0x4001 4BFF  | APB2 | 0x4001 4800 - 0x4001 4BFF  |

| TIM16      | APB2 | 0x4001 4400 - 0x4001 47FF  | APB2 | 0x4001 4400 - 0x4001 47FF  |

| TIM15      | APB2 | 0x4001 4000 - 0x4001 43FF  | APB2 | 0x4001 4000 - 0x4001 43FF  |

| USART1     | APB2 | 0x4001 3800 - 0x4001 3BFF  | APB2 | 0x4001 3800 - 0x4001 3BFF  |

| TIM8       | APB2 | 0x4001 3400 - 0x4001 37FF  | N/A  | N/A                        |

| SPI1       | APB2 | 0x4001 3000 - 0x4001 33FF  | APB2 | 0x4001 3000 - 0x4001 33FF  |

| TIM1       | APB2 | 0x4001 2C00 - 0x4001 2FFF  | APB2 | 0x4001 2C00 - 0x4001 2FFF  |

AN6012 - Rev 2 page 10/33

| STM32U5     |      |                            | STM32U3 |                            |

|-------------|------|----------------------------|---------|----------------------------|

| Peripheral  | Bus  | Nonsecure boundary address | Bus     | Nonsecure boundary address |

| UCPD1       | APB1 | 0x4000 DC00 - 0x4000 DFFF  | N/A     | N/A                        |

| FDCAN1 SRAM | APB1 | 0x4000 AC00 - 0x4000 AFFF  | APB1    | 0x4000 AC00 - 0x4000 AFFF  |

| FDCAN1      | APB1 | 0x4000 A400 - 0x4000 A7FF  | APB1    | 0x4000 A400 - 0x4000 A7FF  |

| I2C6        | APB1 | 0x4000 9C00 - 0x4000 9FFF  | N/A     | N/A                        |

| I2C5        | APB1 | 0x4000 9800 - 0x4000 9BFF  | N/A     | N/A                        |

| LPTIM2      | APB1 | 0x4000 9400 - 0x4000 97FF  | N/A     | N/A                        |

| DTS         | APB1 | 0x4000 8C00 - 0x4000 8FFF  | N/A     | N/A                        |

| I2C4        | APB1 | 0x4000 8400 - 0x4000 87FF  | N/A     | N/A                        |

| USART6      | APB1 | 0x4000 6400 - 0x4000 67FF  | N/A     | N/A                        |

| CRS         | APB1 | 0x4000 6000 - 0x4000 63FF  | APB1    | 0x4000 6000 - 0x4000 63FF  |

| I3C1        | N/A  | N/A                        | APB1    | 0x4000 5C00 - 0x4000 5FFF  |

| I2C2        | APB1 | 0x4000 5800 - 0x4000 5BFF  | APB1    | 0x4000 5800 - 0x4000 5BFF  |

| I2C1        | APB1 | 0x4000 5400 - 0x4000 57FF  | APB1    | 0x4000 5400 - 0x4000 57FF  |

| UART5       | APB1 | 0x4000 5000 - 0x4000 53FF  | APB1    | 0x4000 5000 - 0x4000 53FF  |

| UART4       | APB1 | 0x4000 4C00 - 0x4000 4FFF  | APB1    | 0x4000 4C00 - 0x4000 4FFF  |

| USART3      | APB1 | 0x4000 4800 - 0x4000 4BFF  | APB1    | 0x4000 4800 - 0x4000 4BFF  |

| USART2      | APB1 | 0x4000 4400 - 0x4000 47FF  | N/A     | N/A                        |

| SPI2        | APB1 | 0x4000 3800 - 0x4000 3BFF  | APB1    | 0x4000 3800 - 0x4000 3BFF  |

| IWDG        | APB1 | 0x4000 3000 - 0x4000 33FF  | APB1    | 0x4000 3000 - 0x4000 33FF  |

| WWDG        | APB1 | 0x4000 2C00 - 0x4000 2FFF  | APB1    | 0x4000 2C00 - 0x4000 2FFF  |

| TIM7        | APB1 | 0x4000 1400 - 0x4000 17FF  | APB1    | 0x4000 1400 - 0x4000 17FF  |

| TIM6        | APB1 | 0x4000 1000 - 0x4000 13FF  | APB1    | 0x4000 1000 - 0x4000 13FF  |

| TIM5        | APB1 | 0x4000 0C00 - 0x4000 0FFF  | N/A     | N/A                        |

| TIM4        | APB1 | 0x4000 0800 - 0x4000 0BFF  | APB1    | 0x4000 0800 - 0x4000 0BFF  |

| TIM3        | APB1 | 0x4000 0400 - 0x4000 07FF  | APB1    | 0x4000 0400 - 0x4000 07FF  |

| TIM2        | APB1 | 0x4000 0000 - 0x4000 03FF  | APB1    | 0x4000 0000 - 0x4000 03FF  |

#### 3.4 Boot mode compatibility

The principle of selecting boot mode is the same for both series – it depends on option bytes and BOOT0 pin. The only difference is in the names of FLASH option byte registers for storing the boot address. Refer to Table 4 and/or Table 8. The location of the option bytes remains the same.

For both series, boot selection is different when TrustZone is enabled and disabled.

Table 4. Different naming of boot address option byte registers

| STM32U5      | STM32U3       |

|--------------|---------------|

| NSBOOTADDOR  | FLASH_BOOT0R  |

| NSBOOTADD1R  | FLASH_BOOT1R  |

| SECBOOTADD0R | FLASH_SBOOT0R |

See also Table 5 for overview of peripherals and pins used by the system bootloader to reprogram the flash memory on both series. The difference is mainly in available peripherals and pins used by SPI2 and SPI3 which are highlighted.

AN6012 - Rev 2 page 11/33

| Peripheral | STM32U5             | STM32U3                                                                                        |

|------------|---------------------|------------------------------------------------------------------------------------------------|

| USART1     | PA9/PA10            | PA9/PA10                                                                                       |

| USART2     | PA2/PA3             | N/A                                                                                            |

| USART3     | PC10/PC11           | PC10/PC11                                                                                      |

| I2C1       | PB6/PB7             | PB6/PB7                                                                                        |

| I2C2       | PB10/PB11           | PB10/PB11                                                                                      |

| I2C3       | PC0/PC1             | PC0/PC1                                                                                        |

| I3C1       | N/A                 | PA1/PB13                                                                                       |

| I3C2       | N/A                 | N/A                                                                                            |

| SPI1       | PA4/PA5/PA6/PA7     | PA4/PA5/PA6/PA7  Note: For WLCSP68-G, PG3/PG4/PG5/PG2 are selected instead of PA4/PA5/PA6/PA7. |

| SPI2       | PB12/PB13/PB14/PB15 | PD0/PD1/PD3/PD4                                                                                |

| SPI3       | PB5/PG9/PG10/PG12   | PA15/PB3/PB4/PB5                                                                               |

| FDCAN      | PB8/PB9             | PB8/PB9                                                                                        |

| USB/OTG    | PA11/PA12           | PA11/PA12                                                                                      |

Table 5. Comparison of peripherals and pins used by bootloader

## 3.5 Global TrustZone® controller (GTZC)

The main difference is the number of instances for each serie: while STM32U3 devices embed one GTZC peripheral, STM32U5 devices embed two GTZC peripherals. The STM32U5 devices offers also watermark memory peripheral controller (MPCWM), protecting external memories, and backup SRAM. Concerning the MPCBB part, the number of its instances and blocks differ from device to device, as these depend on the counts and sizes of internal SRAMs.

Due to the differences mentioned above and different sets of peripherals and memories for each series, the content and size of registers differ significantly. Refer to document [1] and [2] to see GTZC configuration for individual devices.

#### 3.6 SRAMs and RAM configuration controller (RAMCFG)

STM32U5 devices offer more SRAMs and more volatile memory size than STM32U3 devices. For comparison of available SRAMs and its sizes, refer to the Section 3.1.

See Table 6 to find an overview of features of individual SRAMs for both series. Note that due to the continuous memory mapping, the boundary addresses of SRAMs in memory mapping differ. Refer to [1] and [2] for more details.

The most significant difference is the error detection and correction mechanism. While STM32U5 devices use ECC for error detection and single error correction, STM32U3 devices only use hardware parity check for error detection. Also, the wait states of STM32U5 must be correctly set, while STM32U3 does not need any wait states for read/write operations.

AN6012 - Rev 2 page 12/33

Table 6. Comparison of features for individual SRAMs

|                                       |       |       |       | STM32U5 |       |       |             | STM   | 32U3  |

|---------------------------------------|-------|-------|-------|---------|-------|-------|-------------|-------|-------|

| Feature                               | SRAM1 | SRAM2 | SRAM3 | SRAM4   | SRAM5 | SRAM6 | BKP<br>SRAM | SRAM1 | SRAM2 |

| DMA accessibility in Stop 0/1 modes   | Х     | Х     | Х     | X       | Х     | Х     | Х           | X     | X     |

| DMA accessibility in Stop 2 mode      | -     | -     | -     | X       | -     | -     | -           | X     | X     |

| Optional retention in Standby mode    | -     | х     | -     | _       | -     | -     | Х           | -     | X     |

| Optional retention in VBAT mode       | -     | -     | -     | _       | -     | -     | X           | -     | -     |

| Erased with RDP regression            | Х     | Х     | Х     | X       | Х     | Х     | Х           | X     | Х     |

| Erased or blocked by tamper detection | -     | Х     | -     | -       | -     | -     | Х           | -     | Х     |

| Optionally erased with system reset   | Х     | Х     | Х     | X       | Х     | Х     | -           | X     | Х     |

| Software erase                        | Х     | Х     | Х     | Х       | Х     | Х     | X           | Х     | Х     |

| ECC                                   | -     | Х     | Х     | -       | -     | -     | X           | -     | -     |

| Hardware parity check                 | -     | -     | -     | -       | -     | -     | -           | -     | х     |

| Write protection                      | -     | Х     | -     | -       | -     | -     | -           | -     | Х     |

| Wait states                           | X     | X     | X     | X       | X     | X     | X           | -     | -     |

The registers of both series are similar and differ in setting of ECC or hardware parity check, and wait states. For more details, refer to the corresponding chapters in document [1] and [2].

#### 3.7 **Embedded flash memory (FLASH)**

The sizes of embedded flash memory may differ throughout the devices. For comparison of individual lines of both series, see Section 3.1 and/or corresponding datasheets.

The embedded flash memories of both series are different also in the memory organization and set of features that they support. Refer to Table 7 to see an overview of features for each serie.

Table 7. Overview of flash memory features for STM32U3 and STM32U5 devices

| Feature                          | STM32U5                                                                                                                                      | STM32U3                                                                                                                               |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| Memory organization              | <ul> <li>Dual bank architecture</li> <li>Up to 2 Mbytes per bank for main memory</li> <li>64.5 Kbytes information block in bank 1</li> </ul> | <ul> <li>Dual bank architecture</li> <li>Up to 512 Kbytes per bank for main memory</li> <li>104.5 Kbytes information block</li> </ul> |  |

| Page size                        | 8 Kbytes                                                                                                                                     | 4 Kbytes                                                                                                                              |  |

| Endurance                        | 100 kcycles for up to 256 Kbytes per bank, 10 kcycles for the reset                                                                          | 10 kcycles                                                                                                                            |  |

| Programming and read granularity | 128 effective bits + 9 ECC bits                                                                                                              | 64 effective bits + 8 ECC bits                                                                                                        |  |

| OTP                              | 512                                                                                                                                          | bytes                                                                                                                                 |  |

| Wait states                      | <ul> <li>Up to 4 WS with LPM = 0</li> <li>Up to 15 WS with LPM = 1</li> </ul>                                                                | <ul> <li>Up to 2 WS with LPM = 0</li> <li>Up to 4 WS with LPM = 1</li> </ul>                                                          |  |

| Read/write protection            | RDP protection (4 levels)                                                                                                                    | RDP protection (4 levels)                                                                                                             |  |

AN6012 - Rev 2 page 13/33

| Feature           | STM32U5                                                                                                                                                         | STM32U3                                                                                                                                                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | Write protection (2 areas per<br>bank, 8-Kbyte granularity)                                                                                                     | Write protection (2 areas per<br>bank, 4-Kbyte granularity)                                                                                                                                                                     |

| TrustZone support | <ul> <li>Watermark-based secure flash memory area protection</li> <li>Secure hide protection areas (HDP)</li> <li>Block-based secure area protection</li> </ul> | <ul> <li>Watermark-based secure flash memory area protection</li> <li>Secure hide protection areas (HDP)</li> <li>Secure hide protection extension areas (HDP extension)</li> <li>Block-based secure area protection</li> </ul> |

Other changes concern the registers of the flash memory peripheral. Even though the functionality is very similar for both series, several registers on STM32U3 were renamed, shrunk/extended or moved. Some registers were even added, for new features like HDP extension, or larger OEM keys. See Table 8 with an overview of changes between the series.

Table 8. Comparison of flash memory registers and option bytes for STM32U5 and STM32U3

| Register           |                | Difference                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|--------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| STM32U5            | STM32U3        | DITTETENCE                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| FLASH_NSKEYR       | FLASH_KEYR     | Register (NSKEYR <-> KEYR) and field (NSKEY <-> KEY) name change.                                                                                                                                                                                                                                                                                                                                                          |  |

| FLASH_SECKEYR      | FLASH_SKEYR    | Register (SECKEYR <-> SKEYR) and field (SECKEY <-> KEY) name change.                                                                                                                                                                                                                                                                                                                                                       |  |

| FLASH_OPTKEYR      | FLASH_OPTKEYR  | Field (OPTKEY <-> KEY) name change.                                                                                                                                                                                                                                                                                                                                                                                        |  |

| FLASH_NSSR         | FLASH_SR       | Register (NSSR <-> SR) name change.                                                                                                                                                                                                                                                                                                                                                                                        |  |

| FLASH_SECSR        | FLASH_SSR      | Register (SECSR <-> SSR) name change.                                                                                                                                                                                                                                                                                                                                                                                      |  |

| FLASH_NSCR         | FLASH_CR       | Register (NSCR <-> CR) name change. Size of PNB field differs - 8 bits on STM32U5 compared to 7 bits on STM32U3 (fewer pages).                                                                                                                                                                                                                                                                                             |  |

| FLASH_SECCR        | FLASH_SCR      | Register (SECCR <-> SCR) name change. Size of PNB field differs - 8 bits on STM32U5 compared to. 7 bits on STM32U3 (fewer pages).                                                                                                                                                                                                                                                                                          |  |

|                    | FLASH_ECCCORR  | Split of the ECCR register on STM32U5 to two registers on STM32U3:                                                                                                                                                                                                                                                                                                                                                         |  |

| FLASH_ECCR         | FLASH_ECCDETR  | ECCCORR for single error correction and ECCDETR for double error detection. Fields are split accordingly, SYSF_ECC and BK_ECC are present in both. Size of ADDR_ECC differs - 21 bits on STM32U5 compared to 19 bits on STM32U3.                                                                                                                                                                                           |  |

| FLASH_OPSR         | FLASH_OPSR     | Register address offset change (0x34 for STM32U5 compared to 0x38 for STM32U3). The size of ADDR_OP differs - 21 bits on STM32U5 compared to 19 bits on STM32U3.                                                                                                                                                                                                                                                           |  |

| FLASH_OPTR         | FLASH_OPTR     | Option bit PA15_PUPEN (bit 28) not present on STM32U3. SRAM2_ECC (bit 24) on STM32U5 corresponds to SRAM2_PE (bit 24) on STM32U3 (ECC compared to hardware parity). SRAM3_ECC and BKPRAM_ECC (bits 22 and 23) not present on STM32U3. SRAM_RST (bit 15) on STM32U5 corresponds to SRAM1_RST on STM32U3 and influences only SRAM1 erase. BDRST_STOP (backup domain reset on power-on reset, bit 11) not present on STM32U5. |  |

| FLASH_NSBOOTADD0R  | FLASH_BOOT0R   | Register (NSBOOTADD0R <-> BOOT0R) and field (NSBOOTADD0 <-> ADD) name change.                                                                                                                                                                                                                                                                                                                                              |  |

| FLASH_NSBOOTADD1R  | FLASH_BOOT1R   | Register (NSBOOTADD1R <-> BOOT1R) and field (NSBOOTADD1 <-> ADD) name change.                                                                                                                                                                                                                                                                                                                                              |  |

| FLASH_SECBOOTADDOR | FLASH_SBOOT0R  | Register (SECBOOTADD0R <-> SBOOT0R) and field (SECBOOTADD0 <-> ADD) name change.                                                                                                                                                                                                                                                                                                                                           |  |

| FLASH_SECWMxR1     | FLASH_SECWMxR1 | Field (SECWM1_PEND <-> SECWM1_END, SECWM1_PSTRT <-> SECWM1_STRT) name change. The size of both fields differs - 8 bits on STM32U5 compared to 7 bits on STM32U3.                                                                                                                                                                                                                                                           |  |

AN6012 - Rev 2 page 14/33

| Register        |                  | Difference                                                                                                                                                                                                        |

|-----------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STM32U5         | STM32U3          | Difference                                                                                                                                                                                                        |

| FLASH_SECWMxR2  | FLASH_SECWMxR2   | Field (HDP1_PEND <-> HPD1_END) name change. HDP disable done with 1 bit on STM32U5 compared to 8 bits on STM32U3 (keyword needed). Size of HDP1_(P)END differs - 8 bits on STM32U5 compared to 7 bits on STM32U3. |

| FLASH_WRPxyR    | FLASH_WRPxyR     | Field (WRPxyR_PSTRT <-> STRT, WRPxyR_PEND <-> END) name change.                                                                                                                                                   |

| FLASH_SECBByRRx | FLASH_SECBByRRx  | Different count of registers - $x = (1 \text{ to } 8)$ on STM32U5 compared to $x = (1 \text{ to } 4)$ on STM32U3                                                                                                  |

| FLASH_SECHDPCR  | FLASH_SECHDPCR   | HDP access disable fields - only 1 bit for each HDP area on STM32U5 compared to 8-bit keyword for each HDP and HDP extension area on STM32U3.                                                                     |

| FLASH_PRIVCFGR  | FLASH_PRIVCFGR   | Field (NSPRIV <-> PRIV) name change.                                                                                                                                                                              |

| N/A             | FLASH_SECHDPEXTR | New register for STM32U3 for enable of HDP extension areas.                                                                                                                                                       |

| FLASH_PRIVBByRx | FLASH_PRIVBByRx  | Different count of registers - $x = (1 \text{ to } 8)$ on STM32U5 compared to $x = (1 \text{ to } 4)$ on STM32U3.                                                                                                 |

| FLASH_OEM1KEYRx | FLASH_OEM1KEYRx  | Different count of registers, or size of the OEM1 key respectively - 64 bits on STM32U5 compared to 128 bits on STM32U3. Register address offset change (0x70 on STM32U5 compared to 0x110 on STM32U3).           |

| FLASH_OEM2KEYRx | FLASH_OEM2KEYRx  | Different count of registers, or size of the key respectively - 64 bits on STM32U5 compared to 128 bits on STM32U3. Register address offset change (0x78 on STM32U5 compared to 0x120 on STM32U3).                |

| N/A             | FLASH_OEMKEYSR   | New register for STM32U3 with OEM1 and OEM2 keys CRC.                                                                                                                                                             |

For more details, refer to document [1] and [2].

#### 3.8 Power controller (PWR)

Even though both STM32U3 and STM32U5 devices fall into the ultra-low-power family of MCUs and share similar bases, there are many differences between them from the user point-of-view.

Starting with hardware, both series contain LDO regulators and offer packages with embedded SMPS requiring some external circuitry. These requirements are for both the same. Concerning the power pins, some STM32U5 devices require additional DSI supply and offer V<sub>DD11USB</sub> and/or V<sub>DD11DSI</sub> domains.

The PWR of STM32U5 devices offer up to 24 pins for up to eight WKUP events, whereas STM32U3 devices have 23 pins (compatible with STM32U5) and up to 10 WKUP events. Two additional events are reserved for I3C reset patterns. These pins can also invoke a wake-up interrupt. On STM32U5, this is limited to Stop 3 mode only. STM32U5 devices also embed a temperature sensor and backup domain voltage monitor to continuously check operational conditions.

STM32U5 devices provide four voltage ranges, whereas STM32U3 devices only provide two. However, as the STM32U3 devices use subtreshold technology, the  $V_{CORE}$  voltage of both ranges is lower than on STM32U5 and so is the power consumption. The EPOD booster of STM32U3 devices must be turned on for frequencies above 24 MHz (compared to 55 MHz on STM32U5).

The consumption is even lower on STM32U3 thanks to the adaptive voltage scaling (AVS) technique. The  $V_{CORE}$  is tuned individually on each device to achieve the target frequency of every voltage range and have the lowest consumption at the same time. The exact voltages of STM32U3 voltage ranges might therefore vary.

As the SmartRun domain (SRD) is not present on STM32U3 devices, it does not offer the LPBAM functionality and the number of peripherals autonomous in Stop 0/1/2 modes is limited.

The mentioned differences are summarized in Table 9.

AN6012 - Rev 2 page 15/33

Table 9. Overview of differences of PWR on STM32U3 and STM32U5 devices

| Feature                      |                   | STM32U5 series                                                                                                                                                                                                                               | STM32U3 series                                                                                                         |

|------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Power supply domains         |                   | V <sub>CORE</sub> , V <sub>DD</sub> , backup, analog,<br>V <sub>DDSMPS</sub> , V <sub>DDIO2</sub> , V <sub>DDUSB</sub><br>(and optional V <sub>DD11USB</sub> ),<br>V <sub>DDDSI</sub> <sup>(1)</sup> and V <sub>DD11DSI</sub> <sup>(1)</sup> | V <sub>CORE</sub> , V <sub>DD</sub> , backup, analog,<br>V <sub>DDSMPS</sub> , V <sub>DDIO2</sub> , V <sub>DDUSB</sub> |

| Power supply supervision     |                   | BOR, PVD, PVM monitors,<br>out of functional range<br>temperature & backup<br>domain voltage monitors                                                                                                                                        | BOR, PVD, PVM monitors                                                                                                 |

| Voltage ranges               |                   | 4                                                                                                                                                                                                                                            | 2                                                                                                                      |

| EPOD booster corner freque   | ency              | 55 MHz                                                                                                                                                                                                                                       | 24 MHz                                                                                                                 |

| Adaptive voltage scaling (AV | <b>/</b> S)       | No                                                                                                                                                                                                                                           | Yes                                                                                                                    |

| Output pins                  |                   | CSLEEP, CDSTOP,<br>SRDSTOP                                                                                                                                                                                                                   | PWR_CSLEEP,<br>PWR_CSTOP                                                                                               |

|                              | WKUPx events      | 8                                                                                                                                                                                                                                            | 10                                                                                                                     |

|                              | Wake-up pins      | 24 pins                                                                                                                                                                                                                                      | 23 pins                                                                                                                |

| PWR wake-up                  | Wake-up interrupt | PWR_S3WU (Stop 3 mode<br>only) - Exit from Stop 3,<br>Standby, and Shutdown<br>modes                                                                                                                                                         | PWR and PWR_S - Exit from<br>Sleep, Stop 0/1/2/3, Standby<br>and Shutdown modes                                        |

| LPBAM                        |                   | Yes                                                                                                                                                                                                                                          | No                                                                                                                     |

| Autonomous peripherals       | Stop 0/1          | ADC4, DAC, all LPTIMs, all<br>U(S)ARTs, LPUART1, all<br>SPIs, all I2Cs, MDF1, ADF1,<br>GPDMA1, LPDMA1                                                                                                                                        | DAC, LPTIMx (x = 1 to 4), all<br>U(S)ARTs, LPUART1, all<br>SPIs, all I2Cs, all I3Cs, ADF1,<br>GPDMA1                   |

|                              | Stop 2            | ADC4, DAC, LPTIM1,<br>LPTIM3, LPUART1, SPI3,<br>I2C3, ADF1, LPDMA1                                                                                                                                                                           | LPTIM1, LPTIM3, LPTIM4,<br>LPUART1, I2C3                                                                               |

<sup>1.</sup> Only on STM32U59x/Ax/Fx/Gx devices.

Due to these differences and different sets of peripherals available the PWR registers of both series are not compatible. Refer to document [1] and [2] for more details.

#### 3.9 Reset and clock control (RCC)

The first part, reset control, is the same for both STM32U3 and STM32U5 devices. For the clocks and its control, there are many differences.

The main differences are the maximum operational frequency and the absence of PLL on STM32U3 devices. This is compensated by MSI clocks offering frequencies up to maximum frequency, that is 96 MHz (the MSI of STM32U5 offers frequencies up to 48 MHz) with more options of hardware autocalibration (so called PLL-mode). Additionally, using PLL-mode on STM32U3, the multiplication factor for the MSIRCx (x = 0,1) oscillator might be tuned to obtain other frequencies from 3 up to 96 MHz.

The STM32U3 devices also offer additional clock output, MCO2.

Refer to Table 10 for overview of these differences.

AN6012 - Rev 2 page 16/33

Table 10. Overview of differences of RCC on STM32U3 and STM32U5

| Feat              | tures       | STM32U5                                                                                                                                                          | STM32U3                                                                                                          |

|-------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Maximum frequency |             | 160 MHz                                                                                                                                                          | 96 MHz                                                                                                           |

| SYSCLK clocks     |             | <ul> <li>HSI16 (16 MHz)</li> <li>MSIS (0.1-48 MHz)</li> <li>HSE (4-50 MHz)</li> <li>PLL1</li> </ul>                                                              | <ul><li>HSI16</li><li>MSIS (3-96 MHz)</li><li>HSE (4-50 MHz)</li></ul>                                           |

| Additional clocks |             | <ul> <li>MSIK (0.1-48 MHz)</li> <li>LSI (32/0.25 kHz)</li> <li>LSE (32.768 kHz)</li> <li>HSI48 (48 MHz)</li> <li>SHSI (48 MHz)</li> <li>PLL2 and PLL3</li> </ul> | <ul> <li>MSIK (3-96 MHz)</li> <li>LSI (32/0.25 kHz)</li> <li>LSE (32.768 kHz)</li> <li>HSI48 (48 MHz)</li> </ul> |

| PLL               |             | main PLL + 2x PLL for kernel clocks                                                                                                                              | N/A                                                                                                              |

| Clock output      |             | MCO, LSCO                                                                                                                                                        | MCO, MCO2, LSCO                                                                                                  |

|                   | Oscillators | 4 (48/4/3.072/0.4 MHz)                                                                                                                                           | 2 (96/24 MHz)                                                                                                    |

| MSI               | Frequencies | 48, 24, 16, 12, 4, 2, 1.33, 1, 3.072, 1.536, 1.024, 0.768, 0.4, 0.2, 0.133, 0.1 MHz                                                                              | 96, 48, 24.576, 24, 22.5792, 12.288, 12, 11.2896, 6.144, 6, 5.6448, 3.072, 3, 2.8224 MHz                         |

|                   | PLL-mode    | LSE                                                                                                                                                              | HSE (16 or 32 MHz), LSE                                                                                          |

Concerning the kernel clocks, the STM32U5 devices offers more options. See Table 11 for more details.

Table 11. Comparison of available kernel clocks for individual peripherals on STM32U3 and STM32U5

| Peripheral           | STM32U5                                                           | STM32U3                                                      |

|----------------------|-------------------------------------------------------------------|--------------------------------------------------------------|

| IWDG                 | LSI                                                               | LSI                                                          |

| UCPD1                | HSI16                                                             | N/A                                                          |

| RTC                  | <ul><li>LSI</li><li>LSE</li><li>HSE/32</li></ul>                  | <ul><li>LSI</li><li>LSE</li><li>HSE/32</li></ul>             |

| LPTIM1/3/4           | <ul><li>LSI</li><li>LSE</li><li>MSIK</li><li>HSI16</li></ul>      | <ul><li>LSI</li><li>LSE</li><li>MSIK</li><li>HSI16</li></ul> |

| SysTick              | LSI LSE HCLK/8                                                    | LSI     LSE     HCLK/8                                       |

| TIM2/3/4/(5)/6/7     | PCLK1 x1 or x2                                                    | PCLK1 x1 or x2                                               |

| U(S)ART(2)/3/4/5/(6) | <ul><li>PCLK1</li><li>LSE</li><li>HSI16</li><li>SYSCLK</li></ul>  | PCLK1     HSl16                                              |

| SPI2                 | <ul><li>PCLK1</li><li>MSIK</li><li>HSI16</li><li>SYSCLK</li></ul> | PCLK1     MSIK                                               |

| I2C1/2/(4/5/6)       | <ul><li>PCLK1</li><li>MSIK</li><li>HSI16</li><li>SYSCLK</li></ul> | PCLK1     MSIK                                               |

| I3C1                 | N/A                                                               | PCLK1                                                        |

AN6012 - Rev 2 page 17/33

| Peripheral        | STM32U5                                                                               | STM32U3                                                         |

|-------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|                   |                                                                                       | • MSIK                                                          |

| LPTIM2            | <ul><li>PCLK1</li><li>LSI</li><li>LSE</li><li>HSI16</li></ul>                         | <ul><li>PCLK1</li><li>LSI</li><li>LSE</li><li>HSI16</li></ul>   |

| FDCAN1            | <ul><li>HSE</li><li>PLL1_Q</li><li>PLL2_P</li></ul>                                   | PCLK1     MSIK                                                  |

| CRS               | HSI48                                                                                 | HSI48                                                           |

| OCTOSPI1/(2)      | <ul><li>SYSCLK</li><li>MSIK</li><li>PLL1_Q</li><li>PLL2_Q</li></ul>                   | PCLK1     MSIK                                                  |

| SAES              | SHSI SHSI /2                                                                          | HCLK                                                            |

| TIM1/(8/)15/16/17 | PCLK2 x1 or x2                                                                        | PCLK2 x1 or x2                                                  |

| USART1            | <ul><li>PCLK2</li><li>HSI16</li><li>LSE</li><li>SYSCLK</li></ul>                      | PCLK2     HSI16                                                 |

| SPI1              | <ul><li>PCLK2</li><li>MSIK</li><li>HSI16</li><li>SYSCLK</li></ul>                     | PCLK2     MSIK                                                  |

| I3C2              | N/A                                                                                   | PCLK2     MSIK                                                  |

| ADF1 (and MDF1)   | MSIK     AUDIOCLK     HCLK     PLL1     PLL3                                          | MSIK     AUDIOCLK     SAI1 clock                                |

| SAI1/(2)          | <ul><li>AUDIOCLK</li><li>PLL1_P</li><li>PLL2_P</li><li>PLL3_P</li><li>HSI16</li></ul> | MSIK     AUDIOCLK     HSE                                       |

| ICLK              | <ul><li>MSIK</li><li>HSI48</li><li>PLL1_Q</li><li>PLL2_Q</li></ul>                    | <ul><li>MSIK</li><li>HSI48</li><li>HSE</li><li>SYSCLK</li></ul> |

| SDMMC1/(2)        | • ICLK • PLL1_P                                                                       | ICLK                                                            |

| USB or OTG_FS     | ICLK                                                                                  | ICLK     ICLK /2                                                |

| RNG               | <ul><li>HSI16</li><li>HSI48</li><li>HSI48 /2</li></ul>                                | MSIK     HSI48                                                  |

| 12C3              | <ul><li>PCLK3</li><li>MSIK</li><li>HSI16</li><li>SYSCLK</li></ul>                     | PCLK3     MSIK                                                  |

| SPI3              | PCLK3     MSIK                                                                        | <ul><li>PCLK3</li><li>MSIK</li></ul>                            |

AN6012 - Rev 2 page 18/33

| Peripheral         | STM32U5                                                                                     | STM32U3                                                                           |

|--------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

|                    | <ul><li>HSI16</li><li>SYSCLK</li></ul>                                                      |                                                                                   |