## How to implement an NFC coil multiplexer for multi-antenna switching

#### Introduction

NFC technology is becoming increasingly popular for products in consumer electronics, moving away from its strict use as a card reader.

This document applies to the NFC transceivers indicated in Table 1. It describes the basic solution of the switching sequence when the device operates with more than one antenna, the physical effects and signals, and a complete solution in form of a prototype.

Table 1. Applicable products

| Туре             | Product RPNs                                                     |

|------------------|------------------------------------------------------------------|

| ST25 NFC readers | ST25R200, ST25R3916, ST25R3918, ST25R3916B, ST25R3917B, ST25R500 |

# 1 Acronyms

**Table 2. List of acronyms**

| Acronym    | Definition                               |

|------------|------------------------------------------|

| NFC        | Near field communication                 |

| WLC        | Wireless charging                        |

| Q - factor | Quality factor                           |

| EMI        | Electromagnetic interference             |

| HW         | Hardware                                 |

| SW         | Software                                 |

| PA         | Power amplifier                          |

| GUI        | Graphical user interface                 |

| IC         | Integrated circuit                       |

| MCU        | Main controlling unit                    |

| NMOS       | N-doped silicon metal oxid semiconductor |

| VNA        | Vector network analyzer                  |

| ID         | Identity                                 |

AN6121 - Rev 2 page 2/24

## 2 Current working status

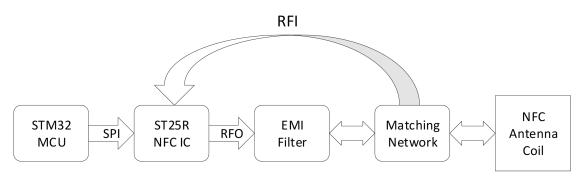

An NFC network includes a coil and a matching network, as shown in Figure 1. The matching impedance is adapted to the antenna form factor.

Figure 1. Block diagram of an NFC reader

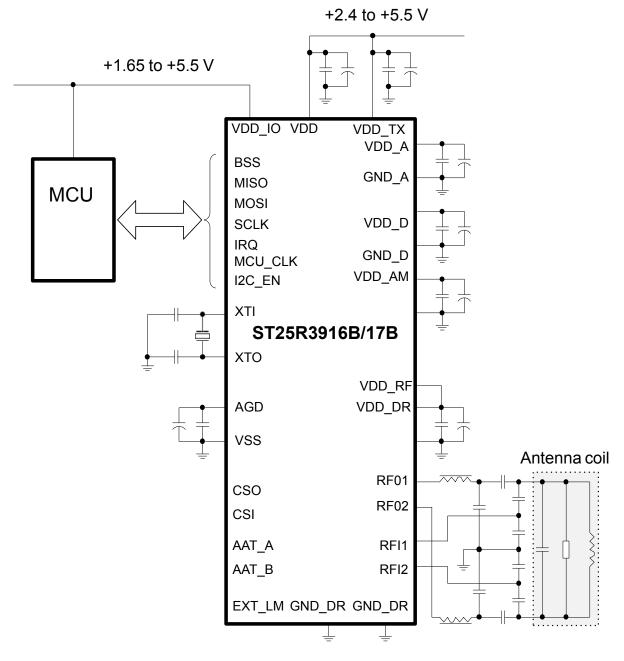

The RFO pins of the ST25R3916B are differential square signals with a frequency of 13.56 MHz. This means that the maximum amplitude of the signal is equal to the supply voltage, which is 5 V. The minimum is the ground potential (0 V).

AN6121 - Rev 2 page 3/24

Figure 2. System diagram (single antenna driving)

If a second antenna is connected to the same network on the RFO output pins, the system does not work because it is not possible to match two different antennas to one output. The antennas must be separated.

AN6121 - Rev 2 page 4/24

#### 3 Solution with more antennas

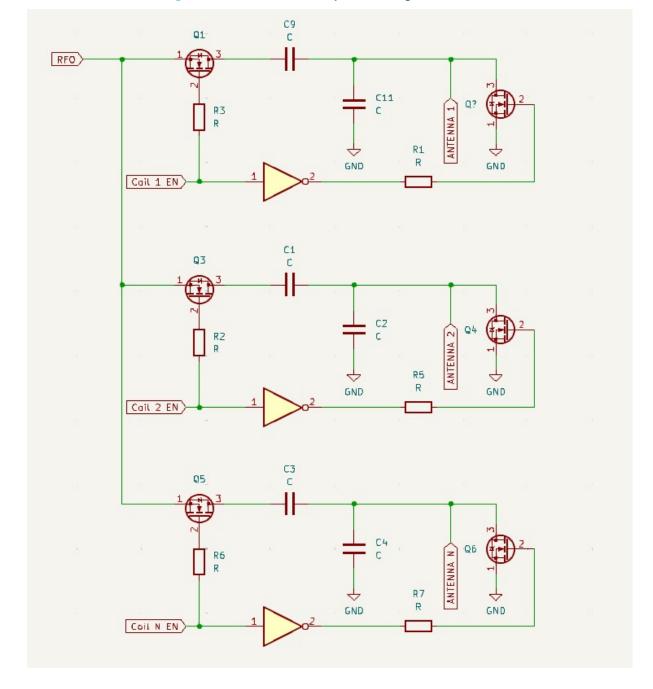

As shown in Figure 3, each antenna is individually tuned, hence it can be individually designed. The switch selects the antennas, allowing the user to choose between different NFC coils.

Control signal NFC Matching Antenna Network Coil RFI NFC Matching Antenna Network Coil Antenna STM32 ST25R **EMI** SPI RFO Selection NFC IC MCU Filter Circuit NFC Matching Antenna Network Coil

Figure 3. Block diagram of an NFC reader with multiplexed antennas

The selection must be made from a separate multiplexing IC or from the GPIO pins of the MCU controller. The number of available GPIO pins must be at least equal to the number of antennas used.

AN6121 - Rev 2 page 5/24

### 4 The basic solution of the switching sequence

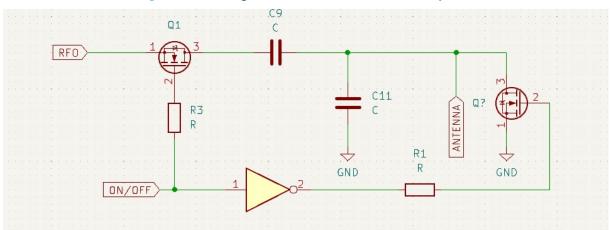

In a system with more than one antenna, an NMOS switching transistor creates a separation circuit. This means that each antenna has its own matching network.

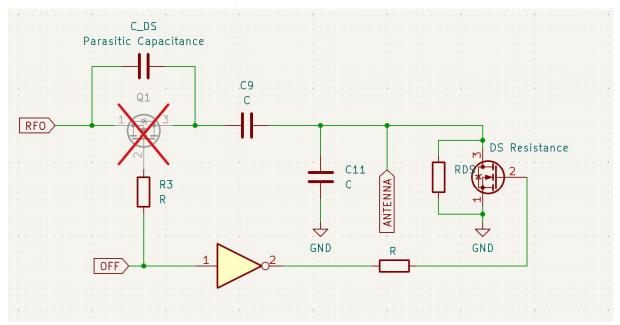

In Figure 4, a serial NMOS switch (Q1) disconnects the matching network and the antenna from the RFO terminals of the chip. The NMOS transistor has a parasitic capacitance, which leads to a parasitic current in the matching network. For this reason, a second NMOS transistor is connected in parallel to the antenna. This pulls down the floating open side of the matching network. In this case, no parasitic current in the coil can cause a field that would read tags on this antenna.

Figure 4. Switching block of one antenna in the multiplexer

If the voltage at the NMOS gate is equal to or lower than the voltage at the source, the transistor is turned off and does not conduct current through the RFO path to the coil. This is the case when the gate of the NMOS transistor is pulled to GND.

To turn on the transistor, the gate voltage must be raised above the RFO voltage plus the threshold voltage of the transistor. In this case 12 V is high enough to drive the transistor into saturation. Now, the NMOS transistor is turned on and drives the RFO path to the coil.

The antenna is ON.

AN6121 - Rev 2 page 6/24

Figure 5. Schematic of a multiplexer in single ended mode

AN6121 - Rev 2 page 7/24

# 5 Impedance grounding during off state

When the antenna is not in use, the RFO switches have a small parasitic capacitance, which causes crosstalk. To suppress this effect, it is necessary to pull down the RFO pins to GND. This is possible using additional NMOS transistors, connected in parallel with the parallel matching capacitors.

Figure 6. Parasitic components

AN6121 - Rev 2 page 8/24

#### 6 Schematics

Each antenna has a basic element, assembled in the complete system.

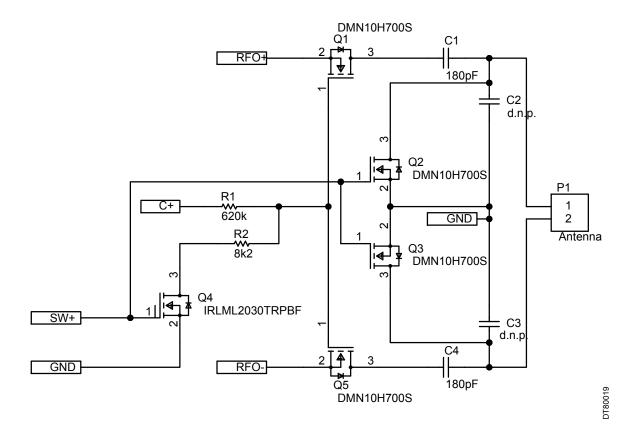

All antennas use the same switching element, whose schematic is shown in Figure 7. It comprises the RFO switching MOSFETs (Q1 and Q5), the grounding MOSFETs (Q2 and Q3), and one controlling MOSFET for the RFO switches (Q4). The ratio and value of R1 and R2 are chosen in a way that Q4 can pull the gate of Q1 and Q5 to ground. If Q4 is high ohmic the gate of Q1 and Q5 should reach the high level of the net C+. Thus their value also depend on the used transistor.

Figure 7. Single switching module

Source from external boost converter

An external boost converter (in this case the ST8R00W device) is used to control the gate voltage of the RFO MOSFET. This is useful if more than four antennas are used, as in Figure 8. The cascade supply also loads the RFO ports of the ST25R3916B device, causing losses.

AN6121 - Rev 2 page 9/24

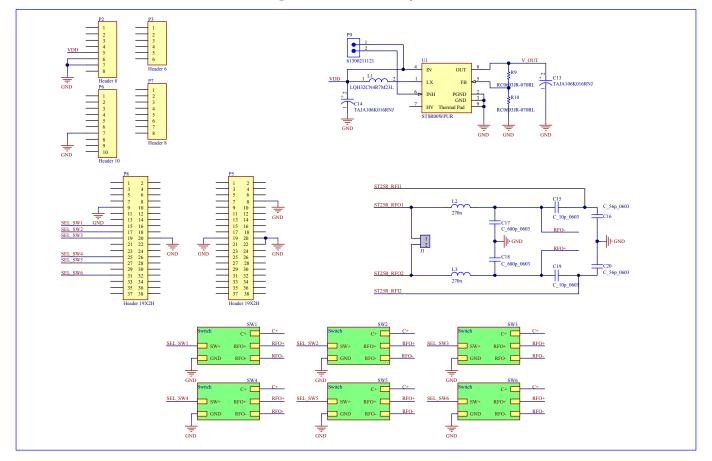

Figure 8. 6-antenna multiplexer

AN6121 - Rev 2 page 10/24

#### 6.1 PCB design

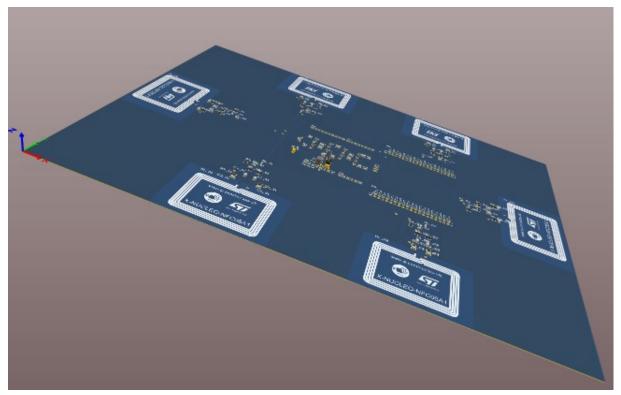

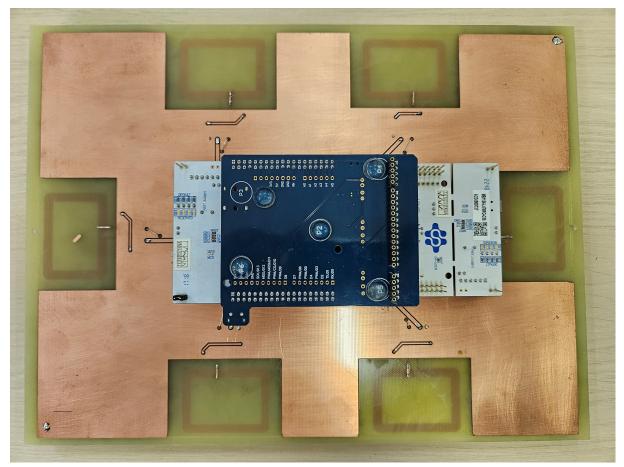

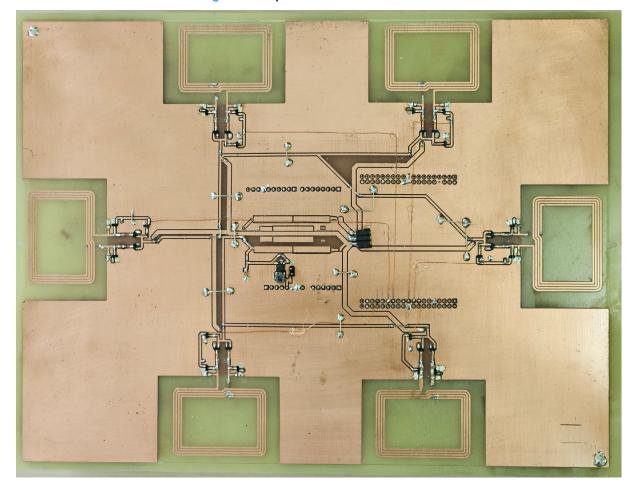

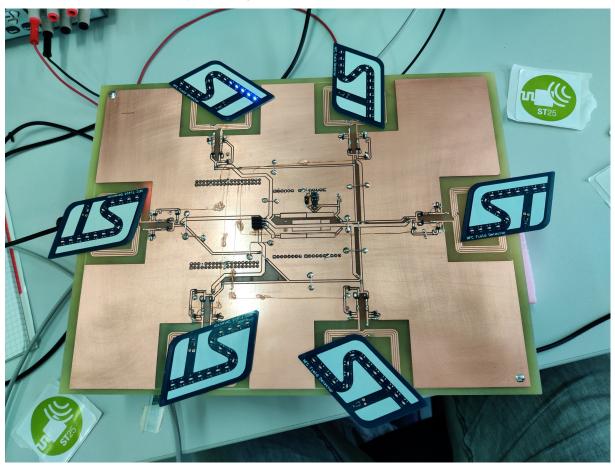

The prototype is based on a copper PCB (30 cm x 23 cm), milled on an LPKF CNC milling machine.

TOTAL STATE OF THE STATE OF THE

Figure 9. PCB design for a 6-antenna multiplexer

The board is double-sided, with pure copper islands connected to the ground plane to reduce emissions and parasitics. The EMI filter has been modified on the NFC05 demonstration board. This board is connected to the antenna matrix board together with a Nucleo L476 board to control the antenna switching.

AN6121 - Rev 2 page 11/24

In Figure 10, the headers of the Nucleo switching board are on the right, and the NFC05 board are on the left. The boards are placed on the antenna board from below.

AN6121 - Rev 2 page 12/24

Viewed from below, the Nucleo board is on the left and the NFC05 is on the right. The red twisted cable is used to connect the VNA to the RFO pins and capture the Smith chart of the individual antennas.

AN6121 - Rev 2 page 13/24

Figure 12. Top view of the machined PCB

AN6121 - Rev 2 page 14/24

### 7 Tests

## 7.1 Signal quality

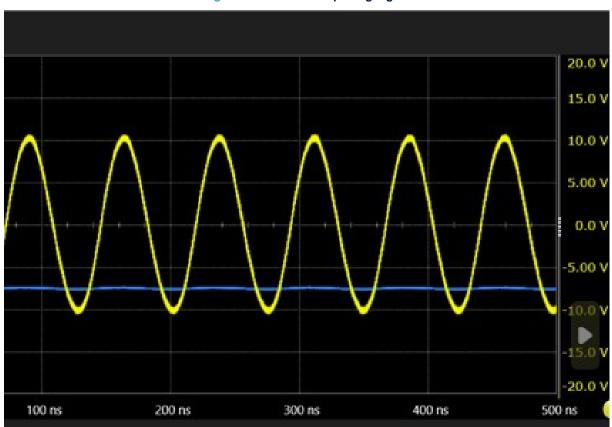

The 13.56 MHz main signal is measured differentially at the output ports after the matching network. The antenna is unloaded for this measurement.

Figure 13. Continuous polling signal

AN6121 - Rev 2 page 15/24

#### 7.2 Antenna matching

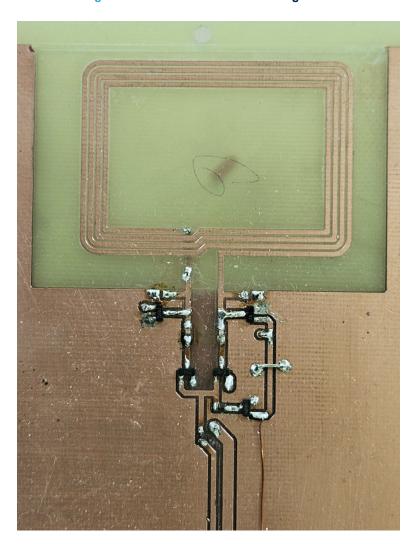

As shown in Figure 14, each antenna has its switching system close to the ports. This matching network is located directly on these ports. Each antenna should show approximately the same matching behavior under these conditions, which can be proved with the VNA. The path between the switching, matching network, and EMI filter should be equalized as much as possible.

Figure 14. Antenna with the switching block

The parasitics of the capacitor manufacturer's accuracy of 5% causes a few Hz deviation.

#### 7.3 Card reading

A card reading test is performed to verify that each antenna switch works.

An NFC tag with a unique ID is placed on each antenna. Pressing the 'next' button on the Nucleo control panel turns off the active antenna and turns on the next antenna in the sequence.

T79229V1

AN6121 - Rev 2

SCALE STATE OF THE STATE OF THE

Figure 15. Setup for the sequential card reading test

As shown in Figure 16, the GUI shows that the chip reads each card on the currently selected antenna.

Figure 16. Reading cards on discovery graphical user interface

AN6121 - Rev 2 page 17/24

☐ Tune antenna when there are no tags

When reading, the system waits four seconds before moving to the next card. No crosstalk is visible. The card reads are recognized at the button press.

Pressing the enable button activates only the selected antenna. Figure 17 shows part of the polling sequence. The field detector is illuminated. All other detectors remain dark.

AN6121 - Rev 2 page 18/24

## 8 Conclusion

This document has demonstrated the possibility of driving several antennas using applicable devices. Refer to Table 1.

The system is built with six antennas as a proof of concept, but it is possible to drive up to 84 antennas, depending on their dimensions.

This expands the possibilities for NFC applications in parallelized systems such as game boards, shelf-sorting tables or general sorting boards.

AN6121 - Rev 2 page 19/24

## **Revision history**

Table 3. Document revision history

| Date        | Version | Changes                          |

|-------------|---------|----------------------------------|

| 19-Sep-2025 | 1       | Initial release.                 |

| 03-Nov-2025 | 2       | Updated: • Section 6: Schematics |

AN6121 - Rev 2 page 20/24

## **Contents**

| 1   | Acr     | onyms                                    |    |

|-----|---------|------------------------------------------|----|

| 2   | Cur     | rent working status                      |    |

| 3   | Soli    | ution with more antennas                 | 5  |

| 4   | The     | basic solution of the switching sequence | 6  |

| 5   |         | pedance grounding during off state       |    |

| 6   | Sch     | nematics                                 | g  |

|     | 6.1     | PCB design                               |    |

| 7   | Tes     | ts                                       | 15 |

|     | 7.1     | Signal quality                           |    |

|     | 7.2     | Antenna matching                         |    |

|     | 7.3     | Card reading                             |    |

| 8   | Cor     | nclusion                                 | 19 |

| Rev | /ision  | n history                                | 20 |

|     |         | ables                                    |    |

| Lis | t of fi | aures                                    | 23 |

## **List of tables**

| Table 1. | Applicable products       |

|----------|---------------------------|

| Table 2. | List of acronyms          |

|          | Document revision history |

AN6121 - Rev 2 page 22/24

# **List of figures**

| Figure 1.  | Block diagram of an NFC reader                           | . 3 |

|------------|----------------------------------------------------------|-----|

| Figure 2.  | System diagram (single antenna driving)                  | . 4 |

| Figure 3.  | Block diagram of an NFC reader with multiplexed antennas | . 5 |

| Figure 4.  | Switching block of one antenna in the multiplexer        | . 6 |

| Figure 5.  | Schematic of a multiplexer in single ended mode          | . 7 |

| Figure 6.  | Parasitic components                                     | . 8 |

| Figure 7.  | Single switching module                                  | . 9 |

| Figure 8.  | 6-antenna multiplexer                                    | 10  |

| Figure 9.  | PCB design for a 6-antenna multiplexer                   | 11  |

| Figure 10. | 3D view of the board                                     | 12  |

| Figure 11. | PCB bottom view                                          | 13  |

| Figure 12. | Top view of the machined PCB                             | 14  |

| Figure 13. | Continuous polling signal                                | 15  |

| Figure 14. | Antenna with the switching block                         | 16  |

| Figure 15. | Setup for the sequential card reading test               | 17  |

| Figure 16. | Reading cards on discovery graphical user interface      | 17  |

| Figure 17. | Lights on indicate the active module                     | 18  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

AN6121 - Rev 2 page 24/24