# SRK1004A/B/C/D/E/F synchronous rectification controller for non-complementary Active Clamp Flyback converters evaluation board

#### Introduction

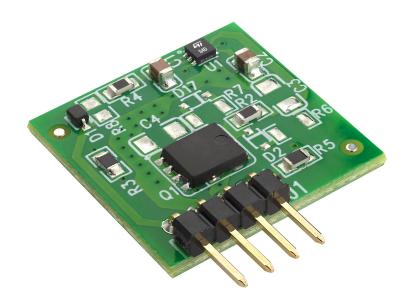

The EVLSRK1004A, EVLSRK1004B, EVLSRK1004C, EVLSRK1004D, EVLSRK1004E and EVLSRK1004F in Figure 1 are evaluation boards, designed for the evaluation of the SRK1004 synchronous rectification controller.

The first part of this application note describes the features of the IC along with some applicative information.

The evaluation board schematics are then described and suggestions are provided on how to connect to an existing flyback converter.

The document concludes with a discussion on thermal and layout optimization principles.

The board codes and descriptions are provided in Table 1.

Figure 1. EVLSRK1004-SR controller demonstration board

**Table 1. Product summary**

| Board       | MOSFET        |         |        |             | Controller |         |                          |

|-------------|---------------|---------|--------|-------------|------------|---------|--------------------------|

| Pn          | Pn            | VDS [V] | ID [A] | Rds,on [mΩ] | Pn         | vcc [v] | Typ. turn-off delay [ns] |

| EVLSRK1004A | BSC080N12LS-G | 120     | 99     | 9.5 @4.5V   | SRK1004A   | 5.5     | 25                       |

| EVLSRK1004B | BSC034N10LS5  | 100     | 156    | 4.5 @4.5V   | SRK1004B   | 5.5     | 150                      |

| EVLSRK1004C | BSC093N15NS5  | 150     | 87     | 9.3 @10V    | SRK1004C   | 9       | 25                       |

| EVLSRK1004D | STL120N10F8   | 100     | 125    | 4.6 @10V    | SRK1004D   | 9       | 150                      |

| EVLSRK1004E | BSC080N12LS-G | 120     | 99     | 9.5@4.5V    | SRK1004E   | 5.5     | 25                       |

| EVLSRK1004F | BSC093N15NS5  | 150     | 87     | 9.3@10V     | SRK1004F   | 9       | 25                       |

AN6183 - Rev 2 page 2/30

#### Operating principle of the SRK1004

#### 1.1 Application connection

The SRK1004 is a family of controllers intended for secondary-side synchronous rectification (SR) in both Non-Complementary Actively Clamped Flyback converters and Quasi Resonant Flyback converters. The six different variants of this IC provide a gate-drive output voltage suitable for N-channel logic-level or standard level power MOSFETs.

The control scheme of this IC is such that the SR MOSFET is switched on as soon as current starts flowing through its body diode and it is then switched off as current approaches zero.

The SRK1004 is supplied by the voltage present at the VCC pin: such voltage is obtained by an internal low dropout regulator connected to the VO voltage, that must be lower than 36 V. When VO is lower than the VCC regulation setpoint, VCC approximates VO. The VO pin embeds UVLO protection to prevent the SR MOSFET being driven by insufficient driving voltage.

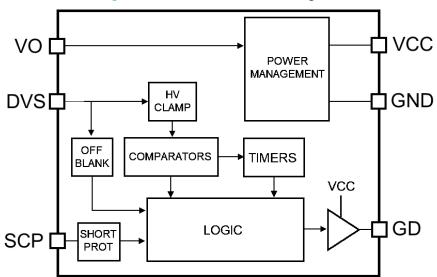

Figure 2. SRK1004 internal block diagram

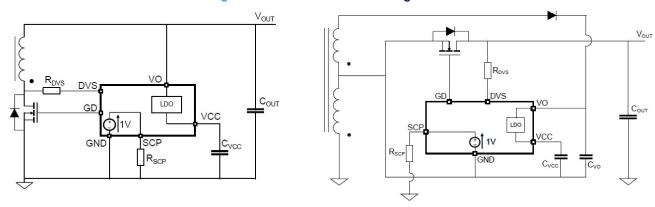

The SRK1004 can be used with the SR MOSFET placed either between the secondary-side GND and transformer (low-side configuration - Figure 3 - *left*) or between the transformer and output voltage (high-side configuration - Figure 3 - *right*).

Figure 3. SRK1004 connection diagrams

Low-side configuration

High-side configuration

AN6183 - Rev 2 page 3/30

In case of low-side configuration of the SR MOSFET, the VO pin of the IC can be supplied by the output voltage bus, while the ground (GND) pin must be connected to secondary-side GND together with the source terminal of the SR MOSFET.

In case of high-side configuration, the source terminal of the SR MOSFET and the ground of the IC are connected to the swinging node of the secondary winding, while VO is typically supplied by an auxiliary winding with a rectifier diode and a buffer capacitor connected, as shown in Figure 3 *right-hand side*.

When operated in high-side configuration, a dedicated short-circuit protection (SCP) function enables a quick detection of short-circuit conditions to inhibit its operation as if the IC were powered directly from the output voltage.

#### 1.2 Control algorithm

The SRK1004 control algorithm operates by sensing the drain-to-source voltage  $V_{DS\_SR}$  of the SR MOSFET using the DVS pin: this is a high-voltage pin and needs to be properly routed to the MOSFET drain through a resistor (220  $\Omega$  - 0805 size to withstand surge currents occurring during transient conditions). The signal captured by DVS is applied to a comparator that, using a set of thresholds, triggers turn-on and turn-off of the SR switch, while internal timers TON-ENW mask undesired SR switch activations as described in detail in the SRK1004 datasheet.

Flyback converters are operated either close to the boundary between Continuous Conduction Mode (CCM) and Discontinuous Conduction Mode (DCM) or in Transition Mode (TM).

Burst mode is generally used at very light or no load to optimize efficiency in those conditions and minimize standby consumption.

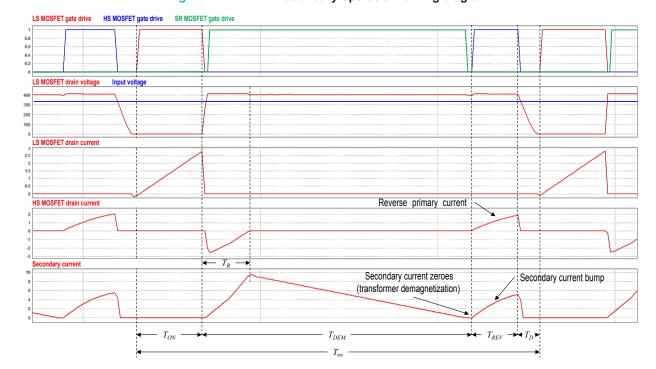

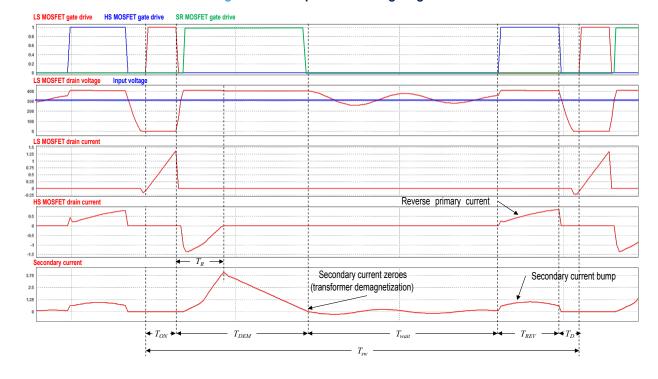

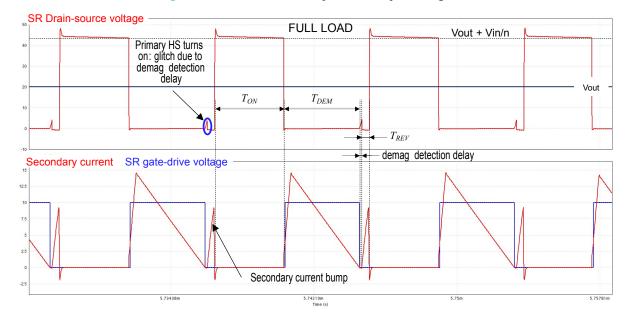

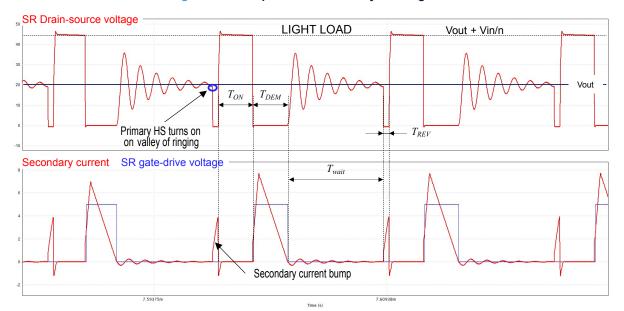

The NC-ACF converter exhibits a specific behavior during demagnetization time: as shown in the timing diagrams of Figure 4 and Figure 5, during the off phase of the main primary switch two or three temporal windows can be observed: the transformer de-magnetization time (TDEM), an idle time (Twait, Figure 5 only), with no current at both primary and secondary, proper DCM operation, and the reverse current build-up time (TREV). QR flyback algorithm does not generate TREV.

Figure 4. CCM-DCM boundary operation: timing diagram

AN6183 - Rev 2 page 4/30

Figure 5. DCM operation: timing diagram

TDEM, the transformer de-magnetization time begins at low-side MOSFET turn-off, and ends when the secondary current reaches zero, or in other words, when transformer complete de-magnetization occurs.

In the first part of TDEM, the energy stored in the magnetizing inductance is released to the secondary, while the energy stored in the leakage inductance is delivered to the clamp capacitor. So, on the one hand, the secondary current builds up, reaching the peak when the primary current is zeroed, and, on the other hand, the drain voltage of the low-side MOSFET is clamped.

In the second part of TDEM, the secondary current linearly decays from peak to zero, that is, the transformer is de-magnetized, while the energy that was in the leakage inductance is maintained into the clamp capacitor.

At the end of TDEM QR flyback and ACF flyabcks behaves differently.

While the QR flyback controller turns on the main switch on the bottom of self resonant oscillation, the NC-ACF controller turns on the high side switch of the primary side half bridge for a proper time to generate ZVS conditions.

At heavy loads, the converter works at CCM-DCM boundary, TDEM, and TREV (that is null in QR flybacks) are contiguous and the high-side MOSFET is turned on right after the transformer de-magnetization (Figure 4), and the idle time (Twait) is zero.

As the load is reduced, the converter starts operating in DCM: the idle time (Twait) appears between TDEM and TREV, getting longer and longer as the load becomes smaller and smaller (Figure 5). In this DCM condition, the high-side primary switch is turned on either in correspondence with a peak of the low-side MOSFET drain voltage ringing, when the ringing is detectable, or after a certain time-out, when the drain ringing is no longer detectable.

In both cases, CCM-DCM boundary and DCM operations, during TREV the primary current and the secondary current flow contemporarily in a forward mode fashion: at primary, this current creates the conditions to obtain ZVS, while, at secondary, it represents an additional energy delivered to the output in the form of a "current bump". The current bump during TREV has typically a low amplitude and duration. For this reason, the synchronous rectifier (SR) MOSFET should be on during the first conduction interval only (TDEM), and must be off during TREV to avoid extra power losses.

The control algorithm implemented in the SRK1004 is able to distinguish the two secondary conduction phases. The NC-ACF controller operation is shown in the following (Figure 6) and (Figure 7), for CCM-DCM boundary and DCM operations respectively.

AN6183 - Rev 2 page 5/30

Figure 6. CCM-DCM boundary: secondary-side signals

AN6183 - Rev 2 page 6/30

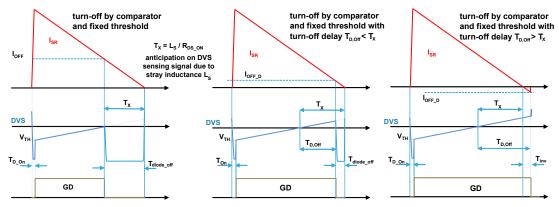

#### 1.3 SR MOSFET stray inductance compensation

The SRK1004 is able to compensate for the misdetection of secondary-side current due to the parasitic inductance of the drain terminal of the SR MOSFET. If not compensated, this parasitic causes an earlier detection of the zero-crossing of the DVS voltage signal than the actual zero-crossing of the rectified current and the time lead is given by the ratio:

$$TX = \frac{Ls}{R_{DS,om}} \tag{1}$$

Where Ls is the parasitic inductance (stray inductance) and R<sub>DS ON</sub> is the on-resistance of the SR switch.

The consequence is a premature turn-off, as shown in Figure 7, that means a larger residual diode conduction time, that is, an efficiency degradation.

Considering a current slope of  $\frac{di}{dt}$ , this residual current ( $I_{OFF}$ ) is given by:

$$I_{OFF} = -T_X \cdot \frac{di}{dt} \tag{2}$$

Including the internal turn-off delay of a real comparator ( $T_{D,off}$ ). The  $I_{OFF}$  current can be better estimated as:

$$I_{OFF\_D} = -(T_X - T_{D,off}) \cdot \frac{di}{dt}$$

(3)

If  $T_X > T_{D,off}$  (as shown in Figure 8, in the center) the zero-crossing on the voltage signal occurs in advance with respect to the zero-crossing of the rectified current and a residual diode conduction time is still present even if much better than an ideal comparator case.

If  $T_X < T_{D,off}$  (as shown in Figure 8, on the right) the MOSFET turn-off occurs after the zero voltage crossing, causing a current inversion that could be dangerous at high current value.

This shows that by properly tuning this propagation delay a perfect match between the zero-crossing of DVS voltage and SR current can be theoretically obtained.

Figure 8. Comparison between comparator turn-off and comparator with extra turn-off delay

To optimize the application, the SRK1004 is provided with different values of extra turn-off delay to avoid a large current flowing into the body diode MOSFET.

Typical extra turn-off delays are as highlighted in Table 2.

Table 2. SRK1004 - internal extra turn-off delay

|             | Typ. extra turn-off delay [ns] | Typ. Turn on enable window [ns] |

|-------------|--------------------------------|---------------------------------|

| SRK1004A, C | 25                             | 125                             |

| SRK1004B, D | 150                            | 125                             |

| SRK1004E, F | 25                             | 215                             |

AN6183 - Rev 2 page 7/30

#### 1.4 Short-circuit protection – SCP

When the SRK1004 is configured to operate in the low-side configuration (that is, VO =  $V_{OUT}$  - Figure 3 – *left-hand side*) in case of short-circuit on the converter's output, as the VO voltage falls below the UVLO threshold (VOOff), the SRK1004 shuts down and stops driving the SR MOSFET. Secondary current conduction through the body diode of the SR MOSFET ensures that, on the primary-side, the ACF controller is still able to correctly detect transformer demagnetization and ensure proper operation of the converter during a short-circuit. The SCP pin, in this configuration, must be connected to GND using a 22 k $\Omega$  resistor to disable the short-circuit detection mechanism that is dedicated to high-side configuration.

When the SRK1004 is configured to operate in the high-side configuration (Figure 3 – *right-hand side*), in case of short-circuit on the converter's output, V<sub>OUT</sub> drops quickly because of the short-circuit impedance, whereas VO decays in a longer time, defined by VCC capacitance and the IC consumption. UVLO protection might not be triggered and the SRK1004 must be stopped by short-circuit protection to prevent operation under a short-circuit condition causing power components to overstress and primary-side controller malfunctioning.

Short-circuit protection is active during demagnetization only and can be configured connecting a resistor (RSCP) between the SCP pin and secondary-side ground. The SCP pin provides a reference voltage VSCP = 1 V, while an internal current comparator triggers SCP if pin source current falls below the ISCP\_TH threshold (20  $\mu$ A). When SCP is triggered, a short-circuit condition is assumed and the SRK1004 turns off the SR MOSFET until the SRK1004 is shut down by VO falling below the UVLO threshold.

The output short-circuit voltage level (VOUT<sub>SC</sub>) can be adjusted selecting RSCP as follows:

$$R_{SCP} = \frac{V_{OUT_{SC}} + 1}{I_{SCP\_TH}} \tag{4}$$

During the primary conduction phase, the SCP pin is clamped to a maximum voltage of 2 V.

AN6183 - Rev 2 page 8/30

#### 2 Evaluation board description

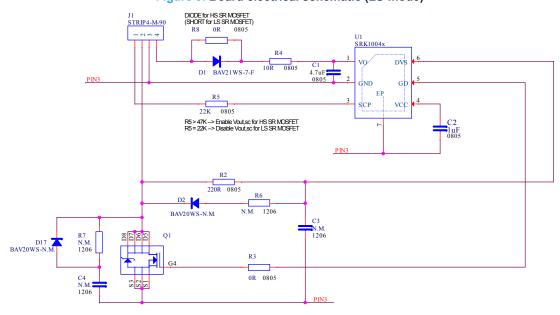

The board is shipped with low-side configuration enabled as per the schematic shown in Figure 9.

Different board variants, equipped by different SRK1004 variants, are listed in Table 1.

The SR MOSFET of the different boards has been selected according to the controller used: logic or standard level and appropriate anticipation.

The breakdown voltages are in the 100 ÷ 150 V range in order to manage applications with output voltages from 5 V to 20 V. This voltage range can also be directly used to supply the SRK1004 VO pin.

Figure 9. Board electrical schematic (LS-mode)

SRK1004 supply voltage, VO, is provided by R8 directly connected to application output voltage. C1 and C2 are the recommended bulk capacitors for SRK1004 supply voltages.

The GND pin and exposed pad are the connection of the IC reference potential: bulk capacitors of supply voltages and SR MOSFET source are then connected to pin3 of J1.

The gate driver (GD) and MOSFET gate terminal are directly connected, but R3 can be substituted by a higher value resistor if needed.

DVS pin current is limited by 220  $\Omega$ , 0805, SMD resistor. Considering a worst case with dDVS/dt = 5 V/ns, DVS,max = 150 V, dVout/dt = 1.5 V/300 $\mu$ s = 5 V/ms, from device simulations a resistor R1 = 220  $\Omega$  in series to the DVS pin is required to limit dynamic current injections.

C3 is a spare footprint that can be used if the target application shows excessive dV/dt resulting in excessive dynamic current into the DVS pin.

The board layout offers some spare footprints, namely R7, C4, and D17, to place an additional snubber to mitigate EMI effects if needed (to be evaluated, case by case, on target applications).

SCP protection is inhibited on the board in LS mode, R5 is set to  $22k\Omega$  to prevent undesired SCP comparator trigger: UVLO protection of VO pin will serve as short circuit protection.

If the target application requires high-side configuration, very few changes need to be implemented. In particular:

R5 must be modified by according to equation in Section 1.4: Short-circuit protection – SCP. As a sake of example, considering VOUT<sub>SC</sub> = 3V:

$$R_5 = \frac{V_{OUT_{SC}} + 1}{I_{SCP\_TH}} = 200 \text{k}\Omega \tag{5}$$

R8 must be removed and SRK1004 supply voltage, VO, is provided by auxiliary winding: D1 is used to block negative voltages while R4 limits inrush currents. Hold up time guaranteed by the values provided with the board can be estimated as:

AN6183 - Rev 2 page 9/30

$$T_{res} \approx \frac{C_1 \cdot (V_O - V_{O,OFF,max})}{I_{q,max}} \tag{6}$$

As an example, if nominal VO equals 5V and C1 is  $4.7\mu F$  the holdup time is approximately equal to:

$$T_{res} \approx \frac{4.7 \mu \text{F} \cdot (5\text{V} - 4.12\text{V})}{290 \mu \text{A}} = 14 ms$$

(7)

The bill of material of the four EVLSRK1004x boards (Table 3) are identical, differing only in the MOSFET and SRK1004x part number.

Table 3. EVLSRK1004x - bill of material

| Reference | Value                                                                               | Description                                                                                                                                               | Package     | Manufacturer                                  | Part number                                                  |

|-----------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------|--------------------------------------------------------------|

| C1        | 4.7uF                                                                               | 50V CERCAP X7R - General purpose                                                                                                                          | 0805        | TDK                                           | C2012X7R1H475K125AC                                          |

| C2        | 1uF                                                                                 | 25V CERCAP - X7R - 10%                                                                                                                                    | 0805        |                                               |                                                              |

| C3        | N.M.                                                                                | 500V CERCAP - X7R - 10%                                                                                                                                   |             |                                               |                                                              |

| C4        | N.M.                                                                                | 500V CERCAP - X7R - 10%                                                                                                                                   |             |                                               |                                                              |

| D1        | BAV21WS-7-F                                                                         | SMD Schottky rectifier                                                                                                                                    | SOD-323     | Diodes Incorporated                           | BAV21WS-7-F                                                  |

| D2        | BAV20WS-N.M.                                                                        | Small signal switching diode                                                                                                                              |             |                                               |                                                              |

| D17       | BAV20WS-N.M.                                                                        | Small signal switching diode                                                                                                                              |             |                                               |                                                              |

| J1        | STRIP4-M-90                                                                         | 4 pins strip, right angle, male                                                                                                                           |             | WURTH                                         | 61304011021                                                  |

| Q1        | BSC080N12LS-G<br>(A,E)<br>BSC034N10LS5 (B)<br>BSC093N15NS5 (C,F)<br>STL120N10F8 (D) | N-Channel power MOSFET 120 V<br>12A<br>N-Channel power MOSFET 100V<br>19A/100A<br>N-Channel power MOSFET 100 V<br>125A<br>N-Channel power MOSFET 150V 87A | 8-PowerTDFN | Infineon Infineon Infineon STMicroelectronics | BSC080N12LS-G<br>BSC034N10LS5<br>BSC093N15NS5<br>STL120N10F8 |

| R2        | 220R                                                                                | SMD standard film RES - 1/8W -5% - 250ppm/°C                                                                                                              | 0805        |                                               |                                                              |

| R3        | 0R                                                                                  | SMD standard film RES - 1/8W -5% - 250ppm/°C                                                                                                              | 0805        |                                               |                                                              |

| R4        | 10R                                                                                 | SMD standard film RES - 1/8W -5% - 250ppm/°C                                                                                                              | 0805        |                                               |                                                              |

| R5        | 22K                                                                                 | SMD standard film RES - 1/8W -5% - 250ppm/°C                                                                                                              | 0805        |                                               |                                                              |

| R6        | N.M.                                                                                | SMD standard film RES - 1/8W -5% - 250ppm/°C                                                                                                              |             |                                               |                                                              |

| R7        | N.M.                                                                                | SMD standard film RES - 1/8W -5% - 250ppm/°C                                                                                                              |             |                                               |                                                              |

| R8        | 0R                                                                                  | SMD standard film RES - 1/8W -5% - 250ppm/°C                                                                                                              | 0805        |                                               |                                                              |

| U1        | SRK1004A/B/C/D/E/F                                                                  | SRK1004A/B/C/D/E/F - VFDFPN 6L<br>2x2 pitch 0.65                                                                                                          | 6DFN_2X2    | STMicroelectronics                            | SRK1004A/B/C/D/E/F                                           |

AN6183 - Rev 2 page 10/30

## 3 How to connect the board to the application

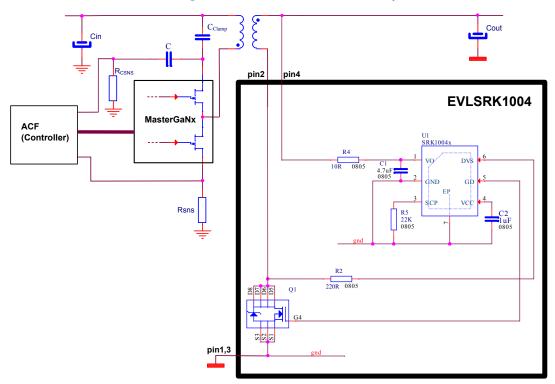

The evaluation board is intended to implement synchronous rectification in an existing flyback converter in the low-side configuration as indicated in Figure 10.

Pin connection must be set as follows:

- Pin 1 to the secondary ground.

- Pin 2 to the transformer negative (flying) terminal.

- Pin 3 to the secondary ground.

- Pin 4 to output voltage.

Figure 10. Low-side connection example

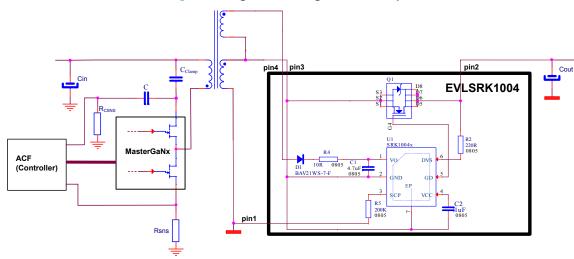

The evaluation board can also be used configured to operate in high-side configuration as indicated in Figure 11. In this case, referring to connector J1 in the board schematic, different pins have to be connected as follows:

- Pin 1 to the secondary ground.

- Pin 2 to the output voltage.

- Pin 3 to the transformer positive (flying) terminal.

- Pin 4 to auxiliary winding.

In the depicted example, R5 value is modified to 200 k $\Omega$  to set short circuit  $V_{out}$  level to ~3V.

AN6183 - Rev 2 page 11/30

Figure 11. High-side configuration example

AN6183 - Rev 2 page 12/30

### 4 Supply SRK1004

The SRK1004 controller is supplied by the voltage applied to V<sub>o</sub> pin.

When it is used to drive a rectification mosfet in low side configuration, the  $V_0$  and GND pins can be connected respectively to output voltage and Output common potential. A 10  $\Omega$  0805 SMD decoupling resistor in series with  $V_0$  and a 100 nF MLCC capacitor is suggested to obtain a cleaner supply voltage.

R<sub>VO</sub> are optional

OUT

R<sub>VO</sub> are optional

C OUT

C OUT

C OUT

Figure 12. SRK1004 supply in low-side configuration

When it is used to drive a rectification mosfet in high side configuration, two configurations are possible. An auxiliary winding having the same polarity of secondary side winding and referred to SR mosfet's source can be used to obtain a floating supply voltage. A properly selected diode connected between auxiliary winding positive terminal and  $V_o$  and 1uF MLCC capacitor between  $V_o$  and GND pin of SRK are mandatory for a proper operation (see Figure 13).

R DVS

R VO

C OUT

C OUT

C VCC

C VCC

C VCC

Figure 13. SRK1004 standard supply in high-side configuration

AN6183 - Rev 2 page 13/30

Eventually the transformer has no room for secondary side auxiliary winding, the alternate arrangement depicted in Figure 14 can be used. The adoption of a Depletion mosfet in place of standard bipolar transistor is useful to minimize the effect of the reference (Zener) biasing current.

R DVS

O D V S

O D V S

O C VCC

C V

Figure 14. SRK1004 alternate supply in high-side configuration

The diode voltage rating equals  $V_{outmax} + V_{inpkmax}/N$ , where N is the transformer primary to secondary side turn ratio,  $V_{outmax}$  is the maximum value of output voltage and  $V_{inpkmax}$  is the absolute maximum value of input voltage.

The MOSFET drain to source rating equals  $V_{inpkmax}/N$  and must cope with a power dissipation approximately equals to  $V_{inpkmax}/N$  times SRK1004 switching current consumption.

AN6183 - Rev 2 page 14/30

#### 5 Bench evaluation

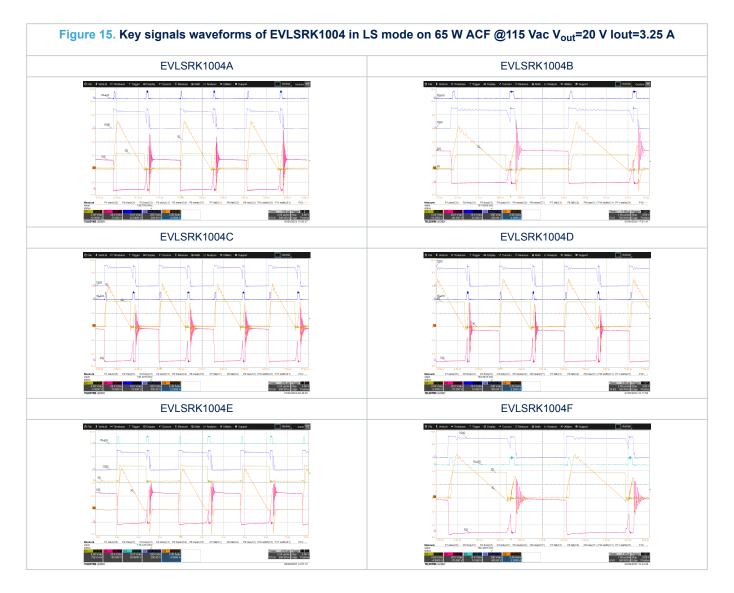

The board has been tested on a 65 W 20-5 V ACF converter. The following assertions refer to EVLSRK1004A/B/C/D/E/F.

Note that current and voltage probes can affect the IC sensing, leading to malfunctioning.

Signal probing must be accomplished carefully and with minimal modification with respect to the original circuit.

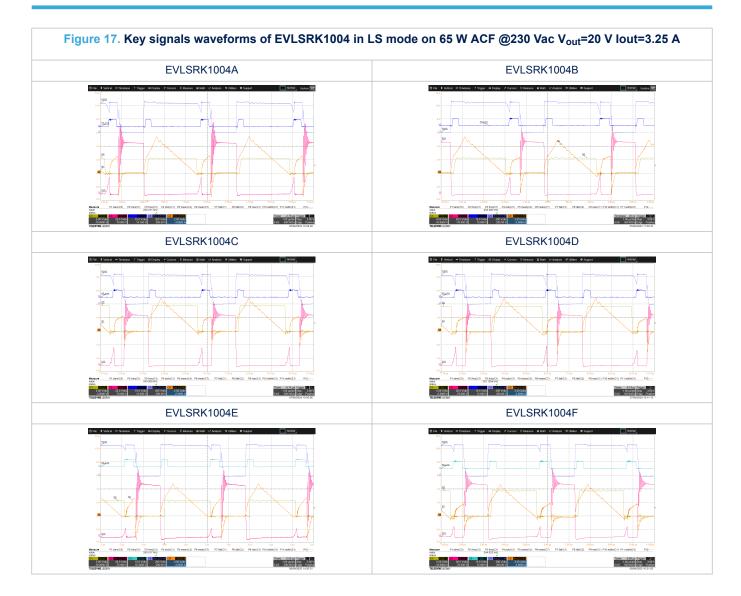

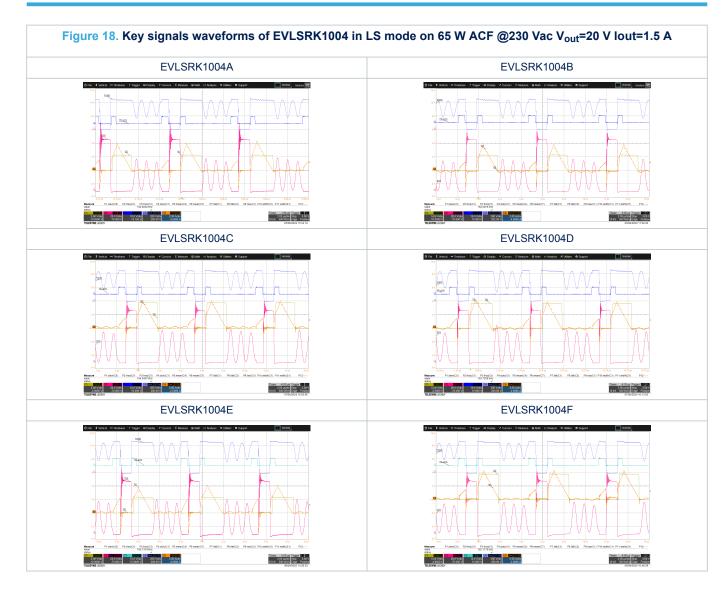

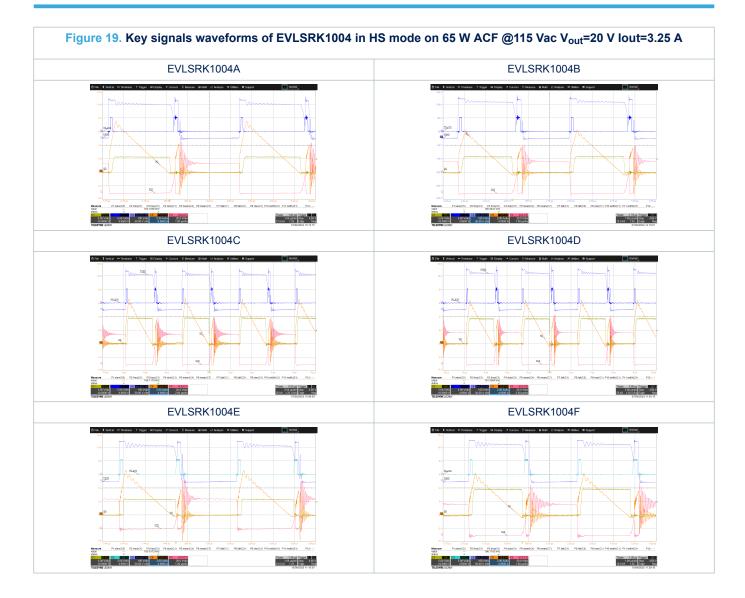

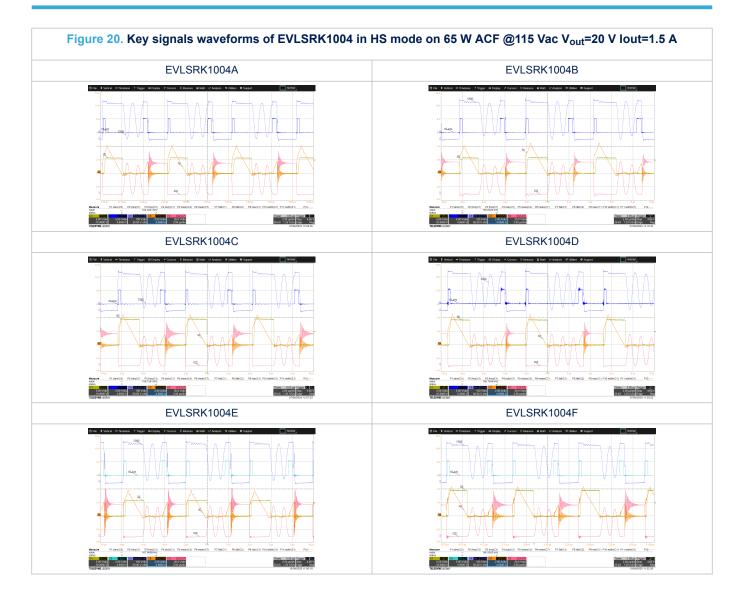

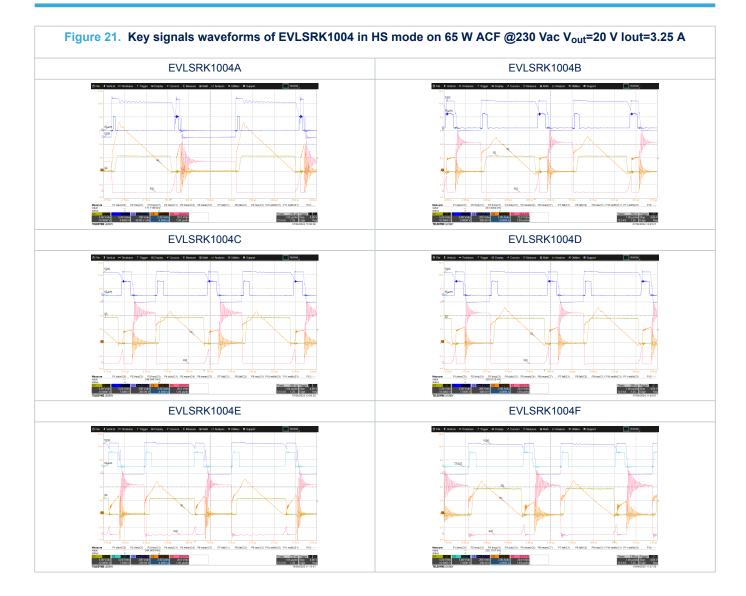

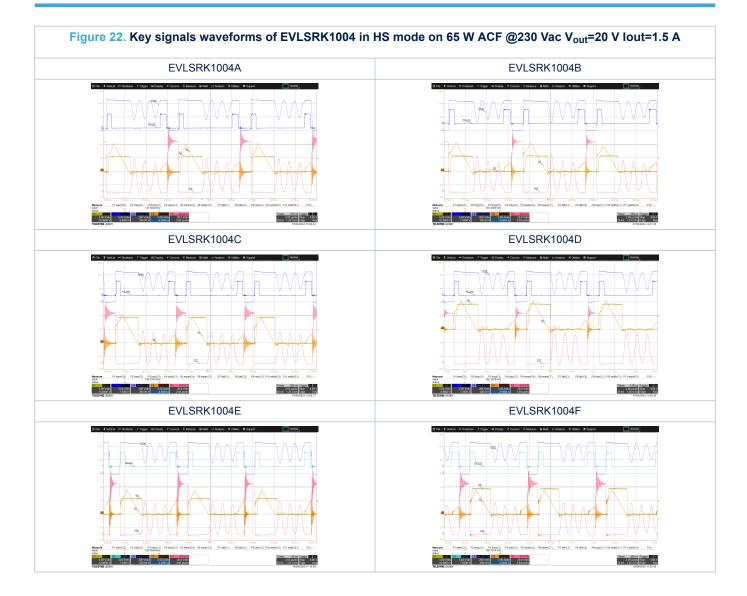

In the figures below, the key signals of the SRK1004 are shown: SRK gate driver (GD), SRK drain voltage sensing (DVS). Other signals shown are SR power MOSFET current (Iq1) and primary-side voltages floating ground (FGND) and high-side driver (HS\_prim).

The MOSFET is switched on and off according to its drain-source voltage.

AN6183 - Rev 2 page 15/30

The MOSFET remains on while the secondary current is flowing through the load (energy is transferred from primary to secondary-side) and turns off (due to DVS crossing the 0 V threshold) when the current is around 0 A. Note that similar behavior is shown between EVLSRK1004C and EVLSRK1004D. This means that the SRK1004x chosen has turn-off delay adequate to compensate MOSFET anticipation TX =  $\frac{Ls}{R_{DS,on}}$

In addition, these results show that Ls = 3nH based on simulation model are not verified on test bench since turn-off delay 150 ns is enough to compensate the anticipation on DVS.

Similar results are shown @230 Vac as shown below:

AN6183 - Rev 2 page 16/30

AN6183 - Rev 2 page 17/30

Similar results are shown using EVLSRK1004x in a high-side configuration.

The next image shows a comparison at @high/low input line and full load.

AN6183 - Rev 2 page 18/30

AN6183 - Rev 2 page 19/30

AN6183 - Rev 2 page 20/30

AN6183 - Rev 2 page 21/30

AN6183 - Rev 2 page 22/30

#### 6 Thermal consideration

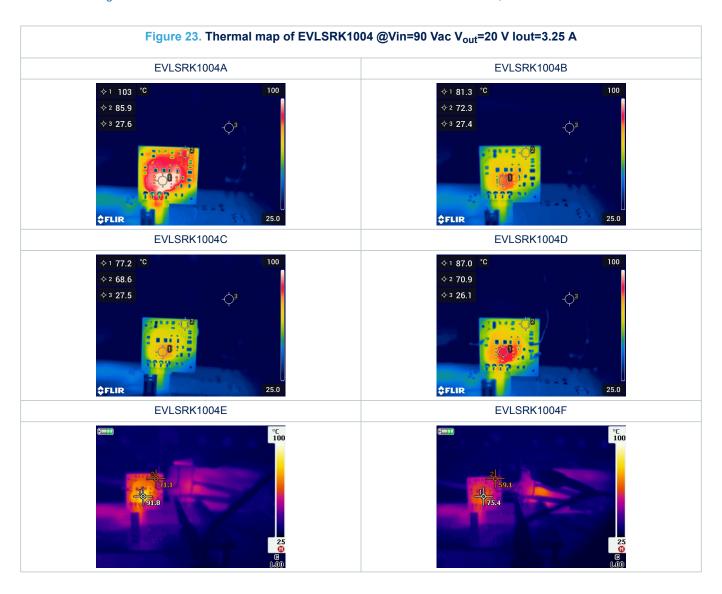

The thermal emissions of SRK1004 boards are shown in Figure 23 and Table 4.

Some markers visible on the images have been placed across key components (SR MOSFET and SRK1004, respectively marked as M1 and M2).

The ambient temperature during both measurements was 27 °C.

Figure 23 shows the thermal behavior at Vin=90 Vac Vout=20 V lout=3.25 A, 20 minutes after board turn-on.

Table 4. Temp. [°C] measured on EVLSRK1004x

|         | EVLSRK1004A | EVLSRK1004B | EVLSRK1004C | EVLSRK1004D | EVLSRK1004E | EVLSRK1004F |

|---------|-------------|-------------|-------------|-------------|-------------|-------------|

| MOSFET  | 103°        | 81.3°       | 77.2°       | 87.0°       | 91.8°       | 75.4°       |

| SRK1004 | 85.9°       | 72.3°       | 68.6°       | 70.9°       | 71.1°       | 59.1°       |

If a current greater than 3.25 A is used in the application, it is recommended to use a fan or MOSFET heat sink.

AN6183 - Rev 2 page 23/30

## 7 Layout suggestions

The GND pin is the return of the bias current of the device and the return for gate-drive current. It should be routed in the shortest way possible.

The usage of bypass capacitors between the VCC pin and GND pin is recommended.

They should be low-ESR, low-ESL type and located as close to the IC pins as possible.

The following recommendations should be considered when designing the PCB:

- Use a bypass capacitor across VCC and GND as close to the device pins as possible.

- Reduce the driving current path length and area as much as possible:

- — Minimize the area of circuit done by the GD pin, SR MOSFET, and DVS pin

- Short trace from DRAIN of SR MOSFET to DVS pin

- The DVS connection to the SR MOSFET drain terminal is critical (for stray inductances in the SR MOSFET current path). It is preferable to sense the MOSFET voltage as close as possible to its drain terminal.

- Exposed pad: connect to GND pin/net.

- Connect the device GND pin as close as possible to the SR MOSFET source terminal.

MOTTOB

22.00mm

22.00mm

Control of the second sec

Table 5. Board layout

AN6183 - Rev 2 page 24/30

## 8 References

1. SRK1004 datasheet: available at SRK1004

AN6183 - Rev 2 page 25/30

## **Revision history**

Table 6. Document revision history

| Date        | Version | Changes                                       |

|-------------|---------|-----------------------------------------------|

| 11-Dec-2024 | 1       | Initial release.                              |

| 29-Sep-2025 | 2       | EVLSRK1004E and EVLSRK1004F description added |

AN6183 - Rev 2 page 26/30

## **Contents**

| Ope | erating principle of the SRK1004          | 3                     |

|-----|-------------------------------------------|-----------------------|

| 1.1 | Application connection                    | 3                     |

| 1.2 | Control algorithm                         | 4                     |

| 1.3 | SR MOSFET stray inductance compensation   | 7                     |

| 1.4 | Short-circuit protection – SCP            | 8                     |

| Eva | aluation board description                |                       |

| Hov | w to connect the board to the application |                       |

| Sup | oply SRK1004                              |                       |

|     |                                           |                       |

| The | ermal consideration                       | 23                    |

| Lay | out suggestions                           | 24                    |

| •   |                                           |                       |

|     |                                           |                       |

|     |                                           |                       |

|     |                                           |                       |

|     | 1.1 1.2 1.3 1.4 Eva Hov Sup Ber Lay Ref   | 1.2 Control algorithm |

## **List of tables**

| Table 1. | Product summary                         | . 2 |

|----------|-----------------------------------------|-----|

| Table 2. | SRK1004 - internal extra turn-off delay | . 7 |

| Table 3. | EVLSRK1004x - bill of material          | 10  |

| Table 4. | Temp. [°C] measured on EVLSRK1004x      | 23  |

| Table 5. | Board layout                            | 24  |

| Table 6. | Document revision history               | 26  |

AN6183 - Rev 2 page 28/30

## **List of figures**

| Figure 1.  | EVLSRK1004–SR controller demonstration board                                                           | . 1 |

|------------|--------------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | SRK1004 internal block diagram                                                                         | . 3 |

| Figure 3.  | SRK1004 connection diagrams                                                                            | . 3 |

| Figure 4.  | CCM-DCM boundary operation: timing diagram                                                             | . 4 |

| Figure 5.  | DCM operation: timing diagram                                                                          | . 5 |

| Figure 6.  | CCM-DCM boundary: secondary-side signals                                                               | . 6 |

| Figure 7.  | DCM operation: secondary-side signals                                                                  |     |

| Figure 8.  | Comparison between comparator turn-off and comparator with extra turn-off delay                        | . 7 |

| Figure 9.  | Board electrical schematic (LS-mode)                                                                   | . 9 |

| Figure 10. | Low-side connection example                                                                            | 11  |

| Figure 11. | High-side configuration example                                                                        | 12  |

| Figure 12. | SRK1004 supply in low-side configuration                                                               | 13  |

| Figure 13. | SRK1004 standard supply in high-side configuration                                                     | 13  |

| Figure 14. | SRK1004 alternate supply in high-side configuration                                                    | 14  |

| Figure 15. | Key signals waveforms of EVLSRK1004 in LS mode on 65 W ACF @115 Vac V <sub>out</sub> =20 V lout=3.25 A | 15  |

| Figure 16. | Key signals waveforms of EVLSRK1004 in LS mode on 65 W ACF @115 Vac $V_{out}$ =20 V lout=1.5 A         | 16  |

| Figure 17. | Key signals waveforms of EVLSRK1004 in LS mode on 65 W ACF @230 Vac V <sub>out</sub> =20 V lout=3.25 A | 17  |

| Figure 18. | Key signals waveforms of EVLSRK1004 in LS mode on 65 W ACF @230 Vac V <sub>out</sub> =20 V lout=1.5 A  | 18  |

| Figure 19. | Key signals waveforms of EVLSRK1004 in HS mode on 65 W ACF @115 Vac V <sub>out</sub> =20 V lout=3.25 A | 19  |

| Figure 20. | Key signals waveforms of EVLSRK1004 in HS mode on 65 W ACF @115 Vac V <sub>out</sub> =20 V lout=1.5 A  | 20  |

| Figure 21. | Key signals waveforms of EVLSRK1004 in HS mode on 65 W ACF @230 Vac V <sub>out</sub> =20 V lout=3.25 A | 21  |

| Figure 22. | Key signals waveforms of EVLSRK1004 in HS mode on 65 W ACF @230 Vac V <sub>out</sub> =20 V lout=1.5 A  | 22  |

| Figure 23. | Thermal map of EVLSRK1004 @Vin=90 Vac Vout=20 V lout=3.25 A                                            | 23  |

AN6183 - Rev 2 page 29/30

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

AN6183 - Rev 2 page 30/30