# How to optimize power consumption on STM32U3 MCUs

#### Introduction

The STM32U3 series microcontrollers (MCUs) are based on the high-performance Arm<sup>®</sup> 32-bit Cortex<sup>®</sup>-M33 CPU with Arm<sup>®</sup> TrustZone<sup>®</sup> and FPU. These MCUs use an innovative architecture to reach best-in-class, ultra-low-power figures owing to their high flexibility and advanced set of peripherals. They outperform the competition in the ultra-low-power world by providing the best energy efficiency for applications.

The STM32U3 series are the first STM32 series based on near-threshold voltage technology to deliver breakthrough improvement in battery life. With near-threshold technology, the STM32U3 series devices reduce the active consumption down to  $10 \mu A/MHz$ , resulting in far longer battery life for any application.

With the integration of the ART Accelerator 8-Kbyte instruction cache, the STM32U3 series MCUs can operate at frequencies up to 96 MHz and achieve 144 DMIPS performance, while maintaining extremely low dynamic power consumption and best-in-class low-power modes.

This application note provides qualitative and quantitative information to be able to configure different parameters, such as frequency, range, and low-power mode, before starting the implementation and optimization. All computations are performed with typical data from the product datasheet and at ambient temperature, unless otherwise specified.

This application note uses the industry-standard ULPMark $^{\text{m}}$  benchmark from EEMBC $^{\text{m}}$  as a reference case to correlate the computations and simulations with the measurements.

Note:

# 1 General information

This application note applies to the STM32U3 series microcontrollers that are Arm<sup>®</sup> Cortex<sup>®</sup> core-based devices. *Arm is a registered trademark of Arm limited (or its subsidiaries) in the US and/or elsewhere.*

arm

## **Reference documents**

- [1] STM32U3 series Arm®-based 32-bit MCUs, reference manual (RM0487)

- [2] STM32U375xx datasheet (DS14861)

- [3] STM32U385xx datasheet (DS14830)

- [4] STM32U375xx and STM32U385xx errata (ES0626)

- [5] STM32 microcontroller GPIO configuration for hardware settings and low-power consumption, application note (AN4899)

- [6] EEMBC organization on www.eembc.org

AN6195 - Rev 2 page 2/23

# 2 Energy efficiency processing

The high processing performance in Run mode (expressed in DMIPS/MHz) is achieved by using a Cortex<sup>®</sup>-M33 core associated with the interfaces of its memories. To ensure full performance operation at maximum operating frequency, the STM32U3 series devices embed the ART accelerator instruction cache (ICACHE), which masks the flash memory access wait state. The processing performance can then achieve 1.5 DMIPS/MHz, regardless of the system clock frequency.

The consumption is even lower on STM32U3 series thanks to the adaptive voltage scaling (AVS) technique. The  $V_{CORE}$  is tuned individually on each device to achieve the target frequency of every voltage range and have the lowest consumption at the same time

All consumption data used in this application note are based on typical specifications extracted from documents [2] and [3] at  $T_A = 25$ °C and  $V_{DD} = 3.0$  V, unless otherwise specified.

# 2.1 Internal regulator efficiency

The devices embed two internal regulators, that can be selected when the application runs, depending on the application requirements:

- SMPS step-down converter

- Linear voltage regulator (LDO)

The LDO and SMPS regulators have two modes:

- Main regulator mode (used when performance is needed)

- Low-power regulator mode

Both regulators can be used in all voltage scaling ranges, and can operate in all Stop modes.

Table 1. Power distribution of the internal regulators

| Voltage regulator mode            | Device mode                                                  |

|-----------------------------------|--------------------------------------------------------------|

| Main regulator (Range 1, 2)       | Run, Sleep, Stop 0                                           |

| Low-power regulator (SMPS or LDO) | Stop 1, Stop 2, Stop 3, (Standby with 8-Kbyte or full SRAM2) |

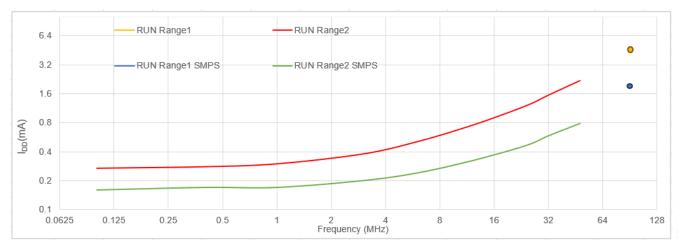

Figure 1 shows the typical current consumption of an STM32U3 series microcontroller in Run mode, as a function of system frequency, for both SMPS and LDO configurations with  $F_{HCLK} = F_{HSE}$  bypass mode, all peripherals disabled, flash memory Bank 2 in power down, and all SRAMs enabled.

Figure 1. Current consumption for STM32U3 in Run mode with ICACHE ON, 1-way, prefetch ON, SMPS versus LDO

DT75679V

AN6195 - Rev 2 page 3/23

Note:

The lowest power consumption is achieved when running from the internal flash memory with cache 1-way. The instruction cache tends to reduce the number of accesses to the memory, thus reducing the overall current consumption. The current consumption from the internal SRAM is similar to the flash memory when the ICACHE is used.

Figure 2 shows the same curve translated into power efficiency by dividing the current consumption ( $\mu A$ ) by the CPU frequency.

800 750 RUN Range2 700 RUN Range1 650 CURRENT EFFICIENCY (UA\MHZ) 600 RUN Range1 SMPS RUN Range2 SMPS 550 500 450 400 350 300 250 200 150 100 50 0 0.0625 0.125 0.25 0.5 1 8 16 32 64 FREQUENCY (MHZ)

Figure 2. Power efficiency for STM32U3 with ICACHE ON, 1-way, prefetch ON, SMPS versus LDO

Note: Enabling the SMPS can improve power efficiency by up to 65%, depending on the system frequency.

# 2.2 Dynamic voltage scaling management

The STM32U3 series devices support dynamic voltage scaling, which is a power management technique that allows the voltage ( $V_{CORE}$ ) and frequency to be dynamically adjusted based on processing requirements to optimize power consumption.

Dynamic voltage scaling to increase  $V_{CORE}$  is known as overvolting. It allows the device to improve its performance. It is performed to save power, particularly in laptops and other mobile devices where the energy comes from a battery and is thus limited.

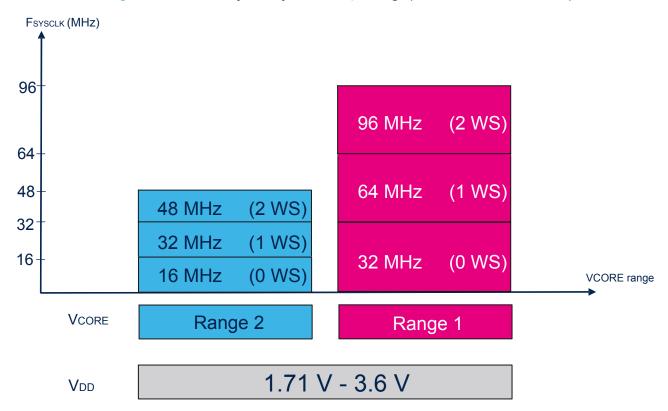

The regulator operates in the following ranges:

- Range 1: high performance. It provides a typical output voltage of 0.9 V. It is used when the system clock frequency is up to 96 MHz.

- Range 2: low-power range. It provides a typical output voltage of 0.75 V. The system clock frequency can be up to 48 MHz.

The EPOD (embedded power distribution) booster of STM32U3 series devices must be turned on for frequencies above 24 MHz in Range 1 and Range 2 (refer to document [1] for sequences to switch between voltage scaling ranges).

| Product voltage range |                       | AHB1/AHB2/APB1/APB2/APB3 |

|-----------------------|-----------------------|--------------------------|

| Range 1               | EPOD booster enabled  | 96 MHz                   |

|                       | EPOD booster disabled | 24 MHz                   |

| Range 2               | EPOD booster enabled  | 48 MHz                   |

|                       | EPOD booster disabled | 24 MHz                   |

Table 2. Bus maximum frequency

Reducing power consumption in Run mode is done by configuring voltage scaling according to application performance needs.

AN6195 - Rev 2 page 4/23

# 2.3 Flash memory and ICACHE efficiency

# 2.3.1 Flash memory efficiency

Figure 3 shows the flash memory latency (number of wait states to be programmed in the flash memory access control register), depending on the STM32U3 series regulator voltage scaling range and system clock frequency.

Figure 3. Flash memory latency versus  $V_{CORE}$  range ( $V_{DD} = 1.71$  to 3.6 V, LPM = 0)

The flash memory supports a low-power read mode (LPM). The number of wait states (WS) depends on the LPM value:

- Up to 2 WS when LPM = 0 (depending on the supply voltage and the frequency)

- Up to 4 WS when LPM = 1 (depending on the supply voltage and the frequency)

Table 3. Current consumption for STM32U3 series in Run mode versus LPM

| Symbol Conditions -  |                                                                                                                      | Current consumption (mA) |         |

|----------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------|---------|

|                      |                                                                                                                      | LPM = 1                  | LPM = 0 |

| I <sub>DD(RUN)</sub> | SMPS, prefetch ON, SecureMark <sup>™</sup> code, V <sub>DD</sub> = 1.8 V, 24 MHz<br>Range 2, FLASH power-down Bank 2 | 0.58                     | 0.61    |

In Range 2, it is particularly beneficial to reduce dynamic consumption by enabling LPM in FLASH\_ACR.

#### 2.3.2 ICACHE efficiency

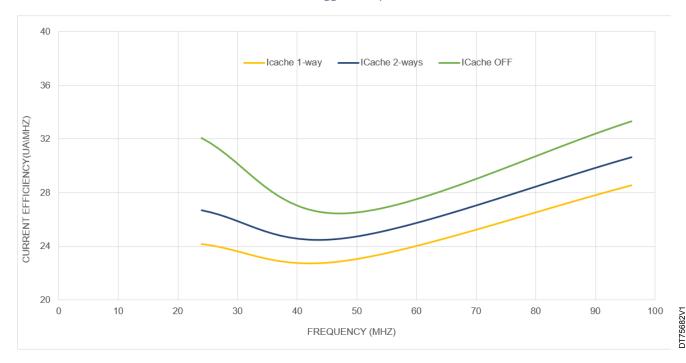

The STM32U3 series devices embed an 8-Kbyte instruction cache (ICACHE) that allows boosted code execution from the internal flash memory or external octo-SPI memories. This cache can be configured in either a 2-way associative mode or a more power-efficient direct-mapped mode.

AN6195 - Rev 2 page 5/23

Table 4. Current consumption for STM32U3 series in Run mode with ICACHE ON (1-way) versus prefetch

SecureMark<sup>™</sup> benchmark with SMPS and  $V_{DD}$  = 1.8 V and FLASH power-down Bank 2.

| Frequency (MHz)  | Current consumption (mA) |              |  |

|------------------|--------------------------|--------------|--|

| Frequency (MITZ) | Prefetch ON              | Prefetch OFF |  |

| 96 (Range 1)     | 2.74                     | 2.73         |  |

| 48 (Range 2)     | 1.1                      | 1.09         |  |

| 24 (Range 2)     | 0.61 (0.58 if LPM = 1)   | 0.61         |  |

Note:

Prefetch tends to increase code execution performance at the cost of extra flash memory accesses, resulting in a moderate rise in current consumption up to 1% when LPM = 0.

Setting the LPM bit at 24 MHz in Range 2 leads to a 5% reduction in power consumption when prefetch is activated and ICACHE is set to 1-way.

Table 5. Current consumption for STM32U3 series in Run mode with prefetch ON versus ICACHE configurations

SecureMark<sup>™</sup> benchmark with SMPS and V<sub>DD</sub> = 1.8 V and FLASH power-down Bank 2.

| Frequency (MHz) | Current consumption (mA) |                   |            |  |

|-----------------|--------------------------|-------------------|------------|--|

| Frequency (MHZ) | ICACHE ON (1-way)        | ICACHE ON (2-way) | ICACHE OFF |  |

| 96 (Range 1)    | 2.74                     | 2.94              | 3.2        |  |

| 48 (Range 2)    | 1.1                      | 1.18              | 1.27       |  |

| 24 (Range 2)    | 0.61 (0.58 if LPM = 1)   | 0.64              | 0.77       |  |

Note:

Configuring the ICACHE in 1-way mode can save up to 10% energy compared to the 2-way mode, and up to 26% compared to when the ICACHE is turned off.

The 1-way ICACHE configuration provides lower performance and consumes less power than the 2-way configuration, but it is more efficient.

AN6195 - Rev 2 page 6/23

Figure 4 shows the power efficiency of an STM32U3 series microcontroller in Run mode on a SecureMark<sup>TM</sup> for benchmark for different ICACHE configurations, as a function of system frequency, with SMPS and  $V_{DD} = 1.8 \text{ V}$ .

Figure 4. Power efficiency for various ICACHE configurations (SecureMark<sup>™</sup>, SMPS, prefetch ON, V<sub>DD</sub> = 1.8 V)

# 2.4 ULPMark<sup>™</sup> CoreMark<sup>®</sup> performance comparison (CoreMark/mW with different IDEs)

# 2.4.1 ULPMark<sup>™</sup> CoreMark<sup>®</sup> description

The ULPMark<sup>™</sup> CoreMark<sup>®</sup> provides a comprehensive evaluation of a microcontroller energy efficiency by considering both processing performance (CoreMark) and power consumption (ULPMark).

The ULPMark<sup>™</sup> CoreMark<sup>®</sup> score is the number of CoreMark iterations a device can execute per millijoule. This number, when presented with the CoreMark iterations-per-second score, illustrates how the two opposing metrics are related.

The benchmark defines three operating-point configurations:

- 1. A best-case "Performance [PERF]" configuration score

- 2. A best-case "Energy Efficiency [EE]" configuration score at the lowest voltage

- 3. An "Energy Efficiency 3V [EE3V]" score collected at 3 V to facilitate a baseline comparison across products at a same voltage

For more information on ULPMark<sup>™</sup> CoreMark<sup>®</sup>, refer to document [6].

# 2.4.2 ULPMark<sup>™</sup> CoreMark<sup>®</sup> results on STM32U3 series devices

Table 6 and Table 7 show the ULPMark<sup>™</sup> CoreMark<sup>®</sup> results on STM32U375/385 with the following configuration:

- System clock at 48 MHz Range 2 (optimum configuration) for energy efficiency and 96 MHz Range 1 for performance

- ICACHE configured to 1-way

- Code in FLASH Bank 1 and data, stack/seap in SRAM1 page 1

- FLASH Bank 2 powered down with low-power mode set to 1

AN6195 - Rev 2 page 7/23

Table 6. ULPMark<sup>™</sup> CoreMark<sup>®</sup> score on STM32U375/385 with IAR<sup>™</sup> 9.40

| Data and stack/heap in SRAM1 |                 |                       |                              |  |

|------------------------------|-----------------|-----------------------|------------------------------|--|

| Metric                       | Performance Run | Energy efficiency Run | Energy efficiency Run at 3 V |  |

| CoreMark                     | 382.68          | 191.34                | 191.34                       |  |

| CoreMark/MHz                 | 3.99            | 3.99                  | 3.99                         |  |

| Power (uW)                   | 4302.20         | 1734.60               | 1947.11                      |  |

| Voltage (V)                  | 1.8             | 1.8                   | 3                            |  |

| Frequency (MHz)              | 96              | 48                    | 48                           |  |

| Estimated freq. (MHz)        | 96.30           | 48.20                 | 48.28                        |  |

| Library                      | libcmM33i9040   | libcmM33i9040         | libcmM33i9040                |  |

| Iterations                   | 4500            | 2000                  | 2000                         |  |

| Temperature (°C)             | 22              | 22                    | 22                           |  |

| ULPMark-CM                   | 89.23           | 110.77                | 98.84                        |  |

Table 6 shows the best performance on the STM32U3 series with IAR $^{\text{™}}$  9.40.1 is 3.99 CM/MHz, using high-speed, no-size-constraint optimization. The best energy efficiency on the STM32U3 series obtained with IAR $^{\text{™}}$  is 110.77 Coremark/mW at 1.8 V and system clock at 48 MHz.

Table 7. ULPMark<sup>™</sup> CoreMark<sup>®</sup> score on STM32U375/385 with Keil<sup>®</sup> 5.36 (arm compiler V6.16)

| Data and stack/heap in SRAM1                                          |              |              |              |  |  |

|-----------------------------------------------------------------------|--------------|--------------|--------------|--|--|

| Metric Performance Run Energy efficiency Run Energy efficiency Run at |              |              |              |  |  |

| CoreMark                                                              | 387.3        | 196.14       | 196.14       |  |  |

| CoreMark/MHz                                                          | 4.03         | 4.09         | 4.09         |  |  |

| Power (uW)                                                            | 4217.40      | 1682.19      | 1839.16      |  |  |

| Voltage (V)                                                           | 1.8          | 1.8          | 3            |  |  |

| Frequency (MHz)                                                       | 96           | 48           | 48           |  |  |

| Estimated freq. (MHz)                                                 | 96.33        | 48.21        | 48.28        |  |  |

| Library                                                               | libcmM33k536 | libcmM33k536 | libcmM33k536 |  |  |

| Iterations                                                            | 4500         | 2000         | 2000         |  |  |

| Temperature (°C)                                                      | 22           | 22           | 22           |  |  |

| ULPMark-CM                                                            | 92.15        | 117.10       | 107.27       |  |  |

Table 7 shows the best performance on the STM32U3 series with Keil $^{\$}$  5.36 is 4.09 CM/MHz, using Omax and LTO optimization. The best energy efficiency on the STM32U3 series obtained with Keil $^{\$}$  is 117.10 Coremark/mW at 1.8 V and system clock at 48 MHz.

The ULPMark  $^{\text{\tiny M}}$  CoreMark  $^{\text{\tiny B}}$  score is a quantitative measure that indicates the energy efficiency of the microcontroller in continuous monitoring tasks. A higher ULPMark  $^{\text{\tiny M}}$  CoreMark  $^{\text{\tiny B}}$  score signifies better energy efficiency and lower power consumption in such scenarios.

Note:

The ULPMark $^{\text{\tiny M}}$  CoreMark $^{\text{\tiny B}}$  score (Performance: CoreMark/MHz or energy efficiency: CoreMark/mW) varies based on the chosen IDEs and their respective versions.

AN6195 - Rev 2 page 8/23

# 3 STM32U3 series low-power modes

The STM32U3 series microcontrollers offer a range of low-power modes to optimize energy efficiency and extend battery life in embedded application when the CPU does not need to be kept running, for example when waiting for an external event. It is up to the user to select the mode that gives the best compromise between low-power consumption, short startup time, and available wake-up sources. Refer to document [1] for more details.

# 3.1 Low-power overview

By default, the microcontroller is in Run mode after a system or a power reset. It is up to the user to select one of the low-power modes described in the following sections:

#### Sleep mode

CPU clock off, all peripherals including Cortex<sup>®</sup>-M33 core such as NVIC and SysTick can run and wake up the CPU when an interrupt or an event occurs.

The typical average power consumption of the system in Sleep mode is 150 µA at 3 V.

#### Stop 0, Stop 1, Stop 2, and Stop 3 modes

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. The SRAMs can be totally or partially switched off to further reduce consumption. All clocks in the core domain are stopped. The MSI (MSIS and MSIK) RC, the HSI16 RC, and the HSE crystal oscillators are disabled while the low-speed ones (LSE, LSI) can be kept active.

In Stop 0 mode, the regulator remains in main regulator mode, allowing a very fast wake-up time but with much higher consumption.

In Stop 1 mode, the regulator is in low-power mode, and the whole core domain is fully powered. All autonomous peripherals are functional. The typical average power consumption of the system in Stop 1 mode is 50  $\mu$ A at 3 V.

In Stop 2 mode, most of the core domain (D1 domain) is put in a lower leakage mode, keeping register retention but without any possible functionality. The D2 domain, embedding APB3 peripherals, is kept fully powered, so those peripherals can be kept functional. The typical average power consumption of the system in Stop 2 mode with 8-Kbyte SRAM is 3.1 µA at 3 V.

Stop 3 is the lowest power mode with full retention, but the functional peripherals and sources of wake-up are reduced to the same ones as in Standby mode. The typical average power consumption of the system in Stop 3 mode with 8-Kbyte SRAM is  $1.15 \,\mu A$  at  $3 \, V$ .

The system clock when exiting from Stop mode can be either MSIS up to 48 MHz or HSI16, depending on software configuration.

#### Standby mode

The Standby mode is used to achieve the lowest power consumption with BOR. The internal regulator is switched off so that the core domain is powered off. The MSI (MSIS and MSIK) RC, the HSI16 RC, and the HSE crystal oscillators are also switched off. The system clock after wake-up is MSIS up to 12 MHz.

The typical average power consumption of the system in Standby mode is 0.22 µA at 3 V.

# Shutdown mode

The Shutdown mode allows the lowest power consumption. The internal regulator is switched off so that the core domain is powered off. The HSI16, the MSI (MSIS and MSIK), the LSI, and the HSE oscillators are also switched off.

The system clock after wake-up is MSIS at 12 MHz.

The typical average power consumption of the system in Shutdown mode is 0.19 µA at 3 V.

AN6195 - Rev 2 page 9/23

# 3.2 Power consumption optimization

## 3.2.1 ICACHE in low-power mode

ICACHE reduces power consumption by fetching instructions from the internal ICACHE most of the time, rather than from the larger and more power-consuming main memories. This reduction is even higher if the cached main memories are external. Applications with a lower-performance profile and stringent low-power consumption constraints may benefit from the lower power consumption of an ICACHE configured as direct mapped (ICACHE\_1-way). This single-way cache configuration is obtained by programming WAYSEL = 0 in ICACHE\_CR.

Note: The hit and miss monitors are disabled (stopped) by default to reduce power consumption.

# 3.2.2 FLSAH in low-power mode

After reset, Bank 1 and Bank 2 are in normal mode. To reduce power consumption in Run and Sleep modes, each bank can be independently put in power-down mode by setting the PDREQx bit in FLASH\_ACR. The flash memory supports a low-power read mode (LPM) to reduce power consumption, which can be enabled by setting LPM = 1 in FLASH\_ACR. When the LPM bit is set, the flash latency must be configured according to the CPU (HCLK) frequency. For more details, refer to document [1].

Note: Prefetch tends to increase code execution performance at the cost of extra flash memory accesses. It must be used carefully in low-power applications.

## 3.2.3 Power control optimization

After reset, the regulator is the LDO in Range 2. Switching to SMPS provides lower consumption, particularly at high  $V_{DD}$  voltage in Run, Sleep, or any other low-power mode. When exiting the Stop or Standby mode, the regulator is the same as when entering low-power modes. The voltage range is Range 2 (low-power range), except when exiting Stop 0 mode.

During Standby mode, and if BOR level 0 is selected, it is possible to set the BOR in ultra-low-power mode to further reduce current consumption by setting the ULPMEN bit in PWR CR1.

# 3.2.4 RCC in low-power mode

To reduce the power consumption, it is recommended to select MSIRC1 as an oscillator source and lower the speeds of SYSCLK, HCLK, and PCLK clocks.

After a reset or when exiting Shutdown mode, the CPU clock frequency is 12 MHz, generated from MSIRC1. When exiting Standby mode, the selected oscillator is always MSIRC1 (from 3 to 12 MHz). When exiting Stop modes, the system clock can be either MSIS (up to 48 MHz) or HSI16, depending on the STOPWUCK bit in the RCC CR.

By default, the MSI bias (for both MSIS and MSIK) is in continuous mode to maintain the output clock accuracy. Setting the MSIBIAS bit in RCC\_ICSCR1 reduces MSI consumption when the device is in Stop 1 or Stop 2 mode, or when the regulator is in Range 2, but it decreases MSI accuracy.

Each clock source can be switched on or off independently when it is not used, to optimize power consumption.

#### 3.2.5 GPIO in low-power mode

Refer to document [5] for more details.

# Configure unused GPIO input as analog input

A GPIO always has an input channel, which can be either digital or analog. If it is not necessary to read the GPIO data, prefer the analog input configuration. This saves the input Schmitt trigger consumption.

Note: To further reduce power consumption, it is recommended to put all unused I/Os in the analog state.

#### Disable GPIO register clock

If a GPIO bank is not needed for a long time, disable its clock by using the <code>HAL\_RCC\_GPIOx\_CLK\_DISABLE()</code> function.

AN6195 - Rev 2 page 10/23

#### Configure GPIO when entering low-power modes

In Sleep, Stop 0, and Stop 1 modes, all I/O pins keep the same state as in Run mode. For outputs, set the level required by the external component. In Stop 2 mode, all I/O pins also keep the same state as in Run mode, except for I3C-specific pull-up. In Stop 3, Standby, or Shutdown mode, the I/Os are in a floating state by default. Apply an internal pull-up or pull-down by software, depending on the level required by the external component.

Note:

This software internal pull-up/pull-down is not applied when exiting Shutdown mode until the firmware configures the GPIO.

Refer to document [1] for more details.

# 3.2.6 SRAMs in low-power mode

In Stop 0, Stop 1, Stop 2, and Stop 3 modes, the SRAMs (Sub-blocks of SRAM1 and SRAM2, ICACHE, FDCAN, PKA SRAM) can be powered down to further reduce power consumption by setting the corresponding bit to 1 in PWR CR2.

In Standby mode, the SRAMs and register contents are lost except for registers in the Backup domain and Standby circuitry. Optionally, the SRAM2 content can be partially (8 Kbytes or 24 Kbytes or 32 Kbytes) or fully (64 Kbytes) preserved depending on RRSB1, RRSB2, and RRSB3 bits configuration in PWR\_CR1. In this case, the low-power regulator is on and provides the supply to SRAM2 only.

In Shutdown mode, the SRAMs and register contents are lost except for registers in the Backup domain. Refer to document [1] for more details.

# 3.2.7 Debug in low-power mode

In Standby and Stop modes, it is possible to maintain the core supply and keep all the clocks and oscillators active to enable full debugging capability for low-power applications.

This can be achieved by setting DBG STANDBY or DBG STOP bits in DBGMCU CR register.

Note:

Using this feature in low-power mode increases power consumption and simulates the entry into low-power mode

By default, all clocks are disabled and the core is powered down automatically in Stop and Standby modes if the power is switched off or if the core is not clocked.

Note:

For the NUCLEO-U385RG-Q board, PA13 and PA14 are SWDIO/SWDCLK. If they are kept active in stop modes for debugging purposes, an extra consumption of up to 200 µA can be added in Stop modes. To further reduce power consumption when entering Stop modes, it is recommended to disable the debug by resetting the DBG\_STANDBY or DBG\_STOP bits in the DBGMCU\_CR register and putting PA13/PA14 in Analog mode.

Refer to document [1] for more details.

# 3.3 Peripherals clock gating and autonomous mode

# Clock gating in Sleep mode

When a peripheral is enabled, its clock can be automatically gated off when the device is in Sleep mode, by clearing the peripheral SLPEN bit in RCC\_AHBxSLPENR and RCC\_APBxSLPENR.

To keep the clock on in Sleep mode, both the EN and SLPEN bits of the peripheral must be set.

#### Clock gating in Stop 0, Stop 1, and Stop 2 modes

When a peripheral is enabled, its clock can be automatically gated off when the device is in Stop mode, by clearing the peripheral STPEN bit in RCC AHBXSTPENR and RCC APBXSTPENR.

To keep the clock on in Stop mode, all the EN, SLPEN, and STPEN bits of the peripheral must be set.

#### **Autonomous peripherals**

Several peripherals support the Autonomous mode and can operate in Stop mode by requesting their Kernel clock and their bus (APB or AHB) when needed, in order to transfer data with GPDMA1 depending on peripherals and power mode.

Refer to document [1] for more details.

AN6195 - Rev 2 page 11/23

The table below lists all STM32U3 series peripherals that support the autonomous mode.

Table 8. Peripherals supporting Autonomous mode

| Low-power mode    | Peripherals                                                                                                                                                                                                                     |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Stop 0 and Stop 1 | <ul> <li>DAC1 (2 channels)</li> <li>LPTIMx (x = 1 to 4)</li> <li>U(S)ARTx (x = 1, 3 to 5)</li> <li>LPUART1</li> <li>SPIx (x = 1 to 3)</li> <li>I2Cx (x = 1 to 3)</li> <li>I3Cx (x = 1 to 2)</li> <li>ADF1 and GPDMA1</li> </ul> |

| Stop 2            | <ul> <li>LPTIM1</li> <li>LPTIM3</li> <li>LPTIM4</li> <li>LPUART1</li> <li>I2C3</li> </ul>                                                                                                                                       |

In Stop 2 mode, if one of the autonomous peripherals requests the AHB/APB clocks for a DMA transfer, the whole core domain is switched to Stop 1 higher leakage mode, and the clock is distributed to GPDMA1, enabled SRAMs, and peripherals to perform the autonomous peripheral DMA transfer. Then the core domain automatically returns to Stop 2 lower leakage mode.

Note:

GPDMA1 transfers are functional and autonomous in Stop 0 and 1 modes.

In Stop 2 mode, GPDMA1 supports only LPUART1, I2C3, LPTIM1, LPTIM3, and LPTIM4 requests. None of GPDMA1 triggers are supported. Interrupts wake up from Stop 2 modes.

The COMPs, the PVM, and the PVD can be used in Stop 2 mode. If they are not needed, they must be disabled by software to save their power consumptions.

All the peripherals that cannot be functional in Stop 2 mode must be either disabled by clearing the enable bit in the peripheral itself or put under reset state by configuring RCC\_AHBxENR and RCC\_APBxENR.

AN6195 - Rev 2 page 12/23

# 4 Energy saving in ultra-low-power application (different duty cycle) using STM32U3, STM32L4, and STM32U5

The next section delves into a comparative analysis of energy efficiency versus duty cycle runtime across distinct STM32 products. This investigation aims to provide a comprehensive understanding of how different STM32 microcontrollers handle energy consumption in relation to varying duty cycle runtime.

# 4.1 Low-power application profile

In applications where the battery lifetime is a concern, the system must be optimized to provide maximum performance and reactivity with the minimal power consumption. This type of application generally contains two different phases:

- Active phase (process) requires a certain number of instructions to be executed in a given regular time frame

- Inactive phase requires a certain minimal context to be kept (data RAM retention) and wake-up capability (RTC) while keeping the power consumption as low as possible.

TPERIOD Inactive

Figure 5. Application profile

Two parameters need to be selected to optimize the average power consumption:

- Run mode and clock frequency to be used during the active phase

- Low-power mode to be used during the inactive phase

# 4.2 Application profile overview

This section demonstrates the benefits of using the STM32U3 series in ultra-low-power applications with various application profiles. These applications execute the CoreMark<sup>®</sup> algorithm during the processing phase in each frame time. Afterward, the system transitions to Stop mode and waits for an RTC interrupt to wake it up.

The three application profiles outlined below are executed with different duty cycles, combining the CoreMark® code with extended inactivity periods to simulate various application domains such as consumer, metering, and industrial.

# Human activity recognition (HAR)

Human activity recognition (HAR) focuses on the automatic identification and classification of human activities based on data collected from various sensors. HAR systems can recognize and categorize different activities or gestures performed by individuals, such as walking, running, sitting, or specific exercises.

AN6195 - Rev 2 page 13/23

Figure 6. HAR application

, T

This application simulates a consumer scenario with a 3% duty cycle, consisting of a 3 ms runtime and 97 ms inactive period, with a wake-up frequency of 10 Hz over a duration of 100 ms. It measures over one second consisting in 30 ms runtime and 970 ms inactive period.

## Metering (flow meter)

A metering system is designed to measure, monitor, and record the consumption of utilities such as electricity, water, gas, or heat. Metering applications are commonly used in residential, commercial, and industrial settings to track and manage resource usage for billing, analysis, and conservation purposes.

Figure 7. Flow meter application

This application simulates a metering scenario with a 0.1% duty cycle, consisting of a 3 ms runtime and a 2997 ms inactive period, with a wake-up frequency of 0.3 Hz over a duration of 3 seconds.

#### **Industrial GPS tracker**

An industrial GPS tracker is used in industrial settings to track and monitor the location and movement of assets, vehicles, or equipment. These applications are tailored to meet the specific needs of industrial operations, such as fleet management, logistics, asset tracking, and supply chain management.

AN6195 - Rev 2 page 14/23

Figure 8. GPS tracker application

This application simulates an industrial GPS tracker scenario with a 0.04% duty cycle, consisting of a 11 ms runtime and a 29989 ms inactive period, with a wake-up frequency of 0.03 Hz over a duration of 30 seconds.

# 4.3 Energy consumption for the three different application profiles

Table 9, Table 10, and Table 11 show the dynamic(mW) and static( $\mu$ W) energy consumption of the different three application profiles on STM32U3, STM32L4, and STM32U5. The measurements are taken at 1.8 V for the HAR application and at 3.3 V for the metering and tracker applications, with 128-kbyte SRAM retention during the inactive phase.

Table 9. STM32U385 energy consumption with system clock at 48 MHz

| STM32U385 at 48 MHz (R2) 128-KB RAM retention |                        |                      |                 |                               |

|-----------------------------------------------|------------------------|----------------------|-----------------|-------------------------------|

| -                                             | Application            | HAR (3%)<br>Consumer | Metering (0.1%) | Tracker (0.04%)<br>Industrial |

|                                               | Voltage (V)            | 1.8                  | 3.3             | 3.3                           |

|                                               | Time (s)               | 0.03                 | 0.003           | 0.011                         |

| Dynamia anargy                                | Current (mA)           | 1.1                  | 0.685           | 0.683                         |

| Dynamic energy                                | mW                     | 1.98                 | 2.26            | 2.25                          |

|                                               | μJoule                 | 59.40                | 6.78            | 24.79                         |

|                                               | Energy % for Run mode  | 92.72                | 24.79           | 10.75                         |

|                                               | Voltage (V)            | 1.8                  | 3.3             | 3.3                           |

|                                               | Time (s)               | 0.97                 | 2.997           | 29.989                        |

| Ctatia anama                                  | Current (µA)           | 2.67                 | 2.08            | 2.08                          |

| Static energy                                 | μW                     | 4.81                 | 6.86            | 6.86                          |

|                                               | μJoule                 | 4.66                 | 20.57           | 205.84                        |

|                                               | Energy % for Stop mode | 7.28                 | 75.21           | 89.25                         |

| -                                             | Total (µJ)             | 64.06                | 27.35           | 230.64                        |

Note: For STM32U385, 128-kbyte SRAM is retained in Stop mode, while the full RAM is available in Run mode.

AN6195 - Rev 2 page 15/23

Table 10. STM32U545 energy consumption with system clock at 48 MHz

| STM32U545 at 48 MHz (R3) 128-KB RAM retention |                        |                      |                 |                               |

|-----------------------------------------------|------------------------|----------------------|-----------------|-------------------------------|

| -                                             | Application            | HAR (3%)<br>Consumer | Metering (0.1%) | Tracker (0.04%)<br>Industrial |

|                                               | Voltage (V)            | 1.8                  | 3.3             | 3.3                           |

|                                               | Time (s)               | 0.03                 | 0.003           | 0.011                         |

| Dynamia anaray                                | Current (mA)           | 2.53                 | 1.81            | 1.81                          |

| Dynamic energy                                | mW                     | 4.55                 | 5.97            | 5.97                          |

|                                               | μJoule                 | 136.62               | 17.92           | 65.70                         |

|                                               | Energy % for Run mode  | 97.05                | 46.67           | 24.28                         |

|                                               | Voltage (V)            | 1.8                  | 3.3             | 3.3                           |

|                                               | Time (s)               | 0.97                 | 2.997           | 29.989                        |

| Statio anarqu                                 | Current (µA)           | 2.38                 | 2.07            | 2.07                          |

| Static energy                                 | μW                     | 4.28                 | 6.83            | 6.83                          |

|                                               | μJoule                 | 4.16                 | 20.47           | 204.85                        |

|                                               | Energy % for Stop mode | 2.95                 | 53.33           | 75.72                         |

| -                                             | Total (µJ)             | 140.78               | 38.39           | 270.56                        |

Table 11. STM32L476 energy consumption with system clock at 48 MHz

| STM32L476 at 48 MHz (R1) 128-KB RAM retention |                        |                      |                 |                               |

|-----------------------------------------------|------------------------|----------------------|-----------------|-------------------------------|

| -                                             | Application            | HAR (3%)<br>Consumer | Metering (0.1%) | Tracker (0.04%)<br>Industrial |

|                                               | Voltage (V)            | 1.8                  | 3.3             | 3.3                           |

|                                               | Time (s)               | 0.035                | 0.0035          | 0.013                         |

| Dynamia anaray                                | Current (mA)           | 7.54                 | 7.66            | 7.66                          |

| Dynamic energy                                | mW                     | 13.57                | 25.28           | 25.28                         |

|                                               | μJoule                 | 475.02               | 88.47           | 328.61                        |

|                                               | Energy % for Run mode  | 99.44                | 82.48           | 63.61                         |

|                                               | Voltage (V)            | 1.8                  | 3.3             | 3.3                           |

|                                               | Time (s)               | 0.965                | 2.9965          | 29.987                        |

| Static operay                                 | Current (µA)           | 1.55                 | 1.90            | 1.90                          |

| Static energy                                 | μW                     | 2.79                 | 6.27            | 6.27                          |

|                                               | μJoule                 | 2.69                 | 18.79           | 188.02                        |

|                                               | Energy % for Stop mode | 0.56                 | 17.52           | 36.39                         |

| -                                             | Total (µJ)             | 477.71               | 107.26          | 516.63                        |

Table 12 shows the energy consumption gains on STM32U3 compared to STM32L4 and STM32U5 for different application profiles.

AN6195 - Rev 2 page 16/23

Table 12. Comparison between STM32U3, STM32L4, and STM32U5

|                                                 | cation<br>MHz    | Consumer<br>HAR<br>3% Run | Metering<br>(flow meter)<br>0.1% Run | Industrial<br>GPS tracker<br>0.04% Run |

|-------------------------------------------------|------------------|---------------------------|--------------------------------------|----------------------------------------|

| STM32L476                                       | Run              | 99.44%                    | 82.48%                               | 63.61%                                 |

| Run (136 μA/MHz)<br>Stop (1.5 μA)               | Stop             | 0.56%                     | 17.52%                               | 36.39%                                 |

| STM32U545                                       | Run              | 97.05%                    | 46.67%                               | 24.28%                                 |

| Run (39 µA/MHz)                                 | Stop             | 2.95%                     | 53.33%                               | 75.72%                                 |

| Stop (2 µA)                                     | Gain versus L476 | 3.4x                      | 2.8x                                 | 1.9x                                   |

|                                                 | Run              | 93.42%                    | 25.86%                               | 11.33%                                 |

| STM32U385<br>Run (14.2 μA/MHz)<br>Stop (2.0 μA) | Stop             | 6.58%                     | 74.14%                               | 88.67%                                 |

|                                                 | Gain versus L476 | 7.4x                      | 3.9x                                 | 2.2x                                   |

|                                                 | Gain versus U545 | 2.2x                      | 1.4x                                 | 1.2x                                   |

Note:

In applications requiring 3% of runtime, the STM32U385 is 7.4 times energy-efficient than the STM32L476 and 2.2 times better than the STM32U545.

In the metering application, the STM32U385 is 3.9 times more energy-efficient than the STM32L476 and 1.4 times more energy-efficient than the STM32U545.

Even for applications that perform only 0.04% of the runtime and remain most of the time in Stop mode, the STM32U385 is 2.2 times more energy-efficient than the STM32L476 and 1.2 times more energy-efficient than the STM32U545, despite the STM32L476 consuming less power in Stop mode than the STM32U385.

In conclusion, despite the very low duty cycle, the STM32U385 outperforms the STM32L476 and STM32U545 when using application profiles representing various applications such as consumer, metering, and industrial.

AN6195 - Rev 2 page 17/23

# 5 Conclusion

The main ultra-low-power features of the STM32U3 series microcontrollers are presented in this application note. They show the benefits offered by this microcontroller family to reduce power consumption in embedded systems. These devices offer a large choice of options for optimizing both performance and power consumption, regardless of the application.

This document provides guidelines based on experiments and quantitative results to quickly select the best running and low-power modes, according to the characteristics and constraints of the end-user application.

AN6195 - Rev 2 page 18/23

# **Revision history**

Table 13. Document revision history

| Date        | Version | Changes                       |

|-------------|---------|-------------------------------|

| 13-Feb-2025 | 1       | Initial release.              |

| 28-Feb-2025 | 2       | Updated Section Introduction. |

AN6195 - Rev 2 page 19/23

# **Contents**

| 1   | Gen      | eral info | ormation                                                                                          | 2  |

|-----|----------|-----------|---------------------------------------------------------------------------------------------------|----|

| 2   | Ene      | rgy effic | ciency processing                                                                                 | 3  |

|     | 2.1      | Interna   | al regulator efficiency                                                                           | 3  |

|     | 2.2      | Dynam     | nic voltage scaling management                                                                    | 4  |

|     | 2.3      | Flash     | memory and ICACHE efficiency                                                                      | 5  |

|     |          | 2.3.1     | Flash memory efficiency                                                                           | 5  |

|     |          | 2.3.2     | ICACHE efficiency                                                                                 | 5  |

|     | 2.4      | ULPMa     | ark <sup>™</sup> CoreMark <sup>®</sup> performance comparison (CoreMark/mW with different IDEs) . | 7  |

|     |          | 2.4.1     | ULPMark <sup>™</sup> CoreMark <sup>®</sup> description                                            | 7  |

|     |          | 2.4.2     | ULPMark <sup>™</sup> CoreMark <sup>®</sup> results on STM32U3 series devices                      | 7  |

| 3   | STM      | 32U3 s    | eries low-power modes                                                                             | 9  |

|     | 3.1      | Low-po    | ower overview                                                                                     | 9  |

|     | 3.2      |           | consumption optimization                                                                          |    |

|     |          | 3.2.1     | ICACHE in low-power mode                                                                          |    |

|     |          | 3.2.2     | FLSAH in low-power mode                                                                           | 10 |

|     |          | 3.2.3     | Power control optimization                                                                        | 10 |

|     |          | 3.2.4     | RCC in low-power mode                                                                             | 10 |

|     |          | 3.2.5     | GPIO in low-power mode                                                                            | 10 |

|     |          | 3.2.6     | SRAMs in low-power mode                                                                           | 11 |

|     |          | 3.2.7     | Debug in low-power mode                                                                           | 11 |

|     | 3.3      | Periph    | erals clock gating and autonomous mode                                                            | 11 |

| 4   |          |           | ring in ultra-low-power application (different duty cycle) using STM32L4, and STM32U5             | 13 |

|     | 4.1      | Low-po    | ower application profile                                                                          | 13 |

|     | 4.2      | Applica   | ation profile overview                                                                            | 13 |

|     | 4.3      | Energy    | consumption for the three different application profiles                                          | 15 |

| 5   | Con      | clusion   |                                                                                                   | 18 |

| Rev | vision   | history   |                                                                                                   | 19 |

|     |          | _         |                                                                                                   |    |

|     | t of fig |           |                                                                                                   | 22 |

# **List of tables**

| Table 1.  | Power distribution of the internal regulators                                                                      | 3    |

|-----------|--------------------------------------------------------------------------------------------------------------------|------|

| Table 2.  | Bus maximum frequency                                                                                              | 4    |

| Table 3.  | Current consumption for STM32U3 series in Run mode versus LPM                                                      | 5    |

| Table 4.  | Current consumption for STM32U3 series in Run mode with ICACHE ON (1-way) versus prefetch                          | 6    |

| Table 5.  | Current consumption for STM32U3 series in Run mode with prefetch ON versus ICACHE configurations                   | 6    |

| Table 6.  | ULPMark <sup>™</sup> CoreMark <sup>®</sup> score on STM32U375/385 with IAR <sup>™</sup> 9.40                       | 8    |

| Table 7.  | ULPMark <sup>™</sup> CoreMark <sup>®</sup> score on STM32U375/385 with Keil <sup>®</sup> 5.36 (arm compiler V6.16) | 8    |

| Table 8.  | Peripherals supporting Autonomous mode                                                                             | . 12 |

| Table 9.  | STM32U385 energy consumption with system clock at 48 MHz                                                           | . 15 |

| Table 10. | STM32U545 energy consumption with system clock at 48 MHz                                                           | . 16 |

| Table 11. | STM32L476 energy consumption with system clock at 48 MHz                                                           | . 16 |

| Table 12. | Comparison between STM32U3, STM32L4, and STM32U5                                                                   | . 17 |

| Table 13. | Document revision history                                                                                          | . 19 |

AN6195 - Rev 2 page 21/23

# **List of figures**

| Figure 1. | Current consumption for STM32U3 in Run mode with ICACHE ON, 1-way, prefetch ON, SMPS versus LDO                           | . 3 |

|-----------|---------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2. | Power efficiency for STM32U3 with ICACHE ON, 1-way, prefetch ON, SMPS versus LDO                                          | . 4 |

| Figure 3. | Flash memory latency versus V <sub>CORE</sub> range (V <sub>DD</sub> = 1.71 to 3.6 V, LPM = 0)                            | . 5 |

| Figure 4. | Power efficiency for various ICACHE configurations (SecureMark <sup>™</sup> , SMPS, prefetch ON, V <sub>DD</sub> = 1.8 V) | . 7 |

| Figure 5. | Application profile                                                                                                       | 13  |

| Figure 6. | HAR application                                                                                                           | 14  |

| Figure 7. | Flow meter application                                                                                                    | 14  |

| Figure 8. | GPS tracker application                                                                                                   | 15  |

AN6195 - Rev 2 page 22/23

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

AN6195 - Rev 2 page 23/23