# LSM6DSV320X: finite state machine

### Introduction

The LSM6DSV320X is a high-end, low-noise, low-power, small IMU, featuring a 3-axis digital low-g accelerometer at 16 g, a 3-axis digital high-g accelerometer at 320 g, and a 3-axis digital gyroscope, which offers the best IMU sensor with a quad-channel architecture for processing acceleration and angular rate data on four separate channels (user interface, OIS, EIS, and high-g accelerometer data) with dedicated configuration, processing, and filtering along with a dedicated high-g sensor for high-g shock and car crash detection.

This document provides information on the finite state machine feature available in the LSM6DSV320X. The finite state machine processing capability allows moving some algorithms from the application processor to the MEMS sensor, enabling consistent reduction of power consumption.

The processing capability of a finite state machine is achieved through logical connections. A state machine is a mathematical abstraction consisting of a finite number of states and transitions between them. The definition of the states and how they are connected implement the desired logic for pattern recognition.

The LSM6DSV320X can be configured to run up to eight finite state machines simultaneously and independently. The finite state machines are stored in the device and generate results in the dedicated output registers.

The results of the finite state machine can be read from the application processor at any time. Furthermore, there is the possibility to generate an interrupt when the desired pattern is detected.

# 1 Finite state machine (FSM)

# 1.1 Finite state machine definition

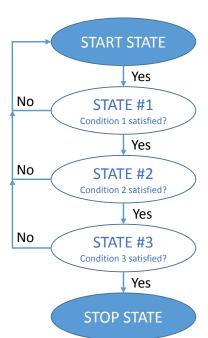

A finite state machine (FSM) is a mathematical abstraction used to design logic connections. It is a behavioral model composed of a finite number of states and transitions between states, similar to a flowchart in which it is possible to inspect the way logic runs when certain conditions are met. The state machine begins with a start state, goes to different states through transitions dependent on the inputs, and can finally end in a specific state (called stop state). The current state is determined by the past states of the system. The following figure depicts the flow of a generic state machine.

Figure 1. Generic state machine

AN6291 - Rev 1 page 2/75

# 1.2 Finite state machine in the LSM6DSV320X

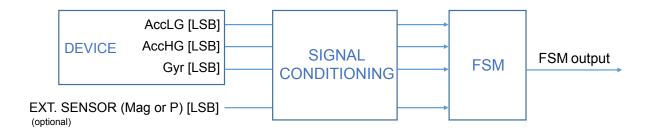

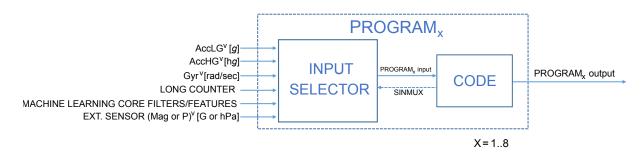

The LSM6DSV320X is a small IMU featuring a 3-axis digital low-g accelerometer at 16 g, a 3-axis digital high-g accelerometer at 320 g, and a 3-axis digital gyroscope. It is also possible to connect an external sensor like a magnetometer or pressure sensor by using the sensor hub feature (mode 2). These data can be used as input of up to eight programs in the embedded finite state machine (refer to the following figure).

Figure 2. State machine in the LSM6DSV320X

The FSM structure is highly modular: it is possible to easily write up to eight programs, each one able to recognize a specific gesture.

All eight finite state machines are independent: each one has its dedicated memory area and it is independently executed. An interrupt is generated when the end state is reached or when some specific command is performed. Typically, the interrupt is generated when a specific gesture is recognized.

AN6291 - Rev 1 page 3/75

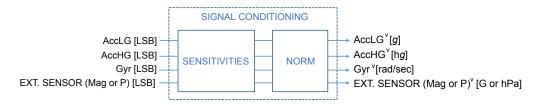

# 2 Signal conditioning block

The signal conditioning block is shown in the following figure and it is used as the interface between incoming sensor data and the FSM block. This block is needed to convert the output sensor data (represented in [LSB]) with the following unit conventions:

- Low-g accelerometer data in [g]

- High-g accelerometer data in [hg]

- Gyroscope data in [rad/sec]

- External sensor: if it is a magnetometer, data have to be converted to [G]. If it is a pressure sensor, data have to be converted to [hPa].

Figure 3. Signal conditioning block

This block is intended to apply the sensitivity to [LSB] input data, and then convert these data in half-precision floating-point (HFP) format before passing them to the FSM block. In greater detail:

- Low-g accelerometer data conversion factor of the LSM6DSV320X is automatically handled by the device.

- High-g accelerometer data conversion factor of the LSM6DSV320X is automatically handled by the device

if the selected full-scale range is equal to or lower than ±256 g; otherwise, if the selected full-scale range is

equal to ±320 g, the host must write in the XL\_HG\_SENSITIVITY\_L (58h) and XL\_HG\_SENSITIVITY\_H

(59h) embedded advanced features registers the value 0x06D4.

- Gyroscope data conversion factor of the LSM6DSV320X is automatically handled by the device.

AN6291 - Rev 1 page 4/75

- External sensor data conversion factor is not automatically handled by the device. The LSM6DSV320X FSM supports processing external sensor data in two different formats as listed below:

- 3-axis sensors with 16-bit data like magnetometer sensors, which are enabled by setting the EXT\_FORMAT\_SEL bit of the EXT\_FORMAT (00h) embedded advanced features register to 0 (default value). In this case, the external sensor data are internally processed as follows.

- 1. Raw external sensor data are converted in HFP format (no sensitivity is applied).

- Hard-iron offset is applied. The FSM\_EXT\_OFFX\_L (C0h), FSM\_EXT\_OFFX\_H (C1h), FSM\_EXT\_OFFY\_L (C2h), FSM\_EXT\_OFFY\_H (C3h), FSM\_EXT\_OFFZ\_L (C4h), and FSM\_EXT\_OFFZ\_H (C5h) embedded advanced features registers must contain the raw hard-iron offset in HFP format.

- Soft-iron compensation is applied. The FSM\_EXT\_MATRIX\_XX\_L (C6h), FSM\_EXT\_MATRIX\_XX\_H

(C7h), FSM\_EXT\_MATRIX\_XY\_L (C8h), FSM\_EXT\_MATRIX\_XY\_H (C9h), FSM\_EXT\_MATRIX\_XZ\_L

(CAh), FSM\_EXT\_MATRIX\_XZ\_H (C8h), FSM\_EXT\_MATRIX\_YY\_L (CCh), FSM\_EXT\_MATRIX\_YY\_H

(CDh), FSM\_EXT\_MATRIX\_YZ\_L (C8h), FSM\_EXT\_MATRIX\_YZ\_H (C7h), FSM\_EXT\_MATRIX\_ZZ\_L

(D0h), and FSM\_EXT\_MATRIX\_ZZ\_H (D1h) embedded advanced features registers must contain the soft-iron coefficients in HFP format.

- 4. Sensitivity is applied. The FSM\_EXT\_SENSITIVITY\_L (BAh) and FSM\_EXT\_SENSITIVITY\_H (BBh) embedded advanced features registers must contain the sensitivity value in HFP format.

- 5. Data are rotated. The EXT\_CFG\_A (D4h) and EXT\_CFG\_B (D5h) embedded advanced features registers must contain the external sensor orientation configuration.

- 1-axis sensors with 24-bit data like pressure sensors, which are enabled by setting the EXT\_FORMAT\_SEL bit of the EXT\_FORMAT (00h) embedded advanced features register to 1. In this case, the external sensor data are internally processed as follows.

- 1. Raw external sensor data is kept in LSB format (no sensitivity is applied).

- Offset is applied. The EXT\_3BYTE\_OFFSET\_XL (06h), EXT\_3BYTE\_OFFSET\_L (07h), and EXT\_3BYTE\_OFFSET\_H (08h) embedded advanced features registers must contain the offset in LSB format.

- Sensitivity is applied. The EXT\_3BYTE\_SENSITIVITY\_L (02h) and EXT\_3BYTE\_SENSITIVITY\_H (03h)

embedded advanced features registers must contain the sensitivity value in HFP format.

Note: Magnetometer data have to be converted to [G], while pressure data have to be converted to [hPa].

Example: LIS2MDL magnetometer sensitivity is 1.5 mG/LSB  $\rightarrow$  0.0015 G/LSB  $\rightarrow$  1624h HFP; this is the default external sensor sensitivity value for the LSM6DSV320X.

#### Procedure to change the conversion factor for an external sensor:

| 1. | Write 80h to register 01h                     | // Enable embedded functions registers access                                  |

|----|-----------------------------------------------|--------------------------------------------------------------------------------|

| 2. | Write 40h to register 17h                     | // PAGE_RW (17h) = 40h: enable write operation                                 |

| 3. | Write 01h to register 02h                     | // PAGE_SEL (02h) = 01h: select embedded advanced features registers page 0 $$ |

| 4. | Write BAh to register 08h                     | // PAGE_ADDRESS (08h) = BAh (FSM_EXT_SENSITIVITY_L address)                    |

| 5. | Write [LSB] conversion factor to register 09h | // Write [LSB] conversion factor value to register FSM_EXT_SENSITIVITY_L (BAh) |

| 6. | Write [MSB] conversion factor to register 09h | // Write [MSB] conversion factor value to register FSM_EXT_SENSITIVITY_H (BBh) |

| 7. | Write 01h to register 02h                     | // PAGE_SEL (02h) = 01h: select embedded advanced features registers page 0 $$ |

| 8. | Write 00h to register 17h                     | // PAGE_RW (17h) = 00h: disable read / write operation                         |

| 9. | Write 00h to register 01h                     | // Disable embedded functions registers access                                 |

In addition to the conversion to HFP format, the signal conditioning block computes the norm of the input data, defined as follows:

$$V = \sqrt{x^2 + y^2 + z^2}$$

The norm of the input data can be used in the state machine programs, in order to guarantee a high level of program customization for the user.

AN6291 - Rev 1 page 5/75

# 3 FSM block

Output data signals coming from the signal conditioning block are sent to the FSM block that is detailed in the following figure. The FSM block is mainly composed of:

- A general FSM configuration block: it affects all programs and includes some registers that have to be properly initialized in order to configure and customize the entire FSM block.

- A maximum of eight configurable programs: each program processes input data and generates an output.

FSM CONFIGURATION  $PROGRAM_{1} \text{ output}$   $AccHG^{V}[hg] \longrightarrow PROGRAM_{2} \text{ output}$   $Gyr^{V}[rad/sec] \longrightarrow PROGRAM_{2}$   $EXT. SENSOR (Mag or P)^{V} [G \text{ or hPa}] \longrightarrow PROGRAM_{8} \text{ output}$

Figure 4. FSM block

FSM configuration and program blocks are described in the following sections.

AN6291 - Rev 1 page 6/75

# 3.1 Configuration block

The configuration block is composed of a set of registers involved in the FSM configuration (FSM ODR, interrupts, programs configuration, and so forth).

The embedded functions registers can be used to properly configure the FSM: these registers are accessible when the FUNC\_CFG\_EN bit is set to 1 and the SHUB\_REG\_ACCESS bit is set to 0 in the FUNC\_CFG\_ACCESS (01h) register.

The LSM6DSV320X device is provided with an extended number of registers inside the embedded functions register set, called embedded advanced features registers, that are divided in pages. A specific read / write procedure must be followed to access the embedded features registers. Registers involved in this specific procedure are the following:

- PAGE\_SEL (02h): it selects the desired page.

- PAGE\_ADDRESS (08h): it selects the desired register address in the selected page.

- PAGE VALUE (09h): it sets the value to be written in the selected register (only in write operation).

- PAGE RW (17h): it is used to select the read / write operation.

The script below shows the generic procedure to write a YYh value in the register having address XXh inside the page number Z of the embedded features registers set:

- 1. Write 80h to register 01h // Enable embedded functions registers access

- 2. Write 40h to register 17h // PAGE\_RW (17h) = 40h: enable write operation

- 3. Write Z1h to register 02h // PAGE\_SEL (02h) = Z1h: select embedded advanced features registers page Z

- 4. Write XXh to register 08h // PAGE\_ADDRESS (08h) = XXh: XXh is the address of the register to be configured

- 5. Write YYh to register 09h // PAGE VALUE (09h) = YYh: YYh is the value to be written

- 6. Write 01h to register 02h // PAGE\_SEL (02h) = 01h: select embedded advanced features registers page 0. This is needed for the correct operation of the device.

- 7. Write 00h to register 17h // PAGE\_RW (17h) = 00h: disable read / write operation

- 8. Write 00h to register 01h // Disable embedded functions registers access

Note: After a write transaction, the PAGE\_ADDRESS (08h) register is automatically incremented.

Program configurations must be written in the embedded advanced features registers, starting from the register address indicated by the FSM\_START\_ADD\_L (7Eh) and FSM\_START\_ADD\_H (7Fh) registers. All programs have to be written in consecutive registers, including two important aspects:

- Both the PAGE\_SEL (02h) register and PAGE\_ADDRESS (08h) register have to be properly updated when moving from one page to another (that is, when passing from page 03h, address FFh to page 04h, address 00h). The LSM6DSV320X device provides eight pages that can be addressed through the PAGE\_SEL (02h) register. To address the last page, PAGE\_SEL (02h) has to be set to 71h.

- Program SIZE byte must be an even number. If it is odd, an additional STOP state has to be added at the end of the instruction section.

Once the program configurations have been written, the FSM programs are executed at the rate configured through the FSM\_ODR\_[2:0] bits of the FSM\_ODR (5Fh) embedded functions register, as explained below:

- If the configured FSM execution rate is equal to the fastest active sensor ODR, the FSM programs are executed at the rate of the fastest active sensor ODR, which matches the FSM execution rate.

- If the configured FSM execution rate is lower than the fastest active sensor ODR, the FSM programs are executed at the rate of the FSM execution rate. In this case, the FSM decimates the input data.

- If the configured FSM execution rate is greater than the fastest active sensor ODR, the FSM programs are executed at the rate of the fastest active sensor ODR.

- If all the sensors are configured in power-down mode (there is no active sensor), the FSM programs are not executed.

For a detailed example of how to configure the entire FSM, refer to Section 11: FSM configuration example.

AN6291 - Rev 1 page 7/75

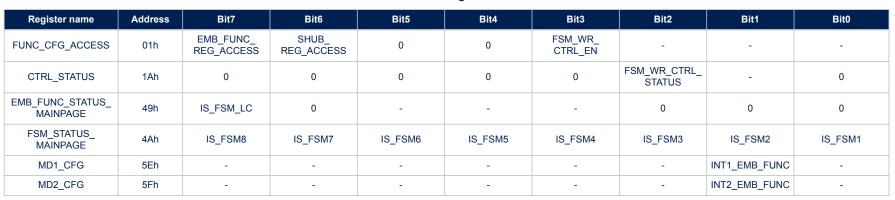

# 3.1.1 Registers

All the FSM-related registers given in the following table are accessible from the primary SPI/I²C/MIPI I3C® interface only.

# 3.1.2 Embedded functions registers

The table given below provides a list of the FSM-related registers for the embedded functions available in the device and the corresponding addresses. Embedded functions registers are accessible when the EMB\_FUNC\_REG\_ACCESS bit is set to 1 in the FUNC\_CFG\_ACCESS (01h) register.

**Table 2. Embedded functions registers**

| Register name          | Address | Bit7             | Bit6        | Bit5        | Bit4        | Bit3        | Bit2        | Bit1        | Bit0       |

|------------------------|---------|------------------|-------------|-------------|-------------|-------------|-------------|-------------|------------|

| PAGE_SEL               | 02h     | PAGE_SEL3        | PAGE_SEL2   | PAGE_SEL1   | PAGE_SEL0   | 0           | 0           | 0           | 1          |

| EMB_FUNC_EN_B          | 05h     | 0                | 0           | 0           | -           | -           | 0           | 0           | FSM_EN     |

| PAGE_ADDRESS           | 08h     | PAGE_ADDR7       | PAGE_ADDR6  | PAGE_ADDR5  | PAGE_ADDR4  | PAGE_ADDR3  | PAGE_ADDR2  | PAGE_ADDR1  | PAGE_ADDR  |

| PAGE_VALUE             | 09h     | PAGE_VALUE7      | PAGE_VALUE6 | PAGE_VALUE5 | PAGE_VALUE4 | PAGE_VALUE3 | PAGE_VALUE2 | PAGE_VALUE1 | PAGE_VALUE |

| EMB_FUNC_INT1          | 0Ah     | INT1_FSM_LC      | 0           | -           | -           | -           | 0           | 0           | 0          |

| FSM_INT1               | 0Bh     | INT1_FSM8        | INT1_FSM7   | INT1_FSM6   | INT1_FSM5   | INT1_FSM4   | INT1_FSM3   | INT1_FSM2   | INT1_FSM1  |

| EMB_FUNC_INT2          | 0Eh     | INT2_FSM_LC      | 0           | -           | -           | -           | 0           | 0           | 0          |

| FSM_INT2               | 0Fh     | INT2_FSM8        | INT2_FSM7   | INT2_FSM6   | INT2_FSM5   | INT2_FSM4   | INT2_FSM3   | INT2_FSM2   | INT2_FSM1  |

| EMB_FUNC_STATUS        | 12h     | IS_FSM_LC        | 0           | -           | -           | -           | 0           | 0           | 0          |

| FSM_STATUS             | 13h     | IS_FSM8          | IS_FSM7     | IS_FSM6     | IS_FSM5     | IS_FSM4     | IS_FSM3     | IS_FSM2     | IS_FSM1    |

| PAGE_RW                | 17h     | EMB_FUNC_<br>LIR | PAGE_WRITE  | PAGE_READ   | 0           | 0           | 0           | 0           | 0          |

| EMB_FUNC_FIFO_EN_B     | 45h     | 0                | 0           | 0           | 0           | 0           | FSM_FIFO_EN | -           | 0          |

| FSM_ENABLE             | 46h     | FSM8_EN          | FSM7_EN     | FSM6_EN     | FSM5_EN     | FSM4_EN     | FSM3_EN     | FSM2_EN     | FSM1_EN    |

| FSM_LONG_<br>COUNTER_L | 48h     | FSM_LC_7         | FSM_LC_6    | FSM_LC_5    | FSM_LC_4    | FSM_LC_3    | FSM_LC_2    | FSM_LC_1    | FSM_LC_0   |

| FSM_LONG_<br>COUNTER_H | 49h     | FSM_LC_15        | FSM_LC_14   | FSM_LC_13   | FSM_LC_12   | FSM_LC_11   | FSM_LC_10   | FSM_LC_9    | FSM_LC_8   |

| FSM_OUTS1              | 4Ch     | P_X              | N_X         | P_Y         | N_Y         | P_Z         | N_Z         | P_V         | N_V        |

| FSM_OUTS2              | 4Dh     | P_X              | N_X         | P_Y         | N_Y         | P_Z         | N_Z         | P_V         | N_V        |

| FSM_OUTS3              | 4Eh     | P_X              | N_X         | P_Y         | N_Y         | P_Z         | N_Z         | P_V         | N_V        |

| FSM_OUTS4              | 4Fh     | P_X              | N_X         | P_Y         | N_Y         | P_Z         | N_Z         | P_V         | N_V        |

| FSM_OUTS5              | 50h     | P_X              | N_X         | P_Y         | N_Y         | P_Z         | N_Z         | P_V         | N_V        |

| FSM_OUTS6              | 51h     | P_X              | N_X         | P_Y         | N_Y         | P_Z         | N_Z         | P_V         | N_V        |

| FSM_OUTS7              | 52h     | P_X              | N_X         | P_Y         | N_Y         | P_Z         | N_Z         | P_V         | N_V        |

| FSM_OUTS8              | 53h     | P_X              | N_X         | P_Y         | N_Y         | P_Z         | N_Z         | P_V         | N_V        |

| FSM_ODR                | 5Fh     | 0                | 1           | FSM_ODR_2   | FSM_ODR_1   | FSM_ODR_0   | 0           | 1           | 1          |

| EMB_FUNC_INIT_B        | 67h     | 0                | 0           | 0           | -           | -           | PT_INIT     | 0           | FSM_INIT   |

# 3.1.3 Embedded advanced features pages

The table given below provides a list of the FSM-related registers for the embedded advanced features page 0. These registers are accessible when PAGE\_SEL[3:0] are set to 0000 in the PAGE\_SEL (02h) register.

Table 3. Embedded advanced features registers - page 0

| Register name         | Address | Bit7                  | Bit6                  | Bit5                  | Bit4                  | Bit3                  | Bit2                    | Bit1                 | Bit0                 |

|-----------------------|---------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-------------------------|----------------------|----------------------|

| FSM_EXT_SENSITIVITY_L | BAh     | FSM_EXT_S_7           | FSM_EXT_S_6           | FSM_EXT_S_5           | FSM_EXT_S_4           | FSM_EXT_S_3           | FSM_EXT_S_2             | FSM_EXT_S_1          | FSM_EXT_S_0          |

| FSM_EXT_SENSITIVITY_H | BBh     | FSM_EXT_S_15          | FSM_EXT_S_14          | FSM_EXT_S_13          | FSM_EXT_S_12          | FSM_EXT_S_11          | FSM_EXT_S_10            | FSM_EXT_S_9          | FSM_EXT_S_8          |

| FSM_EXT_OFFX_L        | C0h     | FSM_EXT_OFFX_7        | FSM_EXT_OFFX_6        | FSM_EXT_OFFX_5        | FSM_EXT_OFFX_4        | FSM_EXT_OFFX_3        | FSM_EXT_OFFX_2          | FSM_EXT_OFFX_1       | FSM_EXT_OFFX_0       |

| FSM_EXT_OFFX_H        | C1h     | FSM_EXT_<br>OFFX_15   | FSM_EXT_<br>OFFX_14   | FSM_EXT_<br>OFFX_13   | FSM_EXT_<br>OFFX_12   | FSM_EXT_<br>OFFX_11   | FSM_EXT_<br>OFFX_10     | FSM_EXT_<br>OFFX_9   | FSM_EXT_<br>OFFX_8   |

| FSM_EXT_OFFY_L        | C2h     | FSM_EXT_OFFY_7        | FSM_EXT_OFFY_6        | FSM_EXT_OFFY_5        | FSM_EXT_OFFY_4        | FSM_EXT_OFFY_3        | FSM_EXT_OFFY_2          | FSM_EXT_OFFY_1       | FSM_EXT_OFFY_0       |

| FSM_EXT_OFFY_H        | C3h     | FSM_EXT_<br>OFFY_15   | FSM_EXT_<br>OFFY_14   | FSM_EXT_<br>OFFY_13   | FSM_EXT_<br>OFFY_12   | FSM_EXT_<br>OFFY_11   | FSM_EXT_<br>OFFY_10     | FSM_EXT_<br>OFFY_9   | FSM_EXT_<br>OFFY_8   |

| FSM_EXT_OFFZ_L        | C4h     | FSM_EXT_OFFZ_7        | FSM_EXT_OFFZ_6        | FSM_EXT_OFFZ_5        | FSM_EXT_OFFZ_4        | FSM_EXT_OFFZ_3        | FSM_EXT_OFFZ_2          | FSM_EXT_OFFZ_1       | FSM_EXT_OFFZ_0       |

| FSM_EXT_OFFZ_H        | C5h     | FSM_EXT_<br>OFFZ_15   | FSM_EXT_<br>OFFZ_14   | FSM_EXT_<br>OFFZ_13   | FSM_EXT_<br>OFFZ_12   | FSM_EXT_<br>OFFZ_11   | FSM_EXT_<br>OFFZ_10     | FSM_EXT_<br>OFFZ_9   | FSM_EXT_<br>OFFZ_8   |

| FSM_EXT_MATRIX_XX_L   | C6h     | FSM_EXT_<br>MAT_XX_7  | FSM_EXT_<br>MAT_XX_6  | FSM_EXT_<br>MAT_XX_5  | FSM_EXT_<br>MAT_XX_4  | FSM_EXT_<br>MAT_XX_3  | FSM_EXT_<br>MAT_XX_2    | FSM_EXT_<br>MAT_XX_1 | FSM_EXT_<br>MAT_XX_0 |

| FSM_EXT_MATRIX_XX_H   | C7h     | FSM_EXT_<br>MAT_XX_15 | FSM_EXT_<br>MAT_XX_14 | FSM_EXT_<br>MAT_XX_13 | FSM_EXT_<br>MAT_XX_12 | FSM_EXT_<br>MAT_XX_11 | FSM_EXT_<br>MAT_XX_10   | FSM_EXT_<br>MAT_XX_9 | FSM_EXT_<br>MAT_XX_8 |

| FSM_EXT_MATRIX_XY_L   | C8h     | FSM_EXT_<br>MAT_XY_7  | FSM_EXT_<br>MAT_XY_6  | FSM_EXT_<br>MAT_XY_5  | FSM_EXT_<br>MAT_XY_4  | FSM_EXT_<br>MAT_XY_3  | FSM_EXT_<br>MAT_XY_2    | FSM_EXT_<br>MAT_XY_1 | FSM_EXT_<br>MATXY_0  |

| FSM_EXT_MATRIX_XY_H   | C9h     | FSM_EXT_<br>MAT_XY_15 | FSM_EXT_<br>MAT_XY_14 | FSM_EXT_<br>MAT_XY_13 | FSM_EXT_<br>MAT_XY_12 | FSM_EXT_<br>MAT_XY_11 | FSM_EXT_<br>MAT_XY_10   | FSM_EXT_<br>MAT_XY_9 | FSM_EXT_<br>MAT_XY_8 |

| FSM_EXT_MATRIX_XZ_L   | CAh     | FSM_EXT_<br>MAT_XZ_7  | FSM_EXT_<br>MAT_XZ_6  | FSM_EXT_<br>MAT_XZ_5  | FSM_EXT_<br>MAT_XZ_4  | FSM_EXT_<br>MAT_XZ_3  | FSM_EXT_<br>MAG_SI_XZ_2 | FSM_EXT_<br>MAT_XZ_1 | FSM_EXT_<br>MAT_XZ_0 |

| FSM_EXT_MATRIX_XZ_H   | CBh     | FSM_EXT_<br>MAT_XZ_15 | FSM_EXT_<br>MAT_XZ_14 | FSM_EXT_<br>MAT_XZ_13 | FSM_EXT_<br>MAT_XZ_12 | FSM_EXT_<br>MAT_XZ_11 | FSM_EXT_<br>MAT_XZ_10   | FSM_EXT_<br>MAT_XZ_9 | FSM_EXT_<br>MAT_XZ_8 |

| FSM_EXT_MATRIX_YY_L   | CCh     | FSM_EXT_<br>MAT_YY_7  | FSM_EXT_<br>MAT_YY_6  | FSM_EXT_<br>MAT_YY_5  | FSM_EXT_<br>MAT_YY_4  | FSM_EXT_<br>MAT_YY_3  | FSM_EXT_<br>MAT_YY_2    | FSM_EXT_<br>MAT_YY_1 | FSM_EXT_<br>MAT_YY_0 |

| FSM_EXT_MATRIX_YY_H   | CDh     | FSM_EXT_<br>MAT_YY_15 | FSM_EXT_<br>MAT_YY_14 | FSM_EXT_<br>MAT_YY_13 | FSM_EXT_<br>MAT_YY_12 | FSM_EXT_<br>MAT_YY_11 | FSM_EXT_<br>MAT_YY_10   | FSM_EXT_<br>MAT_YY_9 | FSM_EXT_<br>MAT_YY_8 |

| FSM_EXT_MATRIX_YZ_L   | CEh     | FSM_EXT_<br>MAT_YZ_7  | FSM_EXT_<br>MAT_YZ_6  | FSM_EXT_<br>MAT_YZ_5  | FSM_EXT_<br>MAT_YZ_4  | FSM_EXT_<br>MAT_YZ_3  | FSM_EXT_<br>MAT_YZ_2    | FSM_EXT_<br>MAT_YZ_1 | FSM_EXT_<br>MAT_YZ_0 |

| FSM_EXT_MATRIX_YZ_H   | CFh     | FSM_EXT_<br>MAT_YZ_15 | FSM_EXT_<br>MAT_YZ_14 | FSM_EXT_<br>MAT_YZ_13 | FSM_EXT_<br>MAT_YZ_12 | FSM_EXT_<br>MAT_YZ_11 | FSM_EXT_<br>MAT_YZ_10   | FSM_EXT_<br>MAT_YZ_9 | FSM_EXT_<br>MAT_YZ_8 |

| FSM_EXT_MATRIX_ZZ_L   | D0h     | FSM_EXT_<br>MAT_ZZ_7  | FSM_EXT_<br>MAT_ZZ_6  | FSM_EXT_<br>MAT_ZZ_5  | FSM_EXT_<br>MAT_ZZ_4  | FSM_EXT_<br>MAT_ZZ_3  | FSM_EXT_<br>MAT_ZZ_2    | FSM_EXT_<br>MAT_ZZ_1 | FSM_EXT_<br>MAT_ZZ_0 |

| FSM_EXT_MATRIX_ZZ_H   | D1h     | FSM_EXT_<br>MAT_ZZ_15 | FSM_EXT_<br>MAT_ZZ_14 | FSM_EXT_<br>MAT_ZZ_13 | FSM_EXT_<br>MAT_ZZ_12 | FSM_EXT_<br>MAT_ZZ_11 | FSM_EXT_<br>MAT_ZZ_10   | FSM_EXT_<br>MAT_ZZ_9 | FSM_EXT_<br>MAT_ZZ_8 |

| EXT_CFG_A             | D4h     | 0                     | EXT_Y_AXIS2           | EXT_Y_AXIS1           | EXT_Y_AXIS0           | 0                     | EXT_Z_AXIS2             | EXT_Z_AXIS1          | EXT_Z_AXIS0          |

| EXT_CFG_B             | D5h     | 0                     | 0                     | 0                     | 0                     | 0                     | EXT_X_AXIS2             | EXT_X_AXIS1          | EXT_X_AXIS0          |

The table given below provides a list of the FSM-related registers for the embedded advanced features page 1. These registers are accessible when PAGE\_SEL[3:0] are set to 0001 in the PAGE\_SEL (02h) register.

Table 4. Embedded advanced features registers - page 1

| Register name       | Address | Bit7                 | Bit6                 | Bit5                 | Bit4                 | Bit3                 | Bit2                 | Bit1                | Bit0                |

|---------------------|---------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|---------------------|---------------------|

| XL_HG_SENSITIVITY_L | 58h     | XL_HG_S_7            | XL_HG_S_6            | XL_HG_S_5            | XL_HG_S_4            | XL_HG_S_3            | XL_HG_S_2            | XL_HG_S_1           | XL_HG_S_0           |

| XL_HG_SENSITIVITY_H | 59h     | XL_HG_S_15           | XL_HG_S_14           | XL_HG_S_13           | XL_HG_S_12           | XL_HG_S_11           | XL_HG_S_10           | XL_HG_S_9           | XL_HG_S_8           |

| FSM_LC_TIMEOUT_L    | 7Ah     | FSM_LC_<br>TIMEOUT7  | FSM_LC_<br>TIMEOUT6  | FSM_LC_<br>TIMEOUT5  | FSM_LC_<br>TIMEOUT4  | FSM_LC_<br>TIMEOUT3  | FSM_LC_<br>TIMEOUT2  | FSM_LC_<br>TIMEOUT1 | FSM_LC_<br>TIMEOUT0 |

| FSM_LC_TIMEOUT_H    | 7Bh     | FSM_LC_<br>TIMEOUT15 | FSM_LC_<br>TIMEOUT14 | FSM_LC_<br>TIMEOUT13 | FSM_LC_<br>TIMEOUT12 | FSM_LC_<br>TIMEOUT11 | FSM_LC_<br>TIMEOUT10 | FSM_LC_<br>TIMEOUT9 | FSM_LC_<br>TIMEOUT8 |

| FSM_PROGRAMS        | 7Ch     | FSM_N_PROG7          | FSM_N_PROG6          | FSM_N_PROG5          | FSM_N_PROG4          | FSM_N_PROG3          | FSM_N_PROG2          | FSM_N_PROG1         | FSM_N_PROG0         |

| FSM_START_ADD_L     | 7Eh     | FSM_START7           | FSM_START6           | FSM_START5           | FSM_START4           | FSM_START3           | FSM_START2           | FSM_START1          | FSM_START0          |

| FSM_START_ADD_H     | 7Fh     | FSM_START15          | FSM_START714         | FSM_START13          | FSM_START12          | FSM_START11          | FSM_START10          | FSM_START9          | FSM_START8          |

The table given below provides a list of the FSM-related registers for the embedded advanced features page 2. These registers are accessible when PAGE\_SEL[3:0] are set to 0010 in the PAGE\_SEL (02h) register.

Table 5. Embedded advanced features registers - page 2

| Register name               | Address | Bit7                 | Bit6                 | Bit5                 | Bit4                 | Bit3                 | Bit2                 | Bit1                 | Bit0                 |

|-----------------------------|---------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| EXT_FORMAT                  | 00h     | 0                    | 0                    | 0                    | 0                    | 0                    | 0                    | EXT_FORMAT_SEL       | 0                    |

| EXT_3BYTE_<br>SENSITIVITY_L | 02h     | EXT_3BYTE_S_7        | EXT_3BYTE_S_6        | EXT_3BYTE_S_5        | EXT_3BYTE_S_4        | EXT_3BYTE_S_3        | EXT_3BYTE_S_2        | EXT_3BYTE_S_1        | EXT_3BYTE_S_0        |

| EXT_3BYTE_<br>SENSITIVITY_H | 03h     | EXT_3BYTE_S_15       | EXT_3BYTE_S_14       | EXT_3BYTE_S_13       | EXT_3BYTE_S_12       | EXT_3BYTE_S_11       | EXT_3BYTE_S_10       | EXT_3BYTE_S_9        | EXT_3BYTE_S_8        |

| EXT_3BYTE_<br>OFFSET_XL     | 06h     | EXT_3BYTE_OFF_7      | EXT_3BYTE_OFF_6      | EXT_3BYTE_OFF_5      | EXT_3BYTE_OFF_4      | EXT_3BYTE_OFF_3      | EXT_3BYTE_OFF_2      | EXT_3BYTE_OFF_1      | EXT_3BYTE_OFF_0      |

| EXT_3BYTE_<br>OFFSET_L      | 07h     | EXT_3BYTE_<br>OFF_15 | EXT_3BYTE_<br>OFF_14 | EXT_3BYTE_<br>OFF_13 | EXT_3BYTE_<br>OFF_12 | EXT_3BYTE_<br>OFF_11 | EXT_3BYTE_<br>OFF_10 | EXT_3BYTE_<br>OFF_9  | EXT_3BYTE_<br>OFF_8  |

| EXT_3BYTE_<br>OFFSET_H      | 08h     | EXT_3BYTE_<br>OFF_23 | EXT_3BYTE_<br>OFF_22 | EXT_3BYTE_<br>OFF_21 | EXT_3BYTE_<br>OFF_20 | EXT_3BYTE_<br>OFF_19 | EXT_3BYTE_<br>OFF_18 | EXT_3BYTE_<br>OFF_17 | EXT_3BYTE_<br>OFF_16 |

# 3.2 Program block

Output data coming from the signal conditioning block are sent to the FSM block, composed of eight program blocks. Each program block, as shown in the following figure, consists of:

- An input selector block, which selects the desired input data signal that is processed by the program

- A code block, composed of the data and the instructions that are executed

Figure 5. Program block

#### 3.2.1 Input selector block

The input selector block allows the selection of the input data signal between the following physical sensor data signals or internally calculated data signals:

- LSM6DSV320X low-g accelerometer data, with precomputed norm (V)

- LSM6DSV320X high-g accelerometer data, with precomputed norm (V)

- LSM6DSV320X gyroscope data, with precomputed norm (V)

- External 3-axis sensors with 16-bit data like magnetometer sensors, with precomputed norm (V)

- External 1-axis sensors with 24-bit data like pressure sensors

- Long counter value

- Internally filtered data and computed features, by properly configuring the machine learning core

- Internally calculated angles, with precomputed norm (V)

The norm (V) is internally computed with the following formula:

$$V = \sqrt{x^2 + y^2 + z^2}$$

The machine learning core allows configuring the device to compute features (like average, variance, peak-to-peak, energy, and so forth) or filters (like high pass, band pass, IIR1 and IIR2) applied to internal / external sensor data. For more details about the machine learning core capabilities, refer to application note AN6292.

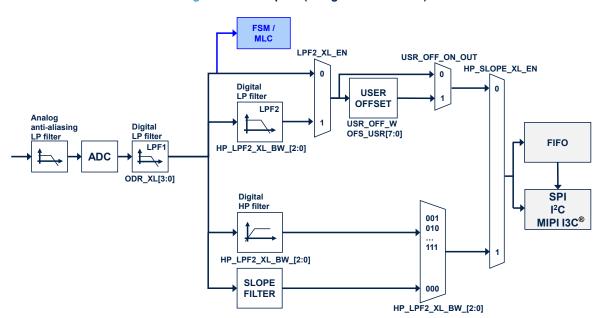

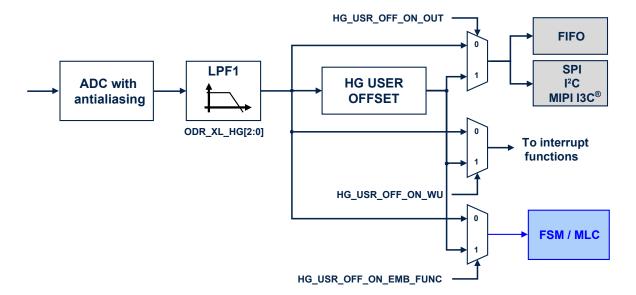

The following figures show the inputs of the finite state machine block in the low-*g* accelerometer, high-*g* accelerometer, and gyroscope digital chains. The position of the finite state machine (FSM) block in the digital chains is the same for all four connection modes available in the LSM6DSV320X.

AN6291 - Rev 1 page 12/75

Figure 6. FSM inputs (low-g accelerometer)

Figure 7. FSM inputs (high-g accelerometer)

AN6291 - Rev 1 page 13/75

**MLC**

Digital **FIFO** LPF1\_G\_EN LP filter LPF2 **ADC** 0 **Digital** LP filter 1 LPF1 ODR\_G\_[3:0] SPI / I<sup>2</sup>C / MIPI I3C® LPF1\_G\_BW\_[2:0] FSM /

Figure 8. FSM inputs (gyroscope)

The signal bandwidth of the accelerometer and gyroscope depends on the device configuration. For additional information, refer to AN6119 available at <a href="https://www.st.com">www.st.com</a>. The program block executes the configured program (code block) by processing the selected input signal and generating the corresponding program output signals, according to the purpose of the program.

Note:

The SINMUX command can be used by the user inside the program instructions section to dynamically switch the desired input signal for the program block. Refer to SINMUX (23h) for additional and detailed information about the SINMUX command.

AN6291 - Rev 1 page 14/75

#### 3.2.2 Code block

The FSM program $_x$  code block contains the state machine program. The structure of a single program is shown in the following figure. It is composed of:

- A data section, composed of a fixed part (same size for all the FSMs) and a variable part (specific size for each FSM)

- An instructions section, composed of conditions and commands

Each program can generate an interrupt $_x$  signal and modify the corresponding FSM\_OUTS $_x$  register value, according to processed sample sets coming from the PROGRAM $_x$  input signal that can be selected by issuing a specific SINMUX command.

PROGRAM<sub>x</sub> input

VARIABLE DATA SECTION

Interrupt<sub>x</sub>

VARIABLE DATA SECTION

FSM\_OUTS,

Figure 9. FSM program<sub>x</sub> code structure

All FSM programs are stored consecutively in a set of reserved embedded advanced features registers, as shown in the following figure. The maximum allowed size for each program is 256 bytes.

X = 1..8

Note: FSMs (according to all the embedded functions) have to be reconfigured each time the device is powered on.

AN6291 - Rev 1 page 15/75

FSM Program<sub>1</sub> Code **FIXED DATA SECTION** Interrupt<sub>1</sub>  $\mathsf{PROGRAM}_1$  input VARIABLE DATA SECTION FSM\_OUTS<sub>1</sub> **INSTRUCTIONS SECTION** SINMUX FSM Program<sub>2</sub> Code **FIXED DATA SECTION** Interrupt<sub>2</sub>  $\mathsf{PROGRAM}_2$  input **VARIABLE DATA SECTION** FSM\_OUTS<sub>2</sub> **INSTRUCTIONS SECTION SINMUX** FSM Program<sub>8</sub> Code **FIXED DATA SECTION** Interrupt<sub>8</sub> PROGRAM<sub>8</sub> input **VARIABLE DATA SECTION** FSM\_OUTS<sub>8</sub> **INSTRUCTIONS SECTION** SINMUX

Figure 10. FSM program<sub>x</sub> memory area

AN6291 - Rev 1 page 16/75

# 4 FSM interrupt status and signal

The FSM supports generating two different interrupt signals: the FSM program interrupt signal and the FSM long counter interrupt signal.

The FSM program interrupt signal is generated when the end state is reached (STOP command) or when some specific command is performed (OUTC / CONT / CONTREL commands). When an FSM program interrupt is generated, the corresponding temporary mask value is transmitted to its corresponding FSM\_OUTS embedded functions register.

The FSM long counter interrupt signal is generated when the long counter value, stored in the FSM\_LONG\_COUNTER\_L (48h) and FSM\_LONG\_COUNTER\_H (49h) embedded functions registers, reaches the configured long counter timeout value stored in the FSM\_LC\_TIMEOUT\_L (7Ah) and FSM\_LC\_TIMEOUT\_H (7Bh) embedded advanced features registers.

The FSM interrupt status can be checked by reading the dedicated register:

- FSM\_STATUS\_MAINPAGE (4Ah) register or FSM\_STATUS (13h) embedded functions register for the FSM interrupt status

- EMB\_FUNC\_STATUS\_MAINPAGE (49h) register or EMB\_FUNC\_STATUS (12h) embedded functions register for the long counter interrupt status

The FSM interrupt signal can be driven to the INT1/INT2 interrupt pin by setting the dedicated bit:

- INT1\_FSM[1:8]/INT2\_FSM[1:8] bit of the FSM\_INT1/FSM\_INT2 embedded functions register to 1

- INT1\_FSM\_LC/INT2\_FSM\_LC bit of the EMB\_FUNC\_INT1/EMB\_FUNC\_INT2 embedded functions register to 1

Note:

In both of the above cases it is mandatory to also enable routing the embedded functions events to the INT1/INT2 interrupt pin by setting the INT1\_EMB\_FUNC/INT2\_EMB\_FUNC bit of the MD1\_CFG/MD2\_CFG register.

The behavior of the interrupt signal is pulsed by default. The duration of the pulse is equal to 1 / MAX\_RATE seconds, where MAX\_RATE denotes the maximum rate of the enabled embedded functions.

Latched mode can be enabled by setting the EMB\_FUNC\_LIR bit of the PAGE\_RW (17h) embedded functions register to 1. In this case, the interrupt signal and the status bit are reset when reading:

- FSM\_STATUS\_MAINPAGE (4Ah) register or FSM\_STATUS (13h) embedded functions register for the FSM interrupt

- EMB\_FUNC\_STATUS\_MAINPAGE (49h) register or EMB\_FUNC\_STATUS (12h) embedded functions register for the long counter interrupt

AN6291 - Rev 1 page 17/75

# 5 Long counter

The long counter is a 15-bit temporary counter resource shared by all the available FSM programs and available to the user. Each FSM program can increment, decrement, or reset the long counter value by using the INCR, DECR, or RESET command, respectively. The long counter value is stored in the FSM\_LONG\_COUNTER\_L (48h) and FSM\_LONG\_COUNTER\_H (49h) embedded functions registers. The minimum (and default) long counter value is 0, while the maximum long counter value is the configured timeout value stored in the FSM\_LC\_TIMEOUT\_L (7Ah) and FSM\_LC\_TIMEOUT\_H (7Bh) embedded advanced features registers.

When the long counter value is equal to the configured long counter timeout value, the IS\_FSM\_LC status bit of the EMB\_FUNC\_STATUS\_MAINPAGE (49h) register and EMB\_FUNC\_STATUS (12h) embedded functions register is set to 1.

Details about the FSM long counter interrupt are available in Section 4: FSM interrupt status and signal.

This resource is common to all programs and does not need additional allocated resources in the [Variable Data Section].

Note: When FSM\_LC\_TIMEOUT is equal to 0, the long counter feature is disabled.

Note: The FSM\_LC\_TIMEOUT value must be set lower than 2<sup>15</sup> in 15-bit unsigned format.

AN6291 - Rev 1 page 18/75

# 6 Peak tracking

The LSM6DSV320X device allows detecting the intensity of shock events by exploiting the new peak-tracking feature, which is particularly useful in car crash detection or fall detection applications.

The high-*g* accelerometer peak-tracking feature allows monitoring the magnitude of the high-*g* accelerometer within a time window that can be defined by issuing dedicated commands from the finite state machine. When issuing the command related to the end of the monitoring window, this feature stores the high-*g* accelerometer three-axis components of the detected peak in the FIFO with a dedicated TAG.

Section 7.2: Peak-tracking outputs in FIFO and Section 10.2.8: SETM (F9h) show more details on its usage: an example is available in Section 13.5: Peak-tracking and extended sinmux.

The peak-tracking feature is automatically reset by the device when the monitoring window is closed. Anyway, it is possible to perform the reset by the host interface by setting the PT\_INIT bit of the EMB\_FUNC\_INIT\_B (67h) register to 1. This must be done in case the host has to disable one FSM while the peak-tracking feature is still running.

AN6291 - Rev 1 page 19/75

# 7 FIFO

The LSM6DSV320X finite state machine allows storing FSM events or peak-tracking output data in the FIFO buffer. This is particularly useful when the host enters a sleep or power-down state in which it cannot read and process IMU data. Keeping the LSM6DSV320X device powered on allows running edge processing, whose outputs can be retrieved by the host the next time it enters the run state.

Details about the LSM6DSV320X FIFO configuration are available in AN6119.

## 7.1 FSM events in FIFO

The LSM6DSV320X finite state machine supports storing FSM events in the FIFO buffer by setting the FSM\_FIFO\_EN bit of the EMB\_FUNC\_FIFO\_EN\_B (45h) embedded functions register to 1.

The FSM program can store the following FSM events in the FIFO buffer:

- Events related to the long counter timeout, which are stored in FIFO every time the long counter value reaches the configured timeout value.

- Events related to the long counter value, which are stored in FIFO every time a specific SETM command, needed to store the long counter value, is issued. Refer to the dedicated paragraph for more details on its usage.

- Events related to the detected motion pattern, which are stored in FIFO every time a OUTC / CONT / CONTREL command is issued (so when the FSM writes its OUTSx registers or sets its IS\_FSMx bit of the FSM STATUS MAINPAGE (4Ah) register or FSM STATUS (13h) embedded functions register).

All the above cases are identified by a FIFO tag value readable from the FIFO\_DATA\_OUT\_TAG (78h) register equal to 1Fh, but they can be distinguished by decoding the values of the FIFO\_DATA\_OUT\_X\_L (79h) and FIFO\_DATA\_OUT\_X\_H (7Ah) registers. The FIFO\_DATA\_OUT\_Y\_L (7Bh), FIFO\_DATA\_OUT\_Y\_H (7Ch), FIFO\_DATA\_OUT\_Z\_L (7Dh) and FIFO\_DATA\_OUT\_Z\_H (7Eh) registers contain the timestamp value corresponding to the generated FSM event. The format of the FSM events in FIFO is indicated in the following table.

| Event                      | FIFO_DATA_<br>OUT_TAG[7:3]<br>(78h) | FIFO_DATA_<br>OUT_X_L<br>(79h)  | FIFO_DATA_<br>OUT_X_H<br>(7Ah) | FIFO_DATA_<br>OUT_Y_L<br>(7Bh) | FIFO_DATA_<br>OUT_Y_H<br>(7Ch) | FIFO_DATA_<br>OUT_Z_L<br>(7Dh) | FIFO_DATA_<br>OUT_Z_H<br>(7Eh) |

|----------------------------|-------------------------------------|---------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| Long<br>counter<br>timeout | 0x1F                                | 0x00                            | 0x00                           | TIMESTAMP0                     | TIMESTAMP1                     | TIMESTAMP2                     | TIMESTAMP3                     |

| OUTSx /<br>IS_FSMx         | 0x1F                                | OUTSx                           | Index of<br>FSM <sup>(1)</sup> | TIMESTAMP0                     | TIMESTAMP1                     | TIMESTAMP2                     | TIMESTAMP3                     |

| Long                       | 0x1F                                | FSM_LONG_<br>COUNTER_L<br>(48h) | 0x09                           | TIMESTAMP0                     | TIMESTAMP1                     | TIMESTAMP2                     | TIMESTAMP3                     |

| counter<br>value           | 0x1F                                | FSM_LONG_<br>COUNTER_H<br>(49h) | 0x0A                           | TIMESTAMP0                     | TIMESTAMP1                     | TIMESTAMP2                     | TIMESTAMP3                     |

Table 6. Finite state machine events in FIFO

The high part of the long counter value, identified by a FIFO\_DATA\_OUT\_X\_H (7Ah) register value equal to 0Ah, is stored in FIFO only if the FSM\_LONG\_COUNTER\_H (49h) register value is not zero.

AN6291 - Rev 1 page 20/75

<sup>1.</sup> FSMs are indexed from 1 to 8.

# 7.2 Peak-tracking outputs in FIFO

The LSM6DSV320X finite state machine supports storing the peak-tracking output data in the FIFO buffer every time a specific SETM command, needed to stop the peak-tracking monitoring, is issued. Refer to Section 10.2.8: SETM (F9h) for more details on its usage.

The peak-tracking output data are identified by a FIFO tag value readable from the FIFO\_DATA\_OUT\_TAG (78h) register equal to 18h. The FIFO\_DATA\_OUT\_X\_L (79h), FIFO\_DATA\_OUT\_X\_H (7Ah), FIFO\_DATA\_OUT\_Y\_L (7Bh), FIFO\_DATA\_OUT\_Y\_H (7Ch), FIFO\_DATA\_OUT\_Z\_L (7Dh), and FIFO\_DATA\_OUT\_Z\_H (7Eh) registers contain the X, Y, and Z high-g accelerometer data in half-precision floating-point format. The format of peak-tracking outputs in FIFO is indicated in the following table.

Table 7. Format of peak-tracking output data

| Event                               | FIFO_DATA_   | FIFO_DATA_       | FIFO_DATA_ | FIFO_DATA_ | FIFO_DATA_ | FIFO_DATA_              | FIFO_DATA_ |  |

|-------------------------------------|--------------|------------------|------------|------------|------------|-------------------------|------------|--|

|                                     | OUT_TAG[7:3] | OUT_X_L          | OUT_X_H    | OUT_Y_L    | OUT_Y_H    | OUT_Z_L                 | OUT_Z_H    |  |

|                                     | (78h)        | (79h)            | (7Ah)      | (7Bh)      | (7Ch)      | (7Dh)                   | (7Eh)      |  |

| Peak-<br>tracking<br>output<br>data | 0x18         | X <sup>(1)</sup> |            | Y          | (1)        | <b>Z</b> <sup>(1)</sup> |            |  |

<sup>1.</sup> High-g accelerometer data in half-precision floating-point format.

AN6291 - Rev 1 page 21/75

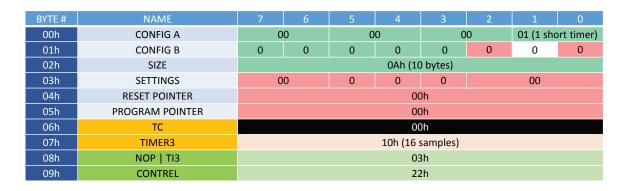

# 8 Fixed Data Section

The [Fixed Data Section] stores information about the [Variable Data Section] and the [Instructions Section]. It is composed of six bytes and it is located at the beginning of each program. The following figure shows the structure of the [Fixed Data Section].

Figure 11. [Fixed Data Section]

|   | NAME            | 7                    | 6                 | 5            | 4     | 3              | 2        | 1             | 0   |

|---|-----------------|----------------------|-------------------|--------------|-------|----------------|----------|---------------|-----|

| 0 | CONFIG A        | NR_THRESH(1:0)       |                   | NR_MASK(1:0) |       | NR_LTIMER(1:0) |          | NR_TIMER(1:0) |     |

| 1 | CONFIG B        | DES                  | EXT_SINMUX        | ANGLE        | PAS   | DECTREE        | STOPDONE | 0             | JMP |

| 2 | SIZE            |                      | PROGRAM SIZE(7:0) |              |       |                |          |               |     |

| 3 | SETTINGS        | MASKS                | EL(1:0)           | SIGNED       | R_TAM | THRS3SEL       |          | IN_SEL(2:0)   |     |

| 4 | RESET POINTER   | RESET POINTER(7:0)   |                   |              |       |                |          |               |     |

| 5 | PROGRAM POINTER | PROGRAM POINTER(7:0) |                   |              |       |                |          |               |     |

Note:

The green colored bits have to be set according to program purposes, while the red colored bits have to be set to 0 when the program is loaded into the embedded advanced features registers and are handled by the FSM program. The white colored bits must be written to 0 for the correct operation of the device.

The first two bytes store the amount of resources used by the program, while other bytes are used by the device to store the program status.

- With CONFIG\_A it is possible to declare:

- Up to three thresholds (NR THRESH bits)

- Up to three masks (NR MASK bits)

- Up to two long (16 bits) timers (NR\_LTIMER bits)

- Up to two short (8 bits) timers (NR\_TIMER bits)

- With CONFIG B it is possible to declare:

- A decimation factor for incoming ODR (DES bit)

- An extended sinmux capability, used to select as FSM input, the long counter value or the value of a filter/feature computed by the machine learning core (EXT\_SINMUX bit)

- Usage of gyroscope angles that have to be computed and stored (ANGLE bit)

- Usage of previous axis signs that have to be computed and stored (PAS bit)

- Usage of a decision tree interface (DECTREE bit)

- The SIZE parameter stores the length in bytes of the whole program (sum of [Fixed Data Section] size,

[Variable Data Section] size and Instruction section size). The SIZE byte must always be an even number.

If the size of the program is odd, an additional STOP state has to be added at the bottom of the Instruction section.

- The SETTINGS parameter stores the current program status (selected mask, selected threshold, input signal, and so forth).

- The RESET POINTER (RP) and PROGRAM POINTER (PP) store respectively the reset pointer relative

address (jump address when a RESET condition is true) and the program pointer relative address (address

of the instruction under execution during the current sample time). Address 00h is referred to CONFIG\_A

byte.

Note:

When PP is equal to 0, the device automatically runs the start routine (refer to Section 12: Start routine for additional information) in order to properly initialize the internal variables and parameters of the state machine. This is mandatory for a correct operation of the device.

AN6291 - Rev 1 page 22/75

# 9 Variable Data Section

The [Variable Data Section] is located below the corresponding [Fixed Data Section] of a program, and its size depends on the amount of resources defined in the [Fixed Data Section].

Each resource enumerated in the [Fixed Data Section] is then allocated in the [Variable Data Section], with the proper size and at the proper position. The following figure shows the structure of the [Variable Data Section].

NAME THRESH1 THRESH1(15:0) THRESH2 THRESH2(15:0) 10 THRESH3 THRESH3(15:0) SINMUX\_ADDR\_B EXT\_SINMUX THRXYZ1 NEXT\_ODR SINMUX ADDR C 13 IN SEL(3) 0 MASKA MASKA(7:0) TMASKA(7:0) **TMASKA** MASKB(7:0) 17 TMASKB(7:0) TMASKR MASKC(7:0) MASKC **TMASKC** TMASKC(7:0) DELTAT DELTAT(15:0) 21 DX(15:0) DX 23 24 DY DY(15:0) 25 DZ(15:0) 28 DV DV(15:0) TC TC(15:0) or TC(7:0) TIMER1(15:0) TIMER1 TIMER2 TIMER2(15:0) 36 TIMER3 TIMER3(7:0) TIMER4 TIMER4(7:0) 38 DEST DEST(7:0) DESC DESC(7:0) SIGN V CANGLE MSKIT SIGN Z PAS SCTC MSKITEQ SIGN X SIGN Y 41 DECTREE DTSEL(1:0)

Figure 12. [Variable Data Section]

Note:

The orange colored bits have to be set according to program purposes, while the black colored bits must be set to 0 when the program is loaded into the embedded advanced features registers and are handled by the FSM program. The white colored bits must be set to 0 for the correct operation of the device.

As shown in the table above, the maximum size of the [Variable Data Section] is 36 bytes. If the program requires fewer resources, the size allocated for the [Variable Data Section] is lower. Bytes from 0 to 5, not shown in the table above, are allocated for the CONFIG A, CONFIG B, SIZE, SETTINGS, RP, and PP bytes of the [Fixed Data Section].

Note:

The usage of the resources declared in the [Fixed Data Section] starts always from the lowest resource number. For example if the user defines NR\_THRESH = 10 in the [Fixed Data Section] (two thresholds defined), the available thresholds that can be used in the program are THRESH1 and THRESH2, while THRESH3 is not available and the bytes corresponding to THRESH3 are not allocated (all the resources below THRESH2 are shifted up).

AN6291 - Rev 1 page 23/75

#### 9.1 Thresholds

Threshold resources are used to check and validate values assumed by the selected input signal (through the SINMUX command) and axis (through MASKS) in comparison conditions.

The unit of measurement of the threshold is that of the selected signal:

- If the LSM6DSV320X low-g accelerometer signal is selected, the unit of the threshold is [g].

- If the LSM6DSV320X high-g accelerometer signal is selected, the unit of the threshold is [hg].

- If the LSM6DSV320X gyroscope signal is selected, the unit of the threshold is [rad/sec].

- If the LSM6DSV320X integrated gyroscope signal is selected, the unit of the threshold is [rad].

- If the external sensor signal is selected, the unit is the same used after applying the sensitivity.

- If the long counter value is selected, the threshold is expressed in 15-bit unsigned format.

- If the MLC filtered signal or computed feature is selected, the unit of the threshold is the same as that of the selected filtered signal or the selected computed feature.

Thresholds can be signed or unsigned. It is possible to move from signed to unsigned mode by using the SSIGN0 / SSIGN1 commands. In signed mode, the signal and threshold keep their original sign in the comparison. In unsigned mode, the comparison is performed between the absolute values of both signal and threshold.

By setting the NR\_THRESH[1:0] bits of CONFIG\_A byte, the corresponding number of thresholds can be configured in the [Variable Data Section], as described below:

- NR THRESH[1:0] = 00: no thresholds are allocated in the [Variable Data Section].

- NR\_THRESH[1:0] = 01: only THRESH1[15:0] is allocated in the [Variable Data Section].

- NR THRESH[1:0] = 10: THRESH1[15:0] and THRESH2[15:0] are allocated in the [Variable Data Section].

- NR\_THRESH[1:0] = 11: THRESH1[15:0], THRESH2[15:0] and THRESH3[15:0] are allocated in the [Variable Data Section].

#### Involved commands:

- STHR1 / STHR2

- SELTHR1 / SELTHR3

- SSIGN0 / SSIGN1

## Involved conditions:

- GNTH1 / GNTH2 / GLTH1 / GRTH1

- LNTH1 / LNTH2 / LLTH1 / LRTH1

#### 9.2 Extended sinmux

The extended sinmux resource is used to select as FSM inputs the long counter value (SINMUX with argument 08h), the high-g accelerometer data (SINMUX with first argument 09h), or a feature / filter computed by the machine learning core (SINMUX with first argument 09h). In addition, this resource is also required when there is the need for executing multiple conditions in one ODR (THRXYZ1).

By setting the EXT\_SINMUX bit of CONFIG\_B byte to 1, the EXT\_SINMUX bytes are allocated in the [Variable Data Section] (the EXT\_SINMUX bytes values are automatically managed by the device). This is mandatory if at least one of the commands listed below is expected to be used in the program.

Involved commands:

- SINMUX with first argument equal to 08h (long counter selection) or 09h (high-g accelerometer data or MLC feature / filter selection)

- THRXYZ0, THRXYZ1

Involved conditions:

N/A

AN6291 - Rev 1 page 24/75

# 9.3 Masks / temporary masks

Mask resources are used to enable or disable mask action on the input data (X, Y, Z, V) when a condition is performed. If a mask bit is set to 1, then the corresponding axis and sign is enabled, otherwise it is disabled. In case the input data is generated by an external sensor with 1-axis in 3-byte data format, its data is available in the X channel of the masks. Masks are used in threshold comparison conditions or zero-crossing detection. Masks allow inverting the sign of the input signal by enabling the corresponding axis bit with a minus sign. Masks are composed of 8 bits (2 bits for each axis), as shown below:

For each axis, it is possible to configure four different mask settings:

- 1. Positive axis bit = 0 / negative axis bit = 0, axis is disabled.

- 2. Positive axis bit = 0 / negative axis bit = 1, axis with opposite sign is enabled.

- 3. Positive axis bit = 1 / negative axis bit = 0, axis with current sign is enabled.

- 4. Positive axis bit = 1 / negative axis bit = 1, axis with current sign and axis with opposite sign are enabled.

When a program is enabled, the value of each mask is copied inside the related temporary mask (TM), which is used during execution of conditions. Each time a condition is issued, the result of the condition is stored again in the temporary mask (it affects also consecutive conditions).

#### Example:

- GNTH1 condition

- THRESH1 =  $0.50 \, q$

- MASKA = 12h (00010010b) → -Y and +V are enabled

- Current input accelerometer sample = [0.72 -0.45 0.77 1.15]

| TM before the condition | 0    | 0     | 0     | 1    | 0    | 0     | 1    | 0     |

|-------------------------|------|-------|-------|------|------|-------|------|-------|

| Accelerometer sample    | 0.72 | -0.72 | -0.45 | 0.45 | 0.77 | -0.77 | 1.15 | -1.15 |

| TM after the condition  | 0    | 0     | 0     | 0    | 0    | 0     | 1    | 0     |

It is possible to reset the temporary mask value to the mask value in the following conditions:

- Anytime there is a reset condition

- When executing a CONTREL command

- When executing a REL command

- After each true next condition, if an SRTAM1 command has been previously issued

By setting the NR\_MASK[1:0] bits of CONFIG\_A byte, the corresponding number of masks can be configured in the [Variable Data Section], as described below:

- NR\_ MASK[1:0] = 00: no masks are allocated in the [Variable Data Section].

- NR\_MASK[1:0] = 01: only MASKA[7:0]/TMASKA[7:0] are allocated in the [Variable Data Section].

- NR\_ MASK[1:0] = 10: MASKA[7:0]/TMASKA[7:0] and MASKB[7:0]/TMASKB[7:0] are allocated in the [Variable Data Section].

- NR\_ MASK[1:0] = 11: MASKA[7:0]/TMASKA[7:0], MASKB[7:0]/TMASKB[7:0], and MASKC[7:0]/TMASKC[7:0] are allocated in the [Variable Data Section].

#### Involved commands:

- SELMA / SELMB / SELMC

- SMA / SMB / SMC

- REL

- SRTAM0 / SRTAM1

## Involved conditions:

- GNTH1 / GNTH2 / GLTH1 / GRTH1

- LNTH1 / LNTH2 / LLTH1 / LRTH1

- PZC / NZC

AN6291 - Rev 1 page 25/75

# 9.4 Angle calculation

Angle resources can be used instead of angular velocity data when a condition is issued. The angle computation is performed internally: gyroscope data are automatically multiplied by the DELTAT value, and the results are added to corresponding angle axis bytes (DX, DY, DZ and DV). This feature is enabled when the ANGLE bit of the CONFIG B byte of the [**Fixed Data Section**] is set to 1. The integration is performed each time a new sample is processed by the FSM, independently of the selected signal.

There are two reset-angle modalities:

- By default, angular velocity integration is cleared each time a reset or next condition is true. In this case, computed angles (DX, DY, DZ and DV bytes) restart from zero when a new sample arrives.

- If the program contains a CANGLE command, a different reset-angle modality is used. In this case, integrated angles are cleared:

- If a CANGLE command is performed (when a new sample arrives)

- Only if a reset condition is true

By setting the ANGLE bit of the CONFIG\_B byte to 1, 10 bytes (DELTAT, DX, DY, DZ and DV) are allocated in the [Variable Data Section]: DELTAT resource has to be set equal to current FSM\_ODR cycle time in seconds (half floating point (16 bits) format). If a CANGLE command is expected to be used, also the PAS bit of the CONFIG\_B byte has to be set to 1.

Involved commands:

CANGLE

Involved conditions:

- GNTH1 / GNTH2 / GLTH1 / GRTH1

- LNTH1 / LNTH2 / LLTH1 / LRTH1

- PZC / NZC

## 9.5 TC and timers

Timer resources are used to manage event durations. It is possible to declare two kinds of timer resources: long timers (16 bits) and short timers (8 bits). The time base is set by the FSM\_ODR[2:0] bits of the FSM\_ODR (5Fh) register, including the decimation factor if used. Long timer resources are called TI1 and TI2, while short timer resources are called TI3 and TI4. An additional internal timer counter (TC) is used as temporary counter to check if a timer has elapsed. The TC value can be preloaded with two different modalities, selectable by using the SCTC0 / SCTC1 commands:

- SCTC0 mode (default): when the program pointer moves to a state with a timeout condition, the TC value

is always preloaded to the corresponding timer value. In this modality, the timer duration affects one state

only.

- SCTC1 mode: when the program pointer moves to a state with a timeout condition, there are two different scenarios depending on which timer is used in the new state:

- If the timer used in the new state is different from the timer used in the previous state, the TC value is preloaded to the corresponding timer value. In this modality, the timer duration affects one state only (same as SCTC0 mode).

- If the timer used in the new state is the same used in the previous state, the TC value is not preloaded. The TC value continues to be decreased starting from its previous value. In this modality, the timer duration could affect more states.

The TC value is decreased by 1 each time a new sample occurs. If TC reaches 0, the condition is true. Example:

- Timer TI3 is set equal to 10 samples. Consider the following states:

- S0 SCTC0 or SCTC1

- S1 TI3 | GNTH1

- S2 TI3 | LNTH2

- S3 TI3 | GNTH1

- TI3 = 0Ah (10 samples)

AN6291 - Rev 1 page 26/75

Depending on S0, there are two different state machine behaviors:

- SCTC0 case: the TC byte is always preloaded (when the program pointer moves to states S1, S2, and S3)

and each condition is checked for a maximum of 10 samples. This means that all conditions can be verified

in a maximum of 30 samples.

- SCTC1 case: the TC byte is preloaded only when the program pointer moves to S1 (and is not preloaded when it moves to S2 and S3), and all conditions have to be verified in a maximum of 10 samples.

SCTC1 modality is typically used when different conditions have to be verified in the same time window.

By setting the NR\_LTIMER[1:0] bits of the CONFIG\_A byte, the corresponding number of long timers can be configured in the [Variable Data Section], as described below:

- NR LTIMER[1:0] = 00: no long timers are allocated in the [Variable Data Section].

- NR LTIMER[1:0] = 01: TIMER1[15:0] is allocated in the [Variable Data Section]

- NR\_LTIMER(1:0) = 10: TIMER1[15:0] and TIMER2[15:0] are allocated in the [Variable Data Section].

By setting the NR\_TIMER[1:0] bits of the CONFIG\_A byte, the corresponding number of short timers can be configured in the [Variable Data Section], as described below:

- NR\_TIMER[1:0] = 00: no short timers are allocated in the [Variable Data Section].

- NR\_TIMER[1:0] = 01: TIMER3[7:0] is allocated in the [Variable Data Section].

- NR TIMER[1:0] = 10: TIMER3[7:0] and TIMER4[7:0] are allocated in the [Variable Data Section].

Below the size of the TC resource:

- If NR\_LTIMER[1:0] = 00 and NR\_TIMER[1:0] = 00, the TC resource is not allocated.

- If NR\_LTIMER[1:0] = 00 and NR\_TIMER[1:0] ≠ 00, the TC resource occupies one byte.

- If NR\_LTIMER[1:0] ≠ 00 and NR\_TIMER[1:0] = 00, the TC resource occupies two bytes.

- If NR LTIMER[1:0] ≠ 00 and NR TIMER[1:0] ≠ 00, theTC resource occupies two bytes.

Involved commands:

- STIMER3 / STIMER4

- SCTC0 / SCTC1

Involved conditions:

TI1 / TI2 / TI3 / TI4

#### 9.6 Decimator

The decimator resource is used to reduce the sample rate of the data going to the finite state machine.

By setting the DES bit of the CONFIG\_B byte to 1, the DEST and DESC bytes can be properly configured in the [Variable Data Section]. The DEST value is the desired decimation factor, while the DESC value is the internal counter (automatically managed by the device). The decimation factor is related to the FSM\_ODR[2:0] bits of the FSM\_ODR (5Fh) register, according to the following formula:

PROGRAM ODR = FSM ODR / DEST

At startup:

DESC = DEST (initial decimation value)

When the sample clock occurs:

DESC = DESC - 1

When DESC is equal to 0, the current sample is used as the new input for the state machine, and the DESC value is set to the initial decimation value again.

Involved commands:

N/A

Involved conditions:

N/A

Note:

Since a DEST value equal to 0 is invalid and a DEST value equal to 1 means "no decimation", the minimum meaningful DEST value is 2.

AN6291 - Rev 1 page 27/75

# 9.7 Previous axis sign

The previous axis sign resource is mainly used to store the sign of the previous sample: this information is used in zero-crossing conditions. In addition, it is also used to store other information such as the selected timer reset method (SCTC0 or SCTC1), the clear angle flag (CANGLE) used to reset the integrated gyroscope data (DX, DY, DZ, and DV bytes inside the [Variable Data Section]) and the selected interrupt mask type (MSKIT, MSKITEQ, or UMSKIT).

By setting the PAS bit of the CONFIG\_B byte to 1, the PAS byte is allocated in the [Variable Data Section] (the PAS byte value is automatically managed by the device). This is mandatory if at least one of the commands or conditions listed below is expected to be used in the program.

Involved commands:

SCTC0 / SCTC1 / CANGLE / MSKIT / MSKITEQ / UMSKIT

Involved conditions:

PZC / NZC

Note: If the SSIGNO command is performed, NZC and PZC are used as a generic ZC condition.

## 9.8 MLC interface

The MLC interface of the FSM includes the possibility of implementing conditions on the output of a decision tree or on the value of a computed filter / feature. This can be very useful when a machine learning logic or a custom filter is expected to be combined with an FSM program.

The output of a decision tree is accessible by using the CHKDT condition, which can be used to evaluate the result of one of the four decision trees available inside the machine learning core algorithms.

By setting the DECTREE bit of CONFIG\_B byte to 1, the DECTREE byte can be properly configured in the **[Variable Data Section**]. The DECTREE byte contains information about the progressive number of the decision trees to be triggered (DTSEL[1:0] bits, from 0 to 3) and the corresponding expected value (DTRES[3:0] bits, from 0 to 15).

The value of a filter / feature computed by the MLC can be selected using the extended sinmux feature.

By setting the EXT\_SINMUX bit of the CONFIG\_B byte to 1, the EXT\_SINMUX bytes are allocated in the [Variable Data Section] (the EXT\_SINMUX bytes are automatically managed by the device). Refer to Section 9.2: Extended sinmux and Section 10.2.22: SINMUX (23h) for more details about how to select a filter / feature computed by the MLC.

Note: Using the SETP command allows reconfiguring dynamically the DECTREE byte inside the program flow in order to trigger a different decision tree and its expected value. Details about the SETP command are provided in its

dedicated paragraph.

Note: Refer to AN6292 for more details about how to configure the MLC.

Involved commands:

SINMUX

Involved conditions:

CHKDT

AN6291 - Rev 1 page 28/75

# 10 Instructions Section

The [Instructions Section] is defined below the [Variable Data Section] and is composed of a series of states that implement the algorithm logic. Each state is characterized by one 8-bit operation code (opcode), and each opcode can implement a command or a RESET/NEXT condition:

- Commands are used to perform special tasks for flow control, output, and synchronization. Some commands may have parameters, executed as one single-step command.

- RESET/NEXT conditions are a combination of two conditions (4 bits for RESET condition and 4 bits for NEXT condition) that are used to reset or continue the program flow.

The opcodes have a direct effect on registers and internal state machine memories. For some opcodes, additional side effects can occur (such as update of status information).

A RESET/NEXT condition or a command, eventually followed by parameters, represents an instruction, also called program state. They are the building blocks of the instructions section of a program.

#### 10.1 RESET/NEXT conditions

The RESET/NEXT conditions are used to reset or continue the program flow, and are composed of one single state.

The RESET condition is defined in the opcode MSB part while the NEXT condition is defined in the opcode LSB part.

The RESET/NEXT conditions affect the program flow as indicated below:

- A transition to the reset pointer occurs whenever the RESET condition is true (PP = RP).

- A transition to the next state occurs whenever the RESET condition is false and the NEXT condition is true (PP = PP + 1).

- No transitions occur when both the RESET and NEXT conditions are false.

As shown in the following figure, the RESET condition is always performed before the NEXT condition that is evaluated only when the RESET condition is not satisfied.

go to Reset Pointer

YES

RESET

CONDITION

SATISFIED

YES

RESET

CONDITION

SATISFIED

YES

go to State n+1

Figure 13. Single state description

By default, a single RESET/NEXT condition is executed when a new data sample is processed by the FSM, but it is possible to execute multiple conditions on the same data sample by using the THRXYZ1/THRXYZ0 commands. Details about how to enable this mode can be found in Section 10.2.28: THRXYZ1 (F7h) and Section 10.2.29: THRXYZ0 (F8h).

Note:

The RESET condition is always evaluated before the NEXT condition. By default, the reset pointer (RP) is set to the first state, but it is possible to dynamically change the reset pointer (RP) by using SRP/CRP commands.

AN6291 - Rev 1 page 29/75

Since a condition is coded over four bits, a maximum of 16 different conditions can be coded: the list of available conditions is shown in the following table. There are four types of conditions:

- Timeouts: these conditions are true when the TC counter, preloaded with a timer value, reaches zero.

- Threshold comparisons: these conditions are true when enabled inputs such as the accelerometer X, Y, Z axis or norm are higher (or lower) than a programmed threshold.

$$V = \sqrt{x^2 + v^2 + z^2}$$

- Zero-crossing detection: these conditions are true when an enabled input crosses the zero level.

- Decision tree output check: these conditions are true when the selected decision tree output is equal to the desired value (see Section 9.8: MLC interface for more details).

| Table | - 0  | Canditiana |

|-------|------|------------|

| iab   | e ö. | Conditions |

| OP code | Mnemonic | Description                                                | Note                                                     | Resources needed                 |

|---------|----------|------------------------------------------------------------|----------------------------------------------------------|----------------------------------|

| 0h      | NOP      | No operation                                               | Execution moves to another condition                     | N/A                              |

| 1h      | TI1      | Timer 1 (16-bit value) valid                               |                                                          | TC, TIMER1                       |

| 2h      | TI2      | Timer 2 (16-bit value) valid                               | No evaluation of data complex                            | TC, TIMER1, TIMER2               |

| 3h      | TI3      | Timer 3 (8-bit value) valid                                | No evaluation of data samples                            | TC, TIMER3                       |

| 4h      | TI4      | Timer 4 (8-bit value) valid                                |                                                          | TC, TIMER3, TIMER4               |

| 5h      | GNTH1    | Any triggered axis ≥ THRESH1                               |                                                          | THRESH1, one<br>MASK             |

| 6h      | GNTH2    | Any triggered axis ≥ THRESH2                               |                                                          | THRESH1,<br>THRESH2, one<br>MASK |

| 7h      | LNTH1    | Any triggered axis < THRESH1                               |                                                          | THRESH1, one<br>MASK             |

| 8h      | LNTH2    | Any triggered axis < THRESH2                               | Input signal, triggered with mask, compared to threshold | THRESH1,<br>THRESH2, one<br>MASK |

| 9h      | GLTH1    | All triggered axes ≥ THRESH1                               |                                                          | THRESH1, one<br>MASK             |

| Ah      | LLTH1    | All triggered axes < THRESH1                               |                                                          | THRESH1, one<br>MASK             |

| Bh      | GRTH1    | Any triggered axis ≥ -THRESH1                              |                                                          | THRESH1, one<br>MASK             |

| Ch      | LRTH1    | Any triggered axis < -THRESH1                              |                                                          | THRESH1, one<br>MASK             |

| Dh      | PZC      | Any triggered axis crossed zero value, with positive slope | Input signal, triggered with mask,                       | PAS                              |

| Eh      | NZC      | Any triggered axis crossed zero value, with negative slope | crossing zero value                                      | PAS                              |

| Fh      | CHKDT    | Check result from a decision tree vs. expected             | Requires machine learning core configuration             | DECTREE                          |

The last column of the table above indicates the resource needed by the conditions. These resources are allocated inside the [Variable Data Section] and can be different between one FSM and another. For correct FSM behavior, it is mandatory to set the amount of resources needed by each program in the [Fixed Data Section].

Note:

Having the same condition in the NEXT and RESET positions does not make sense. Consequently, opcodes such as 11h do not implement the TI1 | TI1 condition, but implement some commands: for example, the opcode 11h implements the CONT command.

AN6291 - Rev 1 page 30/75

Moreover, it is not possible to perform the following conditions because they are recognized as commands:

- PZC | CHKDT opcode (0xDF) is equal to SMB opcode.

- NZC | CHKDT opcode (0xEF) is equal to MSKITEQ opcode.

- CHKDT | GNTH1 opcode (0xF5) is equal to MSKIT opcode.

- CHKDT | LNTH1 opcode (0xF7) is equal to THRXYZ1 opcode.

- CHKDT | GNTH2 opcode (0xF6) is equal to RSTLC opcode.

- CHKDT | LNTH2 opcode (0xF8) is equal to THRXYZ0 opcode.

- CHKDT | GLTH1 opcode (0xF9) is equal to SETM opcode.

- CHKDT | PZC opcode (0xFD) is equal to DECR opcode.

- CHKDT | NZC opcode (0xFE) is equal to SMC opcode.

AN6291 - Rev 1 page 31/75

# 10.1.1 NOP (0h)

Description: NOP (no operation) is used as filler for the RESET/NEXT pair for some particular conditions, which do not need an active opposite condition.

#### Actions:

- If NOP is in the RESET condition, the FSM evaluates only the NEXT condition.

- If NOP is in the NEXT condition, the FSM evaluates only the RESET condition.

#### 10.1.2 TI1 (1h)

Description: TI1 condition counts and evaluates the counter value of the TC bytes.

#### Action:

- When the program pointer moves to a state with a TI1 condition, TC = TIMER1.

- When a new data sample (X, Y, Z, V) is processed by the FSM, then TC = TC 1:

- If TC > 0, continue comparisons in the current state.

- If TC = 0, the condition is valid:

- If TI1 is in the RESET position, PP = RP.

- If TI1 is in the NEXT position, PP = PP + 1.

Note: Details about how to use timers inside the THRXYZ1 / THRXYZ0 commands can be found in Section 10.2.28: THRXYZ1 (F7h) and Section 10.2.29: THRXYZ0 (F8h).

#### 10.1.3 Tl2 (2h)

Description: TI2 condition counts and evaluates the counter value of the TC bytes.

#### Action:

- When the program pointer moves to a state with a TI2 condition, TC = TIMER2.

- When a new data sample (X, Y, Z, V) is processed by the FSM, then TC = TC − 1:

- If TC > 0, continue comparisons in the current state.

- If TC = 0, the condition is valid:

- If TI2 is in the RESET position, PP = RP.

- If TI2 is in the NEXT position, PP = PP + 1.

Details about how to use timers inside the THRXYZ1 / THRXYZ0 commands can be found in Section 10.2.28: THRXYZ1 (F7h) and Section 10.2.29: THRXYZ0 (F8h).

# 10.1.4 TI3 (3h)

Note:

Description: TI3 condition counts and evaluates the counter value of the TC byte. Action:

- When the program pointer moves to a state with a TI3 condition, TC = TIMER3.

- When a new data sample (X, Y, Z, V) is processed by the FSM, then TC = TC 1:

- If TC > 0, continue comparisons in the current state.

- If TC = 0, the condition is valid:

- If TI3 is in the RESET position, PP = RP.

- If TI3 is in the NEXT position, PP = PP + 1.

Note: Details about how to use timers inside the THRXYZ1 / THRXYZ0 commands can be found in Section 10.2.28: THRXYZ1 (F7h) and Section 10.2.29: THRXYZ0 (F8h).

AN6291 - Rev 1 page 32/75

## 10.1.5 TI4 (4h)

Description: TI4 condition counts and evaluates the counter value of the TC byte.

#### Action:

- When the program pointer moves to a state with a TI4 condition, TC = TIMER4.

- When a new data sample (X, Y, Z, V) is processed by the FSM, then TC = TC − 1:

- If TC > 0, continue comparisons in the current state.

- If TC = 0, the condition is valid:

- If TI4 is in the RESET position, PP = RP.

- If TI4 is in the NEXT position, PP = PP + 1.

Note: Details about how to use timers inside the THRXYZ1 / THRXYZ0 commands can be found in Section 10.2.28: THRXYZ1 (F7h) and Section 10.2.29: THRXYZ0 (F8h).

#### 10.1.6 GNTH1 (5h)

Description: GNTH1 condition is valid if any triggered axis of the FSM processed data sample (X, Y, Z, V) is greater than or equal to the threshold 1 level. The threshold used during the comparison depends on the THRS3SEL bit in the SETTINGS byte of the [**Fixed Data Section**] as described below:

- THRS3SEL = 0 (default value or value assumed after the SELTHR1 command is performed): the threshold used is THRESH1.

- THRS3SEL = 1 (value assumed after the SELTHR3 command is performed): the threshold used is THRESH3.

Note: In case the "+" and "-" signs of the same axis are enabled, it is enough that one of them satisfies the condition, which means applying an OR operator (for example,  $+X \ge threshold$ ).

#### Action:

- When a new sample set (X, Y, Z, V) occurs, check the condition:

- If GNTH1 is valid and it is in the RESET position, PP = RP.

- If GNTH1 is valid and it is in the NEXT position, PP = PP + 1.

# 10.1.7 GNTH2 (6h)

Description: GNTH2 condition is valid if any triggered axis of the FSM processed data sample (X, Y, Z, V) is greater than or equal to the threshold 2 level. The threshold used during the comparison is THRESH2.

WITIC

Note:

Note:

In case the "+" and "-" signs of the same axis are enabled, it is enough that one of them satisfies the condition, which means applying an OR operator (for example,  $+X \ge threshold$ ).

#### Action: