## L9965A/L99BM218 Hardware design guide

## Introduction

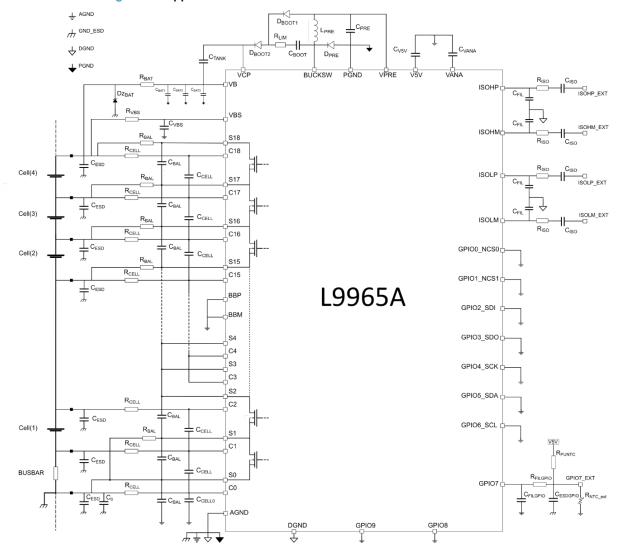

This document describes how to use the L9965A/L99BM218 with related components on a PCB to implement a contact-monitoring cells application.

The L9965A/L99BM218 (analog front end) provides:

- 18 independent ADC for cell voltage monitoring

- 10 GPIOs for temperature sensing using NTCs or absolute measurements for other sensors

- 18 integrated power-MOSFETs for passive balancing

- 1 dedicated ADC for bus bar monitoring

- Isolated serial communication interface (VIF)

- Integrated switching buck pre-regulator (VPRE)

- Integrated 5 V LDO (V5V) to supply external sensors (e.g. NTC)

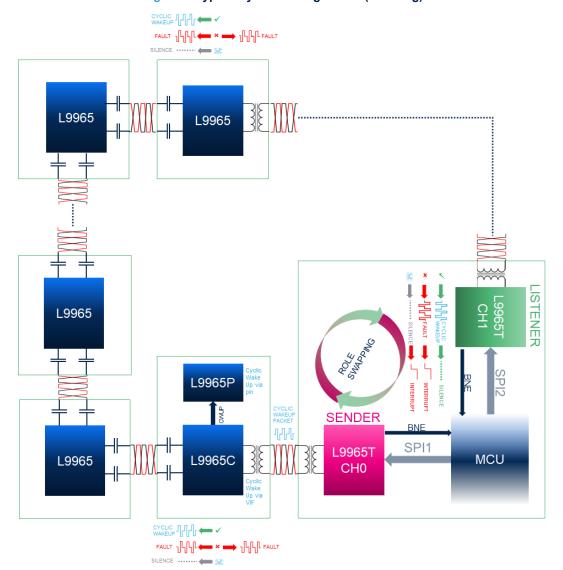

Figure 1. Typical system configuration (dual ring)

### hardware

### design

### guide

## L9965A/L99BM218 hardware design guide

### Cell voltage measurement and cell passive balancing 1.1

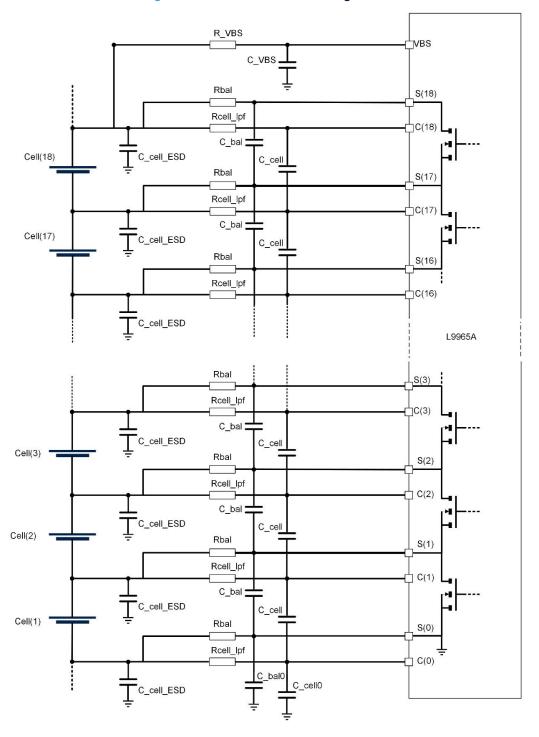

Figure 2. Cell monitor and balancing circuit

AN6387 - Rev 1 page 2/25

hardware

design

guide

#### 1.1.1 Cell voltage measurement

The device has a dedicated ADC for each C(x) pin to measure the differential voltages across the cells.

The R<sub>CELL</sub> and C<sub>CELL</sub> can be chosen according to the indications in Table 1. The cutoff frequency shall be sized according to application requirements. The IC has been characterized for noise and BCI immunity using the BOM in Table 1. A higher cutoff frequency means more external noise coupled to the IC pins, hence noisier measurements.

The R<sub>CELL</sub> can be incremented ensuring that no open load on Cell1 occurs during the open load diagnostic. Please refer to the document AN – open load diagnostic.

#### 1.1.2 Cell balance

For the passive balancing, there is an integrated FET positioned between each S(x) and S(x-1) pins. RBAL shall be sized according to the target balancing current considering the max cell voltage and FET's AMRIBAL (MAX). Assuming the desired balance current  $I_{BAL}$  (MAX) is known, the  $R_{BAL}$  must be sized as follows:

$$I_{BAL} = \frac{V_{CELL}}{(2R_{BAL} + R_{DSON})} \tag{1}$$

$$R_{BAL} = \frac{\frac{V_{CELL}}{I_{BAL}} - R_{DSON}}{2} \tag{2}$$

Considering a cutoff frequency of 100 kHz, the capacitor of each differential channel S(x) is C<sub>BAL</sub>=68 nF.

$$f_{cutoff} = \frac{1}{(2\pi * 2R_{BAL} * C_{BAL})} \tag{3}$$

The device is able to sustain +/- 8 kV ESD according to ISO 10605, system level network 150 pF/330 ohm, using  $C_{CELL ESD} \ge 22 \text{ nF}.$

AN6387 - Rev 1 page 3/25

#### 1.1.3 **Battery sensing**

The ADC positioned on VBS is used for a single-ended measurement; consequently, the filtering capacity is referred to the ground and sized to sustain the V<sub>BAT</sub>, 3 kHz is the suggested cutoff frequency, estimated with the

$$f_{cutoff} = \frac{1}{(2\pi * R_{VBS} * C_{VBS})} \tag{4}$$

#### 1.2 **GPIO**

The GPIO can be used as:

- NTC temperature measurement (Ratiometric)

- GPIO generic analog input (Absolute)

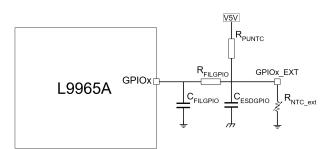

#### 1.2.1 NTC temperature measurement

Using NTC sensors, the GPIO has to be configured as "Analog input ratiometric" by setting the field GPIOx CONF=0b01 in the register GPIO CONF x.

The NTC's voltage divider must be supplied by the V5V regulator by means of the pull-up resistor R<sub>PUNTC</sub> chosen according to the NTC variable resistance. The GPIOs measure the voltage drops on the NTCs according to

Using a first order filter stage can be useful to improve measurement results and filter possible noise.

As an example, for an  $R_{NTC-EXT}$  with a max resistance of 10 k $\Omega$ , possible values for the components can be:

$R_{PUNTC}$ = 10 k $\Omega$ ;

$R_{(FIL\ GPIO)} = 3.3 k\Omega;$

$C_{(FIL\ GPIO)}$ = 100 nF;

Figure 3. GPIO used as NTC

GPIOs connected to external NTCs shall withstand short circuit to VB maximum operating voltage by means of external series resistors, keeping the injected current below 20 mA (a reasonable value to keep the device input

The unused GPIOs must be connected directly to GND as explained in the unused pin section of the product specification.

Optional ESD capacitor CESDGPIO can be used to improve ESD immunity performance. A typical suggested value is C<sub>ESDGPIO</sub> = 6.8 nF to be placed as near the GPIO connectors as possible. The device is able to sustain +/- 8 kV ESD according to ISO 10605, system level network 150 pF/330 ohm, using C<sub>ESDNTC</sub>.

AN6387 - Rev 1 page 4/25

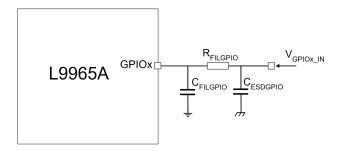

#### 1.2.2 **GPIO** generic analog input

The GPIOs can also be used to convert any V<sub>GPIOx\_IN</sub>. In this case, GPIOx must be configured as an analog absolute input by setting the field GPIOx\_CONF=0b00 in the register GPIO\_CONF\_x.

Figure 4. GPIO used as analog absolute input

AN6387 - Rev 1 page 5/25

hardware

## Battery supply

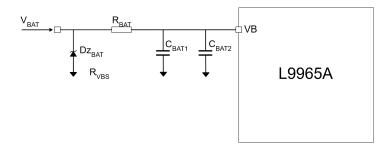

The L9965A/L99BM218 is supplied from the VB pin, which must be connected to the topmost cell of the stack. As reported in the datasheet, it is recommended to place a series resistance on the VB pin to protect it from hot plug inrush currents. A suitable value can be  $R_{BAT}$ = 10  $\Omega$ , to keep the total resistor voltage drop below 1 V.

As an additional protection for the VB pin, to avoid violation of the AMR voltage, it is recommended to add a diode D<sub>ZRAT</sub> as shown in . The diode's breakdown voltage value is chosen according to V<sub>VR</sub> AMR. a good candidate can be SM30T100AY. This component should be placed as near as possible to the V<sub>BAT</sub> connector.

To filter out possible supply noise, capacitors  $C_{BAT1}$ = 4.7 uF and  $C_{BAT2}$ = 100 nF are placed on the  $V_{BAT}$  path. Both capacitors should be placed as close as possible to the VB pin.

When choosing a capacitor component, please take care of the DC bias effect.

Figure 5. Battery supply

#### **VIF** 1.4

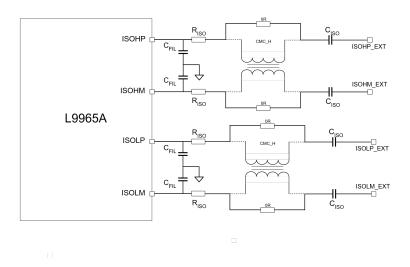

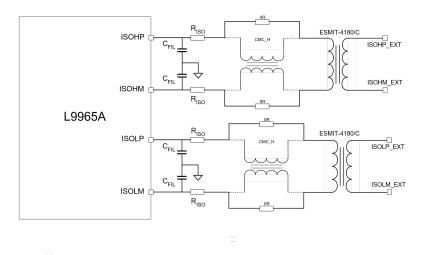

The BMS controller can communicate with other devices in the daisy chain by means of the VIF (Vertical Isolated Interface).

Interconnections between modules can be realized either with UTP (Unshielded Twisted Pair) or STP (Shielded Twisted Pair). The recommended AWG is between 22 and 26, and the recommended cable length is up to 10 meters.

Two different isolation methods are supported:

- Capacitive isolation

- Inductive isolation

In case of capacitive isolation uses series capacitor on the ISO pins, it is recommended to use a 6.8 nF capacitor as C<sub>ISO</sub>. Keep tolerance low to avoid generating unwanted differential signals due to capacitor mismatches.

The capacitor voltage rating shall be sized according to the maximum isolation voltage to be guaranteed in the application:

- 100 V for adjacent devices

- 1 kV is recommended for other cases (this value can be chosen according to the max voltage of the battery pack).

In case of inductive isolation, a transformer between the ISOx\_P and ISOx\_M can be used. ST recommends using the transformer ESMIT- 4180/C, which shows a dielectric breakdown isolation of at least 3750 V.

A low pass filter can be added to ISOx P and ISOx M pins to reject noise and improve protection against the hot plug events and fast transients (R<sub>ISO</sub>= 39 Ω, C<sub>FIL</sub> = 100 pF). Consider sizing the filtering capacitor C<sub>FIL</sub> with a breakdown voltage of 25 V as suggested by the datasheet.

The use of TVS on external VIF lines is recommended as additional protection; the sizing depends on the system and can be defined on a case-by-case basis.

An optional CMC can be added to improve possible EMC issue (a suitable value is 100 uH).

AN6387 - Rev 1 page 6/25

Figure 6. Isolated Vertical Interface (VIF) with capacitive isolation

Figure 7. Isolated Vertical Interface (VIF) with inductive isolation

AN6387 - Rev 1 page 7/25

hardware

design

guide

#### 1.4.1 VIF signal integrity assessment

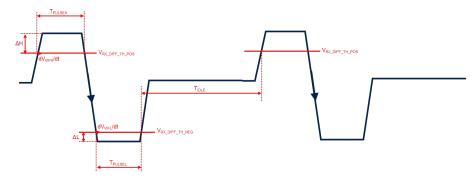

The VIF protocol is Manchester-encoded, meaning that bit '1' or '0' are represented using low==>high transitions or vice versa. The VIF decoding is based on analog differential comparators using fixed thresholds.

Figure 8 reports a reference differential waveform (ISOxP - ISOxM) encoding two consecutive bit.

Figure 8. VIF differential waveform evaluation criteria

Having defined  $V_{VIF}$  as  $V_{ISOxP}$ - $V_{ISOxM}$ , to be correctly interpreted by the receiver, a waveform shall satisfy the following criteria:

Amplitude: pulse absolute peak value shall be 20% above receiver thresholds

$$\begin{cases}

\left| \Delta H \right| \ge 1.2 \quad \left| V_{RX_{DIFFTH_{POS}}} \right| \\

\left| \Delta L \right| \ge 1.2 \quad \left| V_{RX_{DIFFTH_{NEG}}} \right|

\end{cases} \tag{5}$$

Duration: pulse duration shall be enough to allow comparator toggling within the expected time

$$\begin{cases} T_{PULSEH} \ge 45ns \\ T_{PULSEL} \ge 45ns \end{cases} \tag{6}$$

Slope: pulse shall cross thresholds with a slope higher than the minimum specified to allow comparator toggling within the expected time

$$\begin{cases} \frac{dV_{VIFH}}{dt} \ge 0.2 \frac{V}{ns} \\ \frac{dV_{VIFL}}{dt} \le -0.2 \frac{V}{ns} \end{cases}$$

(7)

Idle: pulse differential amplitude shall be below both thresholds for a certain time interval to enable a correct symbol end condition

$$\begin{cases} V_{VIF} < V_{RXDIFFTHPOS} \\ V_{VIF} > V_{RXDIFFTHNEG} \end{cases} for T_{IDLE} > 110ns$$

(8)

A waveform not respecting such constraints may not be decoded correctly, leading to communication error detection.

VIF components listed in the Table 1 have been extensively validated in application and during EMC trials, and are recommended for a correct communication. Usage of different components is possible. However, the signal integrity shall be re-assessed during system trials.

#### 1.4.2 Imbalance due to a VIF port disabled

In single-access daisy chains, the ISOH VIF port of the topmost device is unused and shall be terminated as prescribed in the Section 1.6 paragraph. User software can decide whether to keep this port closed or leave it enabled, based on consumption imbalance considerations.

The SoC imbalance due to one device in the stack having a VIF port disabled is totally negligible most of the times. It only becomes significant if small packs with low capacity are used.

For instance, consider the following system example:

AN6387 - Rev 1 page 8/25

- Suppose to have a single-access daisy chain with N stacked devices. User SW may disable the topmost device ISOH port, as no L9965T/L99BM2T is listening on the other side.

- Suppose to have a 100 ms thread collecting all cell voltage/temperature from the AFEs.

- Suppose to have a 400 V system with N = 7 stacked L9965A/L99BM218. The worst case happens when the pack capacity is small. A reasonably small 400 V system would store 10 kWh energy, thus having a 25 Ah capacity. Then, 1% of SoC corresponds to 0.25 Ah.

If using burst read, the communication loop time to recover all information will be <10 ms, so bus duty-cycle will be <10%

However, the actual duty-cycle where ISOH/ISOL ports are transmitting is < 1%, due to interframe delays and VIF physical layer.

This 1% VIF TX duty-cycle is the parameter to account for calculating imbalancing.

Suppose all the AFEs are programmed with BIDI\_ANSW = 1, except the last one, for which ISOH was disabled. In principle, this is not needed for a single-access chain. However, to compensate for VIF communication imbalance as much as possible, keeping BIDI\_ANSW enabled is the right thing to do.

The main differences between the topmost L9965A/L99BM218 and the other ones are:

- When receiving an SoC command, it won't be propagated upwards. This corresponds to 5.125 us inactivity time of the ISOH port

- When receiving a burst read command, it won't be propagated upwards. This corresponds to 7 x 5.125 us inactivity time of the ISOH port

- When each AFE sends burst read data back to the XCVR, the LAST AFE will not propagate it upwards.

This corresponds to ~14x100 us inactivity time of the ISOH port

The total inactivity time of the ISOH port of the last AFE can be estimated as 1.441 ms in a 100 ms loop time.

The amount of charge difference can then be estimated considering the typical ISO port transmitter consumption:  $8.5 \text{ mA} * 1.441 \text{ ms} = 3.402*10^{-9} \text{ Ah}$ . Such imbalance cumulates at each communication cycle.

With the calculated imbalance per cycle due to VIF,  $7.3486*10^7$  communication cycles are needed to cumulate a 1% SoC imbalance (0.25 Ah). If communication cycle loop time is 100 ms, this corresponds to  $7.3486*10^6$  seconds, which is  $2.0413*10^3$  hours, thus ~85 days.

The days to have a 1% SoC imbalance would proportionally increase with pack capacitance. Therefore, the imbalance due to a VIF port disabled can be considered totally negligible in respect to cell self-discharge performances, which are something like ~10% in a month. In fact, since cells are not perfectly matched, it is reasonable to assume that imbalance cumulated due to self-discharge mismatch is significantly higher in a 30-day timespan.

To conclude, leaving ISOH port disabled will not imbalance packs in a significant way. However, leaving ISOH port enabled and terminated as prescribed, can be helpful when dealing with small capacity packs.

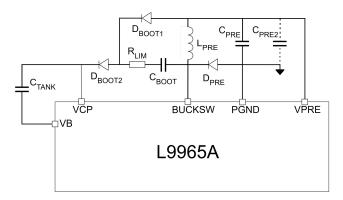

### 1.5 VPRE

The VPRE pin is the output pin of the integrated buck regulator.

Its tank capacitor is sized with  $C_{PRE}$ = 4.7 uF, considering a minimum dielectric breakdown voltage of 100 V according to VPRE AMR value.

The buck converter inductor should have an inductance value  $L_{PRE}$ = 47 uH with saturation current up to 220 mA. An additional  $C_{PRE2}$ = 10 nF capacitor on the VPRE pin can be added if needed.

AN6387 - Rev 1 page 9/25

Figure 9. BUCK regulator

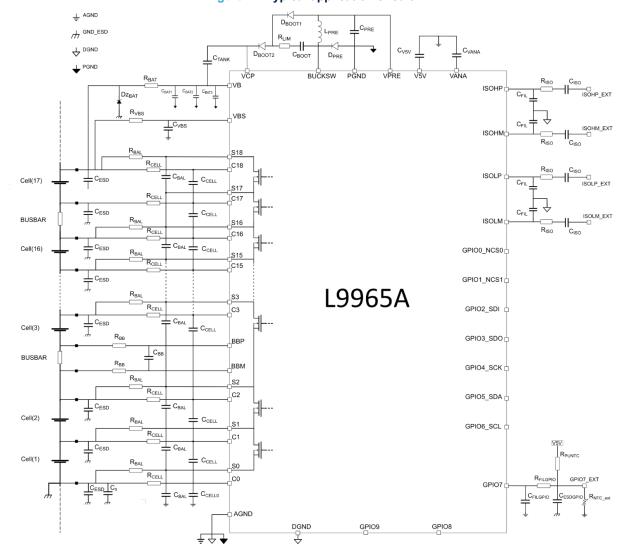

#### 1.6 **Unused pins**

The external connector must be designed to comply with the rules:

- A cell shall always be present between pins C0 and C1

- The remaining cells shall be mounted starting from the topmost (cell 18) and moving downwards

- In case the C0-C1 pair is used as a busbar sensing channel, then the first cell shall be connected between C1 and C2 pins. However, open load diagnostics are not fully guaranteed in this case.

There can be two approaches for adapting a design to a different number of cells:

- Hard-wired approach: it is the most efficient in terms of the BOM, but requires redesigning the PCB for adapting to different modules. Given a number of unused cells, the design shall be adapted as follows:

- Cell pairs C(x) C(x-1), which are completely unused, should be short-circuited and connected to the negative terminal of the first mounted cell upwards

- Unused balancing pairs S(x) S(x-1), should be short-circuited and connected to the negative terminal of the first balancing stage upwards.

- Cell pairs C(x) C(x-1), which are used for busbar sensing, should be treated as regular cells and kept enabled. However, their balancing stage should be unused.

- If the busbar pair BBP BBM is unused, those pins shall be short-circuited and connected to AGND.

- Unused GPIOs shall be connected to AGND. The GPIO must be configured as a digital input via GPIOx\_CONF register

- Unused VIF ports ISOxP ISOxM shall be terminated by connecting a differential 160  $\Omega$  resistor and a common-mode 100 pF capacitor vs. AGND on each pin. Refer to Imbalance due to a VIF port disabled for further information

- Flexible approach: it is less efficient in terms of the BOM, since unused cells are still populated with analog front-end components. On the other hand, it enables quick readaptation of an existing PCB design to a different number of cells. Given a number of unused cells, the following substrategies are possible

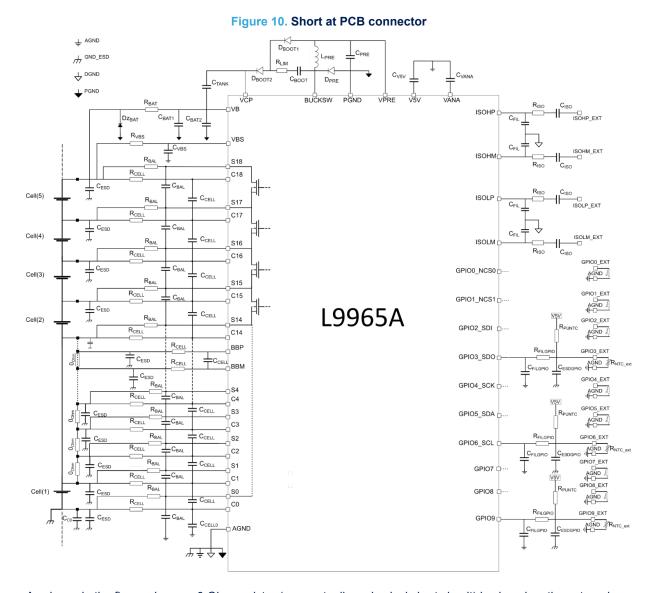

- The Short at PCB connector technique exploits shorts between unused connector pins. It still requires a small external rework, but it is limited to the cell connector and does not involve the PCB layout.

- The Assembly option technique exploits design variants, replacing existing components with 0  $\Omega$ resistors to manage unused cells.

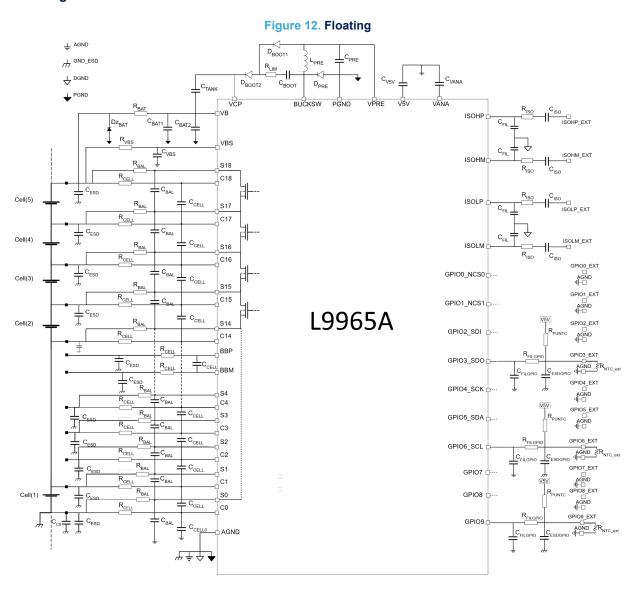

- The Floating technique is as straightforward as it seems: just leave the corresponding PCB connectors floating whenever a cell is unused

AN6387 - Rev 1 page 10/25

# 57

### 1.6.1 Short at PCB connector

As shown in the figure above, a 0 Ohm resistor (or eventually a physical short circuit) is placed on the external connector of the unused pins to connect the cell 1 positive terminal to the negative terminal of the following mounted cell. If the BB channel is brought to the connector, it can be short-circuited and connected to any potential mounted cell as well. Unused GPIO channels are shorted to AGND at the PCB connector.

AN6387 - Rev 1 page 11/25

#### 1.6.2 **Assembly option**

Figure 11. Assembly option ⊥ AGND ₼ GND\_ESD R<sub>LIM</sub>  $\downarrow$  DGND VCP BUCKSW VPRE ISOHM S18 C18 ISOLP S17 R<sub>CELL</sub> C17 ISOLM S16 R<sub>CEL</sub> C16 GPIO0\_EXT GPIO0\_NCS0 Cell(3) C<sub>CELI</sub> AGND S15 R<sub>CELI</sub> GPIO1\_EXT C15 GPIO1\_NCS1 AGND CESD L9965A Cell(2) S14 GPIO2\_EXT GPIO2 SDI R<sub>CELL</sub> AGND C14 BBP GPIO3\_EXT

AGND ≹R<sub>NTO</sub> TCESD RCELL ввм C<sub>ESD</sub> R<sub>B</sub> GPIO4\_EXT GPIO4 SCK AGND R<sub>CELL</sub> C4 GPIO5\_EXT S3 GPIO5\_SDA AGND R<sub>CELI</sub> C3 GPIO6\_EXT S2 R<sub>CELL</sub> AGND RN C2 R<sub>BAL</sub> S1 AGND C1 S0 AGND CO GPIO9\_EXT AGND ₹R<sub>NTC\_ex</sub> AGND ₩<u>+</u>↑

In the example above, unused cells and GPIOs are managed by replacing a few of their analog front-end capacitors with 0 Ohm resistors.

AN6387 - Rev 1 page 12/25

## 1.6.3 Floating

In the example above, unused cells and GPIOs are managed by simply leaving their PCB connectors floating. Their analog front-end BOM is totally populated with recommended components.

AN6387 - Rev 1 page 13/25

## 1.7 EMC considerations

To improve EMC robustness, the following actions are recommended:

Place all buck converter components near the IC as much as possible. To minimize parasitic effects, the PCB area under the buck coil should be free of metal layers and metal traces. Minimize the orange loop area in Figure 13.

Noisy net: far away from semitive ones

Particular care to this connection: capacitor and anode first connected together then the resulting net has to be routed towards GND

Figure 13. Buck converter layout rules

Place protection and/or HV decoupling components, TVS, ESD Cap, ISO-SPI HV Cap, near the relevant external input connector as much as possible.

The L9965A/L99BM218 features 4 ground pins used as internal reference: AGND, DGND, PGND and EP (to be connected to AGND); additional GND can be present on PCB such as GND\_PACK and ESD\_GND.

To avoid relevant ground shifts and noise propagation on AGND, the different GNDs must be joined with a star as close as possible to the IC, and then brought to the PCB connector with a GND plane, connected to pack ground. The ADC and NTC lines should run into inner layers of PCB.

The L9965A/L99BM218 promotional board of the PCB project is available as reference.

AN6387 - Rev 1 page 14/25

# 2 Application information

This section lists the components to be used in typical application scenarios.

## 2.1 Application circuit

Figure 14. Typical application circuit

AN6387 - Rev 1 page 15/25

Figure 15. Application circuit with BB on the first cell and unused cells

AN6387 - Rev 1 page 16/25

Figure 16. Application scenario with SPI master and EEPROM

AN6387 - Rev 1 page 17/25

## 2.2 Bill of material (BOM)

Table 1. Bill of material

| Symbol             | Parameter                                                             | Value                | Rating  | Tolerance | Note                                                                                                                                                                                                                                 |  |

|--------------------|-----------------------------------------------------------------------|----------------------|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Battery su         | pply                                                                  |                      |         |           |                                                                                                                                                                                                                                      |  |

| R <sub>BAT</sub>   | Series resistor for battery supply line                               | 10 Ω                 | 125 mW  | 10%       | Optional, it can be useful to limit possible hot plug spikes, according to specific customer application conditions. It shall be sized so that its voltage drop is kept < 1 V.                                                       |  |

| D <sub>ZBAT</sub>  | TVS for battery supply line                                           | SM30T100AY           | NA      | NA        | Optional. Can be mounted to comply with surge and EFT tests.                                                                                                                                                                         |  |

| C <sub>BAT1</sub>  | Tank capacitor for battery supply line                                | 2.2 uF to 4.7 uF     | 100 V   | 20%       | Lower rating is possible according to the module maximum voltage.                                                                                                                                                                    |  |

| C <sub>BAT2</sub>  | Filtering capacitor for battery supply line                           | 100 nF               | 100 V   | 20%       | Optional, for improving EMC performances. Consider increasing voltage rating to compensate the DC bias effect.                                                                                                                       |  |

| C <sub>BAT3</sub>  | Filtering capacitor for battery supply line                           | 10 nF                | 100 V   | 20%       | Optional, for improving EMC performances. Consider increasing voltage rating to compensate the DC bias effect.                                                                                                                       |  |

| Battery ser        | nsing                                                                 |                      |         |           |                                                                                                                                                                                                                                      |  |

| R <sub>VBS</sub>   | Filtering resistor for battery sensing line                           | 240 Ω                | 62.5 mW | 5%        | VBS gain conversion error due to RVBS can be computed as R <sub>VBS</sub> /R <sub>VBS_IN</sub> . Equalize R <sub>VBS</sub> C <sub>VBS</sub> filter cutoff frequency to cells.                                                        |  |

| C <sub>VBS</sub>   | Filtering capacitor for battery sensing line                          | 220 nF               | 100 V   | 10%       | Consider increasing voltage rating to compensate the DC bias effect. Lower rating is possible according to the module maximum voltage.                                                                                               |  |

| Cell and bu        | usbar sensing                                                         |                      | ·       |           |                                                                                                                                                                                                                                      |  |

| R <sub>CELL</sub>  | Filtering resistor for cell sensing line                              | 240 Ω                | 62.5 mW | 5%        | R <sub>CELL</sub> and C <sub>CELL</sub> values can be chosen to form an RC filter with ~3.3 kHz as cutoff                                                                                                                            |  |

| C <sub>CELL</sub>  | Differential filtering capacitor for cell sensing line                | 100 nF               | 16 V    | 10%       | frequency. Cell gain conversion error duto R <sub>CELL</sub> can be computed as $2R_{CELL}/R_{CELL\_DIFF\_IN}$ . Do not go below 100 $\Omega$ f hotplug robustness. Do not go above 30 $\Omega$ to avoid false cell 1 open flagging. |  |

| C <sub>C0</sub>    | Grounded capacitor<br>for improved BCI<br>immunity on C0<br>connector | 1 nF                 | 16 V    | 10%       |                                                                                                                                                                                                                                      |  |

| C <sub>Cell0</sub> | Consist of 3 grounded capacitors for improved BCI immunity on C0      | 100 nF1nF,<br>100 pF | 16 V    | 10%       |                                                                                                                                                                                                                                      |  |

| R <sub>BB</sub>    | Filtering resistor for busbar sensing line                            | 240 Ω                | 62.5 mW | 5%        | Equalize R <sub>BB</sub> C <sub>BB</sub> filter cutoff frequency to                                                                                                                                                                  |  |

| C <sub>BB</sub>    | Filtering capacitor for busbar sensing line                           | 100 nF               | 16 V    | 10%       | cells.                                                                                                                                                                                                                               |  |

| Cell balanc        | cing                                                                  | 1                    | -       | 1         |                                                                                                                                                                                                                                      |  |

| R <sub>BAL</sub>   | Balancing resistor for cell sensing line                              | 12 Ω                 | 500 mW  | 5%        | Sized to have a 180 mA max. balancing current when cell voltage is 4.3 V.                                                                                                                                                            |  |

AN6387 - Rev 1 page 18/25

| Symbol               | Parameter                                             | Value                        | Rating        | Tolerance | Note                                                                                                                                                                                                                        |

|----------------------|-------------------------------------------------------|------------------------------|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C <sub>BAL</sub>     | Filtering capacitor for cell balancing line           | 22 nF to 68 nF               | 16 V          | 20%       | The maximum R <sub>BAL</sub> C <sub>BAL</sub> cutoff frequency of 100 kHz is recommended for BCI robustness                                                                                                                 |

| ESD                  |                                                       |                              |               |           |                                                                                                                                                                                                                             |

| C <sub>ESD</sub>     | ESD capacitor for pack connectors                     | 22 nF to 47 nF               | 100 V         | 20%       | Optional, according to specific customer application requirements. Smaller values are possible if ESD-Safe MLCCs are used. Going below 6.8 nF is not recommended as it may jeopardize BCI performances                      |

| LDOs                 |                                                       |                              |               |           |                                                                                                                                                                                                                             |

| C <sub>V5V</sub>     | 5 V LDO tank capacitor                                | 1 uF                         | 10 V          | 10%       | Consider increasing voltage rating to compensate the DC bias effect.                                                                                                                                                        |

| C <sub>VANA</sub>    | 3.3 V LDO tank capacitor                              | 470 nF                       | 10 V          | 10%       | Consider increasing voltage rating to compensate the DC bias effect.                                                                                                                                                        |

| VIF                  | <u>'</u>                                              |                              |               |           |                                                                                                                                                                                                                             |

| CMC                  | Common mode choke for VIF H/L ports                   | ACT1210R-101-2P              |               |           | Optional. Can be mounted to improve EMC performances                                                                                                                                                                        |

| EMIF                 | Compact analog front-<br>end for for VIF ports<br>H/L | EMIF04-0410M8                |               |           | Optional. Can be used in place of R <sub>ISO</sub> and C <sub>FIL</sub> components                                                                                                                                          |

| R <sub>ISO</sub>     | Series resistor for ISO pins                          | 35 Ω to 41 Ω<br>39 Ω typical | 100 mW        | 1%        | Optional. Can be used in place of the EMIF component. Filters common mode and differential noise. Keep tolerance low to maximize differential line balancing.                                                               |

| C <sub>ISO</sub>     | Isolation capacitor for VIF ports H/L                 | 2.2 nF to 6.8 nF             | 100 V/1<br>kV | 2%        | Optional. Can be used in place of XFMR component. Voltage rating shall be sized according to the maximum isolation voltage to be guaranteed in the application. Keep tolerance low to maximize differential line balancing. |

| XFMR                 | Isolation transformer for VIF ports H/L               | ESMIT-4180/C                 |               |           | Optional. Can be used in place of $C_{ISO}$ component. Key parameters are:  • Inductance $\geq$ 120 $\mu$ H @-40°C  • Winding resistance $\leq$ 0.5 $\Omega$ Note: EMC trials performed with recommended P/N.               |

| C <sub>FIL</sub>     | Filtering capacitor for ISO termination               | 100 pF                       | 25 V          | 2%        | Optional. Can be used in place of the EMIF component. Filters common mode and differential noise. Keep tolerance low to maximize differential line balancing.                                                               |

| R <sub>TERM</sub>    | Termination resistor for unused port                  | 200 Ω                        | 0.5 W         | 10%       | Optional. To be used only on unused VIF port.                                                                                                                                                                               |

| GPIOs                |                                                       |                              |               |           |                                                                                                                                                                                                                             |

| R <sub>PUNTC</sub>   | Pullup biasing for NTC measurement                    | 10 kΩ                        | 125 mW        | 10%       | Pullup resistor for NTC lines. Rating is to be increased to 0.5 W to protect and withstand short to battery.                                                                                                                |

| R <sub>FILGPIO</sub> | Series resistor for GPIO pins                         | 3.3 kΩ                       | 125 mW        | 10%       | Filters noise on the GPIO pin. Rating is to be increased to 0.5 W to protect and withstand short to battery.                                                                                                                |

| C <sub>FILGPIO</sub> | Filtering capacitor for GPIO pins                     | 100 nF                       | 16 V          | 20%       | Filters noise on the GPIO pin. Rating is to be increased to 100 V to withstand short to battery.                                                                                                                            |

AN6387 - Rev 1 page 19/25

| Symbol                                     | Parameter                                               | Value     | Rating            | Tolerance | Note                                                                                                                                                                                                                                            |  |  |  |  |

|--------------------------------------------|---------------------------------------------------------|-----------|-------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| C <sub>ESDGPIO</sub>                       | ESD capacitor for GPIO pins connected to external lines | 6.8 nF    | 16 V              | 20%       | Optional, according to specific customer application requirements. Rating is to be increased to 100 V to withstand short to battery.                                                                                                            |  |  |  |  |

| Charge pump                                |                                                         |           |                   |           |                                                                                                                                                                                                                                                 |  |  |  |  |

| D <sub>BOOT1</sub> ,<br>D <sub>BOOT2</sub> | Charge pump bootstrap diodes                            | BAV99-QVL | 100 V             | NA        | Bootstrap diodes rated to withstand maximum operating battery voltage.                                                                                                                                                                          |  |  |  |  |

| C <sub>TANK</sub>                          | Charge pump tank capacitor                              | 47 nF     | 100 V             | 10%       | Rated to withstand maximum operating battery voltage.                                                                                                                                                                                           |  |  |  |  |

| C <sub>BOOT</sub>                          | Charge pump flying bootstrap                            | 10 nF     | 100 V             | 10%       | Rated to withstand maximum operating battery voltage.                                                                                                                                                                                           |  |  |  |  |

| R <sub>LIM</sub>                           | Bootstrap peak current limiter                          | 1 Ω       | 100 mW            | 10%       | Needed to limit the current peak at the startup, when the C <sub>TANK</sub> is discharged.                                                                                                                                                      |  |  |  |  |

| Buck prere                                 | gulator                                                 |           | <u>'</u>          | ·         |                                                                                                                                                                                                                                                 |  |  |  |  |

| C <sub>PRE</sub>                           | Buck tank capacitor                                     | 4.7 uF    | 16 V              | 10%       | Rating is to be increased to 100 V to withstand short to battery.                                                                                                                                                                               |  |  |  |  |

| L <sub>PRE</sub>                           | Buck inductor                                           | 47 μH     | ISAT >><br>220 mA | 20%       | Inductance value shall be constant up to 220 mA.                                                                                                                                                                                                |  |  |  |  |

| D <sub>PRE</sub>                           | Freewheeling diode                                      | BAS19LT1G | 120 V             |           | Key parameters are: $ V_R \ge 110 \text{ V} $ • $I_F \ge 100 \text{ mA}_{DC}$ • $T_J \ge 150^{\circ}\text{C}$ • $P_D \ge 100 \text{ mW}$ • $V_F \le 0.75 \text{ V @ }10 \text{ mA @ }25^{\circ}\text{C}$ • $C_J \le 10 \text{ pF@ }0 \text{ V}$ |  |  |  |  |

AN6387 - Rev 1 page 20/25

## **Revision history**

Table 2. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 04-Nov-2025 | 1       | Initial release. |

AN6387 - Rev 1 page 21/25

## **Contents**

| 1  | L990     | 65A/L99  | 9BM218 hardware design guide                  |    |

|----|----------|----------|-----------------------------------------------|----|

|    | 1.1      |          | oltage measurement and cell passive balancing |    |

|    |          | 1.1.1    | Cell voltage measurement                      | 3  |

|    |          | 1.1.2    | Cell balance                                  | 3  |

|    |          | 1.1.3    | Battery sensing                               |    |

|    | 1.2      | GPIO     |                                               | 4  |

|    |          | 1.2.1    | NTC temperature measurement                   |    |

|    |          | 1.2.2    | GPIO generic analog input                     |    |

|    | 1.3      | Batter   | ry supply                                     | 6  |

|    | 1.4      | VIF .    |                                               | 6  |

|    |          | 1.4.1    | VIF signal integrity assessment               | 8  |

|    |          | 1.4.2    | Imbalance due to a VIF port disabled          | 8  |

|    | 1.5      | VPRE     | <b>=</b>                                      |    |

|    | 1.6      | Unuse    | ed pins                                       | 10 |

|    |          | 1.6.1    | Short at PCB connector                        | 11 |

|    |          | 1.6.2    | Assembly option                               | 12 |

|    |          | 1.6.3    | Floating                                      | 13 |

|    | 1.7      | EMC      | considerations                                | 14 |

| 2  | Арр      | lication | n information                                 |    |

|    | 2.1      | Applic   | cation circuit                                | 15 |

|    | 2.2      |          | material (BOM)                                |    |

| Re | vision   |          | y                                             |    |

|    |          | _        |                                               |    |

|    |          |          |                                               |    |

|    | L OI IIL | 141 C3   |                                               |    |

## **List of tables**

7/

| Table 1. | Bill of material          | 18 |

|----------|---------------------------|----|

|          | Document revision history |    |

AN6387 - Rev 1 page 23/25

# **List of figures**

| Figure 1.  | Typical system configuration (dual ring)                       | . 1 |

|------------|----------------------------------------------------------------|-----|

| Figure 2.  | Cell monitor and balancing circuit                             | . 2 |

| Figure 3.  | GPIO used as NTC                                               | . 4 |

| Figure 4.  | GPIO used as analog absolute input                             | . 5 |

| Figure 5.  | Battery supply                                                 | . 6 |

| Figure 6.  | Isolated Vertical Interface (VIF) with capacitive isolation    | . 7 |

| Figure 7.  | Isolated Vertical Interface (VIF) with inductive isolation     | . 7 |

| Figure 8.  | VIF differential waveform evaluation criteria                  | . 8 |

| Figure 9.  | BUCK regulator                                                 | 10  |

| Figure 10. | Short at PCB connector                                         |     |

| Figure 11. | Assembly option                                                | 12  |

| Figure 12. | Floating                                                       |     |

| Figure 13. | Buck converter layout rules                                    | 14  |

| Figure 14. | Typical application circuit                                    | 15  |

| Figure 15. | Application circuit with BB on the first cell and unused cells | 16  |

| Figure 16. | Application scenario with SPI master and EEPROM                | 17  |

### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics - All rights reserved

AN6387 - Rev 1 page 25/25