### How to read or to write STUSB4531 NVM content

#### Introduction

The STUSB4531 embeds a non-volatile memory (NVM) to store key parameters used by the autorun algorithm. The NVM has four sectors of 8 bytes each.

The mapping between bits and sector bytes is performed using the STSW-STUSB020 graphical user interface.

Typically, NVM parameters are programmed during the end-product manufacturing process.

### STUSB4531 prerequisite

#### 1.1 Generic I<sup>2</sup>C functions

Two generic functions are defined in this document to indicate I<sup>2</sup>C read or write actions.

For both functions, the device address is omitted to avoid overloading the document. The device address can be 0x28 or 0x29, as specified in the datasheet.

I2C\_Read(register\_address, number\_of\_byte):

- Register address: indicates address starting point to be read

- Number of byte: indicates if single or multiple consecutive read operations will be performed

I2C Write(register address, data, number of byte):

- Register address: indicates address starting point to be written

- Data: is the content to be written

- Number\_of\_byte: indicates if single or multiple consecutive write operations will be performed

#### 1.2 Register setup

The registers used in this document are:

- NVM\_CUST\_CTRL address 0x0041

- NVM STATUS address 0x001F

- DPM SRC PDO1 address 0x00A0

- DPM SRC PDO2 address 0x00A1

DPM\_SRC\_PDO1 and DPM\_SRC\_PDO2 are used as a single 8-byte NVM buffer, starting at the DPM\_SRC\_PDO1 address, for read or write operations.

As per the register map, NVM CUST CTRL and NVM STATUS descriptions are:

NVM\_CUST\_OPCODE [2:0] NVM\_CUST\_SECT [5:4] M RW RW RW

Figure 1. NVM\_CUST\_CTRL address 0x0041

Address: 0x0041 Reset: 0x00

#### [7] NVM\_MODE:

- 0x0: (MAIN\_MODE) chip in main mode.

- 0x1: (NVM\_MODE) Chip in NVM mode.

#### [5:4] NVM\_CUST\_SECT:

- 0x0: (CUST\_SECT\_0) customer sector 0.

- 0x1: (CUST\_SECT\_1) customer sector 1. 0x2: (CUST\_SECT\_2) customer sector 2. 0x3: (CUST\_SECT\_3) customer sector 3.

#### [2:0] NVM\_CUST\_OPCODE:

- 0x0: (NOP) No Operation.

- 0x1: (READ CUST) Read.

- 0x2: (WRITE\_CUST) Write. 0x3: (WRITE\_FUNC\_REG) copy functional registers to NVM.

- 0x4: (WRITE\_2\_FUNC\_REG) copy NVM to the functional registers.

AN6388 - Rev 1 page 2/11

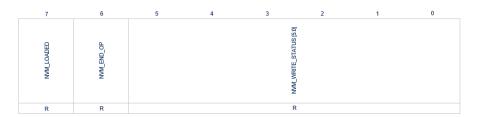

Figure 2. NVM\_STATUS address 0x001F

Address: 0x001F Reset: 0x00

#### [7] NVM\_LOADED:

- 0x0: (NO\_NVM\_LOAD) load not yet done.- 0x1: (NVM\_LOAD\_DONE) load completed.

- [6] NVM\_END\_OP:

- 0x0: (NVM\_OP\_ONGOING) the operation is ongoing.

- 0x1: (NVM\_OP\_ENDED) the operation is finished.

- [5:0] **NVM\_WRITE\_STATUS:** Verify result after last write operation. Each bit represents a sector (bit0: sector0, bit1: sector1...)

#### 1.3 Check STUSB4531 NVM status

In order to be able to read or write NVM content, the STUSB4531 NVM needs to be in a stable state.

- I2C\_Read (NVM\_STATUS, 1)

- Expected content:

- NVM\_LOADED = NVM\_LOAD\_DONE

- NVM\_END\_OP = NVM\_OP\_ENDED

- i.e.: b11xxxxxxx

AN6388 - Rev 1 page 3/11

### 2 Read NVM bank

#### Step 1:

The NVM needs to be set in a special mode of operation in order to access a dedicated sector n:

- NVM\_CUST\_CTRL data:

- NVM MODE = NVM MODE

- NVM CUST OP CODE = NOP

- NVM\_CUST\_SECT = CUST\_SECT\_n

- I2C\_Write(NVM\_CUST\_CTRL, data, 1)

#### Step 2:

Sector n is enabled in read mode:

- NVM\_CUST\_CTRL data:

- NVM MODE = NVM MODE

- NVM CUST OP CODE = READ CUST

- NVM\_CUST\_SECT = CUST\_SECT\_n

- I2C\_Write(NVM\_CUST\_CTRL, data, 1)

#### Step 3:

Wait for the end of the NVM sector n read process:

- I2C\_Read(NVM\_STATUS, 1)

- Expected content:

- NVM\_END\_OP= NVM\_OP\_ENDED

- i.e.: bx1xxxxxx

#### Step 4:

Read sector n content located in DPM SRC PDO1 and DPM SRC PDO2:

- I2C\_Read(DPM\_SRC\_PDO1, 8)

- The data read will be the 8 bytes of the sector n content

#### Step 5:

Disable access to sector n:

- NVM\_CUST\_CTRL data:

- NVM MODE = NVM MODE

- NVM\_CUST\_OP\_CODE = NOP

- NVM\_CUST\_SECT = CUST\_SECT\_n

- I2C\_Write(NVM\_CUST\_CTRL, data, 1)

#### Step 6:

Switch the NVM back to normal operation:

- NVM CUST CTRL data:

- NVM MODE = MAIN MODE

- NVM CUST OP CODE = NOP

- NVM\_CUST\_SECT = CUST\_SECT\_n

- I2C Write(NVM CUST CTRL, data, 1)

In order to read multiple sectors, repeat operations from step 2 to step 5 before executing step 6.

AN6388 - Rev 1 page 4/11

### 3 Write NVM bank

#### Step 1:

The NVM needs to be set in a special mode of operation in order to access a dedicated sector n:

- NVM\_CUST\_CTRL data:

- NVM MODE = NVM MODE

- NVM CUST OP CODE = NOP

- NVM\_CUST\_SECT = CUST\_SECT\_n

- I2C\_Write(NVM\_CUST\_CTRL, data, 1)

#### Step 2:

Write the 8 bytes of sector n content in DPM\_SRC\_PDO1:

I2C\_Write(DPM\_SRC\_PDO1, data, 8)

#### Step 3:

Sector n is enabled in write mode:

- NVM\_CUST\_CTRL data:

- NVM MODE = NVM MODE

- NVM CUST OP CODE = WRITE CUST

- NVM\_CUST\_SECT = CUST\_SECT\_n

- I2C Write(NVM CUST CTRL, data, 1)

#### Step 4:

Wait for the end of the NVM sector n write process:

- I2C\_Read(NVM\_STATUS, 1)

- Expected content:

- NVM\_END\_OP= NVM\_OP\_ENDED

- NVM\_WRITE\_STATUS[5:0] = bit n set

- i.e.: Sector 2 to be written: expect bit 2 to be set

#### Step 5:

Disable access to sector n:

- NVM\_CUST\_CTRL data:

- NVM\_MODE = NVM\_MODE

- NVM\_CUST\_OP\_CODE = NOP

- NVM CUST SECT = CUST SECT n

- I2C Write(NVM CUST CTRL, data, 1)

#### Step 6:

Switch the NVM back to normal operation:

- NVM\_CUST\_CTRL data:

- NVM MODE = MAIN MODE

- NVM\_CUST\_OP\_CODE = NOP

- NVM CUST SECT = CUST SECT n

- I2C\_Write(NVM\_CUST\_CTRL, data, 1)

In order to write to multiple sectors, repeat operations from step 2 to step 5 before executing step 6.

AN6388 - Rev 1 page 5/11

### 4 References

STUSB4531 Datasheet: STUSB4531

STUSB4531 Register map:

STUSB4531 GUI: STSW-STUSB020: STSW-STUSB020

AN6388 - Rev 1 page 6/11

## **Revision history**

Table 1. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 12-Nov-2025 | 1       | Initial release. |

AN6388 - Rev 1 page 7/11

## **Contents**

| 1   | STUS    | SB4531 prerequisite                | . 2 |

|-----|---------|------------------------------------|-----|

|     | 1.1     | Generic I <sup>2</sup> C functions | . 2 |

|     | 1.2     | Register setup                     | . 2 |

|     | 1.3     | Check STUSB4531 NVM status         | . 3 |

| 2   | Read    | I NVM bank                         | .4  |

| 3   | Write   | NVM bank                           | . 5 |

| 4   | Refe    | rences                             | . 6 |

| Rev | ision l | history                            | .7  |

## **List of tables**

| able 1. | ocument revision history     |

|---------|------------------------------|

| able I. | OCUITICIIL TEVISIOIT HISTOLV |

|         |                              |

AN6388 - Rev 1 page 9/11

# **List of figures**

| Figure 1. | NVM_CUST_CTRL address 0x0041 | 2 |

|-----------|------------------------------|---|

| Figure 2. | NVM_STATUS address 0x001F    | : |

AN6388 - Rev 1 page 10/11

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics - All rights reserved

AN6388 - Rev 1 page 11/11