## How to handle STUSB4531 interrupts

### Introduction

#### Interrupts in STUSB4531

The STUSB4531 includes an interrupt management system to notify the application about various types of events.

The interrupt pin, which is used to flag an event to the application of, is an open-drain I/O named ALERT.

Event information that has triggered the alert event is available in the I<sup>2</sup>C registers.

#### I<sup>2</sup>C commands

Two generic functions are defined in this document to indicate I<sup>2</sup>C read or write actions.

For both functions, the device address is omitted to avoid overloading the document. The device address can be 0x28 or 0x29, as specified in the datasheet.

- I2C\_Read(register\_address, number\_of\_byte):

- Register\_address: indicates the address starting point to be read

- Number\_of\_byte: indicates if a single or multiple consecutive reads will be performed

- I2C\_Write(register\_address, data, number\_of\_byte):

- Register\_address: indicates the address starting point to be written

- Data: is the content to be written

- Number\_of\_byte: indicates if a single or multiple consecutive writes will be performed

## 1 STUSB4531 prerequisite

### 1.1 Interrupt default setup

By default, all functional interrupts are masked to the application. Only hardware fault interrupts are non-maskable and could lead to an alert event.

### 1.2 Interrupt structure

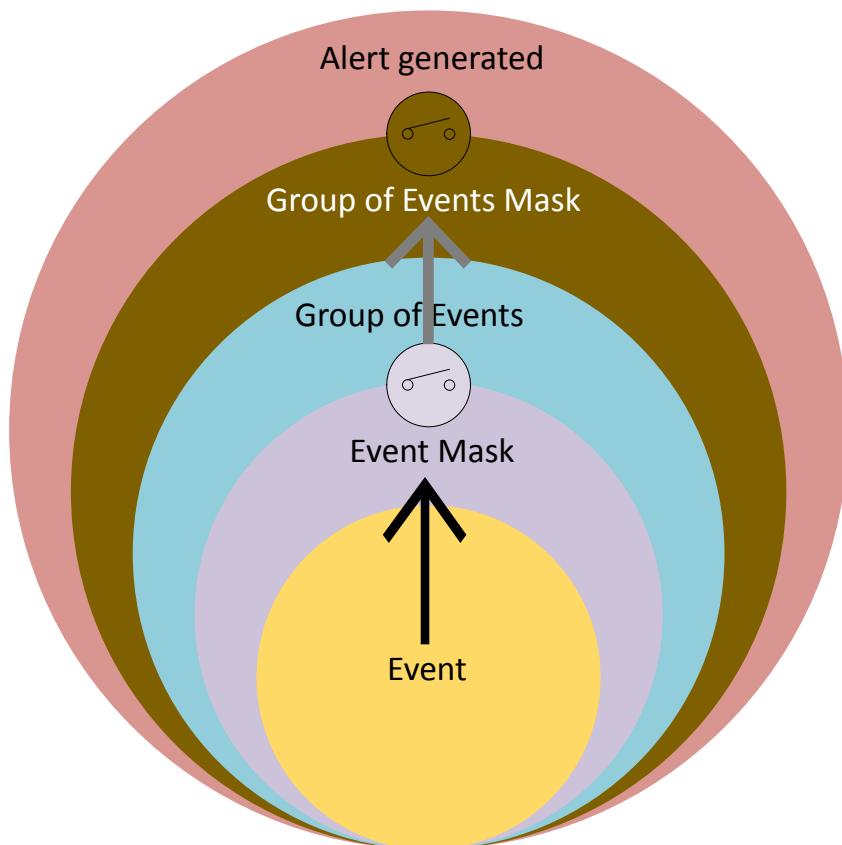

Figure 1. Interrupt generation structure

To generate an Alert, the Event and Group it belongs to need to be unmasked.

Only hardware faults have a direct path from the Event to the Alert generation.

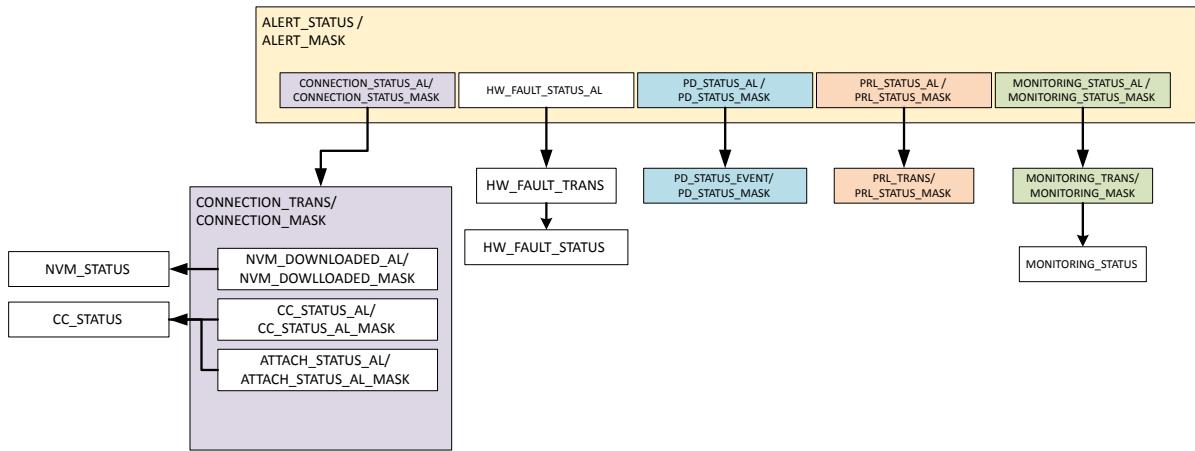

Figure 2. Interrupt register interlinking

## 1.3 Event groups

STUSB4531 interrupts are structured into five groups:

- Configuration and connection: CONNECTION\_STATUS\_AL

- Communication Protocol Layer: PRL\_STATUS\_AL

- Power Delivery: PD\_STATUS\_AL

- Vbus Monitoring: MONITORING\_STATUS\_AL

- Hardware faults: HW\_FAULT\_STATUS\_AL

When an unmasked event occurs in a group, the associated bit in the ALERT\_STATUS register (address 0x0010) will flag an Alert, assuming the associated group is unmasked.

Figure 3. ALERT\_STATUS and ALERT\_STATUS\_MASK registers address 0x0010 and 0x0011

|        |                          |                                                                                                                         |

|--------|--------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 0x0010 | <i>ALERT_STATUS</i>      | [4] CONNECTION_STATUS_AL<br>[3] HW_FAULT_STATUS_AL<br>[2] PD_STATUS_AL<br>[1] PRL_STATUS_AL<br>[0] MONITORING_STATUS_AL |

| 0x0011 | <i>ALERT_STATUS_MASK</i> | [4] CONNECTION_STATUS_AL_MASK<br>[2] PD_STATUS_AL_MASK<br>[1] PRL_STATUS_AL_MASK<br>[0] MONITORING_STATUS_AL_MASK       |

## 1.4 Reading events

The following registers are cleared upon an I<sup>2</sup>C read action:

- CONNECTION\_TRANS: address 0x0027

- PRL\_TRANS: address 0x0017

- PD\_STATUS\_EVENT: address 0x0012

- MONITORING\_TRANS: address 0x0014

- HW\_FAULT\_TRANS: address 0x001C

Consequently, the content of these registers must be stored after being read to take the required action.

## 2 Event signification

### 2.1 Configuration and connection - CONNECTION\_STATUS\_AL:

Figure 4. Event registers linked to CONNECTION\_STATUS\_AL

|        |                  |                                                                                  |

|--------|------------------|----------------------------------------------------------------------------------|

| 0x0027 | CONNECTION_TRANS | [2] NVM_DOWNLOADED_AL<br>[1] CC_STATUS_AL<br>[0] ATTACH_STATUS_AL                |

| 0x0028 | CONNECTION_MASK  | [2] NVM_DOWNLOADED_AL_MASK<br>[1] CC_STATUS_AL_MASK<br>[0] ATTACH_STATUS_AL_MASK |

This register mainly provides information on STUSB4531 startup.

Each event is linked to a dedicated status register, as illustrated in Figure 2. Interrupt register interlinking.

#### 2.1.1 NVM\_DOWNLOADED\_AL

When set, the NVM\_STATUS register should be read.

Figure 5. NVM\_STATUS register

|        |            |                                                            |

|--------|------------|------------------------------------------------------------|

| 0x001F | NVM_STATUS | [7] NVM_LOADED<br>[6] NVM_END_OP<br>[5:0] NVM_WRITE_STATUS |

|--------|------------|------------------------------------------------------------|

During VDD power-up operation, NVM\_LOADED indicates that the STUSB4531 is ready to operate. All I<sup>2</sup>C registers can then be accessed.

NVM\_END\_OP and NVM\_WRITE\_STATUS are used only during NVM read and write operations.

#### 2.1.2 CC\_STATUS\_AL

When set, it indicates that an event occurred on the CC pin. A source Rp value change will generate a CC\_STATUS\_AL event, as CCx\_state will change.

The real-time CC\_STATUS register can then be read.

Figure 6. CC\_STATUS register

|        |           |                                                                                                                                   |

|--------|-----------|-----------------------------------------------------------------------------------------------------------------------------------|

| 0x001A | CC_STATUS | [7] PLUG_ORIENTATION<br>[6] ATTACH_STATUS<br>[5] LOOKING_4_CONNECTION<br>[4] CONNECT_RESULT<br>[3:2] CC2_STATE<br>[1:0] CC1_STATE |

|--------|-----------|-----------------------------------------------------------------------------------------------------------------------------------|

#### 2.1.3 ATTACH\_STATUS\_AL

When set, it indicates that the STUSB4531 is in the Type-C ATTACH state.

By reading the CC\_STATUS register, the exact status of the connection can be determined.

## 2.2

## Communication - Protocol Layer: PRL\_STATUS\_AL

Unless specified, events from this register can be available both in autorun and hybrid mode.

Figure 7. Event registers linked to PRL\_STATUS\_AL

|        |                        |                                                                                                                                                          |

|--------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0017 | <i>PRL_TRANS</i>       | [7] PRL_TX_ERR<br>[6] PRL_TX_DISCARD<br>[3] PRL_MSG_SENT<br>[2] PRL_MSG_RECEIVED<br>[1] PRL_HR_DONE<br>[0] PRL_HR_RECEIVED                               |

| 0x0018 | <i>PRL_STATUS_MASK</i> | [7] PRL_TX_ERR_MASK<br>[6] PRL_TX_DISCARD_MASK<br>[3] PRL_MSG_SENT_MASK<br>[2] PRL_MSG_RECEIVED_MASK<br>[1] PRL_HR_DONE_MASK<br>[0] PRL_HR_RECEIVED_MASK |

- PRL\_TX\_ERR: after retrying nRetry times to send a message to the port partner without acknowledgement, the STUSB4531 notifies that message has not been sent, and the protocol error will be handled through soft reset or hard reset.

- PRL\_TX\_DISCARD: occurs in PD3 when an AMS <sup>(1)</sup> sequence is initiated by software in hybrid mode. It indicates that the message cannot be sent due to collision avoidance. Event valid only in hybrid mode.

- PRL\_MSG\_SENT: successful message sending and acknowledge notification. Event is available in hybrid or autorun operations.

- PRL\_MSG\_RECEIVED: indicates the reception of a new message. Message is available in Rx registers.

- PRL\_HR\_DONE: Hard reset has been sent by STUSB4531.

- PRL\_HR\_RECEIVED: Hard reset message received from the port partner.

1. AMS: Atomic Message Sequence. See "USB Power delivery specification" for more details.

## 2.3

### Power Delivery: PD\_STATUS\_AL

Unless specified, events from this register can be available both in autorun and hybrid mode.

Figure 8. Event registers linked to PD\_STATUS\_AL

|        |                             |                                                                                                           |

|--------|-----------------------------|-----------------------------------------------------------------------------------------------------------|

| 0x0012 | <i>PD_STATUS_EVENT</i>      | [7] TX_BUFFER_READY<br>[2] AMS_STOPPED<br>[1] TRANSITION_END<br>[0] TRANSITION_WINDOW                     |

| 0x0013 | <i>PD_STATUS_EVENT_MASK</i> | [7] TX_BUFFER_READY_MASK<br>[2] AMS_STOPPED_MASK<br>[1] TRANSITION_END_MASK<br>[0] TRANSITION_WINDOW_MASK |

- TX\_BUFFER\_READY: This event indicates when the Tx buffer is ready to be written or updated, to post a new message or to update a predefined hardware answer.

- AMS\_STOPPED: This event indicates the end of an AMS sequence initiated by the counterpart, or an AMS sequence initiated by STUSB4531 and handled by its policy engine hardware.

- TRANSITION\_END: This event indicates that the power transition due to a new explicit contract is complete.

- TRANSITION\_WINDOW: This event indicates that a PD request has been accepted, and the power transition phase has started.

- MONITORING\_TRANS register is cleared on read register.

- MONITORING\_MASK register is used to mask the event, in order not to generate an unwanted alert on monitoring events.

- MONITORING\_STATUS register is providing real-time status information.

## 2.4

### VBUS Monitoring: MONITORING\_STATUS\_AL

This group of events provides various information on VBUS monitoring related to different thresholds reached.

- MONITORING\_TRANS register is cleared on read register.

- MONITORING\_MASK register is used to mask events, in order not to generate an unwanted alert on monitoring events.

- MONITORING\_STATUS register is providing real-time status information.

**Figure 9. Event and status registers linked to MONITORING\_STATUS\_AL**

|        |                          |                                                                                                 |

|--------|--------------------------|-------------------------------------------------------------------------------------------------|

| 0x0014 | <i>MONITORING_TRANS</i>  | [4] VBUS_HIGH_TRANS<br>[3] VBUS_LOW_TRANS<br>[1] VBUS_VALID_TRANS<br>[0] VBUS_VSAFE0V_TRANS     |

| 0x0015 | <i>MONITORING_MASK</i>   | [4] VBUS_HIGH_MASK<br>[3] VBUS_LOW_MASK<br>[1] VBUS_VALID_AL_MASK<br>[0] VBUS_VSAFE0V_MASK      |

| 0x0016 | <i>MONITORING_STATUS</i> | [4] VBUS_HIGH_STATUS<br>[3] VBUS_LOW_STATUS<br>[1] VBUS_VALID_STATUS<br>[0] VBUS_VSAFE0V_STATUS |

- VBUS\_HIGH\_TRANS: This event indicates that VBUS crosses the VBUS overvoltage threshold (see  $V_{TH\_HIGH}$  definition in product datasheet). VBUS\_HIGH\_STATUS reflects comparator output.

- VBUS\_LOW\_TRANS: This event indicates that VBUS crosses the VBUS undervoltage threshold (see  $V_{TH\_LOW}$  definition in product datasheet). VBUS\_LOW\_STATUS reflects comparator output.

- VBUS\_VALID\_TRANS: This event indicates that VBUS crosses the VBUS\_VALID threshold (see VBUS\_VALID definition in product datasheet). VBUS\_VALID\_STATUS reflects comparator output.

- VBUS\_VSAFE0V\_TRANS: This event indicates that VBUS crosses the VBUS\_VSAFE0V threshold (see VBUS\_VSAFE0V definition in product datasheet). VBUS\_VSAFE0V\_STATUS reflects comparator output.

## 2.5 Hardware faults: HW\_FAULT\_STATUS\_AL

Hardware faults event cannot be masked.

Figure 10. Event and status registers linked to HW\_FAULT\_STATUS\_AL

|        |                        |                                                                              |

|--------|------------------------|------------------------------------------------------------------------------|

| 0x001C | <i>HW_FAULT_TRANS</i>  | [7] I2C_WATCHDOG<br>[6] CS_OVP<br>[1] TH_WARN_TRANS<br>[0] TH_SHUTDOWN_TRANS |

| 0x001D | <i>HW_FAULT_STATUS</i> | [1] TH_WARN<br>[0] TH_SHUTDOWN                                               |

- I2C\_WATCHDOG: This event indicates that an I<sup>2</sup>C action has not been observed for approximately 2 seconds after ALERT has been asserted. I2C\_WATCHDOG functionality is not enabled by default.

- CS\_OVP: This event indicates that at least one CC pin voltage has reached  $V_{THOVP\_CC}$ .

- TH\_WARN\_TRANS: This event indicates that the internal temperature has crossed the warning temperature threshold (see TH<sub>WARN</sub> definition in product datasheet). TH\_WARN indicates that the current internal temperature is greater than TH<sub>WARN</sub>.

- TH\_SHUTDOWN\_TRANS: This event indicates that the internal temperature has crossed the shutdown temperature threshold (see TH<sub>SHUTDOWN</sub> definition in product datasheet). TH\_SHUTDOWN indicates that current internal temperature is greater than TH<sub>SHUTDOWN</sub>.

### 3 References

- [STUSB4531 datasheet](#)

- RM0562: STUSB4531 register map

- USB Power Delivery specification: <https://www.usb.org/document-library/usb-power-delivery>

- USB Type-C cable and connector specification: <https://www.usb.org/document-library/usb-type-cr-cable-and-connector-specification-release-24>

## Revision history

**Table 1. Document revision history**

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 16-Dec-2025 | 1       | Initial release. |

## Contents

|              |                                                     |           |

|--------------|-----------------------------------------------------|-----------|

| <b>1</b>     | <b>STUSB4531 prerequisite</b>                       | <b>2</b>  |

| <b>1.1</b>   | Interrupt default setup                             | 2         |

| <b>1.2</b>   | Interrupt structure                                 | 2         |

| <b>1.3</b>   | Event groups                                        | 3         |

| <b>1.4</b>   | Reading events                                      | 3         |

| <b>2</b>     | <b>Event signification</b>                          | <b>4</b>  |

| <b>2.1</b>   | Configuration and connection - CONNECTION_STATUS_AL | 4         |

| <b>2.1.1</b> | NVM_DOWNLOADED_AL                                   | 4         |

| <b>2.1.2</b> | CC_STATUS_AL                                        | 4         |

| <b>2.1.3</b> | ATTACH_STATUS_AL                                    | 4         |

| <b>2.2</b>   | Communication - Protocol Layer: PRL_STATUS_AL       | 5         |

| <b>2.3</b>   | Power Delivery: PD_STATUS_AL                        | 6         |

| <b>2.4</b>   | VBUS Monitoring: MONITORING_STATUS_AL               | 7         |

| <b>2.5</b>   | Hardware faults: HW_FAULT_STATUS_AL                 | 8         |

| <b>3</b>     | <b>References</b>                                   | <b>9</b>  |

|              | <b>Revision history</b>                             | <b>10</b> |

## List of tables

|                                              |    |

|----------------------------------------------|----|

| Table 1. Document revision history . . . . . | 10 |

|----------------------------------------------|----|

## List of figures

|                   |                                                                                  |   |

|-------------------|----------------------------------------------------------------------------------|---|

| <b>Figure 1.</b>  | Interrupt generation structure . . . . .                                         | 2 |

| <b>Figure 2.</b>  | Interrupt register interlinking . . . . .                                        | 3 |

| <b>Figure 3.</b>  | ALERT_STATUS and ALERT_STATUS_MASK registers address 0x0010 and 0x0011 . . . . . | 3 |

| <b>Figure 4.</b>  | Event registers linked to CONNECTION_STATUS_AL . . . . .                         | 4 |

| <b>Figure 5.</b>  | NVM_STATUS register . . . . .                                                    | 4 |

| <b>Figure 6.</b>  | CC_STATUS register . . . . .                                                     | 4 |

| <b>Figure 7.</b>  | Event registers linked to PRL_STATUS_AL . . . . .                                | 5 |

| <b>Figure 8.</b>  | Event registers linked to PD_STATUS_AL . . . . .                                 | 6 |

| <b>Figure 9.</b>  | Event and status registers linked to MONITORING_STATUS_AL . . . . .              | 7 |

| <b>Figure 10.</b> | Event and status registers linked to HW_FAULT_STATUS_AL . . . . .                | 8 |

**IMPORTANT NOTICE – READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to [www.st.com/trademarks](http://www.st.com/trademarks). All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved